# **Improving Prefetching Mechanisms for Tiled CMP Platforms**

### **Martí Torrents**

Computer Architecture Department

Universitat Politècnica de Catalunya - BarcelonaTech

This dissertation is submitted for the degree of Doctor of Philosophy

### THESIS INFORMATION

Title of the thesis: Improving Prefetching Mechanisms for Tiled CMP Platforms

Candidate: Martí Torrents

Degree: Doctor of Philosophy

Advisors:

Raúl Martínez - Oracle Labs

Carlos Molina - Universitat Rovira Virgili

Tutor:

Antonio González - Universitat Politècnica de Catalunya

Department: Computer Architecture Department (DAC)

#### **COMMITTEE MEMBERS**

President: José Luis Sánchez - Universidad de Castilla-La Mancha

Secretary: Ramon Canal Corretger - Universitat Politècnica de Catalunya

Vocal: Pedro Marcuello Pascual - Broadcom Networks

Substitute: Francisco José Alfaro Cortes - Escuela Universitaria Politécnica de Albacete

Substitute: Josep Llosa Espuny - Universitat Politècnica de Catalunya

Submission date: Friday, 29th September 2016

I would like to dedicate this thesis to my loving parents, Florenci and Magda, and my brothers, Cesc and Esteve. I know that, although it has not been easy for them, because they did no understand what I was exactly doing, they gave me all their support when I was down in though times. Also to all my friends, Albert, Balma, Gerard, Laura, Marc Morales, Marc Corominas, Marta, Queralt and Xavi. You found fun in my sad moments and you have helped me week by week along these four years. All these little weekly oasis during our dinners, our "talkings" or simply the moments we spent together had been essential for having this work done today. At last but not least to you, Eli, because we have shared this experience day by day. Thanks for wiping away my tears when I was down, thanks for shining in the darkness and thanks for walking this long way next to me. I am sure that without all this lovely people it would have been impossible for me to achieve this milestone. Thanks to all of you.

M'agradaría dedicar aquesta tesi als meus estimats pares, Florenci i Magda, i als meus germans, Cesc i Esteve. Sé que, encara que no ha estat fàcil per ells perquè sovint no entenien allò que feia, m'han donat suport sempre i sobretot en els moments difícils. També a tots els meus amics, Albert, Balma, Gerard, Laura, Marc Morales, Marc Corominas, Marta, Queralt i Xavi. Vau arrancar-me somriures en els moments mes delicats, i setmana a setmana m'heu ajudat molt durant aquests 4 anys. Tots aquests petits oasis setmanals durant els sopars, els "talkings" o senzillament els moments que passàvem junts, han estat essencials per tenir aquest projecte acabat avui. Finalment, però no per això menys important, a tu, Eli, perquè amb tu he compartit aquesta experiència dia a dia. Gràcies per eixugar-me les llàgrimes quan estava més desanimat, gràcies per brillar a la foscor i per fer aquest llarg camí al meu costat. Estic segur que sense vosaltres, per mi, hagués estat impossible aconseguir aquesta fita. Gràcies a tothom.

### Acknowledgements

My first contact on research was in 2008 when Prof. Ramon Canal suggested that I helped him in his investigations. He introduced me in the research and encouraged me to start a PhD. This was the beginning from everything. From that moment, I started to meet researchers who have helped a lot to me to finish this dissertation. For this reason, first of all, I would like to thank Ramon for introducing me to this world and showing me what has become my passion.

The second person I met when I was starting my research experience was Prof. Antonio Gonzalez and for him goes my second acknowledgement. Antonio proposed doing my Master Thesis in the Intel Barcelona Research Center. I was excited about it, thus, I accepted the proposal and there I met my Master advisors. One of them, Dr. Raúl Martínez, became my PhD advisor. When I finished my internship in Intel, I started the PhD. My tutor, Antonio Gonzalez, introduced to me my second advisor, Prof. Carlos Molina. My two last acknowledgments are for them, Raul and Carlos, who had advised me through this process. Carlos' positivity and Raul's good sense have been the key to overcome this PhD challenges. Without any doubt, the achievement of this milestone would not be possible without them.

To all of you, thanks for everything.

### **Abstract**

Recently, high performance processor designs have evolved toward Chip-Multiprocessor (CMP) architectures to deal with instruction level parallelism limitations and, more important, to manage the power consumption that is becoming unaffordable due to the increased transistor count and clock frequency. At the present moment, this architecture, which implements multiple processing cores on a single die, is commercially available with up to twenty four processors on a single chip and there are roadmaps and research trends that suggest that number of cores will increase in the near future. The increasing on number of cores has converted the interconnection network in a key issue that will have significant impact on performance. Moreover, as the number of cores increases, tiled architectures are foreseen to provide a scalable solution to handle design complexity.

Network-on-Chip (NoC) emerges as a solution to deal with growing on-chip wire delays. On the other hand, CMP designs are likely to be equipped with latency hiding techniques like prefetching in order to reduce the negative impact on performance that, otherwise, high cache miss rates would lead to. Unfortunately, the extra number of network messages that prefetching entails can drastically increase power consumption and the latency in the NoC. In this thesis, we do not develop a new prefetching technique for CMPs but propose improvements applicable to any of them. Specifically, we analyze the behavior of the prefetching in the CMPs and its impact to the interconnect. We propose several dynamic management techniques to improve the performance of the prefetching mechanism in the system. Furthermore, we identify the main problems when implementing prefetching in distributed memory systems like tiled architectures and propose directions to solve them. Finally, we propose several research lines to continue the work done in this thesis.

### **Table of contents**

| Li | ist of figures xv |          |                                                             |    |  |  |  |  |  |

|----|-------------------|----------|-------------------------------------------------------------|----|--|--|--|--|--|

| Li | ist of tables xix |          |                                                             |    |  |  |  |  |  |

| 1  | Introduction      |          |                                                             |    |  |  |  |  |  |

|    | 1.1               | Motiva   | ation                                                       | 1  |  |  |  |  |  |

|    | 1.2               | Object   | tives                                                       | 4  |  |  |  |  |  |

|    | 1.3               | Thesis   | s organization                                              | 7  |  |  |  |  |  |

| 2  | Stat              | e of the | Art                                                         | 9  |  |  |  |  |  |

|    | 2.1               | Introd   | uction                                                      | 9  |  |  |  |  |  |

|    | 2.2               | Prefet   | ching basic concepts                                        | 9  |  |  |  |  |  |

|    |                   | 2.2.1    | Prefetchers in current processors                           | 12 |  |  |  |  |  |

|    |                   | 2.2.2    | Implemented prefetchers                                     | 13 |  |  |  |  |  |

|    |                   | 2.2.3    | Performance implications                                    | 23 |  |  |  |  |  |

|    |                   | 2.2.4    | Prefetching in CMPs                                         | 25 |  |  |  |  |  |

|    | 2.3               | Netwo    | orks on chip                                                | 26 |  |  |  |  |  |

|    |                   | 2.3.1    | Traffic differentiation in the communication infrastructure | 27 |  |  |  |  |  |

|    |                   | 2.3.2    | Traffic differentiation in the communication paradigm       | 28 |  |  |  |  |  |

|    |                   | 2.3.3    | Traffic differentiation in the application mapping          | 29 |  |  |  |  |  |

|    | 2.4               | Dynan    | mic management                                              | 30 |  |  |  |  |  |

|    |                   | 2.4.1    | Filtering                                                   | 30 |  |  |  |  |  |

|    |                   | 2.4.2    | Throttling                                                  | 30 |  |  |  |  |  |

|    |                   | 2.4.3    | Prioritization                                              | 31 |  |  |  |  |  |

|    |                   | 2.4.4    | Summary of other dynamic management techniques              | 32 |  |  |  |  |  |

|    | 2.5               | Open-    | source multiprocessor simulators                            | 32 |  |  |  |  |  |

|    |                   | 2.5.1    | Benchmarks                                                  | 33 |  |  |  |  |  |

Table of contents

| 3 | Pref | fetching | g evaluation in multi-core platforms                             | 35 |

|---|------|----------|------------------------------------------------------------------|----|

|   | 3.1  | Introd   | uction                                                           | 35 |

|   | 3.2  | The of   | fficial release version of the gem5 simulator                    | 37 |

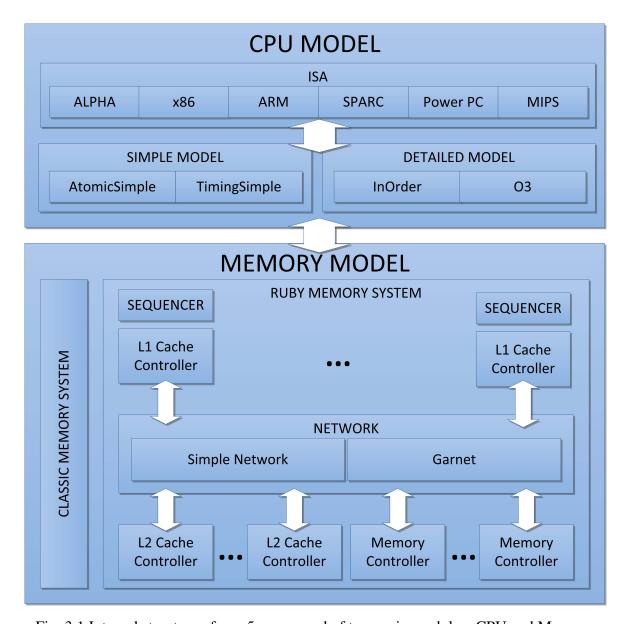

|   |      | 3.2.1    | CPU module                                                       | 37 |

|   |      | 3.2.2    | The memory system                                                | 37 |

|   |      | 3.2.3    | Interconnection network                                          | 40 |

|   | 3.3  | Conve    | erting gem5 to a prefetching-aware simulator                     | 42 |

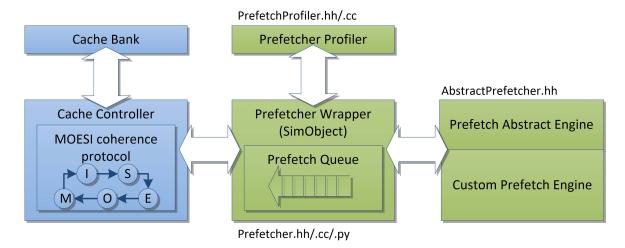

|   |      | 3.3.1    | New SimObject                                                    | 42 |

|   |      | 3.3.2    | Abstract prefetcher and custom prefetch engines                  | 44 |

|   |      | 3.3.3    | Modifications in the cache controller and the coherence protocol | 48 |

|   |      | 3.3.4    | Prefetching statistics                                           | 54 |

|   | 3.4  | Perfor   | mance study                                                      | 55 |

|   |      | 3.4.1    | Experimental framework                                           | 55 |

|   |      | 3.4.2    | Aggressiveness analysis for all prefetchers: average results     | 56 |

|   |      | 3.4.3    | Aggressiveness analysis on Tagged: detailed results              | 61 |

|   |      | 3.4.4    | Aggressiveness analysis on RPT: detailed results                 | 62 |

|   |      | 3.4.5    | Aggressiveness analysis on GHB: detailed results                 | 64 |

|   |      | 3.4.6    | Analysis of the network resources effect                         | 66 |

|   |      | 3.4.7    | Scalability analysis                                             | 68 |

|   | 3.5  | Conclu   | usions                                                           | 70 |

| 4 | Con  | Gdonoo   | nucliator mechanisms for nucletching in CMDs                     | 73 |

| + | 4.1  |          | predictor mechanisms for prefetching in CMPs                     |    |

|   | 4.1  |          | uction                                                           |    |

|   | 4.2  | -        | sed confidence predictors for prefetcher requests                |    |

|   |      | 4.2.1    | Phase history heuristic                                          |    |

|   |      | 4.2.2    | Balanced phase history heuristic                                 |    |

|   |      | 4.2.3    | Stream position based profiling                                  | 76 |

|   |      |          | Code region dynamic profiling                                    |    |

|   | 4.2  | 4.2.5    | Heuristics combination                                           | 79 |

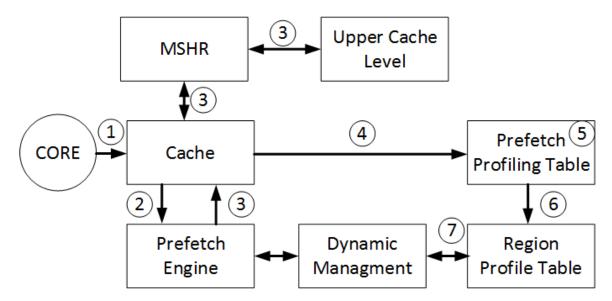

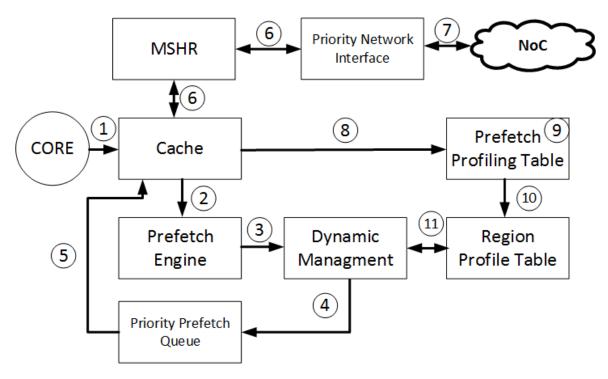

|   | 4.3  | 4.3.1    | vare implementation                                              | 80 |

|   |      |          | New hardware description                                         | 80 |

|   | 1 1  | 4.3.2    | Prediction flow                                                  | 82 |

|   | 4.4  |          | mance evaluation                                                 | 85 |

|   |      | 4.4.1    | Experimental framework                                           | 85 |

|   |      | 4.4.2    | Tagged prefetcher analysis                                       | 86 |

|   |      | 4.4.3    | Reference Prediction Table prefetcher analysis                   | 89 |

|   |      | 4.4.4    | Global History Buffer prefetcher analysis                        | 91 |

| Table of contents | xiii |

|-------------------|------|

|   | 4.5  | Conclu                                                       | usions                                                       | 95  |  |  |  |  |  |

|---|------|--------------------------------------------------------------|--------------------------------------------------------------|-----|--|--|--|--|--|

| 5 | Imp  | roving the Prioritization and Filtering of Prefetch Requests |                                                              |     |  |  |  |  |  |

|   | 5.1  | Introd                                                       | uction                                                       | 97  |  |  |  |  |  |

|   | 5.2  | Confid                                                       | dence predictor based filtering                              | 98  |  |  |  |  |  |

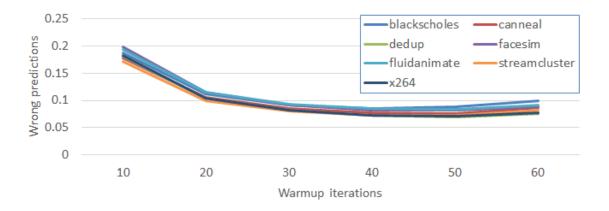

|   |      | 5.2.1                                                        | Warmup period                                                | 99  |  |  |  |  |  |

|   |      | 5.2.2                                                        | Dynamic warmup strategy                                      | 100 |  |  |  |  |  |

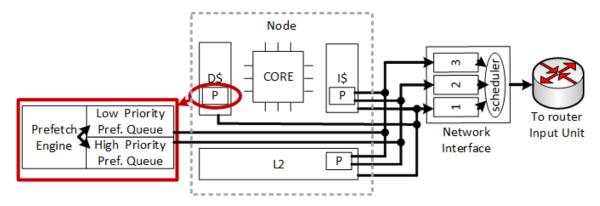

|   | 5.3  | Confic                                                       | dence predictor based prioritization                         | 101 |  |  |  |  |  |

|   |      | 5.3.1                                                        | Levels of priority                                           | 101 |  |  |  |  |  |

|   |      | 5.3.2                                                        | Points of prioritization                                     | 101 |  |  |  |  |  |

|   | 5.4  | Comb                                                         | ined confidence predictor based filtering and prioritization | 103 |  |  |  |  |  |

|   | 5.5  | Hardw                                                        | vare implementation                                          | 104 |  |  |  |  |  |

|   |      | 5.5.1                                                        | Execution flow                                               | 104 |  |  |  |  |  |

|   |      | 5.5.2                                                        | Hardware overhead evaluation                                 | 107 |  |  |  |  |  |

|   | 5.6  | Perfor                                                       | mance evaluation                                             | 109 |  |  |  |  |  |

|   |      | 5.6.1                                                        | Experimental framework                                       | 110 |  |  |  |  |  |

|   |      | 5.6.2                                                        | Implementation of the state of the art heuristics            | 110 |  |  |  |  |  |

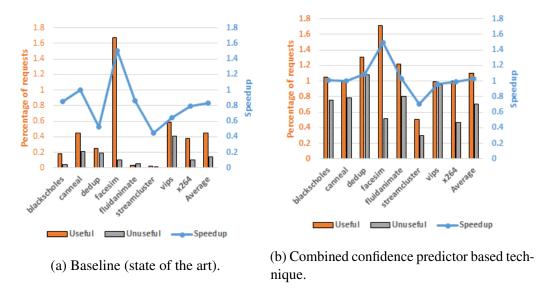

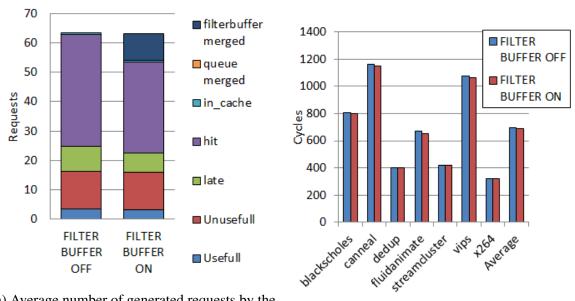

|   |      | 5.6.3                                                        | Filtering experiments                                        | 112 |  |  |  |  |  |

|   |      | 5.6.4                                                        | Prioritization experiments                                   | 115 |  |  |  |  |  |

|   |      | 5.6.5                                                        | Combined filtering and prioritization experiments            | 116 |  |  |  |  |  |

|   | 5.7  | Conclu                                                       | usions                                                       | 117 |  |  |  |  |  |

| 6 | Pref | etching                                                      | Challenges in Distributed Shared Memories for CMPs           | 119 |  |  |  |  |  |

|   | 6.1  | Introd                                                       | uction                                                       | 119 |  |  |  |  |  |

|   | 6.2  | Challe                                                       | enge identification                                          | 121 |  |  |  |  |  |

|   |      | 6.2.1                                                        | Pattern detection                                            | 122 |  |  |  |  |  |

|   |      | 6.2.2                                                        | Prefetching queue filtering                                  | 123 |  |  |  |  |  |

|   |      | 6.2.3                                                        | Dynamic profiling                                            | 124 |  |  |  |  |  |

|   | 6.3  | Challe                                                       | enge evaluation methodology                                  | 124 |  |  |  |  |  |

|   |      | 6.3.1                                                        | Pattern detection                                            | 124 |  |  |  |  |  |

|   |      | 6.3.2                                                        | Prefetching queue filtering                                  | 125 |  |  |  |  |  |

|   |      | 6.3.3                                                        | Dynamic profiling                                            | 126 |  |  |  |  |  |

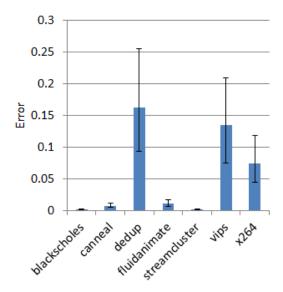

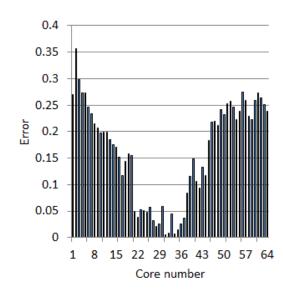

|   | 6.4  | Challe                                                       | enge analysis and quantification                             | 127 |  |  |  |  |  |

|   |      | 6.4.1                                                        | Pattern detection                                            | 128 |  |  |  |  |  |

|   |      | 6.4.2                                                        | Prefetching queue filtering                                  | 129 |  |  |  |  |  |

|   |      | 6.4.3                                                        | Dynamic profiling                                            | 129 |  |  |  |  |  |

|   | 6.5  | Facing                                                       | g the challenges                                             | 130 |  |  |  |  |  |

Table of contents

|   |       | 6.5.1   | Replication                                                      | 131 |

|---|-------|---------|------------------------------------------------------------------|-----|

|   |       | 6.5.2   | Centralization                                                   | 134 |

|   |       | 6.5.3   | Distribution                                                     | 136 |

|   | 6.6   | Conclu  | usions                                                           | 139 |

| 7 | Con   | clusion | s and future work                                                | 141 |

|   | 7.1   | Conclu  | usions                                                           | 141 |

|   | 7.2   | Object  | tive evaluation                                                  | 142 |

|   | 7.3   | Future  | work                                                             | 143 |

|   | 7.4   | Thesis  | contributions                                                    | 144 |

|   |       | 7.4.1   | Prefetching evaluation in multi-core platforms                   | 145 |

|   |       | 7.4.2   | Confidence predictor mechanisms for prefetching in CMPs          | 145 |

|   |       | 7.4.3   | Improving the Prioritization and Filtering of Prefetch Requests  | 145 |

|   |       | 7.4.4   | Prefetching Challenges in Distributed Shared Memories for CMPs . | 145 |

| R | foron | res     |                                                                  | 147 |

## **List of figures**

| 1.1 | Search hits for "network-on-chip" in IEEE Xplore archive                       | 2  |

|-----|--------------------------------------------------------------------------------|----|

| 1.2 | Projected relative delay for local and global wires and for gates in technolo- |    |

|     | gies of the near future [8]                                                    | 3  |

| 1.3 | (a) Normalized execution time and (b) network power consumption for a          |    |

|     | 16-core CMP with different prefetching mechanisms                              | 5  |

| 2.1 | Execution diagram assuming a) no prefetching, b) perfect prefetching, and c)   |    |

|     | degraded prefetching                                                           | 10 |

| 2.2 | Three forms of sequential prefetching: a) Prefetch on miss, b) tagged prefetch |    |

|     | and c) tagged prefetch with $K = 2$                                            | 14 |

| 2.3 | The organization of the reference prediction table                             | 17 |

| 2.4 | Markov prefetching                                                             | 18 |

| 2.5 | Distance Prefetching                                                           | 19 |

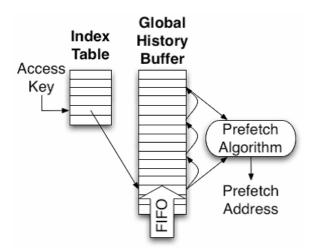

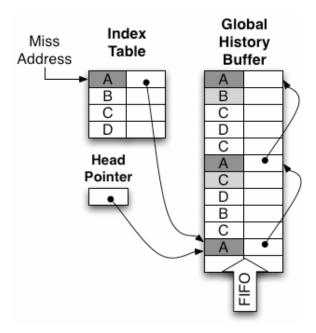

| 2.6 | Global History Buffer Prefetch Structure                                       | 20 |

| 2.7 | GHB Global / Address Correlation                                               | 22 |

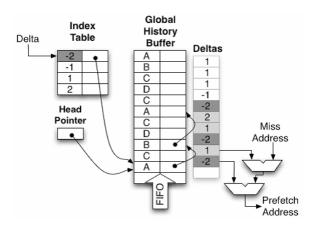

| 2.8 | GHB Global / Delta Correlation                                                 | 23 |

| 2.9 | Qualitative summary of the inherent key characteristics of PARSEC bench-       |    |

|     | marks. The pipeline model is a data-parallel model which also uses a func-     |    |

|     | tional partitioning. PARSEC workloads were chosen to cover different           |    |

|     | application domains, parallel models and runtime behaviors                     | 34 |

| 3.1 | Internal structure of gem5, composed of two main modules: CPU and Memory.      | 38 |

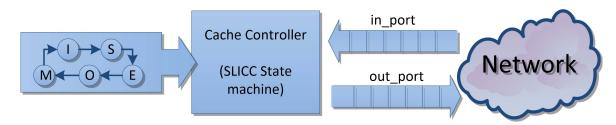

| 3.2 | High level view of the connections between the SLICC state machine and         |    |

|     | network in/out ports                                                           | 39 |

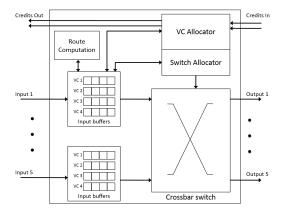

| 3.3 | Design of the 5-stage virtual channel router implemented in gem5               | 40 |

| 3.4 | Pipeline stages for the gem5 virtual channel router                            | 40 |

| 3.5 | Modified and new elements added to the simulator for prefetching support       | 43 |

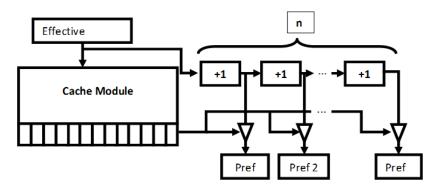

| 3.6 | Tagged prefetcher schema                                                       | 45 |

**xvi** List of figures

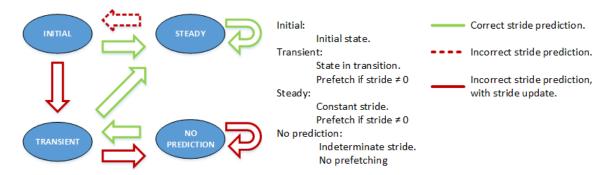

| 3.7  | State transition graph for reference prediction table entries                                          | 46                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

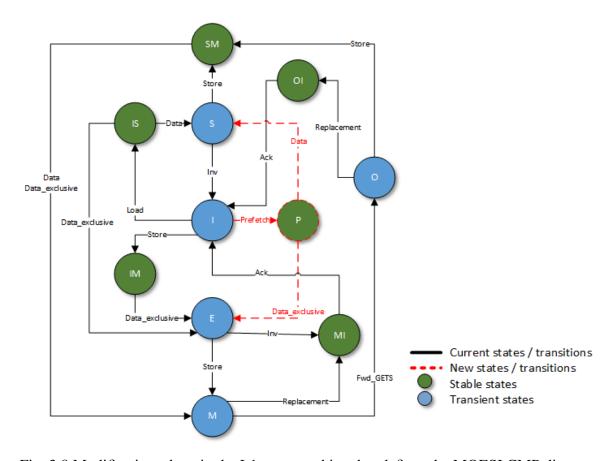

| 3.8  | Modifications done in the L1 state machine that defines the MOESI CMP                                  |                                                                                                                                   |

|      | directory protocol. Stable states detailed in Table 3.1                                                | 51                                                                                                                                |

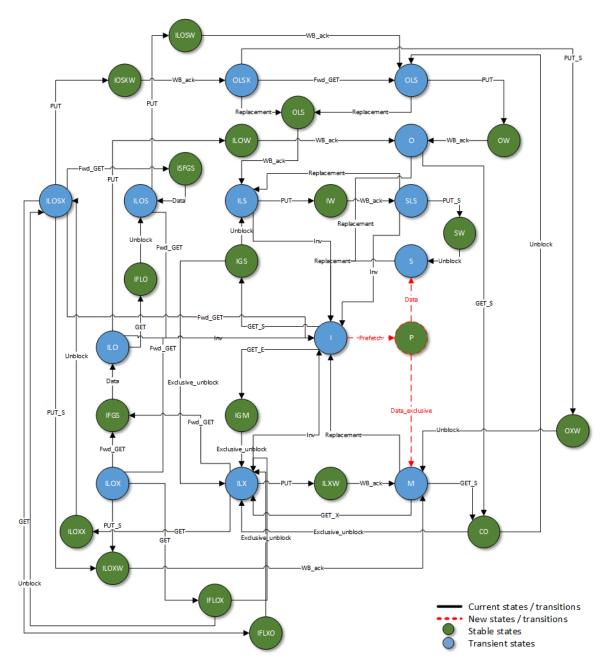

| 3.9  | Modifications done in the L2 state machine that defines the MOESI CMP                                  |                                                                                                                                   |

|      | directory protocol. Stable states detailed in Table 3.2                                                | 52                                                                                                                                |

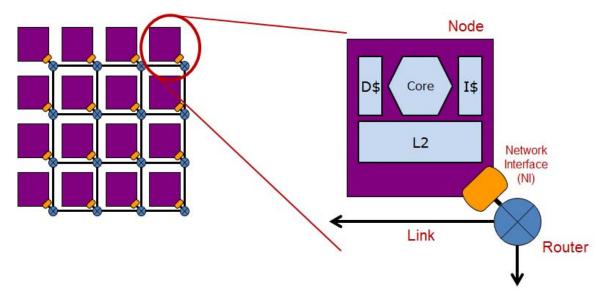

| 3.10 | Tile configuration of the simulated environment                                                        | 56                                                                                                                                |

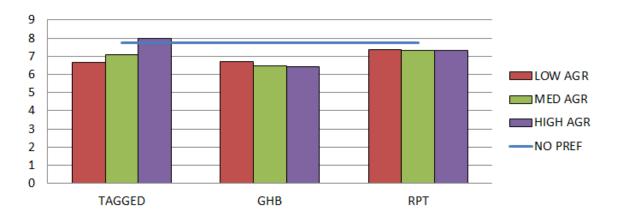

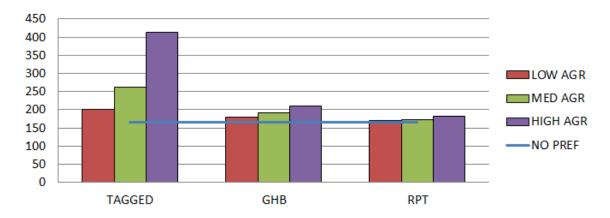

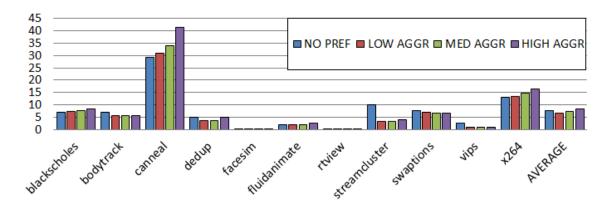

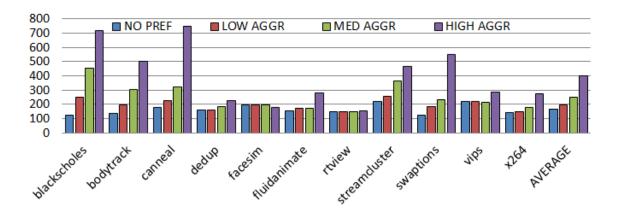

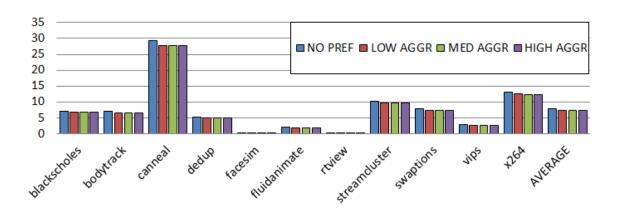

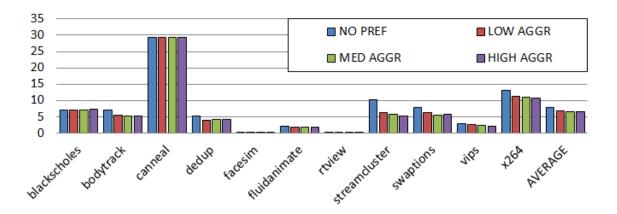

| 3.11 | Average MPKI calculated with the gem5 simulator and the prefetching module.                            | 58                                                                                                                                |

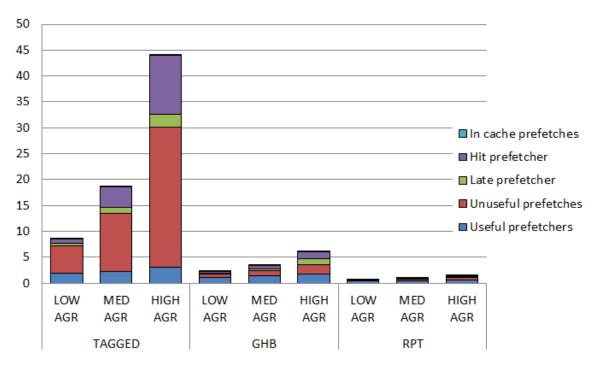

| 3.12 | Average prefetch request distribution                                                                  | 58                                                                                                                                |

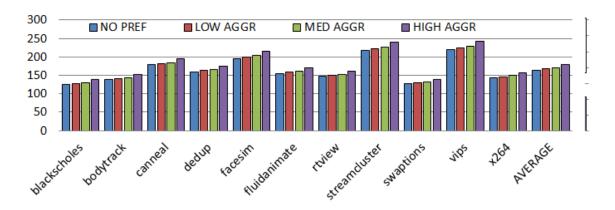

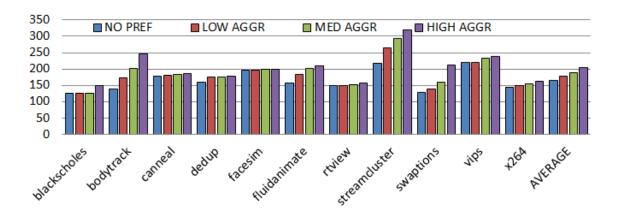

| 3.13 | Average L1 miss latency (cycles) calculated with the gem5 simulator and the                            |                                                                                                                                   |

|      | prefetching module                                                                                     | 59                                                                                                                                |

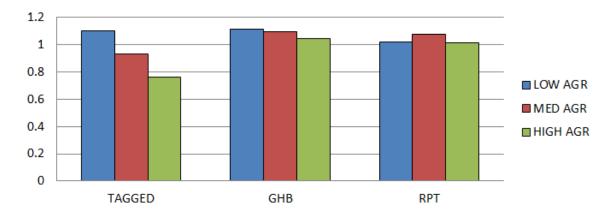

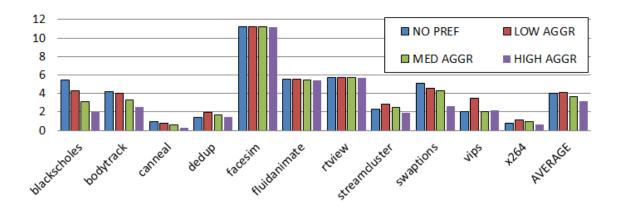

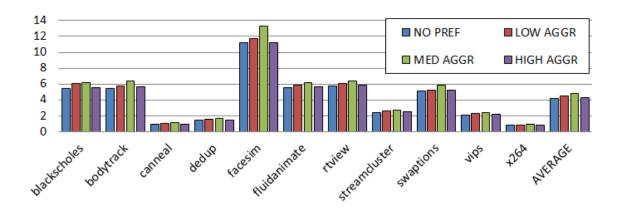

| 3.14 | Average IPC Speedup calculated with the gem5 simulator and the prefetching                             |                                                                                                                                   |

|      | module                                                                                                 | 60                                                                                                                                |

| 3.15 | Per benchmark MPKI results generated with the gem5 simulator and the                                   |                                                                                                                                   |

|      | prefetching module using the Tagged prefetcher                                                         | 61                                                                                                                                |

| 3.16 | Per benchmark average L1 miss latency (cycles) results generated with the                              |                                                                                                                                   |

|      | gem5 simulator and the prefetching module using the Tagged prefetcher                                  | 62                                                                                                                                |

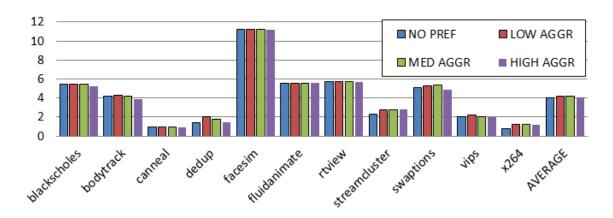

| 3.17 | Per benchmark IPC results generated with the gem5 simulator and the                                    |                                                                                                                                   |

|      | prefetching module using the Tagged prefetcher                                                         | 63                                                                                                                                |

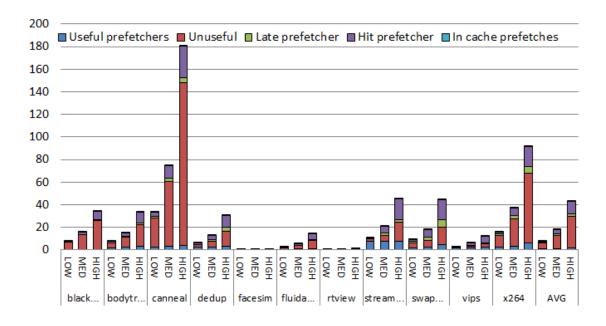

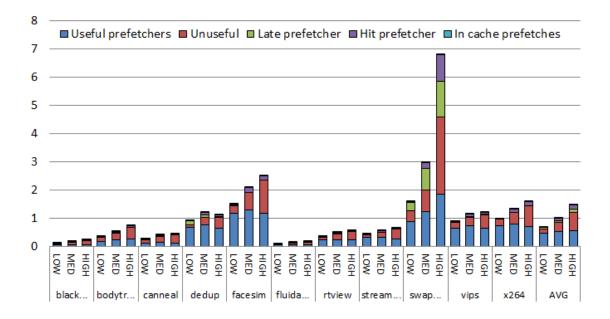

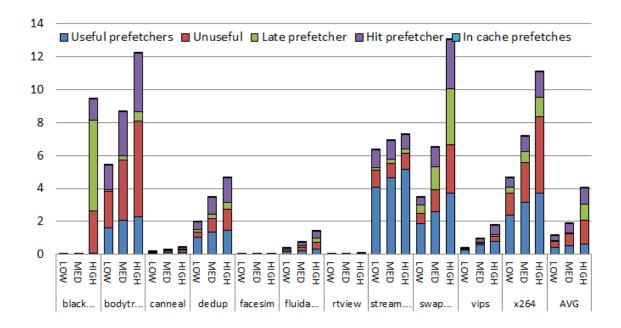

| 3.18 | Tagged prefetcher requests distribution every one thousand instructions                                | 63                                                                                                                                |

| 3.19 | Per benchmark MPKI results generated with the gem5 simulator and the                                   |                                                                                                                                   |

|      | prefetching module using the RPT prefetcher                                                            | 64                                                                                                                                |

| 3.20 | Per benchmark average L1 miss latency (cycles) results generated with the                              |                                                                                                                                   |

|      | gem5 simulator and the prefetching module using the RPT prefetcher                                     | 64                                                                                                                                |

| 3.21 | Per benchmark IPC results generated with the gem5 simulator and the                                    |                                                                                                                                   |

|      | prefetching module using the RPT prefetcher                                                            | 65                                                                                                                                |

| 3.22 | RPT prefetcher requests distribution every one thousand instructions                                   | 65                                                                                                                                |

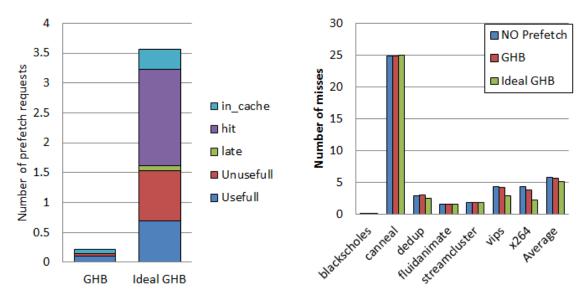

| 3.23 | Per benchmark MPKI results generated with the gem5 simulator and the                                   |                                                                                                                                   |

|      | prefetching module using the GHB prefetcher                                                            | 66                                                                                                                                |

| 3.24 | Per benchmark average L1 miss latency (cycles) results generated with the                              |                                                                                                                                   |

|      | gem5 simulator and the prefetching module using the GHB prefetcher                                     | 66                                                                                                                                |

| 3.25 | Per benchmark IPC Speedup results generated with the gem5 simulator and                                |                                                                                                                                   |

|      | the prefetching module using the GHB prefetcher                                                        | 67                                                                                                                                |

|      | •                                                                                                      | 67                                                                                                                                |

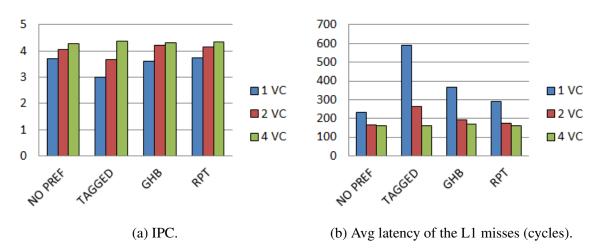

| 3.27 | Network resources analysis                                                                             | 68                                                                                                                                |

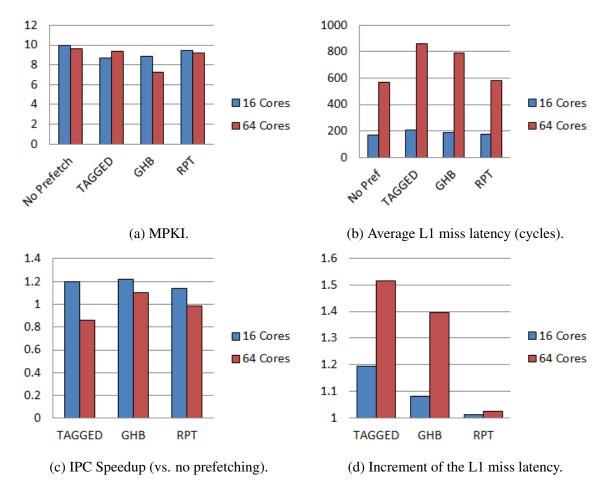

| 3.28 | Scalability analysis results with the prefetching module                                               | 69                                                                                                                                |

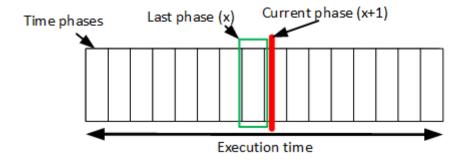

| 4.1  | How the last phase heuristic predicts its confidence                                                   | 75                                                                                                                                |

|      | 3.8 3.9 3.10 3.11 3.12 3.13 3.14 3.15 3.16 3.17 3.18 3.19 3.20 3.21 3.22 3.23 3.24 3.25 3.26 3.27 3.28 | 3.8 Modifications done in the L1 state machine that defines the MOESI CMP directory protocol. Stable states detailed in Table 3.1 |

List of figures xvii

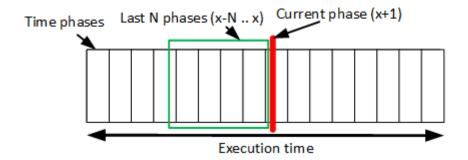

| 4.2  | How the phase history heuristic predicts its confidence                            | 76  |

|------|------------------------------------------------------------------------------------|-----|

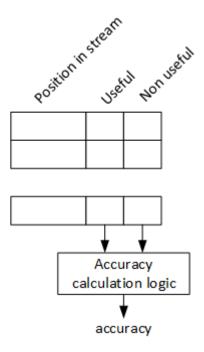

| 4.3  | Design of the stream based predictor                                               | 78  |

| 4.4  | Design of the code region predictor                                                | 79  |

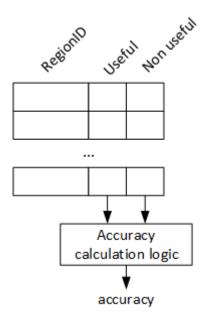

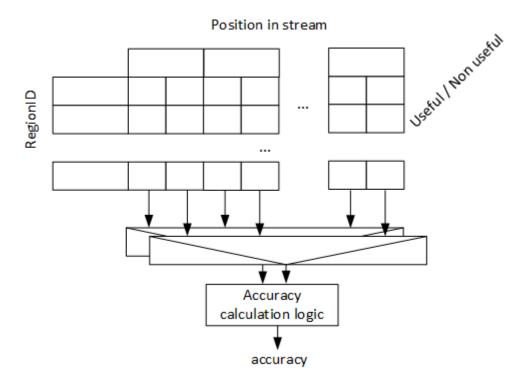

| 4.5  | Design of the combined predictor                                                   | 80  |

| 4.6  | Useful and non-useful classification of prefetch requests that last for more       |     |

|      | than 100 cycles in the Prefetch Profiling Table (using an unbounded table)         | 82  |

| 4.7  | Block diagram for the hardware implementation of the combined predictor.           | 83  |

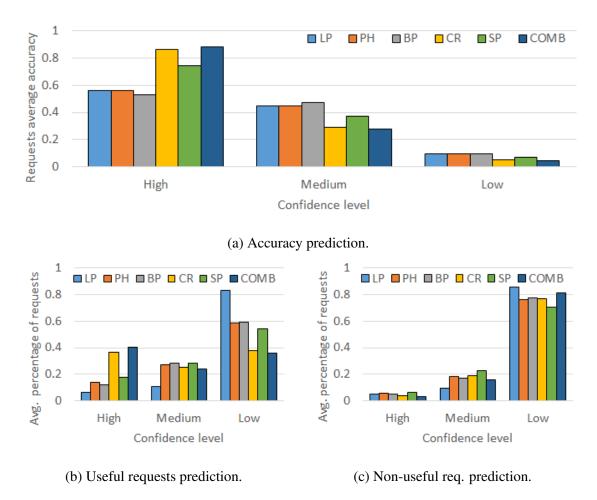

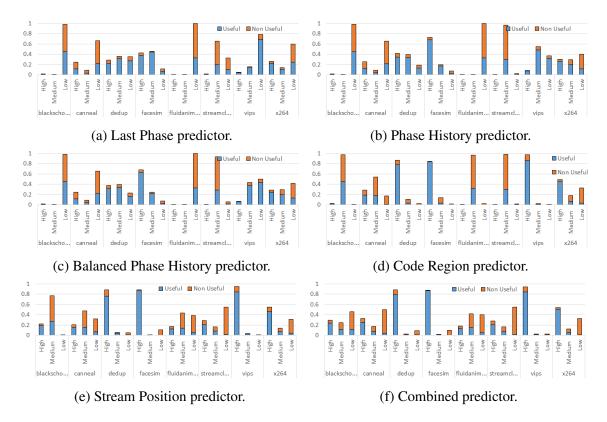

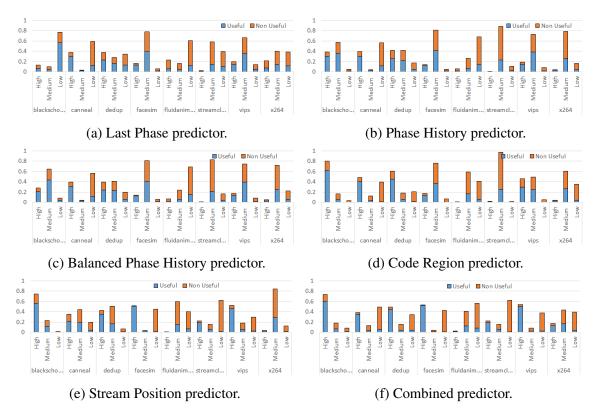

| 4.8  | Results from evaluating the confidence predictors with the Tagged Prefetcher       |     |

|      | as the stream prefetcher                                                           | 87  |

| 4.9  | Percentage of useful and non useful requests generated by the Tagged               |     |

|      | prefetcher classified with high, medium, or low priority by the different          |     |

|      | predictors                                                                         | 89  |

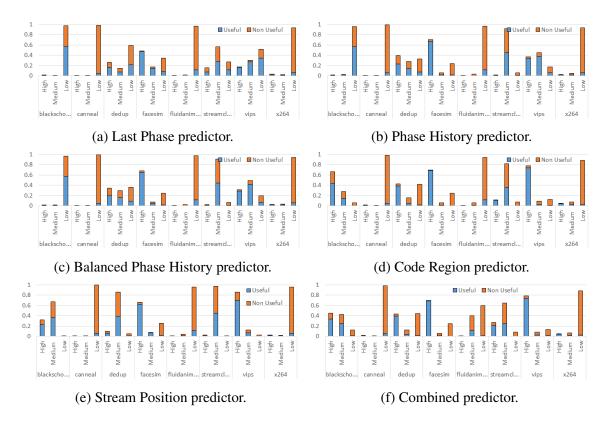

| 4.10 | Results from evaluating the confidence predictors with the RPT as the stride       |     |

|      | prefetcher                                                                         | 90  |

| 4.11 | Percentage of useful and non useful requests generated by the RPT prefetcher       |     |

|      | classified with high, medium, or low priority by the different predictors          | 92  |

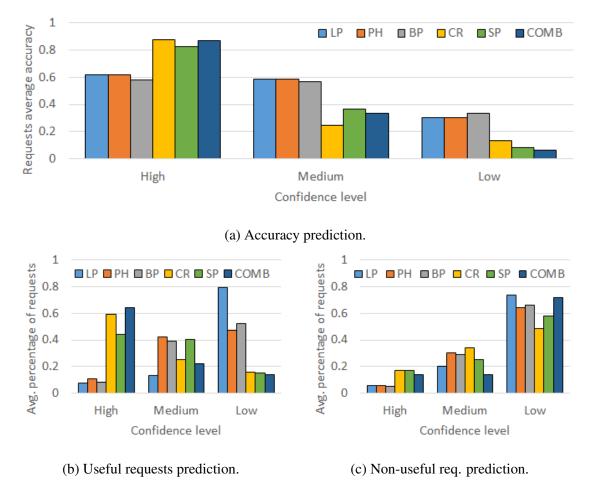

| 4.12 | Results from evaluating the confidence predictors with the GHB as correla-         |     |

|      | tion prefetcher.                                                                   | 93  |

| 4.13 | Percentage of useful and non useful requests generated by the GHB prefetcher       |     |

|      | classified with high, medium, or low priority by the different predictors. $$ . $$ | 94  |

| 5.1  | Implementation of the prioritization in the network interface                      | 102 |

| 5.2  | Block diagram for the hardware implementation of the prioritization and            |     |

|      | filtering technique using the combined confidence predictor                        | 104 |

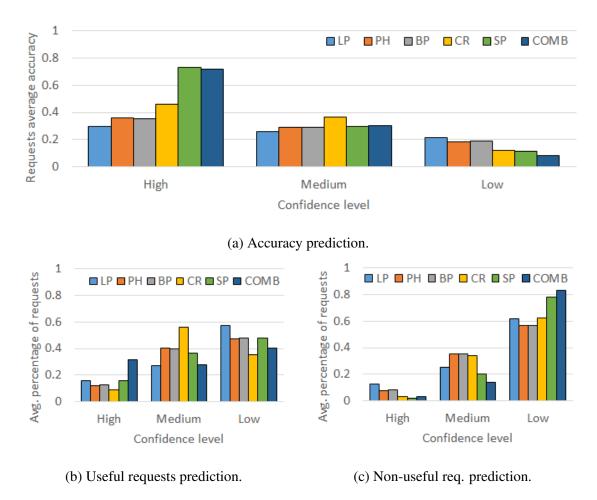

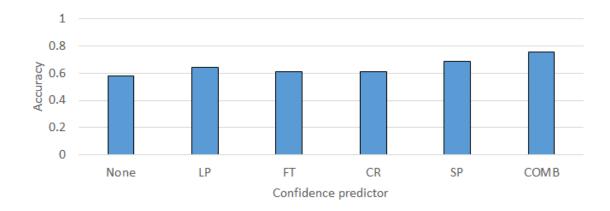

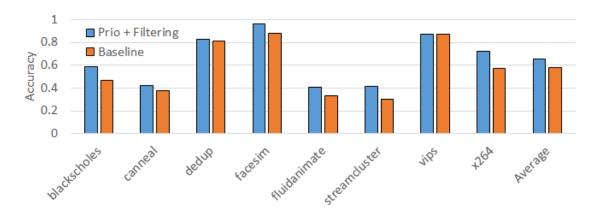

| 5.3  | Accuracy increment estimation after filtering the low confidence requests          | 113 |

| 5.4  | Percentage of regions that change their confidence after the warmup                | 113 |

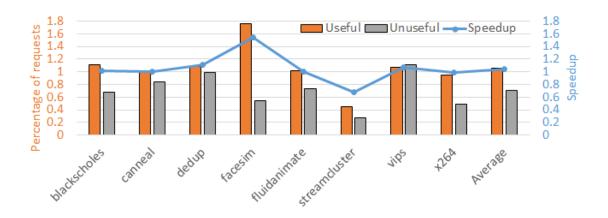

| 5.5  | Results for the filtering technique: Filtered requests vs. IPC speedup             | 114 |

| 5.6  | RPT IPC Speedup after applying prioritization                                      | 115 |

| 5.7  | RPT Request reduction vs. IPC speedup                                              | 116 |

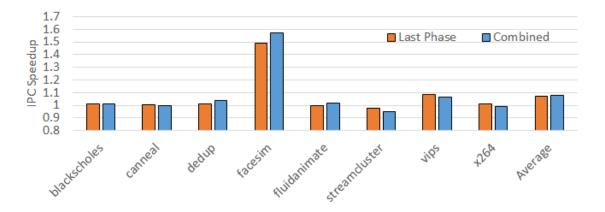

| 5.8  | RPT accuracy increment                                                             | 117 |

| 6.1  | Top: CMP with unified memory hierarchy. Bottom: Tiled CMP architecture             |     |

|      | with distributed and shared memory system                                          | 120 |

| 6.2  | Phases from the prefetcher in a distributed memory system: (1)analysis, (2)        |     |

|      | request generation, and (3) evaluation                                             | 122 |

| 6.3  | A possible distribution of a memory accesses stream: on the left in a unified      |     |

|      | memory and on the right in a distributed and shared memory                         | 123 |

xviii List of figures

| 6.4  | Diagram of the evaluation infrastructure of the pattern detection and the           |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | queue filtering challenges                                                          | 125 |

| 6.5  | Implementation of the useful prefetch. ID: bits to track the issuer of the          |     |

|      | prefetch. U: bit to track if the prefetch is useful or not. P: bit to track if this |     |

|      | has been a prefetch line or not. T00 to TN: accumulators to track the useful        |     |

|      | or unuseful prefetch from each tile                                                 | 126 |

| 6.6  | Pattern detection challenge analysis                                                | 128 |

| 6.7  | Queue filtering challenge analysis                                                  | 129 |

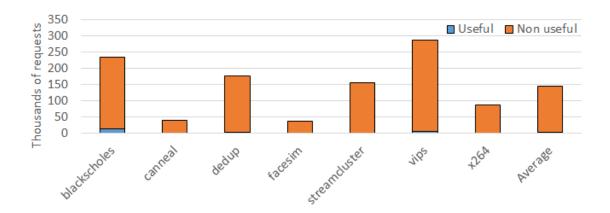

| 6.8  | Dynamic profiling challenge analysis                                                | 130 |

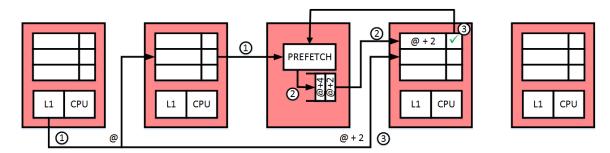

| 6.9  | Phases of the Replication technique: (1) analysis, (2) request generation, and      |     |

|      | (3) evaluation                                                                      | 132 |

| 6.10 | Phases from the prefetcher in a distributed memory system: (1) analysis, (2)        |     |

|      | request generation, and (3) evaluation                                              | 135 |

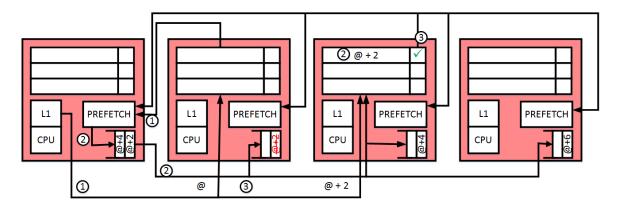

| 6.11 | Phases from the prefetcher in a distributed memory system: (1) analysis, (2)        |     |

|      | request generation, and (3) evaluation                                              | 137 |

## List of tables

| 2.1 | Entries in the reference prediction table                                          |

|-----|------------------------------------------------------------------------------------|

| 2.2 | Requirements for multi-core simulators                                             |

| 3.1 | Stable states of the private cache state machine                                   |

| 3.2 | Stable states of the shared cache state machine                                    |

| 3.3 | Simulation environment specifications                                              |

| 3.4 | Detailed definition of the level of aggressiveness for each prefetch mechanism. 57 |

| 4.1 | Simulation specifications                                                          |

| 5.1 | Example of the warmup process of an entry in the Region Profiler Table 100         |

| 5.2 | Required hardware to calculate the accuracy according to the different thresh-     |

|     | olds. U: Useful, N: Useless                                                        |

| 5.3 | Simulation specifications                                                          |

| 6.1 | Simulator specifications                                                           |

| 6.2 | Consumption of resources by the proposed techniques. N: Number of tiles,           |

|     | uni: Uni-cast message, br: Broadcast message, M: Size of a prefetcher in a         |

|     | tile from the baseline                                                             |

### Chapter 1

### Introduction

Everything begins with an idea.

Earl Nightengale

### 1.1 Motivation

In the last years, processor designs have evolved toward architectures that implement multiple processing cores on a single die, commonly known as chip-multiprocessors or CMPs. Today, multi-core architectures are envisioned as the only way to ensure performance improvements after microprocessors designers have acknowledged that it is no longer efficient to rely on higher clock rates and/or exploiting greater levels of instruction-level parallelism (ILP). In this way, most of the industry would agree that multi-core is the way to go further and those designs with tens of cores on the die will be a reality in the near future. Additionally, future many-core CMPs with several tens (or even hundreds) of processor cores will be probably designed as arrays of replicated tiles connected over an on-chip switched direct network [89]. These tiled architectures have been claimed to provide a scalable solution for managing the design complexity, and effectively using the resources available in advanced VLSI technologies. Maybe, the best known examples of a tiled CMP architecture today from the main HPC developers are the Intel Xeon Phi [32], the Nvidia Tesla [50], the Tilera TILE64 [5], or the AMD FireStream [2] prototypes.

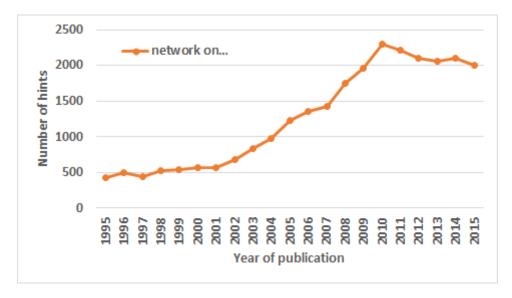

However, one of the greatest roadblocks to provide high performance in such tiled CMP architectures is the high cost of on-chip communication between cores [30]. This on-chip communication subsystem is what we know as the Network on Chip (NoC) [69]. A sign that suggests that this topic is envisioned as one of the current challenges by the research community is that in the last 20 years it has increased the number of publications. Moreover,

2 Introduction

in the last 5 years it growing has stalled but it is still an active topic in the main conferences. (see Figure 1.1).

Fig. 1.1 Search hits for "network-on-chip" in IEEE Xplore archive.

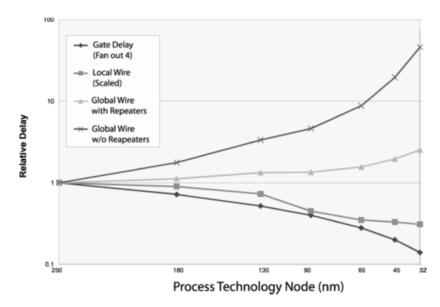

One of the reasons why the NoC are becoming a bottleneck as the number of cores increases is the bad scalability of global communications as process technology advances. Figure 1.2 shows what it was outlined before: the smaller the technology node, the lower the gate delay and the local wire delay (delay from the wires in the same core). However, the global wire delay (delay from the communication between cores) increases exponentially. Although some improvements, such as adding repeaters, reduce the latency, they do not change the exponential trend. This issue is similar to the one related to the different scalability of memory access time and core processing speed [8], which is a problem in both, single and multicore processors.

One way to handle the increasing memory latency due to wire delay and memory access time is to use latency hiding techniques like prefetching, which eliminates some cache misses and/or overlaps the latencies of others. These mechanisms try to predict which data the processor is going to require and bring it to the nearest cache level before it is demanded by the application. Furthermore, prefetching is a technique which is implemented in most of the commercial processors [48] [76] [72] [29]. Each of these processors implements several techniques, however, the details of most of them are secret. An example is the case of the Intel Nehalem processor. In [48] they explain the type of prefetcher implemented in both, first and second cache level, but they do not provide implementation details of any of them.

Apart from providing a good performance in terms of execution time (speedup), an ideal prefetching algorithm should satisfy, among others, other important property: to produce a

1.1 Motivation 3

Fig. 1.2 Projected relative delay for local and global wires and for gates in technologies of the near future [8].

minimum increase of traffic in the memory interconnection. An increase in memory traffic entails higher power consumption and a higher degree of contention in the interconnection network. Note that prefetching generates a potentially high amount of memory requests in order to bring to the cores the data that they would require in advance. As an overall effect, the number of memory requests are in most of the cases going to be higher than in a system without prefetching. This is especially true if we are in a multi-core system because it increases on-chip communication since coherence between the L1 caches of the tiled CMP must be ensured. An increase in the congestion of the network will most probably increase the latency of not only prefetching requests but also regular memory operations [66]. Moreover, although, to the best of our knowledge, there is no specific literature in this regard, it is expected to be a straight relation between the overhead of prefetch operations in the network and memory system and the increment of dissipated power.

If the prefetcher would be perfect and all the prefetch requests would brought only the data blocks that are going to be used by the core, the core would not need to fetch them. This would entail that the prefetch traffic would overlap the traffic from the core demand operations and the same would happen regarding the power consumption. However, depending on the accuracy of the prefetcher for a given application, a certain portion of the data prefetched is not going to be actually used by the cores. Apart from the aforementioned increase in traffic and congestion, the unnecessarily prefetched block lines can displace beforehand other block lines that are going to be required after a short period of time and that have to be fetched again. This may negatively affect the performance of the application, diminishing

4 Introduction

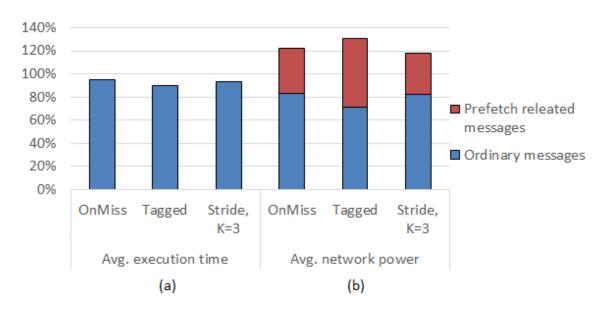

the improvement provided by prefetching in the worst case even degrading the performance compared with a system without prefetching. Nevertheless, it is very difficult for a prefetcher to predict which data block will be needed by its core. In order to increase the number of prefetching operations issue in time (and increase the speedup of the system), the prefetchers usually generates several prefetch requests each time it is triggered (to have a wider range of success), and this decreases the accuracy of the technique. Note that hardware prefetchers in commodity processors can be very aggressive, sometimes prefetching more than twice the data required for an application [38], [37]. Figure 1.3 shows some performance numbers obtained in [21] that also supports this argument. For three prefetching alternatives (one block lookahead [24], on miss prefetch [18], and tagged prefetcher [24]), the average improvement in terms of execution time (Figure 1.3.a) and the increase in the on-chip network power consumption due to the extra communication that prefetching entails for the parallel scientific applications considered in the study (Figure 1.3.b) is shown. As it can be observed, increases over 20% in the on-chip network power consumption are obtained for some of the prefetching techniques.

A lot of research has been done on proposing new prefetch techniques and incrementing their performance in single-core processors [64] [79]. However, research in the multicore environment has received much more less attention. Therefore, in this thesis, we will put a special emphasis on CMP environments, specifically tiled architectures, and on a key aspect of this kind of systems, the NoC. Moreover, we do not pretend to propose new prefetching engines for multicore but we will propose techniques valid for any prefetching mechanism that will improve the overall performance of the prefetching in CMP systems as a whole.

### 1.2 Objectives

Derived from the motivation previously exposed, we define the main general objective of this thesis as developing a better understanding of the implications of prefetching in tiled CMP systems and providing novel proposals to improve the performance in term of power and performance efficiency of prefetching mechanisms in this kind of systems. We have split this general objective in four secondary objectives that have guided all the work in this thesis:

- To characterize the NoC behavior of prefetching in tiled CMP platforms.

- To enhance the profiling of prefetching statistics used in dynamic management techniques to better handle prefetching traffic.

- To propose novel management techniques to improve the performance of prefetching techniques.

1.2 Objectives 5

Fig. 1.3 (a) Normalized execution time and (b) network power consumption for a 16-core CMP with different prefetching mechanisms.

• To identify the challenges for prefetching in shared distributed memory systems and propose directions to address them.

In the following, we elaborate on what we pretend to achieve with each secondary objective, the specific motivation that leads each of them, and a first overview of the work that we have done to fulfill them.

### Characterize the NoC behavior of prefetching in tiled CMP platforms

The aim of this objective is to focus on the behavior of the prefetching traffic in one of the main shared resources, as it is the NoC. Specifically, we want to emphasize the importance of taking into account the underlying NoC on the performance achieved by the prefetching mechanisms. To do this, we will analyze the traffic that is traversing the interconnect, identifying and characterizing the prefetching requests. With this analysis we plan to quantify the impact of the prefetching requests in the congestion of the interconnect.

Furthermore, implementing a simulation infrastructure able to simulate the prefetching traffic in the NoC will not be an easy issue. The reason for that is that we need a simulator which is able to simulate the CPU and the NoC in order to simulate the prefetching traffic in the NoC. The CPU generates the requests, that the prefetcher analyzes and injects them into the NoC. Therefore, a NoC simulator will not be able to generate prefetch requests, and a CPU simulator will not be able to simulate the NoC. There are several open-source

6 Introduction

simulators that are able to work in these two areas. However, they do not have a prefetching infrastructure implemented. For this reason, another important point of this objective will be to adapt a current open-source simulator to integrate the prefetching in its simulation infrastructure.

## Enhance the prefetching statistics profiling used in dynamic management techniques to better handle prefetching traffic

A better management of the prefetch requests could help in reducing or minimizing the effect from congestion on the interconnect and in general in the memory system. Ideally, to successfully manage prefetching requests in the system dynamically, we would have to know the impact of each of these prefetch requests in the system as soon and accurately as possible. Thus, predicting the impact of a prefetch request in the system is key. One of the most important things for making accurate predictions is the way that these requests are profiled.

For this reason, the idea of this objective is to enhance the strategy to collect the dynamic profiling information to help techniques that manage the prefetch generation. Therefore, we plan to develop a new mechanism to dynamically collect the profiling information from the prefetch requests and be able to generate accurate predictions of the usefulness of each potential request that may help decide the impact of the requests in the whole system.

## Propose novel management techniques to improve the performance of prefetching techniques

The idea of this objective is to use the profiling techniques proposed in the previous objective to improve the dynamic management of prefetching requests, developing new techniques that reduce the congestion of the interconnect without losing performance, or losing the minimum performance.

Specifically, we plan to work in a technique that gives a different treatment to the requests according to its predicted impact in the system. Actually, in case the request is predicted with a negative impact, we plan to discard it. Otherwise, if the request is predicted to have a good impact in the system, it will have a higher priority treatment when accessing the shared resources.

## Identify the challenges for prefetching in shared distributed memory systems and propose directions to address them

From the best of our knowledge, in all the prefetching studies for CMPs, the prefetcher works in the private and/or monolithic caches, but not in the shared and distributed ones, which are typical in the upper cache levels of tiled architectures. The reason is probably that implementing prefetching in shared distributed memories face challenges that, as far as we know, have not been properly addressed or even discussed in the literature.

For this reason, the aim of this objective is to identify the challenges of prefetching in distributed and shared memory systems and quantify its effect in the performance of the prefetchers. Moreover, we plan to propose some directions in how this challenges could be addressed.

### 1.3 Thesis organization

The remaining of this thesis is organized as follows: in Chapter 2, we introduce the more important concepts related to prefetching, networks on chip, techniques from the state of the art that manage the prefetcher generated requests or the traffic in the network on chip, and some information on multiprocessor simulators. After this related work, we continue with the contributions of this thesis that are detailed in the next four chapters. Chapter 3 shows our first contribution, where we explain our experimental framework, the modifications that we have introduced to the simulator and experimental results that shows that the traffic injected by the prefetcher to the network on chip is not negligible. There are several techniques in the state of the art that employ dynamic profiling information to offer a better management of prefetching. In Chapter 4, we analyze and evaluate several approaches to get information on the accuracy of prefetching requests and propose a novel confidence predictor for dynamic management techniques. In Chapter 5, we use this new predictor as the base for enhancing two techniques from the state of the art and propose novel management mechanisms. In Chapter 6, we focus on the challenges of prefetching on shared and distributed caches, typical from tiled architectures. We identify these challenges and propose some directions on how to solve them. Finally, in Chapter 7, we conclude the thesis by evaluating the objectives presented in this chapter and giving some ideas for future work.

### Chapter 2

### State of the Art

Learn the rules like a pro so you can break them like an artist.

Pablo Picasso

### 2.1 Introduction

In this chapter, we introduce the most important concepts related to prefetching on networks on chip that will be referenced along this thesis document. We will introduce the prefetching strategies as well as the related work done in techniques that dynamically improves its performance and the current state of the art on simulators that can simulate prefetch mechanisms.

This chapter is organized as follows: Section 2.2 introduces the main concepts about prefetching and the related work on this topic. Section 2.3 is about the networks on chip. What they are and what are the main contributions in this topic. Section 2.4 shows the main dynamic management techniques for prefetching requests that are presented in the literature. Finally, Section 2.5 introduces the main open-source simulators that currently are available in the literature to work in CMP.

### 2.2 Prefetching basic concepts

The memory hierarchy is one of the most important elements in the performance of nowadays processors. In order to reduce the latency of memory accesses, there are a lot of different ways to improve the memory hierarchy. One of the ways is make use of prefetching mechanisms.

10 State of the Art

These mechanisms try to predict which data the processor is going to need, and take it to the nearest cache level before it is demanded by the application.

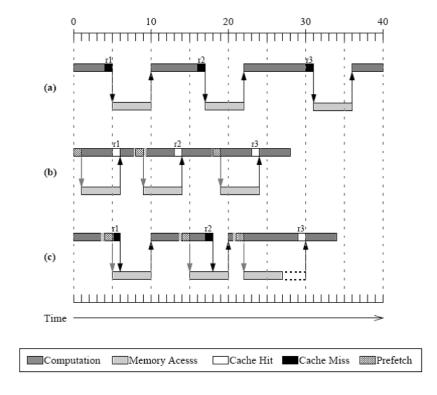

In Figure 2.1, we can see the behavior of different prefetching methods. In this figure, we can see a time chart with 3 different cases. In each case, we can see the regular computation along the time, in this computation there are some memory accesses, that some of them can become a memory miss. Specifically, in Figure 2.1.a we can see the behavior of an execution where there is no prefetching, and whenever there is a memory access the processor has to idle until the access is finished. We can see the idyllic behavior of a prefetcher in Figure 2.1.b, where the prefetcher detects that some data is going to be required and generates a memory access that is processed in parallel with the processor computation and, in the moment that the processor needs that data, it is already in the cache module. However, nowadays prefetchers are working as in Figure 2.1.c because in very few cases is possible to exactly predict what a program is going to do enough cycles before to ask for the data in the correct moment.

Fig. 2.1 Execution diagram assuming a) no prefetching, b) perfect prefetching, and c) degraded prefetching.

There are two main concerns that a good prefetcher must take into account. What to prefetch and when to prefetch in order to get the data timely.

If we do not have these concepts in mind, the prefetcher is going to have an unwanted behavior, so there are some issues we have to consider in order to avoid them. For instance, if the prefetch unit is taking wrong data in the cache module, could replace useful data, or if the data that the prefetch unit is looking for, it is already in the cache module, the prefetcher is going to waste power.

According to the scheme employed, prefetchers can be classified into two main categories: (1) software prefetchers, whose main components are composed of software with some hardware support [87], [46]; and, (2) hardware prefetchers, those for which pure hardware techniques are employed [68], [79]. In this thesis, we have focused our investigations on hardware prefetchers. However, some of the techniques presented in this thesis can be applied to both, hardware or software prefetchers. For this reason, the state of the art information will be focused mainly in the second group, but a brief introduction to software prefetchers is of interest in order to provide a global view of all the prefetching techniques. Although software prefetching falls outside the scope of this thesis, extending the research described here by examining these software prefetching algorithms would be of interest in the future.

### • Software prefetching

Prefetching operations are special instructions that are incorporated by a layer of code generation software (typically the compiler) into the binary. The aim of these instructions is to try to bring the data that is expected to be needed in the near future into a nearer level of memory. These operations are injected to the binary in accordance with the specific prefetching algorithm.

The majority of software prefetchers analyzes the code during the compiling time and then injects the prefetching operations into the locations that the algorithm has identified as providing the best performance.

The injected prefetching instruction must not stall the system if a miss occurs (i.e. the data is not present in the first level cache), as it must be dealt with in parallel with the execution of the program. For this reason, lock-free caches are required [40].

One of the best well know software prefetching studies is [58] [57] [56]. In this study, the authors present a technique where the compiler injects prefetching requests. The technique analyses the code, and through complex mathematical operations tries to predict the behavior of the cache and when a memory request will miss. Therefore, it injects the request some instructions before in order to avoid the miss penalty.

More recently, [67] and [35] published techniques that uses helper threads through the idle processors to execute the prefetching requests and avoid the instruction overheads.

12 State of the Art

This way, the main thread is assisted by the complementary threads and the prefetcher can be more aggressive without injecting overhead.

#### Hardware prefetching

The vast majority of hardware prefetching mechanisms are based on hardware structures that store the recent memory-related activity of the processor. Using this information and dedicated hardware, the prefetcher predicts which data the processor is going to request and physically injects the prefetch requests in the memory hierarchy when it is idle.

The main advantages respect the software prefetching is that the hardware prefetcher knows about the hardware configuration of the memory and it does not inject any instruction overhead. However, making this predictions implies extra hardware, extra power, and extra time. For this reason, software prefetcher is able to do more complex predictions with higher processing time and more accuracy. But hardware prefetcher, can make faster predictions with lower penalty. Thus, as we have already said, in the rest of this thesis we will focus on hardware prefetching.

### 2.2.1 Prefetchers in current processors

Most current commercial processors implement several prefetching techniques, however, the details of most of them are secret. An example is the case of the Intel Nehalem processor. In [48] they explain that the Intel Core i7 processor has a four component hardware prefetcher. Two components associated with the second level cache and two components associated with the first level data cache. The two components of the second cache level hardware prefetcher are similar to those in the Pentium 4 and Intel Core processors [9]. There is a "streaming" component that looks for multiple accesses in a local address window as a trigger and an adjacency component that causes two lines to be fetched instead of one with each triggering of the "streaming" component. The L1 data cache prefetcher is similar to the L1 data cache prefetcher from the Core processors. It has another "streaming" component and a "stride" component that detects constant stride accesses at individual instruction pointers.

Nevertheless, the companies do not provide specific details on the heuristic used to generate new prefetchers. As we have seen, the provided information is always about the type of memory access patterns that they try to detect. The previously cited document talks about two kind of patterns that the Intel Core i7 tries to predict. These are the stream and stride patterns. Apart from this two patterns, the prefetchers can predict also analyzing the correlation between the accesses. Thus, as we will see with more details in the next section,

the prefetchers can be classified according to the pattern that they try to predict in three groups: *stream*, *stride*, and *correlation* prefetchers.

### 2.2.2 Implemented prefetchers

In this section we describe the three main kind of prefetchers according to its strategy to detect patterns. For our studies, we have selected one specific prefetcher from each group. These selected prefetchers are the ones that has been used along this thesis. We have selected these prefetchers because the literature seems to indicate that these mechanisms are the most representative in their categories [64].

#### Sequential prefetchers and the Tagged prefetcher

Most (but not all) prefetching schemes are designed to fetch data from main memory into the processor cache in units of cache blocks. It should be noted, however, that multiple word cache blocks are themselves a form of data prefetching. By grouping consecutive memory words into single units, caches exploit the principle of spatial locality [73] to implicitly prefetch data that is likely to be referenced in the near future.

Sequential prefetching can take advantage of spatial locality without introducing some of the problems associated with large cache blocks. The simplest sequential prefetching schemes are variations upon the one block look ahead (OBL) [73] approach which initiates a prefetch for block b+1 when block b is accessed. This approach differs from simply doubling the block size in that the prefetched blocks are treated separately with regard to the cache replacement and coherency policies. For example, a large block may contain one word which is frequently referenced and several other words which are not in use. Assuming an LRU replacement policy [73], the entire block will be retained even though only a portion of the block's data is in use. If this large block were replaced with two smaller blocks, one of them could be evicted to make room for more active data. Similarly, the use of smaller cache blocks reduces the probability that false sharing occurs.

OBL implementations differ depending on what type of access to block b initiates the prefetch of b+1. In the following, we are going to discuss about the prefetch on miss and tagged prefetch algorithms. The prefetch on miss algorithm simply initiates a prefetch for block b+1 whenever an access for block b results in a cache miss. If b+1 is already cached,

<sup>&</sup>lt;sup>1</sup>False sharing: false sharing occurs when a process attempts to periodically access data that will never be modified by another process, but that data shares a cache block with data that is modified, the caching protocol may force the first process to reload the whole unit despite the lack of logical necessity. The caching system is unaware of activity within this block and forces the first process to bear the caching system overhead required by true shared access of the resource.

State of the Art

no memory access is initiated. On the other hand, the tagged prefetch algorithm associates a tag bit with every memory block. This bit is used to detect when a block is demand-fetched or a prefetched block is referenced for the first time. In either of these cases, the next sequential block is fetched.

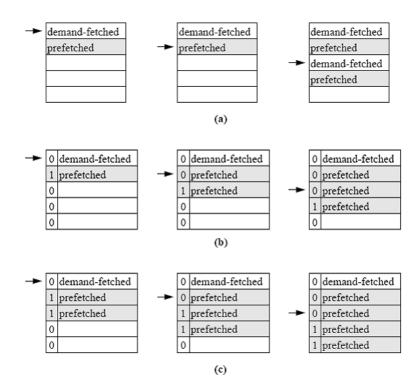

Smith found that tagged prefetching reduced cache miss ratios in a unified (both instruction and data) cache by between 50% and 90% for a set of trace-driven simulations. Prefetch on miss was less than half as effective as tagged prefetching in reducing miss ratios. The reason prefetch on miss is less effective is illustrated in Figure 2.2, where the behavior of each algorithm when accessing three contiguous blocks is shown. Here, it can be seen that a strictly sequential access pattern will result in a cache miss for every other cache block when the prefetch on miss algorithm is used but this same access pattern results in only one cache miss when employing a tagged prefetch algorithm. However, as we have said, it have to be an strictly sequential access pattern, other way the tagged prefetcher will send more useless prefetching operations than the other ones.

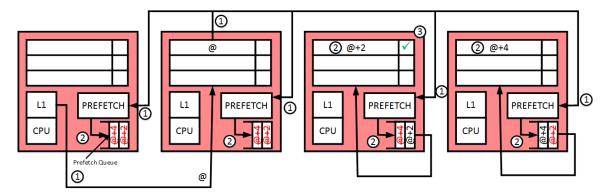

Fig. 2.2 Three forms of sequential prefetching: a) Prefetch on miss, b) tagged prefetch and c) tagged prefetch with K = 2.

Note that one shortcoming of the OBL schemes is that the prefetch may not be initiated far enough in advance of the actual use to avoid a processor memory stall. A sequential access stream resulting from a tight loop, for example, may not allow sufficient time between

the use of blocks b and b+1 to completely hide the memory latency. To solve this problem, it is possible to increase the number of blocks prefetched after a demand fetch from one to K, where K is known as aggressiveness. Prefetching K > 1 subsequent blocks aids the memory system in staying ahead of fast processor requests for sequential data blocks. As each prefetched block, b, is accessed for the first time, the cache is interrogated to check if blocks b+1, ... b+K are present in the cache and, if not, the missing blocks are fetched from memory. Note that when K = 1 this scheme is identical to tagged prefetching.

Although increasing the degree of prefetching reduces miss rates in sections of code that show a high degree of spatial locality, additional traffic and cache pollution are generated by sequential prefetching during program phases that show little spatial locality. This overhead tends to make this approach unfeasible for values of K larger than one as shown in [65].

Simulations of a shared memory multiprocessor found that adaptive prefetching could achieve appreciable reductions in cache miss ratios over tagged prefetching. However, simulated run-time comparisons showed only slight differences between the two schemes. The lower miss ratio of adaptive sequential prefetching was found to be partially nullified by the associated overhead of increased memory traffic and contention[77].

Sequential prefetching requires no changes to existing executables and can be implemented with relatively simple hardware. Compared to nowadays sequential prefetching policies, tagged prefetching appears to offer both simplicity and performance. Compared to software-initiated prefetching, sequential prefetching will tend to generate more unnecessary prefetch demands. Moreover, non-sequential access patterns, such as scalar references or array accesses with large strides, will result in unnecessary prefetch requests because they do not exhibit the spatial locality upon which sequential prefetching is based. To enable prefetching of strided and other irregular data access patterns, several more elaborate hardware prefetching techniques have been proposed, such as the ones explained in the next point.

#### Stride prefetchers and the Reference Prediction Table prefetcher

The idea for this mechanism is to identify a strided array referencing pattern, the simplest way to do it is to explicitly declare when such a pattern occurs within the program and then pass this information to the hardware. This is possible when programs are explicitly vectorized so that computation is described as a series of vector and matrix operations by the programmer, as is commonly done when programming machines which contain vector processors [28]. Given such a program, array address and stride data can be passed to prefetch logic which may then use this information to calculate prefetch addresses. This is what was in mind of Fu and Patel, in their scheme [23], a miss to an address as the result from a vector load or store

16 State of the Art

instruction with a stride of  $\Delta$  prompts the prefetch hardware to issue fetches for addresses  $a, a + \Delta, a + 2 * \Delta, ..., a + K * \Delta$ , where K is again the degree of prefetching. Unlike sequential prefetching techniques, Fu and Patel's approach was found to be effective for values of K up to 32 due to the more informed prefetches that vector stride information affords.

When such high-level information cannot be supplied by the programmer, prefetch opportunities can be detected by hardware that monitors the processor's instruction stream or addressing patterns. Lee, et al.[47] examined the possibility of looking ahead in the instruction stream to find memory references for which prefetches might be dispatched. This approach requires that instructions be brought into a buffer and decoded early so that the operand addresses may be calculated for data prefetching. Instruction look ahead is allowed to pass beyond branches using a branch prediction scheme so that some prefetches will be issued speculatively. This speculation results in some unnecessary prefetches if the branch prediction is incorrect, in which case the buffer holding the speculatively loaded instructions must be flushed. Although this scheme allows for prefetching of arbitrary data access patterns, the prefetch window is limited by the depth of the decoded instruction buffer.

Several techniques have been proposed that employ special logic to monitor the processor's address referencing pattern to detect constant stride array references originating from looping structures [3] [23]. This is accomplished by comparing successive addresses used by load or store instructions. The scheme proposed by Chen and Baer [11] is perhaps one of the the most aggressive thus far. To illustrate its design, assume a memory instruction,  $m_i$ , that references addresses  $a_1$ ,  $a_2$ , and  $a_3$  during three successive loop iterations. A prefetch for  $m_i$  will be initiated if

$$(a_2-a_1)=\Delta\neq 0$$

where  $\Delta$  is now assumed to be the stride of a series of array accesses. The first prefetch address will then be  $A_3 = a_2 + \Delta$ , where  $A_3$  is the predicted value of the observed address,  $a_3$ . Prefetching continues in this way until the equality  $A_n == a_n$  no longer holds true.

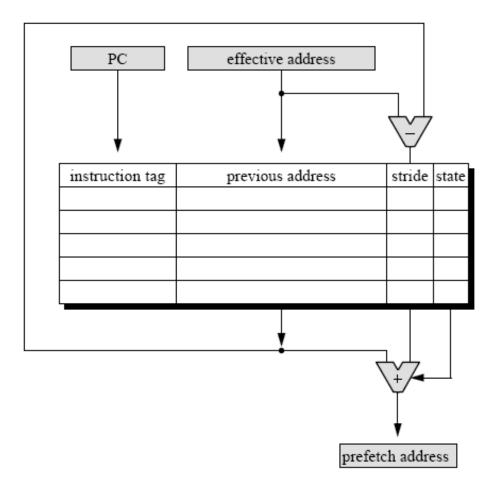

Note that this approach requires the previous address used by a memory instruction to be stored along with the last detected stride, if any. Recording the reference histories of every memory instruction in the program is clearly impossible. Instead, a separate cache called the reference prediction table (RPT) holds this information for only the most recently used memory instructions.

The organization of the RPT is given in Figure 2.3. Table entries contain the address of the memory instruction, the previous address accessed by this instruction, a stride value for those entries which have established a stride, and a state field which records the entry's current state.

Fig. 2.3 The organization of the reference prediction table.

The RPT improves upon sequential policies by correctly handling strided array references. However, the RPT still limits the prefetch distance to one loop iteration. To remedy this shortcoming, a distance field may be added to the RPT which specifies the prefetch distance explicitly. Prefetch addresses would then be calculated as

$$effective address + (stride * distance)$$

The addition of the distance field requires some method of establishing its value for a given RPT entry. To calculate an appropriate value, Chen and Baer decouple the maintenance of the RPT from its use as a prefetch engine. The RPT entries are maintained under the direction of the Program Counter (PC) as described above but prefetches are initiated separately by a pseudo program counter, called the look-ahead program counter (LA-PC) that is allowed to precede the PC. The difference between the PC and LA-PC is then the prefetch distance,  $\delta$ .

This prefetch mechanism consists of a table of RPT\_SIZE entries indexed by the PC. As we have already said, each entry in the table has the structure showed in Table 2.1.

| Instruction Tag                                     | Previous address | stride | state |

|-----------------------------------------------------|------------------|--------|-------|

| Table 2.1 Entries in the reference prediction table |                  |        |       |

When memory instruction  $m_i$  is executed for the first time, an entry for it is made in the RPT with the state set to initial, what means that no prefetching is yet initiated for this instruction. If  $m_i$  is executed again before its RPT entry has been evicted, a stride value is calculated by subtracting the previous address stored in the RPT from the current effective address.

#### **Correlation prefetching. Global History Buffer**

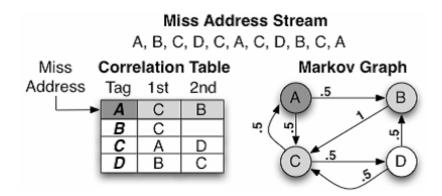

The correlation prefetching techniques make use of a history table to record consecutive address pairs. When a cache miss occurs, the miss address indexes the correlation table (see Figure 2.4). Each entry in the correlation table holds a list of addresses that have immediately followed the current miss address in the past. When a table entry is accessed, the member(s) of its address list are prefetched, with the most recent miss address first. The left side of Figure 2.4 illustrates the state of the correlation table after processing the miss address stream shown at the top of the figure.

Fig. 2.4 Markov prefetching.

There are two main correlation prefetching techniques, both of them use an algorithm to get the correlation between cache misses, and then they use another algorithm to launch the prefetching operations. This second algorithm is exactly the same in both mechanisms. What makes them different is the way to calculate the correlation. The first one is the Markov Prefetching technique and the second one is a generalization of the Markov Prefetching and

it is called Distance Prefetching. In order to have a good point of view for the correlation prefetching methods, we are going to introduce these two mechanisms, and then how they are implemented making use of a Global History Buffer (GHB) [59].

Markov Prefetching [34]: The Markov prefetching mechanism models the miss address stream as a Markov graph – informally, a probabilistic state machine. Each node in the Markov graph is an address and the arcs between nodes are labeled with the probabilities that the arc's source node address will be immediately followed by the target node address. Each entry in the correlation table represents a node in an associated Markov graph, and its list of memory addresses represents arcs with the highest probabilities. Hence, the table maintains only a very crude approximation to the actual Markov probabilities. The right side of Figure 2.4 is the Markov transition graph that corresponds to the example miss address stream.

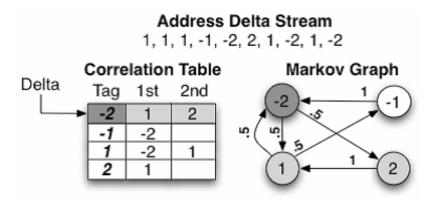

Distance Prefetching [36]: The Distance prefetching mechanism is a generalization of Markov Prefetching. Originally, Distance Prefetching was proposed for prefetching the translation lookaside buffer (TLB) [73] entries, but the method is easily adapted to prefetching cache lines. In this adaptation, Distance Prefetching uses the distance between two consecutive global miss addresses, an address delta, to index the correlation table. Each correlation table entry holds a list of deltas that have followed the entry's delta in the past. Figure 2.5 illustrates the address delta stream for the miss address stream in the previous example (Figure 2.4), and the state of the correlation table after processing the delta stream. Distance Prefetching is considered a generalization of Markov Prefetching because one delta correlation can represent many miss address correlations. By generalizing Markov Prefetching, Distance Prefetching is capable of prefetching most of the reference patterns that Markov Prefetching can. Plus, with the data it has available, it can also detect and prefetch delta access patterns that occur in the global miss address stream.

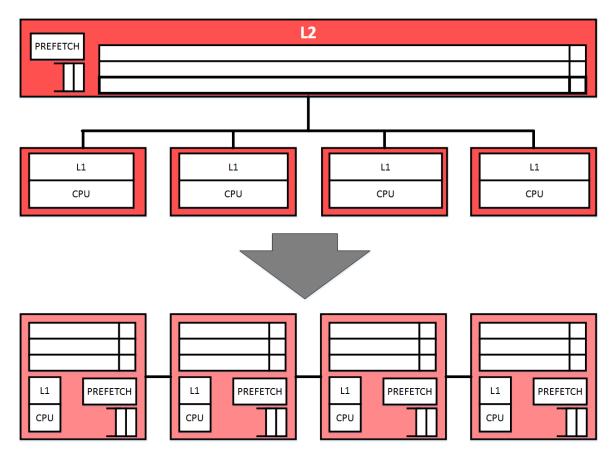

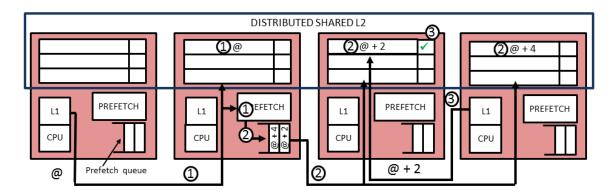

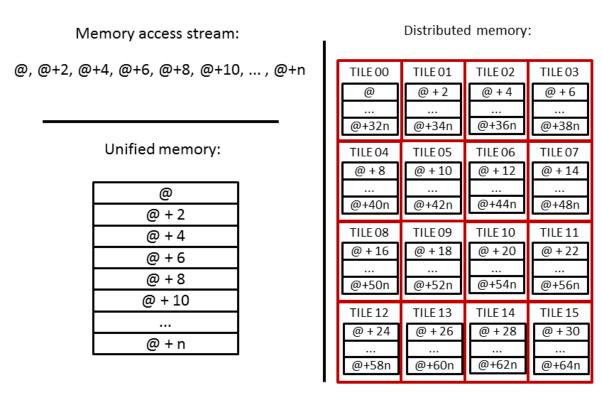

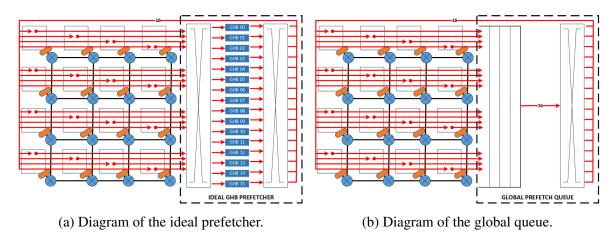

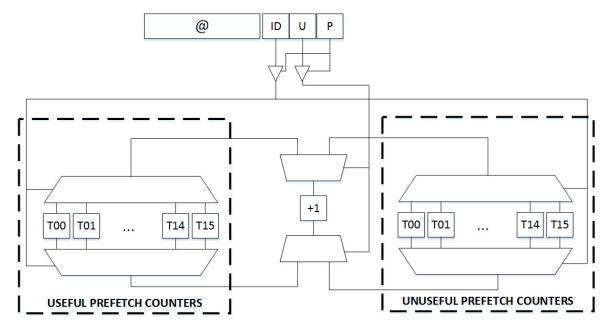

Fig. 2.5 Distance Prefetching.