### Self-healing and secure low-power memory systems

### Mădălin Neagu

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) le repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (<a href="framing">framing</a>). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="framing">framing</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository **UPCommons** (http://upcommons.upc.edu/tesis) and the cooperative repository TDX (http://www.tdx.cat/?localeattribute=en) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# SELF-HEALING AND SECURE LOW-POWER MEMORY SYSTEMS

Author: Mădălin NEAGU Supervisors: Joan FIGUERAS Salvador MANICH

September 2017

## SELF-HEALING AND SECURE LOW-POWER MEMORY SYSTEMS

Tesi doctoral presentada per a l'obtenció del títol de Doctor per la Universitat Politècnica de Catalunya, dins el Programa de Doctorat en Enginyeria Electrònic

Author: Mădălin NEAGU Supervisors:

Joan FIGUERAS

Salvador MANICH

Barcelona, September 2017

### **Abstract**

Memory systems store critical information in any digital system, thus they are susceptible to transient errors and are the focus of various types of attacks. It is crucial for a memory system to keep the information as accurate as possible. There is a need to design, implement and test systems capable of handling errors by themselves, thus, to run autonomously. Self-healing capabilities for memory systems translates into error detecting and correcting codes and replacing/replicating methods of memory elements. Security and data privacy is difficult to implement in memory systems, due to the overwhelming variety of attacks. This thesis proposes strategies against specific attacks that can occur in memory systems. The self-healing methodology and the security solutions are evaluated from varied perspectives: performance, area and delay overhead, and power consumption.

*Keywords*— error detection, error correction, memory systems, data scrambling, cache memories, side-channel attack, simple and differential power analysis

# **Prologue**

The main objective of this thesis is to bring new contributions to the self-healing and secure systems domain. In particular, to develop a self-healing technique for memory systems and to increase security of memory systems, techniques which favor low-power consumption. In order to achieve the main objective, three major research objectives were proposed: design of an error detection and correction scheme for errors that occur in memory systems and integrate them in a memory system, design techniques to increase the security and data privacy of memory systems against different types of attacks and to combine the previous two into a single solution, in order to achieve a self-healing and secure low-power memory system. The low-power aspect of the proposed solutions and techniques is evaluated during design stage and afterwards through simulation. Also, the architectures are evaluated from several other points of view, such as error detecting and correcting performance, area and delay overhead, and security efficiency.

I want to thank all the people who have helped and supported this doctoral thesis. I would like to express my sincere gratitude to prof. Salvador Manich for introducing me to the security domain, for the continuous support of my Ph.D study and related research, for his patience, motivation and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I also want to thank prof. Joan Figueras for indicating a research direction and for stimulating me during the doctoral program and, last but not least, I want to thank prof. Liviu Miclea for the support and encouragement.

I would like to thank my family, especially my wife and parents for supporting me spiritually throughout writing this thesis and my life in general.

This PhD thesis has been partially sponsored by the Spanish government project TEC2013-41209-P.

# **Contents**

| 1 | Intr | roduction |                                                         |    |  |

|---|------|-----------|---------------------------------------------------------|----|--|

|   | 1.1  | Contex    | κt                                                      | 1  |  |

|   | 1.2  | State o   | of the art                                              | 2  |  |

|   |      | 1.2.1     | Motivation                                              | 2  |  |

|   |      | 1.2.2     | Introduction                                            | 4  |  |

|   |      | 1.2.3     | The Self-Healing concept                                | 8  |  |

|   |      | 1.2.4     | Memory systems                                          | 9  |  |

|   |      | 1.2.5     | Low-power systems                                       | 10 |  |

|   |      | 1.2.6     | Security in memory systems                              | 12 |  |

|   | 1.3  | Object    | ives                                                    | 13 |  |

|   | 1.4  | Structu   | ıre                                                     | 15 |  |

|   |      |           |                                                         |    |  |

| 2 | Unio | direction | nal eDLC                                                | 17 |  |

|   | 2.1  | Introdu   | uction                                                  | 17 |  |

|   | 2.2  | Motiva    | ation                                                   | 18 |  |

|   | 2.3  | Theore    | etical background                                       | 19 |  |

|   |      | 2.3.1     | Memory systems                                          | 20 |  |

|   |      | 2.3.2     | Sources of errors in SRAM and DRAM memories             | 29 |  |

|   |      | 2.3.3     | Self-healing memory systems through error detection and |    |  |

|   |      |           | correction schemes                                      | 32 |  |

|   | 2.4  | Propos    | sed solution                                            | 46 |  |

|   |      | 2.4.1     | Modified Berger codes                                   | 46 |  |

|   |      | 2.4.2     | Coding schemes                                          | 49 |  |

|   |      | 2.4.3     | Error localization                                      | 52 |  |

|   |      | 2.4.4     | Error correction                                        | 58 |  |

|   |      | 2.4.5     | Error escapes                                           | 59 |  |

|   | 2.5  | Implen    | mentation                                               | 60 |  |

|   |      | 2.5.1     | Cadence implementation                                  | 60 |  |

viii CONTENTS

|   |      | 2.5.2          |                                                      | 61         |

|---|------|----------------|------------------------------------------------------|------------|

|   | 2.6  | Evneri         | systems                                              | 68         |

|   | 2.0  | 2.6.1          | Code delay                                           | 72         |

|   |      | 2.6.2          | Code redundancy                                      | 72         |

|   |      | 2.6.3          | Error localization ambiguity                         | 73         |

|   |      | 2.6.4          | Error correction                                     | 73         |

|   |      | 2.6.5          | Error escapes                                        | 74         |

|   |      | 2.6.6          | Area of the code generator and memory resources      | 75         |

|   |      | 2.6.7          | Power consumption                                    | 77         |

|   |      | 2.6.8          | Delay                                                | 77         |

|   |      | 2.6.9          | Overall evaluation                                   | 80         |

|   | 2.7  |                |                                                      | 82         |

|   | 2.7  | Conciu         | asions                                               | 02         |

| 3 | Seci | ırity in (     | cache memories (IST)                                 | 85         |

|   | 3.1  |                | uction                                               | 85         |

|   | 3.2  |                | etical background                                    | 86         |

|   | 3.3  |                | crambling                                            | 87         |

|   | 3.4  |                | nent of the problem                                  | 92         |

|   | 3.5  |                | sed solution: Interleaved Scrambling Technique (IST) | 93         |

|   |      | 3.5.1          | Scrambler Table                                      | 94         |

|   |      | 3.5.2          | Cache Memory                                         | 100        |

|   |      | 3.5.3          |                                                      | 101        |

|   | 3.6  | IST pe         |                                                      | 104        |

|   |      | 3.6.1          |                                                      | 104        |

|   |      | 3.6.2          |                                                      | 105        |

|   | 3.7  | Evalua         |                                                      | 108        |

|   |      | 3.7.1          | CACTI tool evaluation                                | 108        |

|   |      | 3.7.2          |                                                      | 112        |

|   | 3.8  | Conclu         |                                                      | 114        |

| 1 | Dof  | oting <b>C</b> | DEMA and DDEMA                                       | 115        |

| 4 | 4.1  |                |                                                      | 115<br>115 |

|   |      |                |                                                      |            |

|   |      |                |                                                      | 116        |

|   | 4.3  |                | C                                                    | 116        |

|   |      | 4.3.1          | •                                                    | 116        |

|   |      | 4.3.2          |                                                      | 117        |

|   | 4.4  |                | e ;                                                  | 119        |

|   |      | 4.4.1          | ·                                                    | 119        |

|   |      | 4.4.2          | Cache memory                                         | 120        |

| CONTRENTEC | •   |

|------------|-----|

| CONTENTS   | 1V  |

| CONTENTS   | IA. |

|    |        | 4.4.3    | Interleaved Scrambling Technique                | 121 |

|----|--------|----------|-------------------------------------------------|-----|

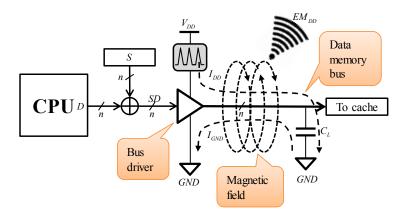

|    | 4.5    | Power    | (P) and Electromagnetic (EM) Radiation Analysis | 122 |

|    |        | 4.5.1    | Simple P or EM Radiation Analysis Attack        | 124 |

|    |        | 4.5.2    | Differential P or EM Radiation Analysis Attack  | 125 |

|    |        | 4.5.3    | Attack model                                    | 126 |

|    | 4.6    | Statem   | ent of the Problem                              | 127 |

|    |        | 4.6.1    | Objective                                       | 129 |

|    | 4.7    | Propos   | ed solution for defeating SPEMA                 | 129 |

|    |        | 4.7.1    | eDLC review and integration with IST            | 129 |

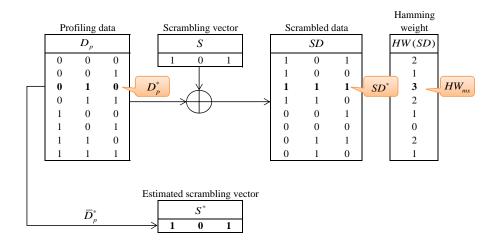

|    |        | 4.7.2    | Scrambling vector redundancy filter             | 132 |

|    | 4.8    | Propos   | ed solution for defeating DPEMA                 | 136 |

|    |        | 4.8.1    | Example of DPEMA attack on ISTe                 | 137 |

|    |        | 4.8.2    | DPEMA countermeasure                            | 140 |

|    |        | 4.8.3    | How it works                                    | 142 |

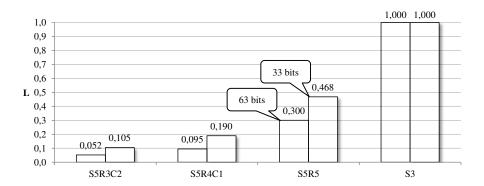

|    | 4.9    | Evalua   | tion and experimental results                   | 144 |

|    |        | 4.9.1    | Leakage function                                | 144 |

|    |        | 4.9.2    | Results                                         | 147 |

|    |        | 4.9.3    | Implementation costs                            | 153 |

|    | 4.10   | Conclu   | sions                                           | 161 |

| 5  | Conc   | clusions | :                                               | 163 |

|    | 5.1    | Scienti  | fic contributions                               | 166 |

|    | 5.2    | Future   | research and developments                       | 170 |

| Bi | bliogr | aphy     |                                                 | 171 |

X CONTENTS

# **List of Figures**

| 1.1  | Conceptual model of the autonomic system [9]                                                                                         | 5  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | SOC Consumer Portable Design Complexity Trends [1]                                                                                   | 7  |

| 1.3  | SOC Consumer Portable Power Consumption Trends [1]                                                                                   | 7  |

| 1.4  | Common construction of a memory hierarchy [13]                                                                                       | 10 |

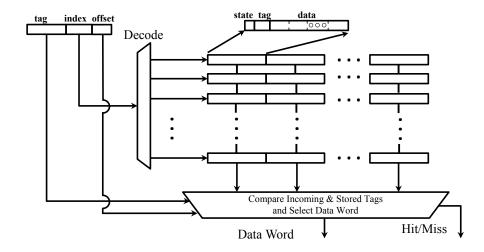

| 1.5  | Components of a cache memory [14]                                                                                                    | 11 |

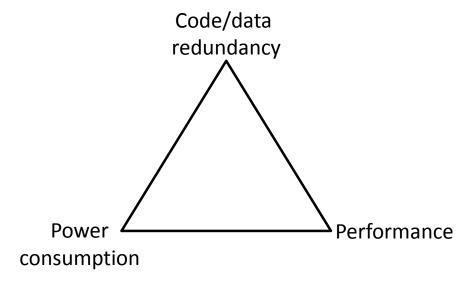

| 2.1  | The triangle of balance for EDCs and ECCs                                                                                            | 20 |

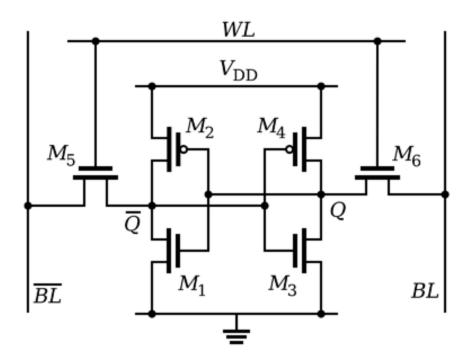

| 2.2  | Basic 6T SRAM cell                                                                                                                   | 21 |

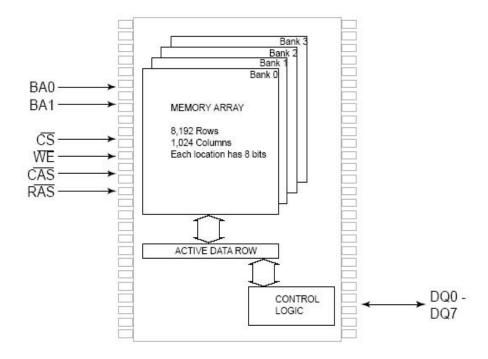

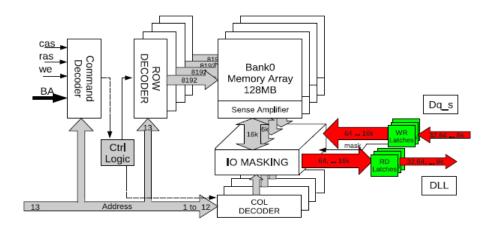

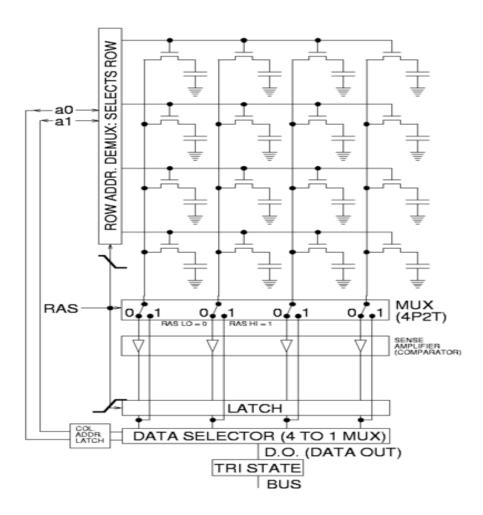

| 2.3  | Older 32MB DRAM design                                                                                                               | 22 |

| 2.4  | Modified DRAM design [49]                                                                                                            | 23 |

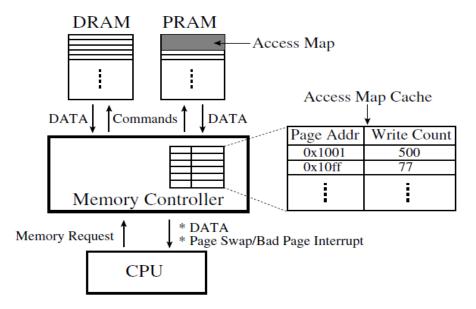

| 2.5  | PDRAM memory controller [50]                                                                                                         | 24 |

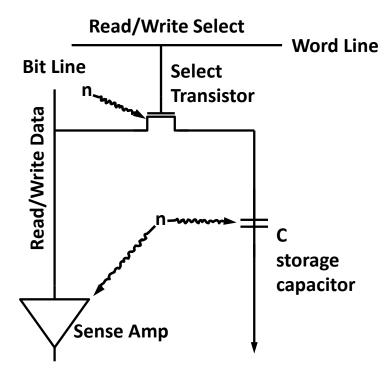

| 2.6  | Basic DRAM cell [32]                                                                                                                 | 25 |

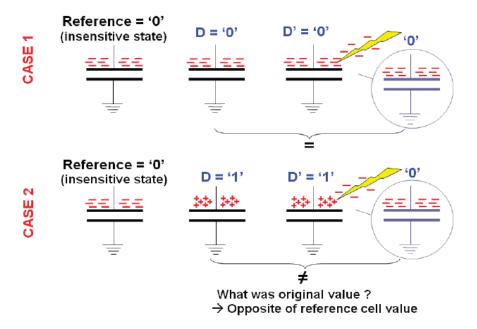

| 2.7  | The "insensitive state" of a DRAM cell. One cell is used as ref-                                                                     |    |

|      | erence to store the discharged state logic value (immune to radi-                                                                    |    |

|      | ations), useful data are stored in 2 other cells, D and D'. If the 2                                                                 |    |

|      | values are different, the original data is sure to be the opposite of                                                                |    |

|      | the reference cell value [51]                                                                                                        | 26 |

| 2.8  | Principle of DRAM read operation                                                                                                     | 27 |

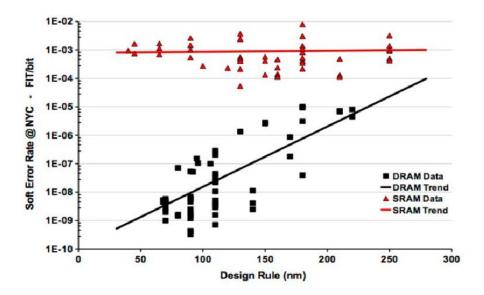

| 2.9  | Soft Error Rate (SER) per bits in DRAM and SRAM [53]                                                                                 | 30 |

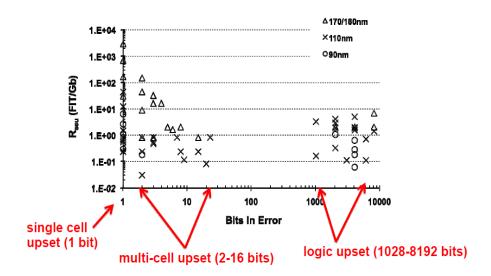

| 2.10 | 1 1 1                                                                                                                                | 31 |

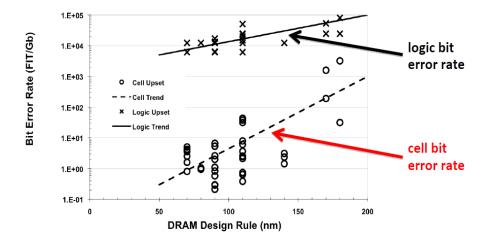

| 2.11 | DRAM Bit Error Rate (BER) [53]                                                                                                       | 31 |

|      | Neutron strikes on DRAM logic [30]                                                                                                   | 32 |

| 2.13 | Memory cell interleaving [53]                                                                                                        | 33 |

| 2.14 | General algorithm for Hamming codes                                                                                                  | 34 |

| 2.15 | Hamming-decoder circuit [37]                                                                                                         | 36 |

| 2.16 | Block diagram of concatenated Hamming and R-S codes [43]                                                                             | 37 |

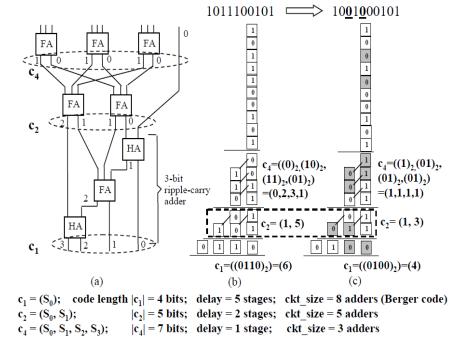

| 2.17 | (a) 10:4 parallel counter tree and check bits generation for (b) an uncorrupted word and codes and (c) a corrupted data word (2 bits |    |

|      | go from 1 to 0) and codes [33]                                                                                                       | 39 |

|      | go nom 1 to 0, and codes [33]                                                                                                        | 27 |

xii LIST OF FIGURES

| 2.18          | Proposed architecture in [33]                                                                       | 40 |

|---------------|-----------------------------------------------------------------------------------------------------|----|

| 2.19          | Block diagram of the proposed Hi-ECC architecture [39]                                              | 42 |

| 2.20          | Design of "bit-fix" scheme for 10 bits [40]                                                         | 43 |

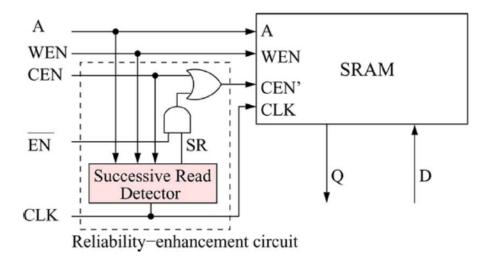

| 2.21          | Reliability-enhancement circuit proposed in [67]                                                    | 45 |

| 2.22          | Combination of restricted single-error correction codes and col-                                    |    |

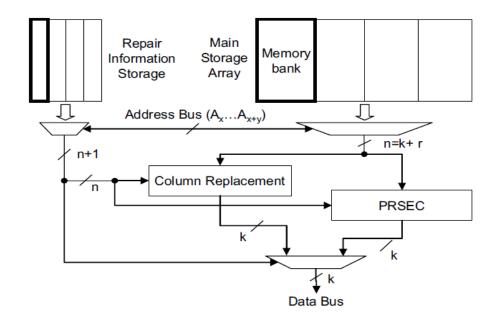

|               | umn replacement proposed in [68]                                                                    | 46 |

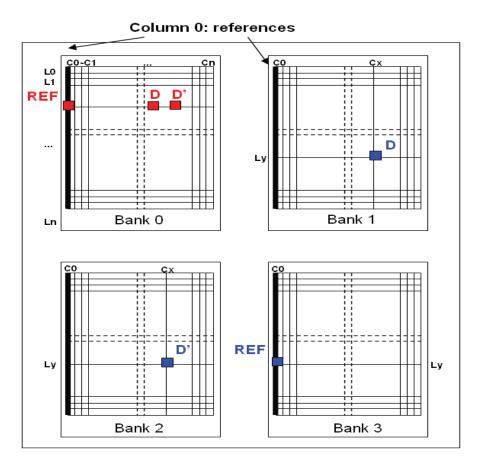

| 2.23          | Error recovering principle proposed in [51]. One cell is used as                                    |    |

|               | reference (REF) to store the discharged state logic value (immune                                   |    |

|               | to radiations), useful data are stored in 2 other cells, D and D'                                   | 47 |

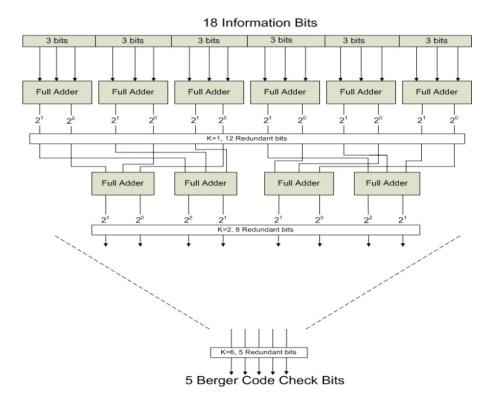

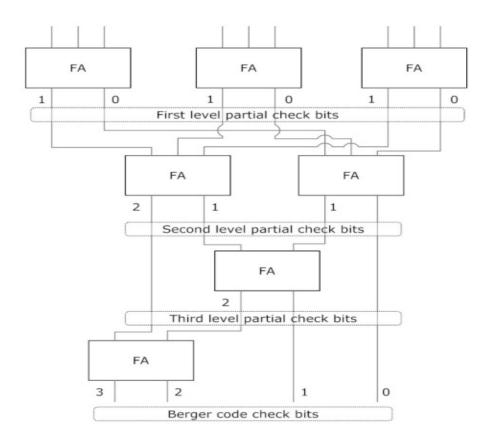

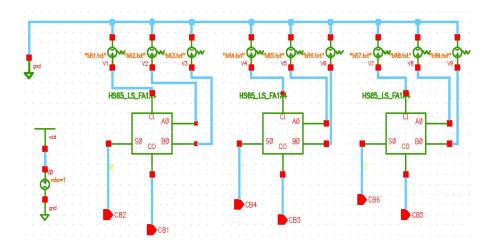

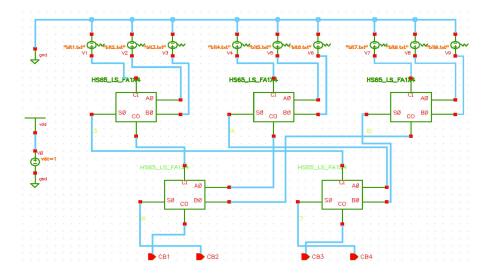

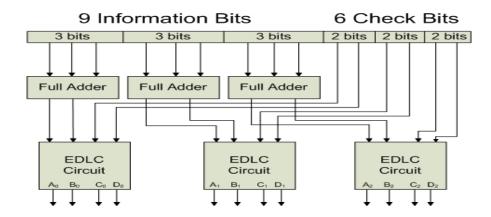

| 2.24          | Generation of the check bits for CS-1 Berger, CS-2 Berger and                                       |    |

|               | plain Berger code $K=6$ . The number of information bits is $N=$                                    |    |

|               | 18. The plain Berger code requires six levels of FA                                                 | 48 |

| 2.25          | Tree-shaped design for 9 information bits and the corresponding                                     |    |

|               | FA levels                                                                                           | 50 |

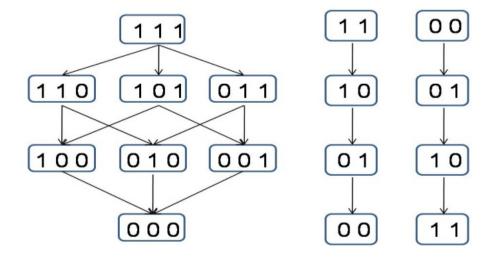

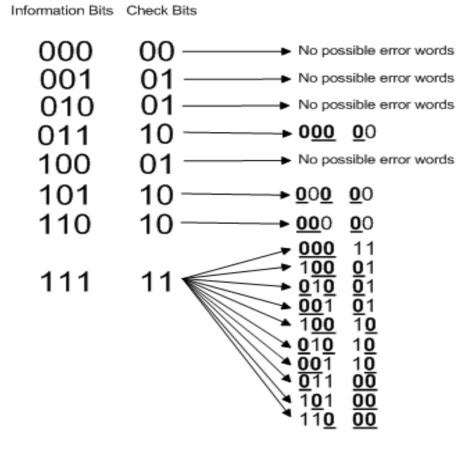

| 2.26          | Unidirectional error states graph for $K=1$ . On the left, all pos-                                 |    |

|               | sible single errors are indicated. On the right, the corresponding                                  |    |

|               | check bits for $B_1$ and $B_0$ scheme with single error transitions                                 | 53 |

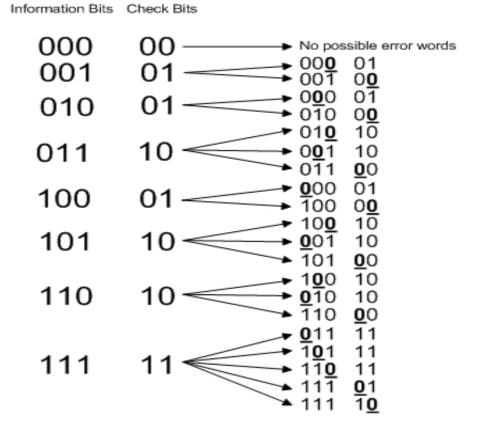

| 2.27          | Example of possible error words for 3 information bits and 2 check                                  |    |

|               | bits, with one error occurring (the first level of FAs is considered                                |    |

|               | K=1)                                                                                                | 54 |

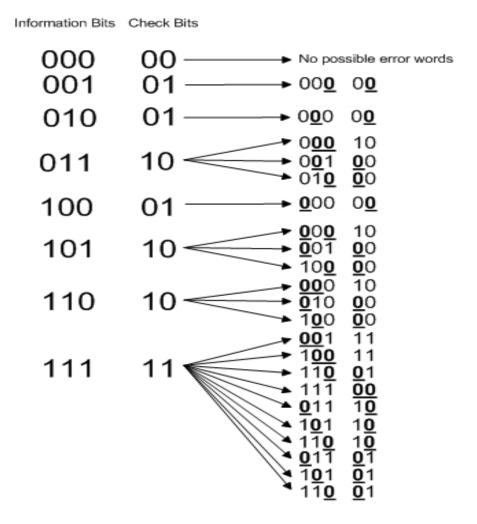

| 2.28          | Example of possible error words for 3 information bits and 2 check                                  |    |

|               | bits, with 2 errors occurring (the first level of FAs is considered                                 |    |

|               | K=1)                                                                                                | 55 |

| 2.29          | Example of possible error words for 3 information bits and 2 check                                  |    |

|               | bits, with 3 errors occurring (the first level of FAs is considered                                 | _, |

| 2.20          | K=1)                                                                                                | 56 |

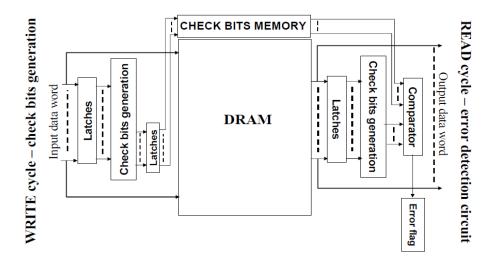

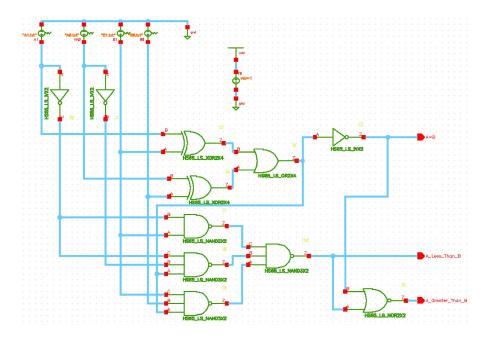

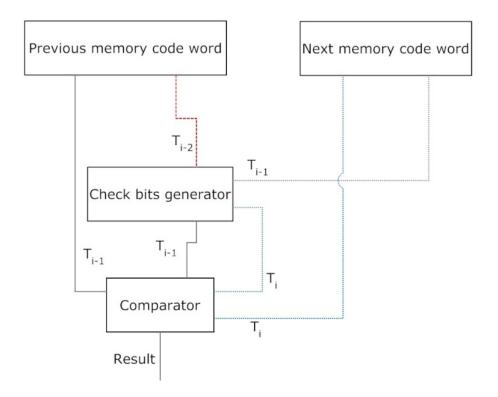

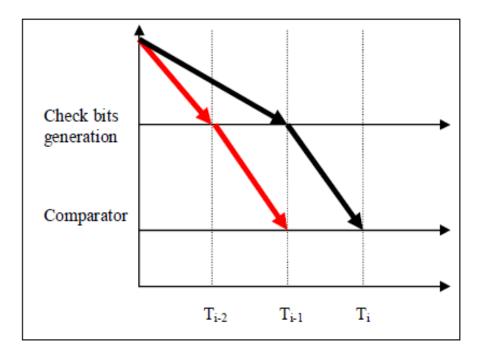

|               | General architecture of the implementation.                                                         | 62 |

|               | Implementation for the 1st level of the FA tree for 9 information bits.                             | 63 |

| 2.32          | Implementation for the 2nd level of the FA tree for 9 information                                   | () |

| 2 22          | bits.                                                                                               | 63 |

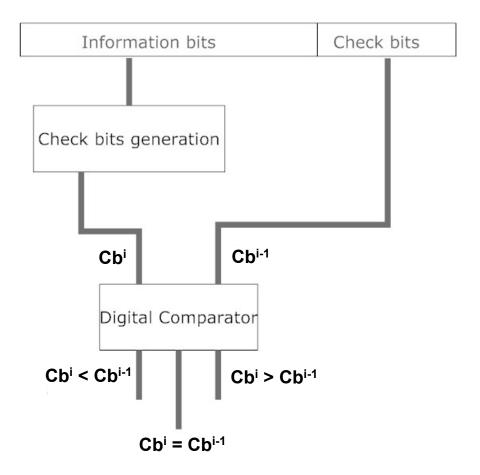

|               | Implementation of digital comparator with input sizes of 2 bits                                     | 64 |

| 2.34          | Error detection and localization circuit (example for 9 information bits 6 shock bits and $V = 1$ ) | 65 |

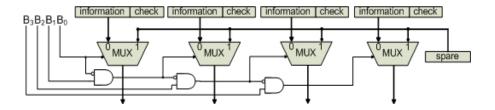

| 2.25          | bits, 6 check bits and $K = 1$ )                                                                    | 65 |

|               | Error correction for uncorrectable segments using a spare segment.                                  | 65 |

|               | General architecture of the implementation                                                          | 69 |

|               |                                                                                                     | 70 |

|               | Example of .txt stimulus file containing values for one bit of the                                  | 70 |

| 2.39          | inputs of an implementation                                                                         | 71 |

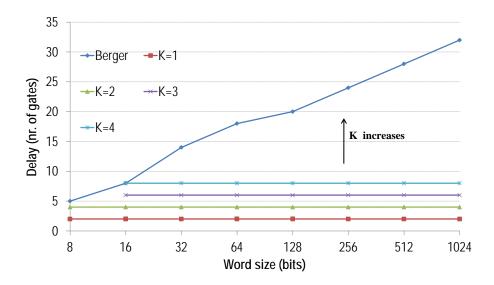

| 2.40          | Code delay of CS-K Berger codes                                                                     | 72 |

| ∠. <b>⊤</b> ∪ | Couc aciay of Co-11 Deigel codes                                                                    | 12 |

LIST OF FIGURES xiii

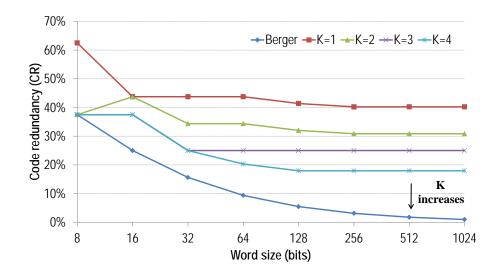

| 2.41 | Code redundancy for CS-K Berger codes and original Berger codes.         | 73  |

|------|--------------------------------------------------------------------------|-----|

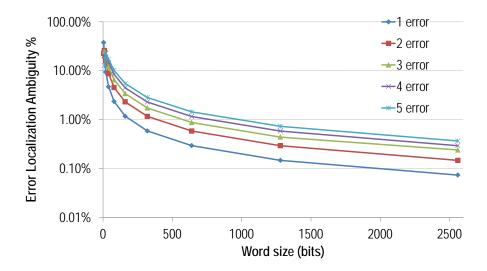

| 2.42 | Error localization ambiguity for the first level of FAs in CS-1 Berger   |     |

|      | code. Simultaneous errors are changed from 1 to 5                        | 74  |

| 2.43 | Error correction per segments for the CS-1 Berger code, errors           |     |

|      | from 1 up to 5 bits                                                      | 75  |

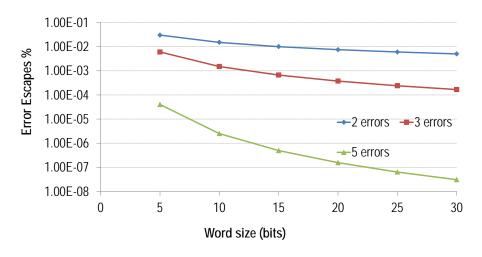

| 2.44 | Error escapes probability for CS-1 Berger code for 2,3 and 5 mul-        |     |

|      | tiple errors                                                             | 76  |

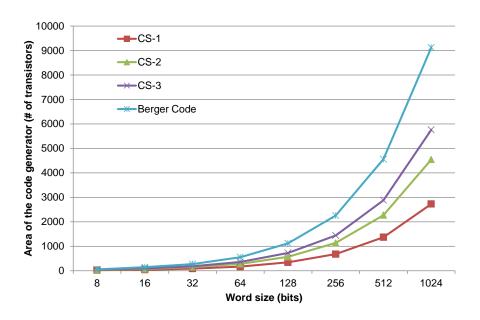

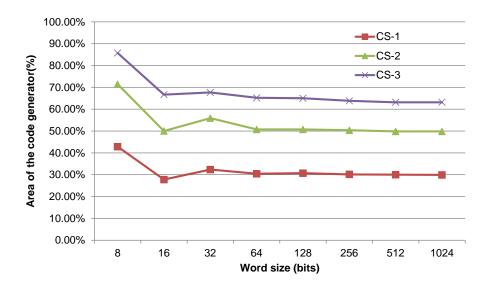

| 2.45 | Area of the code generator computed for CS-1,2,3 and the original        |     |

|      | Berger codes and different word sizes                                    | 76  |

| 2.46 | Area of the code generator computed as percentage from the Berger        |     |

|      | code area for the first three levels of Full Adders                      | 77  |

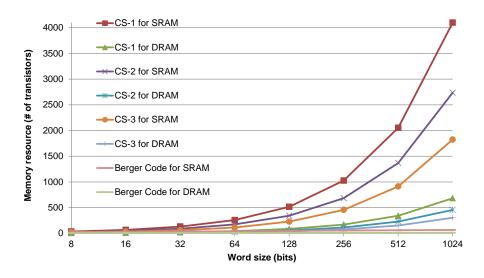

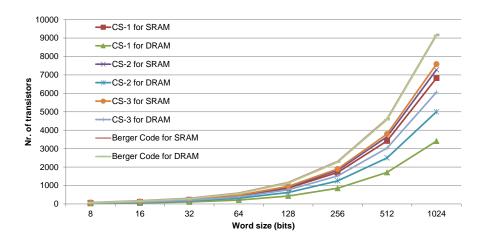

| 2.47 | •                                                                        |     |

|      | SRAM and DRAM cells are used                                             | 78  |

| 2.48 | Area of the code generator and memory resource necessary for CS-         |     |

|      | 1,2,3 and Berger codes                                                   | 78  |

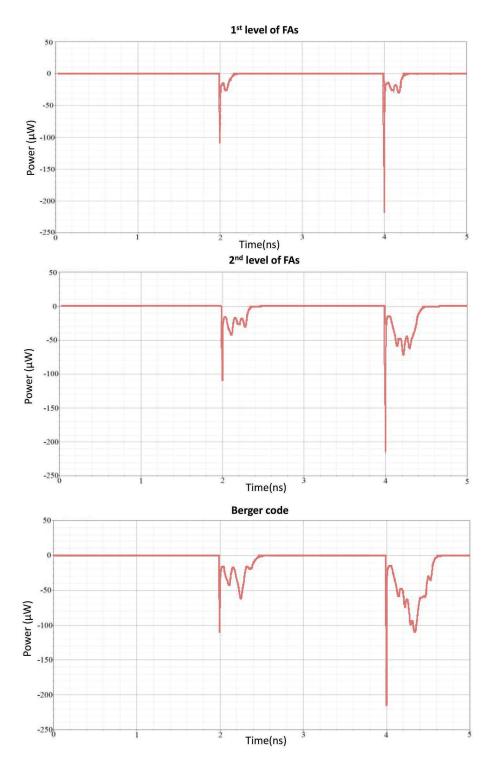

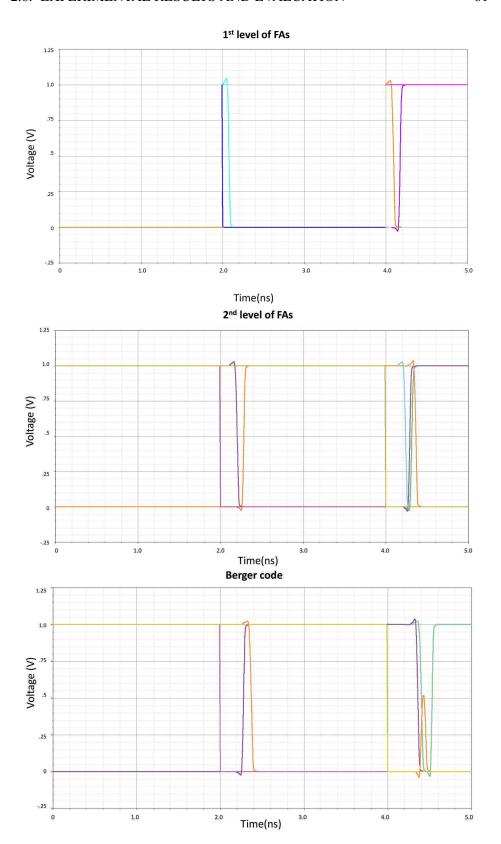

| 2.49 | Power consumption comparison between the 1st and 2nd level of            |     |

|      | the FA tree and Berger code (the values are negative because the         |     |

|      | electric current is measured at the ground node of the circuit)          | 79  |

| 2.50 | Delay comparisons between the 1st and 2nd level of the FA tree           |     |

|      | and Berger code                                                          | 81  |

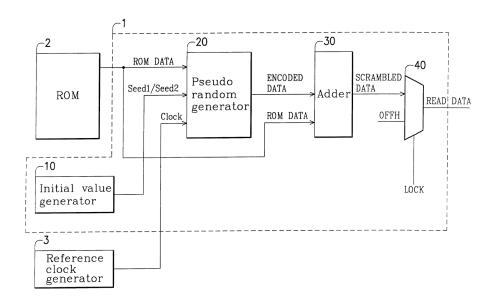

| 3.1  | Design used in [75]                                                      | 89  |

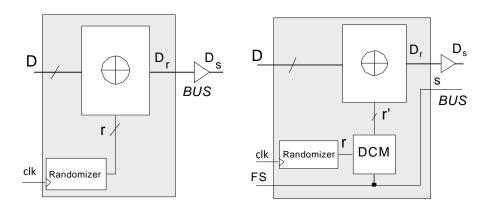

| 3.2  | Pure (left) and conditional (right) scrambling [74]                      | 90  |

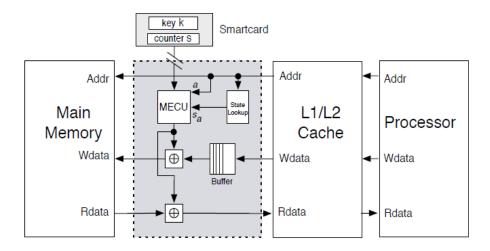

| 3.3  | MECU architecture from [78]                                              | 91  |

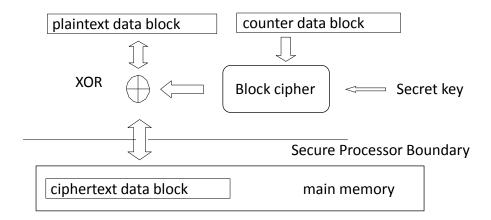

| 3.4  | Counter-mode encryption used in [23]                                     | 92  |

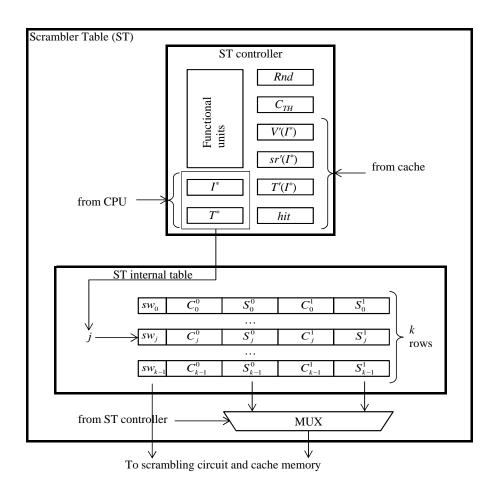

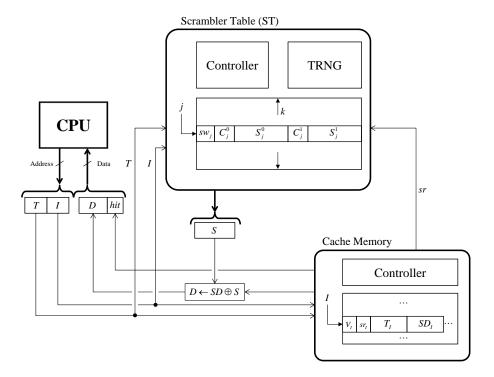

| 3.5  | The scrambler table block and entries structure                          | 95  |

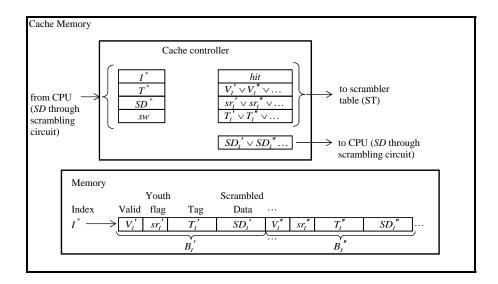

| 3.6  | Cache memory entries structure and main functional blocks                | 100 |

| 3.7  | IST write cycle                                                          | 101 |

| 3.8  | IST read cycle                                                           | 102 |

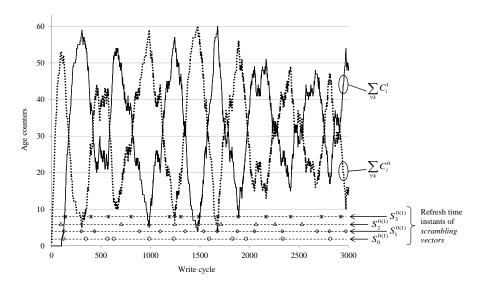

| 3.9  | Simulation of the ST table management of the <i>scrambling vectors</i> . |     |

|      | The scheme is SAU, the number of data blocks is 64 and the num-          |     |

|      | ber of lines in the ST internal table is 4. CPU addresses are gener-     |     |

|      | ated randomly                                                            | 103 |

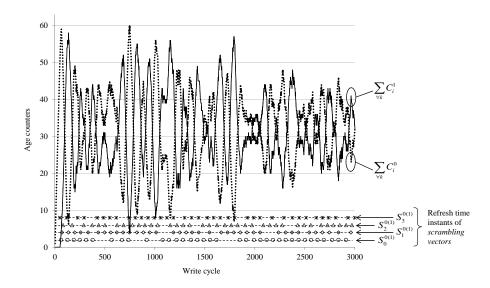

| 3.10 | Simulation of the ST table management of the <i>scrambling vectors</i> . |     |

|      | The scheme is SAU, the number of data blocks is 64 and the num-          |     |

|      | ber of lines in the ST internal table is 4. CPU addresses are gener-     |     |

|      | ated incrementally with a random increment between 0 and 3               | 103 |

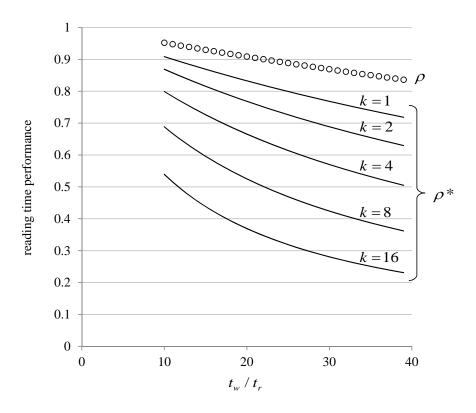

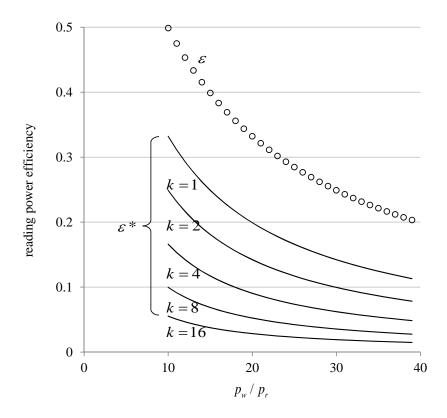

| 3.11 | Representation of Equations 3.11 and 3.12 assuming a miss ratio          |     |

|      | n = 0.005                                                                | 106 |

xiv LIST OF FIGURES

| 3.12 | Representation of Equations 3.13 and 3.14 assuming a miss ratio    |     |

|------|--------------------------------------------------------------------|-----|

|      | $\eta=0.005$ and $t_w=20t_r$                                       | 107 |

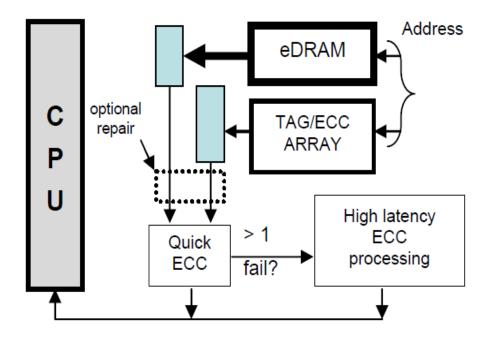

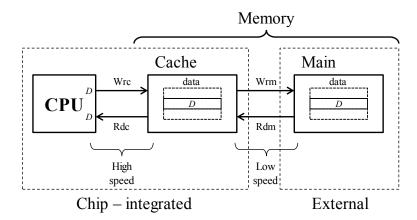

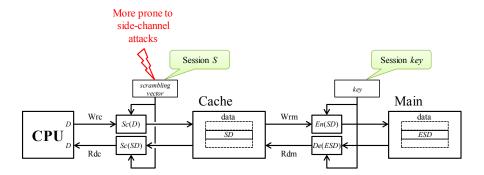

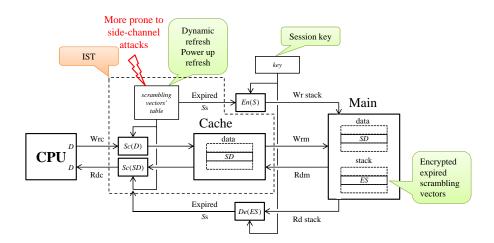

| 4.1  | Simplified model of a computer memory system                       | 117 |

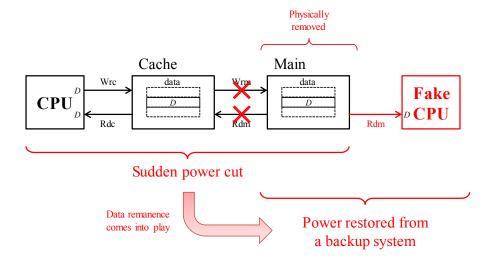

| 4.2  | Cold-boot attack on main memory                                    | 118 |

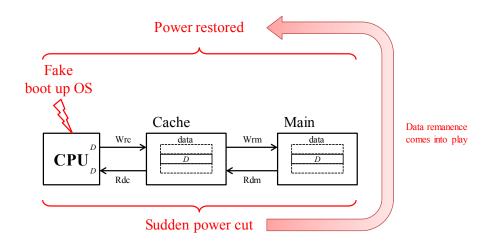

| 4.3  | Cold-boot attack without removing memory chips                     | 119 |

| 4.4  | Published proposals securing memory at hardware level against      |     |

|      | cold-boot attacks                                                  | 120 |

| 4.5  | Interleaved Scrambling Technique. Hardware protection for cache    |     |

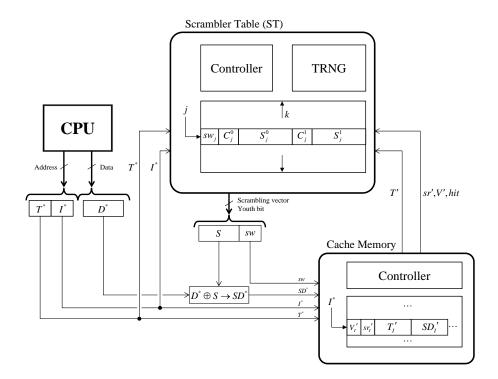

|      | that can be integrated into a global protection scheme             | 121 |

| 4.6  | Switching drivers and bus line currents excite power peaks and     |     |

|      | electromagnetic pulses which leak information about data flowing   |     |

|      | into the drivers and buses                                         | 123 |

| 4.7  | Example of SPEMA attack                                            | 125 |

| 4.8  | Example of DPEMA attack                                            | 127 |

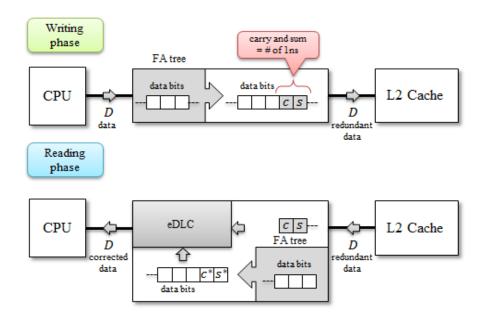

| 4.9  | The error detection, correction and localization technique (eDLC). | 130 |

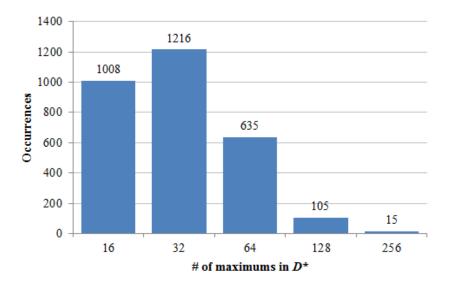

| 4.10 | Histogram of number of maximums found in the $D^*$ set for 12 data |     |

|      | bits after 3.000 attacks. Average is 37.92                         | 135 |

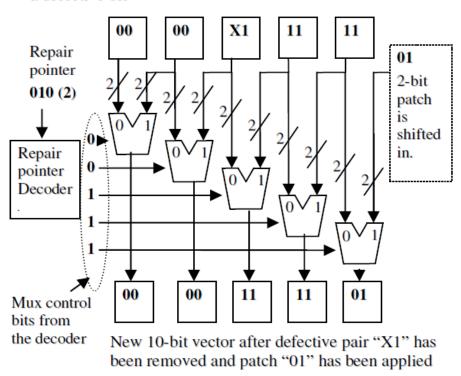

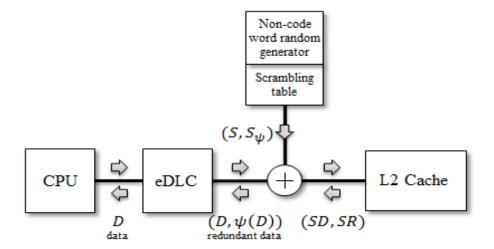

| 4.11 | Overview of the IST with SPEMA protection                          | 136 |

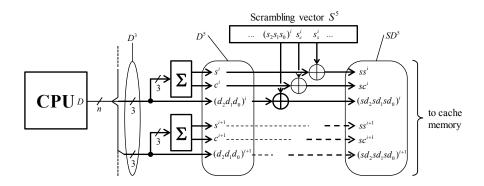

| 4.12 | Overview of the writing cycle in the IST – eDLC technique          | 137 |

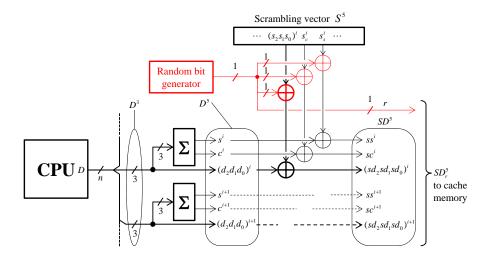

| 4.13 | Overview of the RM-ISTe technique                                  | 141 |

| 4.14 | Architecture flowchart of the write cycle in the RM-ISTe tech-     |     |

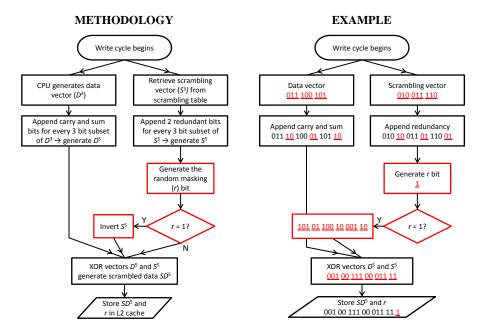

|      | nique. An example on 9 bits is included                            | 141 |

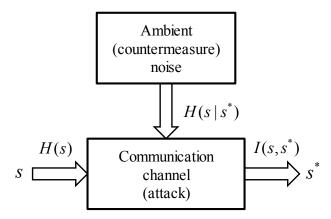

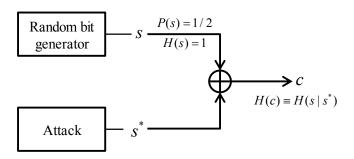

|      | Communication channel model used to evaluate the leakage           | 145 |

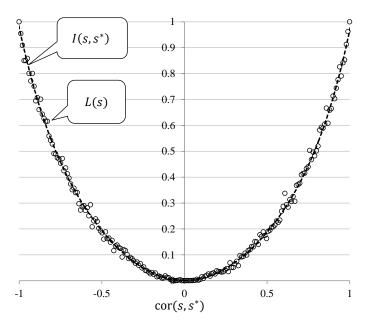

|      | Evaluation of entropies in an attack scenario                      | 146 |

| 4.17 | Simulation of the circuit in Figure 4.16 and Equation 4.14, and    |     |

|      | theoretical curve derived from Equation 4.10                       | 148 |

|      | Information leakage achieved with SPEMA attacks                    | 150 |

| 4.19 | Information leakage achieved by DPEMA attack applied on tech-      |     |

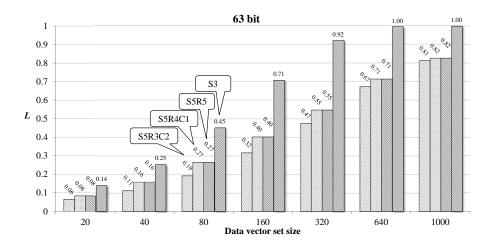

|      | niques without random masking for a 63-bit architecture            | 151 |

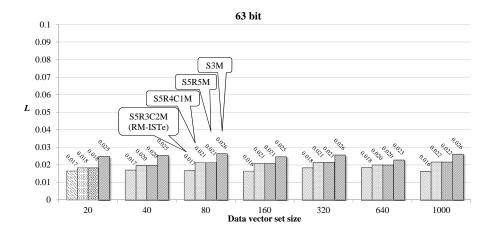

| 4.20 | Information leakage achieved with DPEMA attacks applied on ran-    |     |

|      | dom masking techniques for 63-bit architecture size                | 152 |

# **List of Tables**

| 2.1 | Example of $B_0$ coding scheme for 1 bit in error                                                                                                                                                                 | 51  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Example of $B_1$ coding scheme for 1 bit in error                                                                                                                                                                 | 52  |

| 2.3 | Example of ambiguity for one bit in error                                                                                                                                                                         | 57  |

| 2.4 | Example of ambiguity for two bits in error                                                                                                                                                                        | 57  |

| 2.5 | Correctable error patterns in the information bits $(K = 1)$                                                                                                                                                      | 59  |

| 2.6 | Correctable error patterns in the check bits $(K = 1)$                                                                                                                                                            | 59  |

| 2.7 | Examples of multiple error escapes                                                                                                                                                                                | 60  |

| 2.8 | Actions based on the check bit comparison. $A_i$ are the check bits generated from the information <i>segment</i> of the code during the verification and validation. $B_i$ are the check bits extracted from the |     |

|     | code. See Figure 2.30                                                                                                                                                                                             | 60  |

| 2.9 | Detection and localization circuit behaviour. $A_i, B_i, C_i, D_i$ are outputs of circuit in Figure 2.34                                                                                                          | 61  |

|     |                                                                                                                                                                                                                   |     |

| 3.1 | Evaluation of Equations 3.10 for $n = 32$                                                                                                                                                                         | 99  |

| 3.2 | CACTI results for different cache sizes, 1-way set associative                                                                                                                                                    | 109 |

| 3.3 | CACTI results for different cache sizes, 2-way set associative                                                                                                                                                    | 110 |

| 3.4 | CACTI results for different cache sizes, 4-way set associative                                                                                                                                                    | 111 |

| 3.5 | Area utilization and overhead in the FPGA device implementation.                                                                                                                                                  | 113 |

| 3.6 | Power consumption comparison in normal operation                                                                                                                                                                  | 113 |

| 3.7 | Delay for data and clock path                                                                                                                                                                                     | 114 |

| 4.1 | Example of unique maximum                                                                                                                                                                                         | 131 |

| 4.2 | Example of multiple maximums                                                                                                                                                                                      | 132 |

| 4.3 | Codeword and non-codeword spaces for ${\cal D}^5$ and ${\cal S}^5$ respectively                                                                                                                                   | 133 |

| 4.4 | Hamming weights for the data vector and scrambling vector spaces.                                                                                                                                                 | 134 |

| 4.5 | Number of elements in the set of maximums $D^*$                                                                                                                                                                   | 135 |

| 4.6 | Zero and one data vector sets for the DPEMA attack in a three bit                                                                                                                                                 |     |

|     | bus example.                                                                                                                                                                                                      | 138 |

xvi LIST OF TABLES

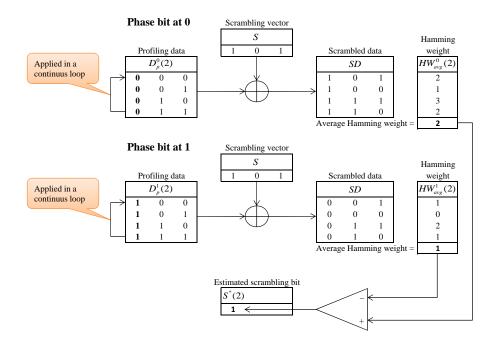

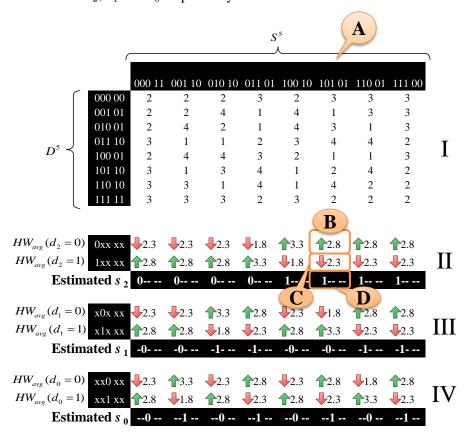

| 4.7  | Example of DPEMA attack applied to a three bit data bus with                        |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | ISTe scrambling technique. (I) is the matrix of hamming weights                     |     |

|      | generated in the data bus after the scrambling. (II), (III) and (IV)                |     |

|      | are the average <i>hamming weights</i> used to estimate bit $s_2$ , $s_1$ and $s_0$ |     |

|      | respectively                                                                        | 139 |

| 4.8  | DPEMA attack applied to RM-ISTe countermeasure                                      | 143 |

| 4.9  | Information leakage measured for DPEMA attacks in different ar-                     |     |

|      | chitecture sizes and techniques. Attacking data vector set is 1000.                 |     |

|      | Number of scrambling vectors tested is 1000. In gray background                     |     |

|      | cells at least one <i>scrambling vector</i> has been correctly estimated            | 153 |

| 4.10 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 1-way set associative cache                                                 | 155 |

| 4.11 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 1-way set associative cache (continued)                                     | 156 |

| 4.12 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 2-way set associative cache                                                 | 157 |

| 4.13 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 2-way set associative cache (continued)                                     | 158 |

| 4.14 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 4-way set associative cache                                                 | 159 |

| 4.15 | Implementation costs of the previous and current proposed tech-                     |     |

|      | niques, 4-way set associative cache (continued)                                     | 160 |

# **List of Acronyms**

| BCH Bose Ray-Chaudhuri                                  |

|---------------------------------------------------------|

| CPU Central Processing Unit                             |

| DCM Duty Cycle Modulator                                |

| DRAM Dynamic Random Access Memory                       |

| ECC Error Correcting Code                               |

| EDC Error Detecting Code                                |

| EDLC Error Detecting, Localization and Correcting       |

| FAFull Adder                                            |

| IC Integrated Circuit                                   |

| IST Interleaved Scrambling Technique                    |

| KB Kilo Bytes                                           |

| LFSRLinear Feedback Shift Register                      |

| LUTLook-Up Table                                        |

| MECU Memory Encryption Control Unit                     |

| OSVOld Scrambling Vector                                |

| PRNG Pseudo-Random Number Generator                     |

| R-S Reed-Solomon                                        |

| SAS Set Address Synchronized                            |

| SAU Set Address Unsynchronized                          |

| SEC-DED Single Error Correction, Double Error Detection |

| 5EC-6ED 5 Errors Correction, 6 Errors Detection         |

| SER Soft Error Rate                                     |

| SRAM Static Random Access Memory                        |

| ST Scrambling Table                                     |

| YSV Young Scrambling Vector                             |

|                                                         |

### **Chapter 1**

### Introduction

#### 1.1 Context

In nowadays technology, there are more and more huge and complex digital systems. Because of the continuous evolution of the technology node, the components and circuits are getting smaller, they occupy less area, have higher speeds and favor low-power consumption. Thus, the systems are more complex and can handle huge amounts of data at the same time. As the complexity increases, devices become resource and power hungry, hence it must be kept under balance. For any given domain, a system must be able to perform complex computations, to output high speed and to keep the information as accurate as possible.

Modularity plays an important role in any system, each one is composed of several subsystems, which perform specific tasks (e.g. monitoring, planning, optimization, data acquisition, etc.). This characteristic is better understood when considering the reliability and maintainability points of view, because if one subsystem fails, it can be easily replaced by a spare one. Also, the system can be easily extended because the architecture of such a system is highly scalable.

Autonomous systems are also a current tendency. Such systems are able to monitor themselves, they can repair themselves if a subsystem is faulty, and they can adapt to environment changes (e.g. new components, errors occurrence, etc.). The main characteristic of autonomous systems is the capability to run without human intervention. To achieve such features, there are several "self-\*" type properties, like: self-configuration, self-management, self-healing, self-optimization, self-protection, etc. Each one of these properties is a priority for autonomous systems.

Although the technology node decreases almost every 2 years and offers higher density and higher speeds for integrated circuits, the occurrence of errors increases

and needs to be mitigated. The errors severely affect any component of a system, but can be mitigated through several methods, techniques and algorithms.

Another relevant trend is the security of devices and systems. There are a large variety of attacks which target memory systems and try to retrieve important information such as encryption and public keys, digital signatures, biometric information, etc. However, developing a system that is secure against every type of attack is nearly impossible due to the diversity and nature of attacks and infeasible because of performance, power and size considerations.

There is a need to design, implement and test systems that can handle errors, to be tolerant to faults. Memory systems are a special and critical category, because they store data which is afterwards used by the system. When errors occur, the system must be able to perform self-healing, to detect and correct the errors, which is achieved by implementing several self-healing methods and techniques. On the other hand, when attacks eventuate, the system must either repel them or disclose useless data. However, the cost for implementing a self-healing memory system must be as low as possible and a trade-off between performance and cost is necessary.

#### 1.2 State of the art

#### 1.2.1 Motivation

Most modern systems present novelty through the self-healing concept, which can be modeled on any given type of system and can be built through several methods, functions and techniques that must accomplish the self-healing objective. This tendency can be extended to high availability and stability (measured by uptime), increased reliability, high maintainability and scalability. Any modern system is desired to have no errors (if some occur, they should be corrected) and to keep the above tendencies as high as possible. So far, the self-healing concept is widely used in distributed network systems, along with other "self-\*" features. Nevertheless, it can also be employed on any system, even on memory systems which encounter high error rates and are accustomed to any type of attacks.

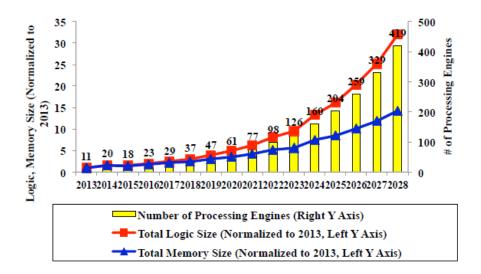

Memory systems are critical in any large and complex digital design. This is because memory systems retain the information which is then used in processing elements of the digital design. The concerns regarding memory systems are because the technology minimum feature size keeps decreasing, therefore, the memory elements are shrinking, have higher density and speed. In addition, the percentage of memory area in System on a Chip (SOC) integrating circuits is expected to grow significantly during the next decade. According to the ITRS Roadmap 2013 [1], the size of the area occupied by memory increases faster than the area dedi-

cated to logic. There is a need to keep the information as accurate as possible by using mitigation techniques. Because the size of the circuitry is getting smaller and smaller, high-energy neutrons and alpha-particle strikes (background radiation) can generate soft (i.e. transient) errors in a memory system and can affect more than one location. Therefore, multiple-bits errors may occur in any memory system, whether it is SRAM or DRAM. There is a need to keep them error free, since critical data is stored at any given time.

Self-healing methods, techniques and algorithms have been employed in order to mitigate these types of errors. For memory systems, self-healing is perceived as error detecting and correcting codes and replacing/replicating methods for the elements of a memory system. Self-healing is mainly used for autonomous systems (i.e. systems that can adapt themselves to the given circumstances and perform repair of erroneous elements), but the concept is widely used for any system that can perform self-monitoring, planning and repair operations without the human assistance.

On the other hand, a low-power trend has emancipated and targets all systems to use as less energy as possible by using intelligent architectures, designs and techniques. This trend is mainly for limited energy source devices, because maximizing the life of the device is the main concern for these types of devices. The main idea of the low-power concept is to use as less power as possible when a device is operating and use no power when it's idle (i.e. no processing is done). However, this approach may limit the computation speed of a device. Therefore, a balance between power consumption and performance is needed and it depends very much on the design and implementation of the device. Any modern self-healing technique must have low area overhead and low power consumption, while the performance degradation must be kept to a minimum.

Data security in memory systems is another growing trend in the last decade. Modern day ICs contain significant information that must be highly secured, so that it stays hidden. In the last 5 years, there have been reported a large variety of attacks against ICs and memories, mostly targeting the vulnerabilities of cache and main memories, smartcards, etc.

In a recent report [2], the author pointed out that 62% of companies world-wide were subject to payment fraud in 2014 and that credit/debit cards are the second most frequent target of payment fraud. Mobile payments are a relatively new payment method, but this trend is increasing among large companies and organizations. However, there are several uncertainties about it such as disclosure of sensitive information or secure transfer of information.

Ensuring the confidentiality of sensitive information is becoming more and more crucial because targets such as credit cards and other kind of legal supports store biometric and personal information [3]. Very often general purpose devices

like desktops, laptops or smartphones are used for private transactions with financial entities or health-care issues, among others. In the case of devices without specialized hardware, all cryptographic operations are executed in software, resulting in an intensive use of memory [4]. This poses sensitive data at risk, including that stored in the cache memory [5].

Solving the challenges imposed by the trends explained above is the main purpose of this work, which are important in any modern device or system. Achieving data security, low power consumption, high performance, small area overhead and new self-healing techniques for memory systems is a priority in nowadays electronic engineering.

#### 1.2.2 Introduction

In modern technology, the concept of a self-healing system is becoming increasingly common in memory systems. This trend revealed itself due to some factors and requirements: autonomous systems, employing "self- features", the evolution of the technology node, multiple random errors, etc. Nowadays, the technology node used is 45nm, 32nm and even 22nm, but it's still decreasing [1]. By scaling down the components of any system, a gateway for errors and faults has been created. This scaling affects the dimensions of circuits, the operating voltage and current, and the power consumption [1]. Decreasing the operating voltage favors low power consumption when the circuit is active, but implies lower limits and thresholds for detecting the operating state (e.g. voltage levels for 1 and 0). Also, when a circuit is idle or deactivated, the leakage current must be negligible. Due to the reduced dimensions, the packaging is very dense, in order to achieve a considerable size. This high density favors, in a negative way, the occurrence of soft and hard errors. The balance is achieved somewhere in the middle, because the new technologies allow higher performance and higher switching speed, but have the disadvantage to be susceptible to any kind of errors.

In order to increase the reliability of systems against soft and hard errors, the self-healing concept emerged. This concept is part of the auto-management features that appeared in autonomous systems. The idea was developed by IBM in 2001 [6] with the purpose of creating a distributed system capable of self-management, which adapts to environmental conditions and defects that may occur, based on certain high-level decisions and policies. In such a self-manageable system, the human intervention is minimal and has the role to define the general policies and rules that govern the system. Thus, IBM defined four self-\* properties:

- Self-configuration: automatic configuration of components and devices

- Self-healing: automatic discovery and correction of errors and faults

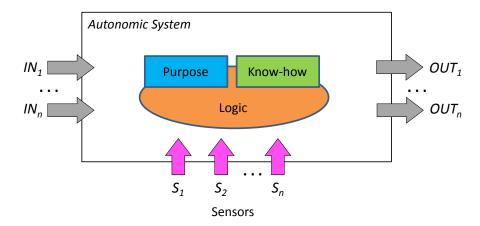

Figure 1.1: Conceptual model of the autonomic system [9]

- Self-optimization: automatic self-monitoring and resource control to ensure optimal functioning with respect to the requirements defined

- Self-protection: proactive identification and protection against random malicious attacks

Depending on the evolutionary level, IBM defined five levels of implementation [7]: the first level is the basic one which shows the current situation for manually managed systems, levels two to four introduce new automated management functions, and level five is the ultimate goal of autonomous systems, the self-management. Moreover, the complexity of an autonomous system can be simplified by using various design patterns, like Model-View-Controller (MVC) to improve the separation between system functions [8].

A basic concept of the autonomous systems is *closed control loops*. These loops monitor specific resources (hardware and software) and try to maintain autonomously specific parameters in a desired range. Depending on the size and complexity of the system, the control loops can be hundreds, even thousands.

The conceptual model of an autonomous system contains several vital elements: sensors, knowledge and logic (Figure 1.1). The sensors allow the system to observe the running operations, as well as the external environment. The knowledge is basically the intention and the "know-how" to self-management, without external intervention. Current operations are dictated by the logic system, which is responsible for making the correct decisions, based on the internal knowledge and the information from sensors.

The model highlights the fact that the operation of an autonomous system is driven by purpose, by intention. This includes the mission (e.g. the service that it must provide), system policies (e.g. what defines the behavior) and "survival instinct". If this system would be a control system, it would be coded as a function of errors with feedback or as an algorithm combined with a set of heuristics, in an heuristic assisted system.

Although autonomous systems may have different objectives and behaviors, each autonomous system must exhibit a minimum set of properties to achieve its own goals. Thus, an autonomous system must be automatic, i.e. to be able to self-control internal functions and operations. Also, it must be independent and can start automatically, without external intervention. Another important feature is adaptability. It should be able to change the current operations (e.g. configuration, status, etc.), so allows the system to cope with spatial and temporal changes in the context of operations, either on long term (e.g. optimization, modifying specific parameters), or short term (e.g. malicious attacks, defects, faults, errors, etc.). The last important property is defined as the awareness of the autonomous system, meaning it is able to monitor (via sensors) the operational context, as well as the internal state, in order to achieve its computational objectives.

A memory system with self-healing features is a relatively new concept in the digital era and requires the existence of algorithms, methods and techniques implemented in the memory system, that try to keep the information as accurate as possible.

As technology evolves, memory systems have developed from small, slow and simple architectures to huge, fast and complex designs. This evolving trend was governed by the technology node which kept shrinking continuously. Therefore, the density and speed of integrated circuits have increased exponentially and the trend was described by Moore's law in 1965. However, the sources which generate errors and faults were not completely removed and still exist in several forms. This leads to developing techniques, methods and algorithms needed for the mitigation of errors in any given system.

In the ITRS Roadmap 2013 [1], it is shown that the area occupied by memory in SOC integrated circuits increases faster than the area dedicated to logic (Figure 1.2).

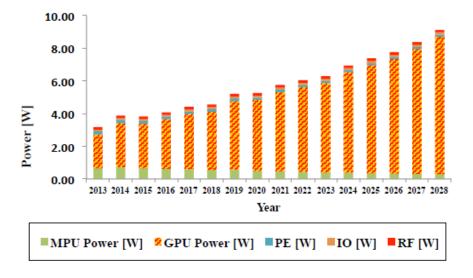

Low-power consumption is another trend for most systems, they favor low power consuming operations, conservation of energy and maximizing the life of limited energy sources. Figure 1.3 shows the power consumption trends for SOC integrated circuits, based on the ITRS Technology Roadmap 2013 [1].

Because there are several and different types of self-healing techniques and low-power architectures, the scope of this chapter is to summarize the existing and proposed methods of self-healing and models for low-power capabilities for

Figure 1.2: SOC Consumer Portable Design Complexity Trends [1]

Figure 1.3: SOC Consumer Portable Power Consumption Trends [1]

memory systems.

This work is focused on current self-healing techniques for systems in general, but more in detail for memory systems. Also, because there are several types of memories that are used nowadays, the most important ones are taken into consideration: SRAM and DRAM. Also, data security in memory systems is tackled from different perspectives and security models and methodologies are proposed and analyzed.

#### 1.2.3 The Self-Healing concept

Self-healing can be described in numerous ways, but when speaking about a self-healing system, the best definition is: "System automatically detects diagnoses and repairs localized software and hardware errors" [10]. Self-healing is just a type of the more general self-\* properties. For example, self-configuration is defined as automated configuration of components and systems follows high-level policies. Self-optimization is known as automated tuning of the system parameters in order to improve performance and efficiency. Self-protection is well-known in security systems where they have the ability to defend against malicious attacks or cascading failures. Usually, an autonomic system must support these four features. An autonomic system is composed of several autonomic elements, each containing internal resources and delivers services to other autonomic elements.

Given the autonomic manager (which controls and represents an element), the managed element could be a hardware resource (e.g. storage), a CPU, hardware device or a software resource (e.g. database, directory service, etc.) Each element is responsible for managing its internal state and behavior and for managing its interactions with an environment that consists of messages and signals from other elements.

Self-healing techniques have been in continuous development, beginning with 1970s when fault tolerant computing was achieved through fault model specifications, fault avoidance, detection and masking. In 1980s, the methods have advanced to dependable computing where they focused reliability, availability, integrity, degradation and maintainability of systems. From 1990 until now, the term of self-healing was used more often when describing systems with capabilities of dependability, modeling, monitoring, diagnosis, planning and adaptation for repair.

Nowadays, a self-healing system can modify its behavior in response to the changes occurring in the environment. In [11], the author states that a self-healing system has in its lifecycle four major activities: monitoring the system at runtime, planning the changes, deploying the change descriptions and adopting the changes. Based on these activities, the architecture of such a system should include: monitoring the system's performance and recognition of faults or anomalies, adapt-

ability to structural, dynamic and run-time aspects, communication integrity and internal state consistency and ability to address the anomalies when discovered (planning, deploying and enacting the necessary changes).

In [12], the authors define, in a formal way, several "self" properties from the perspective of distributed systems. From the self-healing definition, we can infer that this technique is focused on maintaining or restoring a system's safety properties. When these are violated, healing may take an arbitrary but finite amount of time and guarantees the recovery from that subset of actions that perturbs its state. Systems with self-healing will often exhibit a degraded level of performance when the external action causes a crash failure. Most of the self-healing solutions are non-masking or reactive, but there are several proactive versions, known as predictive self-healing. These systems anticipate failures from symptoms of erratic behavior, but protect the system from catastrophic service disruption by internal restarting certain modules (also known as micro-rebooting) and masking the failure from the user.

Self-healing can be employed in a system by using different measures, most of them rely on the problems/errors/faults that can occur in the given system and, of course, on the architecture and design of that system. Thus, self-healing techniques implementations and proposals are addressed in Chapters 2, 3 and 4.

#### 1.2.4 Memory systems

The memory system is the repository of information (data) in any computer system. A CPU will read the data, perform operations and writes it back to the memory. The memory system is composed of a collection of storage locations, organized in memory words and has a numerical address. A key performance parameter of a memory system is the effective speed of the memory. Capacity is important as well, but these properties are always in conflict. Usually, technology tradeoffs are employed to optimize between the two factors (note that cost also influences the tradeoffs). So, there are large but slow memories and fast but small ones.

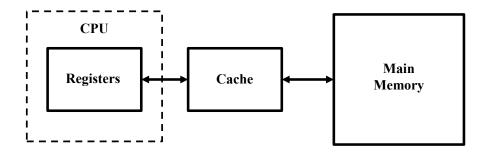

Because latency (i.e. the delay from when the processor first requests a word from the memory until that word arrives and it's available for use) plays an important role when designing a memory system, it is important to engineer a memory system with the lowest latency. Therefore, a simple solution for a memory hierarchy is to use a small but very fast memory in front of the large, slow memory. This idea led to the hierarchy in Figure 1.4, which nowadays is very common.

At the top of the hierarchy are the CPU registers (very small and very fast), then the next level is a special, high-speed semiconductor memory known as *cache memory* and the last level is the main memory, semiconductor as well, but slower and denser than a cache. The cache memory is usually divided in several distinct

Figure 1.4: Common construction of a memory hierarchy [13]

levels (nowadays, at least 2 or 3 levels) and is situated on the CPU chip itself. This is explained below by how the cache memory works. Figure 1.5 exhibits a common cache memory design.

Because the cache memory acts like an intermediate between the main memory and CPU, it contains copies of data from the main memory. But because it has a small capacity, only some data is copied, depending on which technique is used. Common techniques are based on temporal and spatial locality. Spatial locality is the property that an access to a given memory location greatly increases the probability that adjacent locations will be accessed immediately. Temporal locality is based on the fact that an access to a given memory location increases the probability that the same location will be accessed again. These techniques are used for cache management strategy, when the cache memory is full and free blocks are necessary. Also, common cache memories can be associative, or content-addressable. An associative memory, the address of a memory location is stored along with its content.

When reading from the cache memory, a hit occurs if the needed word is found in a level of the hierarchy, however if a *miss* occurs the request must be sent to the next lower level. So, for multi-level caches, the processor proceeds by checking the smallest *level 1* cache first and if it hits, the processor runs at high speed. If level 1 cache misses though, the next larger *level 2* cache is checked and so on, until the main memory is finally checked.

#### 1.2.5 Low-power systems

This concept is currently employed in most modern chips in order to reduce the *dynamic power* (when the circuit or device is executing instructions – normal operations) and the *static power* (when the device or circuit is in idle mode). Although

Figure 1.5: Components of a cache memory [14]

the density and the speed of integrated circuits computing elements have increased almost exponentially for several decades (trend described by Moore's Law), these are limited primarily by power dissipation concerns [15].

There are several methods and techniques to reduce the power consumption low enough so that the device or circuit still performs in normal parameters. Dynamic power is mainly reduced to a minimum by using a "full static logic" which can stop the clock and hold their state indefinitely, thus using no dynamic power, but they still have a small static power consumption caused by leakage current [16]. The static power appears when there is no switching (idle mode) and it's the result of sub-threshold leakage, which is important if the circuits keep on shrinking. A simple technique to reduce this loss is to raise the threshold voltage and decrease supply voltage, but this will reduce the performance. Some modern circuit use dual supply voltages to provide speed for critical parts of the circuit, and lower power for non-critical paths [17]. Another method is to use sleep transistors to disable entire blocks when not in use.

Another method to reduce the dynamic power when changing states is to reduce the operating voltage of the circuit or to reduce the voltage change involved in a state change (use only a fraction of the supply voltage). For clocked logic circuit, the technique of clock gating [18] is used, to avoid of functional blocks that are not required for a given operation when changing the state.

A power management technique in computer architecture is dynamic voltage scaling [19], where the voltage of a component is increased or decreased, depend-

ing on the circumstances. Undervolting is used to conserve power, especially in devices with a limited energy source. Most modern components and devices allow voltage regulation to be controlled through software (e.g. BIOS).

To summarize, the main advantages of low-power systems is that they have a reduced power consumption, but at the expense of computation power. Several methods, techniques and implementations have been proposed so far, each having its own advantages and disadvantages. However, because the low-power designs depend very much on the architecture of the memory system or on the techniques proposed, examples of low-power implementations are included in each chapter. The low-power aspect is considered in each method and technique from each chapter and mainly focuses on designs that have low power consumption, hence the impact is minimal.

#### 1.2.6 Security in memory systems

Modern day integrated circuits (ICs) contain significant information that must be highly secured, so that it stays hidden. In the last 5 years, there have been reported a large variety of attacks against smartcards and ICs dedicated to security mostly targeting the vulnerabilities of cache and main memories. This problem broadens when the attacks focus on devices used by general public like credit cards and other kind of legal supports containing biometric information [3]. Another report [2] points out that 62% of companies worldwide were subject to payment fraud in 2014 and that credit/debit cards are the second most frequent target of payment fraud. Mobile payments are a relatively new payment method, but this trend is increasing among large companies and organizations. However, there are several uncertainties about it such as disclosure of sensitive information or secure transfer of information.

Ensuring the confidentiality of sensitive information is becoming more and more crucial [3]. Very often general purpose devices like desktops, laptops or smartphones are used for private transactions with financial entities or health-care issues, among others. In the case of devices without specialized hardware, all cryptographic operations are executed in software, resulting in an intensive use of memory [4]. This poses sensitive data at risk, including that stored in the cache memory [20].

Computer systems have drawn a lot of attention, because of the fact that sensitive information is stored in the memory during runtime. Some attacks on the main memory have been investigated because the stored information is still visible a small period of time after the system loses power (known as memory remanence). These attacks, called cold-boot attacks [21, 22], target the recovery of the last information which was stored in the main memory. Thus, relevant information such

1.3. OBJECTIVES 13

as encryption keys could be retrieved. Moreover, by keeping the memory module at low temperatures, the information can remain recoverable for as long as 5 min [21].

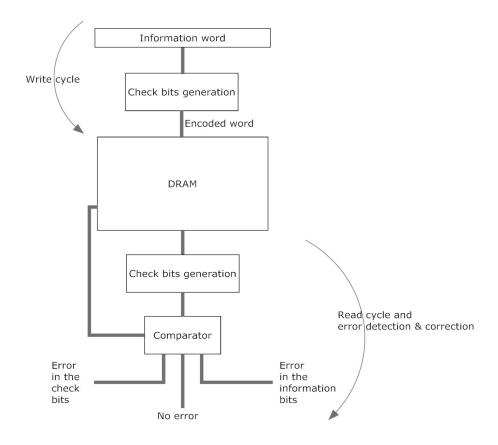

In memory systems, the main memory has usually a low level of protection because it is more accessible than other levels of memory and thus it can be removed by the attacker by simpler technical means. In cold-boot attacks, the information is frozen for a long enough period of time such that the memory modules can be removed and the attacker can download the content into a backup system which stores data in plain text. To avoid this, security is improved by encrypting data while the memory transaction is undertaken [22, 23, 24, 25]. The decrease of bus throughput can be compensated by an increase of L2 cache size.

Unlike the main memory nowadays, for performance reasons, the cache memory is placed in the same central processing unit (CPU) package, either stacked on or embedded within it. This configuration provides a higher protection degree at a free cost. Because of this and also to avoid strong penalty in the throughput between cache and CPU, the information is stored in plain text. Even more, some encryption algorithms are designed to run all the rounds using only cache memory and avoiding main memory transfers [26].

Attacks that target the cache memory and retrieve sensitive data have been analyzed and investigated in several works [24, 25, 26, 27, 28]. Most of these are side-channel attacks, which are based on the information leaked by a cryptographic device, such as power consumption, timings and so on. Attacks against Advanced Encryption Standard (AES) algorithms have been reported that target the stored private keys [24, 25, 26]. It cannot be ruled out the possibility of direct reading of the cache content [27]. If the cache is conveniently frozen, a power-up sequence can derive to the recovery of the same content existing before the power-up [29].

To sum things up, ensuring data security and privacy in digital devices is challenging and, because of the large variety of attacks, there are several methods and techniques that can be implemented. In Chapter 3 and 4, existing security measures are analyzed and discussed, as well as known attacks against memory systems are explained in detail.

### 1.3 Objectives

The main objective of this thesis is to bring new contributions to the self-healing systems domain. In particular, to develop a self-healing technique for memory systems, technique that favors low-power consumption and provides security of data against different types of attacks.

A self-healing low-power memory system is usually achieved by using error

detection and correction codes and/or replacement techniques using spare elements. Data security and privacy on the other hand, can be achieved through several methods and means. Thus, there were defined three major research objectives.

The first one is the design of error detection and correction codes for memory systems. This was motivated by the fact that the memory systems are susceptible to soft and hard errors, in particular, DRAMs present unidirectional errors. This led to the Berger code, an error detection code for unidirectional errors, with a simple and straightforward design. The new codes must also be evaluated from different points of view, such as error detection and correction rate and performance and area overhead. A specific task here is to integrate the proposed codes in a memory system, in order to achieve a self-healing methodology for memory systems. Also, other mitigation techniques can be used, in order to improve the capability of the self-healing technique (especially when dealing with uncorrectable errors). The overall system design must also be evaluated, especially from the perspective of speed, area overhead of additional circuitry and power consumption. The low-power feature is achieved through the design of the proposed codes.

The second research direction is related to data security and privacy in memory systems. Considering the performance peculiarities of cache memories and the existence of a large variety of attacks against them, data scrambling can be used and integrated due to the minimal penalty they impose in performance. Hence, this research direction targets the design and implementation of a novel methodology that can obscure the critical data in the cache memory, rendering it useless for the attacker.

The third and last research direction is to integrate the results of the first two research directions in order to obtain a secure self-healing low-power memory system. The motivation behind is related to power analysis side-channel attacks, in particular simple and differential power or electromagnetic attacks. These types of attacks are widely used in memory systems because they are very powerful and resourceful in breaking systems protected by keys. By combining error detection and correction codes with data scrambling techniques, memory systems can be designed to defend themselves against a large variety of attacks. The overall design must be evaluated in terms of performance, delay penalty, area overhead and security.

In order to better exhibit and demonstrate the objectives, below are some questions (related to the objectives) which are answered in the final chapter, 5.

- Which was the main objective of this thesis?

- Is the main objective accomplished?

- How is the self-healing memory system achieved?

1.4. STRUCTURE 15

- Is the low-power perspective fulfilled?

- How is the security in memories dealt with?

- From the evaluation point of view, can the proposed methodology be considered a good solution?

Can the self-healing technique be further researched and used in other systems?

#### 1.4 Structure

The thesis is organized in five chapters. The first chapter contains a short introduction of the domain and subject of the thesis, motivation, objectives and this sub-chapter Also, the biggest sub-chapter here contains survey of previous works in this domain. It begins with a motivation of the thesis and continues explaining the systems focused in this work. Then, the self-healing concept is presented and afterwards memory systems are described. Note that the review of memory systems contains both SRAM and DRAM, old and new designs. Also, the unidirectional nature of errors is explained and referenced. The security in cache memories is described from several points of view, data scrambling is introduced and power analysis attacks are explained. The rest of the chapter contains recent proposals and implementations of self-healing techniques for memory systems, as well as low-power strategies.

Chapter 2 contains the design of the proposed error detection and corrections codes, which are used for the self-healing technique. The codes are explained and illustrated through several figures and methods. Then, they are analyzed from the following points of view: coding scheme, error localization, error correction and error escapes. For the latter three, metrics are defined, in order to evaluate the code effectiveness. The rest of this chapter contains the integration of the proposed codes into memory systems, presented as DRAM repair strategies.

In Chapter 3, the security in cache memories is illustrated and explained. Data scrambling is presented as a method to obscure the stored data in the cache and the design methodology is exhibited. The implementation is explained, illustrated and evaluated from several points of view. Finally, the experimental results are presented and discussed accordingly.

Chapter 4 consists of the merge between error detection and correction codes from Chapter 2 and the data scrambling technique presented in Chapter 3. The power analysis side-channel attacks are introduced and explained in a sub-chapter and then the methodology proposed against these types of attacks is presented. The

evaluation process contains metrics such as performance, area overhead, power consumption and, in the end, the experimental results are unveiled.

The final Chapter, 5, contains the conclusions of the work, scientific contributions and future research directions.

## **Chapter 2**

# **Unidirectional eDLC**

#### 2.1 Introduction

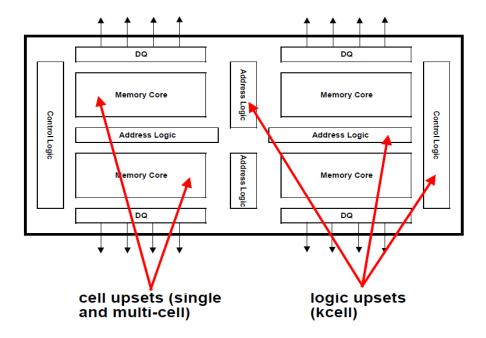

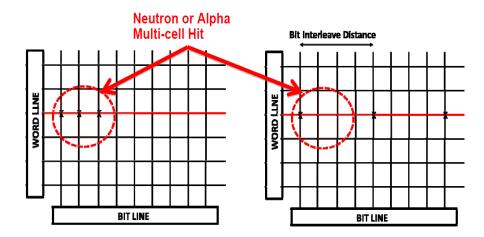

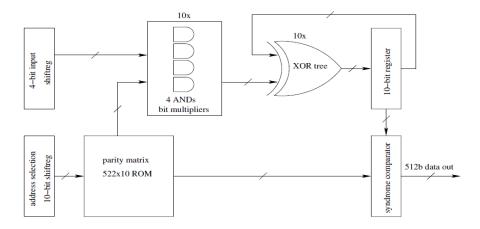

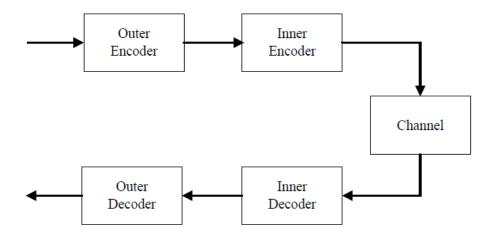

The continuous shrinking of memory cells size as the technology evolves has made them more susceptible to errors. The sources that cause the single or multi cell upsets, and therefore generates multi-bit errors, have been observed and studied intensively. As reported in [30], [31], soft errors due to memory cell upset can be induced from terrestrial cosmic rays (i.e. high-energy neutrons), nowadays more important than alpha-particle induced errors. Because of the high packing density of the DRAM cells, the upset can be on multiple adjacent cells and creating burst errors in the word line [32].

The memory cell upsets in DRAM are unidirectional, which means that the errors occur for all memory cells from 1 to 0 or from 0 to 1, but not in both ways. This is because a charge in the capacitor of the memory cell represents either logic 1 or 0, depending on the implementation [33]. A particle strike can upset the cell, discharging the capacitor, thus changing its original value.