## Multicore architecture optimizations for HPC applications

### by Uglješa Milić

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) i el repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (\*framing\*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="framing">framing</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis the institutional repository **UPCommons** by (http://upcommons.upc.edu/tesis) and the cooperative repository TDX (http://www.tdx.cat/?localeattribute=en) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Multicore Architecture Optimizations for HPC Applications

by UGLJEŠA MILIĆ

Departament d'Arquitectura de Computadors (DAC) Universitat Politècnica de Catalunya (UPC) Barcelona, Spain

Advisor: Dr. Alex Ramírez Co-advisor: Dr. Paul M. Carpenter

### Abstract

From single-core CPUs to detachable compute accelerators, supercomputers made a tremendous progress by using available transistors on chip and specializing hardware for a given type of computation. Today, compute nodes used in HPC employ multi-core CPUs tailored for serial execution and multiple accelerators (many-core devices or GPUs) for throughput computing. However, designing next-generation HPC system requires not only the performance improvement but also better energy efficiency. Current trend of reaching exascale level of computation asks for at least an order of magnitude increase in both of these metrics.

This thesis explores HPC-specific optimizations in order to make better utilization of the available transistors and to improve performance by transparently executing parallel code across multiple GPU accelerators. First, we analyze several HPC benchmark suites, compare them against typical desktop applications, and identify the differences which advocate for proper core tailoring. Moreover, within the HPC applications, we evaluate serial and parallel code sections separately, resulting in an Asymmetric Chip Multiprocessor (ACMP) design with one core optimized for single-thread performance and many lean cores for parallel execution. Our results presented here suggests downsizing of core front-end structures providing an HPC-tailored lean core which saves 16% of the core area and 7% of power, without performance loss.

Further improving an ACMP design, we identify that multiple lean cores run the same code during parallel regions. This motivated us to evaluate the idea where lean cores share the I-cache with the intent of benefiting from mutual prefetching, without increasing the average access latency. Our exploration of the multiple parameters finds the sweet spot on a wide interconnect to access the shared I-cache and the inclusion of a few line buffers to provide the required bandwidth and latency to sustain performance. The projections presented in this thesis show

Contents

additional 11% area savings with a 5% energy reduction at no performance cost. These area and power savings might be attractive for many-core accelerators either for increasing the performance per area and power unit, or adding additional cores and thus improving the performance for the same hardware budget.

Finally, in this thesis we study the effects of future NUMA accelerators comprised of multiple GPU devices. Reaching the limits of a single-GPU die size, next-generation GPU compute accelerators will likely embrace multi-socket designs increasing the core count and memory bandwidth. However, maintaining the UMA behavior of a single-GPU in multi-GPU systems without code rewriting stands as a challenge. We investigate multi-socket NUMA GPU designs and show that significant changes are needed to both the GPU interconnect and cache architectures to achieve performance scalability. We show that application phase effects can be exploited allowing GPU sockets to dynamically optimize their individual interconnect and cache policies, minimizing the impact of NUMA effects. Our NUMA-aware GPU outperforms a single GPU by  $1.5 \times$ ,  $2.3 \times$ , and  $3.2 \times$  while achieving 89%, 84%, and 76% of theoretical application scalability in 2, 4, and 8 sockets designs respectively. Implementable today, NUMA-aware multi-socket GPUs may be a promising candidate for performance scaling of future compute nodes used in HPC.

## Contents

| A  | bstra | nct                                                  | iii  |  |  |

|----|-------|------------------------------------------------------|------|--|--|

| C  | ontei | nts                                                  | iv   |  |  |

| Li | st of | Figures                                              | ix   |  |  |

| Li | st of | Tables                                               | xiii |  |  |

| 1  | Inti  | ntroduction                                          |      |  |  |

|    | 1.1   | High Performance Computing                           | 1    |  |  |

|    | 1.2   | Evolution of a Single Compute Node                   | 3    |  |  |

|    |       | 1.2.1 Multicore Processors                           | 4    |  |  |

|    |       | 1.2.2 Compute Accelerators                           | 5    |  |  |

|    |       | 1.2.3 Multiple Compute Accelerators on a Single Node | 7    |  |  |

|    | 1.3   | Programming Models for Single Node                   |      |  |  |

|    |       | Architectures                                        | 8    |  |  |

|    |       | 1.3.1 OpenMP for Shared Memory Multicore Processors  | 9    |  |  |

|    |       | 1.3.2 OpenACC for Programming Accelerators           | 10   |  |  |

|    |       | 1.3.3 CUDA for Programming GPUs                      |      |  |  |

|    | 1.4   | Thesis Contributions                                 | 12   |  |  |

|    | 1.5   | Timeline                                             | 14   |  |  |

|    | 1.6   | Thesis Organization                                  | 15   |  |  |

| 2  | Bac   | ckground and Related Work                            | 17   |  |  |

|    | 2.1   | From General-purpose to Specialized                  |      |  |  |

|    |       | Systems-on-Chip                                      |      |  |  |

|    | 2.2   | Efficient CMP Design for HPC                         |      |  |  |

|    | 2.3   | More Performance per Compute Node                    | 23   |  |  |

| 3  | Me    | thodology                                            | 27   |  |  |

|    | 3.1   | Code Instrumentation                                 | 27   |  |  |

|    | 3.2   | Simulation Frameworks                                | 28   |  |  |

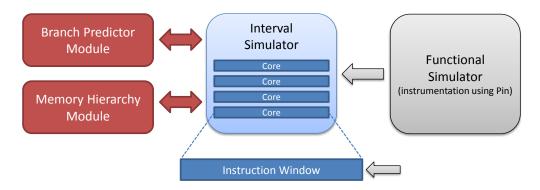

|    |       | 3.2.1 Sniper                                         | 28   |  |  |

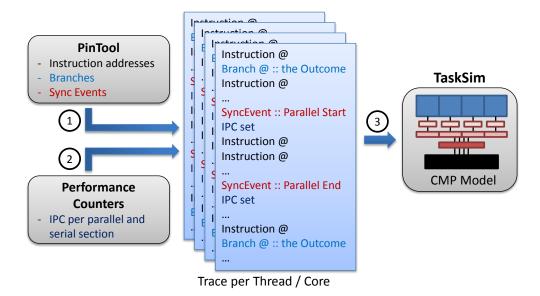

|    |       | 3.2.2 TaskSim                                        | 29   |  |  |

|    |       | 3 2 3 CPUSim                                         | 31   |  |  |

*Contents* vi

|   | 3.3 | Benchmark Suites                                      |    |

|---|-----|-------------------------------------------------------|----|

|   |     | 3.3.1 Workloads for Shared-memory CMPs                |    |

| 4 | HP  | C Workload Characterization                           | 37 |

|   | 4.1 | Microarchitecture Independent                         |    |

|   |     |                                                       | 37 |

|   |     |                                                       | 38 |

|   |     | *                                                     | 39 |

|   |     |                                                       | 41 |

|   |     | 4.1.4 Difference Between Sequential and Parallel Code |    |

|   |     | Sections in HPC Workloads                             | 42 |

|   | 4.2 | Microarchitecture Dependent                           |    |

|   |     |                                                       | 43 |

|   |     |                                                       | 43 |

|   |     | 0                                                     | 47 |

|   |     | 4.2.3 Instruction Cache                               | 48 |

|   | 4.3 | Impact on Performance, Power and Area                 | 50 |

|   |     | 4.3.1 Experimental Setup                              | 51 |

|   |     | 4.3.2 Results                                         | 52 |

| 5 | Sha | ring the I-cache among Lean Cores                     | 55 |

|   | 5.1 | Sequential and Parallel Code within HPC applications  | 55 |

|   | 5.2 | Lean Cores and the Code They Execute                  | 57 |

|   | 5.3 | Shared I-cache Architecture                           | 58 |

|   |     | 5.3.1 Core Front-End                                  | 58 |

|   |     | 5.3.2 Shared I-cache and Interconnect                 | 60 |

|   | 5.4 | Simulation Setup                                      | 61 |

|   | 5.5 | Evaluation                                            | 61 |

|   |     | 5.5.1 Naive I-cache Sharing                           | 62 |

|   |     |                                                       | 64 |

|   |     | 5.5.3 Miss Analysis                                   | 65 |

|   |     |                                                       | 66 |

|   |     |                                                       | 69 |

| 6 | Mu  | lti-socket GPU Design                                 | 73 |

|   | 6.1 | <u> </u>                                              | 74 |

|   | 6.2 |                                                       | 76 |

|   |     |                                                       | 78 |

|   | 6.3 |                                                       | 81 |

|   |     |                                                       | 81 |

|   |     | ·                                                     | 83 |

|   | 6.4 |                                                       | 85 |

|   | 0.1 | <u> </u>                                              | 86 |

|           | ••   |

|-----------|------|

| Contents  | VI   |

| Conticuis | V 1. |

|       | 6.4.2        | Results                                      | 89  |  |  |

|-------|--------------|----------------------------------------------|-----|--|--|

| 6.    | 5 Discus     | ssion                                        | 91  |  |  |

|       | 6.5.1        | Combined Improvement                         | 91  |  |  |

|       | 6.5.2        | Scalability                                  | 93  |  |  |

|       | 6.5.3        | Multi-Tenancy on Large GPUs                  | 94  |  |  |

|       | 6.5.4        | Power Implications                           | 94  |  |  |

|       | 6.5.5        | Scheduling Improvements                      | 95  |  |  |

|       | 6.5.6        | Other Asymmetric Link and Cache Partitioning |     |  |  |

|       |              | Proposals                                    | 96  |  |  |

| 7 C   | onclusio     | $\mathbf{n}\mathbf{s}$                       | 98  |  |  |

| 7.    | 1 Futur      | e Extensions                                 | 10  |  |  |

| 7.5   | 2 Work       | Published                                    | 10: |  |  |

| Bibli | ography      | 1                                            | .05 |  |  |

| Abbı  | bbreviations |                                              |     |  |  |

## List of Figures

| 1.1 | High-level overview of a single core pipeline                                                                                                                                                                     | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Comparison of UMA and NUMA multicore CPUs                                                                                                                                                                         | 5  |

| 1.3 | Accelerated computing offloads parallel portions of the application to the accelerator, while the remainder of the code still runs on the                                                                         |    |

|     | CPU                                                                                                                                                                                                               | 6  |

| 1.4 | Heterogeneous node with one CPU and two GPUs                                                                                                                                                                      | 7  |

| 1.5 | The OpenMP execution flow                                                                                                                                                                                         | 9  |

| 1.6 | Thesis timeline                                                                                                                                                                                                   | 14 |

| 2.1 | Different CMP configurations                                                                                                                                                                                      | 20 |

| 2.2 | Potential speedup obtained by different CMP designs depending on<br>the serial code fraction                                                                                                                      | 21 |

| 2.3 | Percentage of workloads that are able to fill future larger GPUs (average number of concurrent thread blocks exceeds number of SMs in the system)                                                                 | 24 |

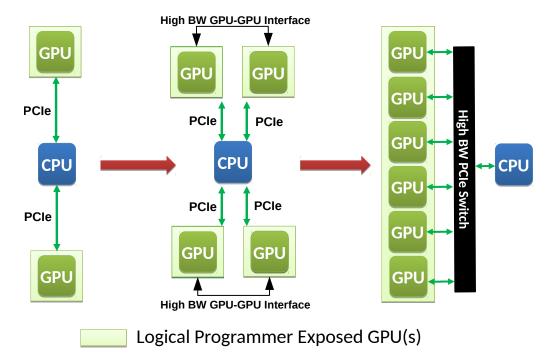

| 2.4 | The evolution of GPUs from traditional discrete PCIe devices to single logical, multi-socketed accelerators utilizing a switched interconnect.                                                                    | 25 |

| 3.1 | Sniper interval simulation model                                                                                                                                                                                  | 28 |

| 3.2 | Temporal flow of a simulation process with TaskSim                                                                                                                                                                | 30 |

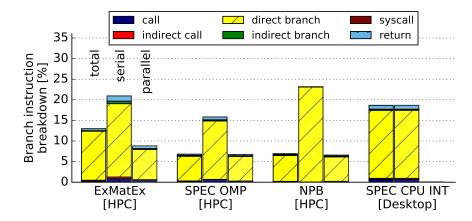

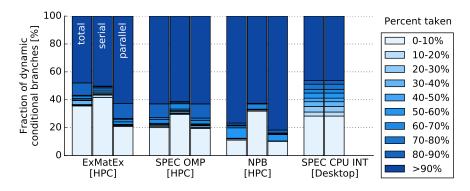

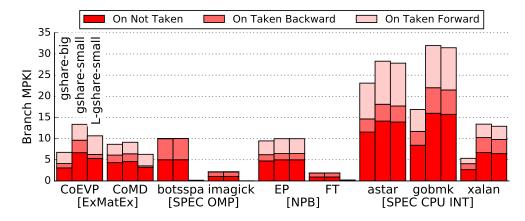

| 4.1 | Dynamic branch instruction breakdown for each benchmark suite as the percentage of total instructions                                                                                                             | 38 |

| 4.2 | Distribution of branch directions. Conditional branches are dominantly decided in one direction, either taken or not taken. Desktop applications have more evenly distributed directions of conditional branches. | 39 |

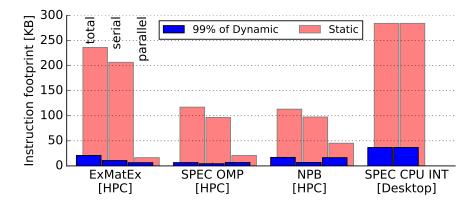

| 4.3 | Static instruction footprint and memory we need to store 99% of dynamic instructions per benchmark suite                                                                                                          | 40 |

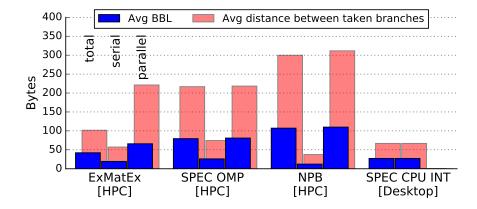

| 4.4 | Average dynamic basic block length and distance between taken                                                                                                                                                     |    |

|     | branches for each benchmark suite                                                                                                                                                                                 | 41 |

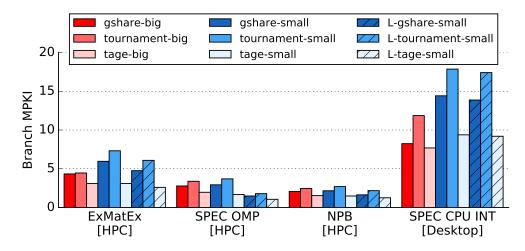

| 4.5 | Branch MPKI for different branch predictor configurations and bench-                                                                                                                                              |    |

|     | mark suites.                                                                                                                                                                                                      | 45 |

List of Figures x

| 4.6  | Branch MPKI breakdown for gshare branch predictor and a subset<br>of workloads. We distinguish mispredictions on not taken, taken                                                                                                                                                                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | backward, and taken forward branches                                                                                                                                                                                                                                                                      | 46 |

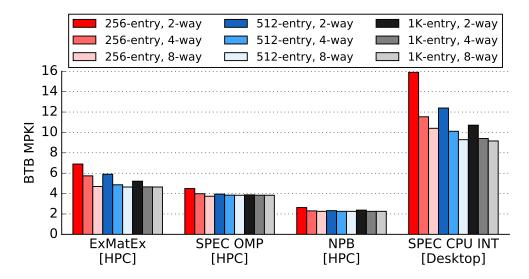

| 4.7  | BTB MPKI for different number of entries and associativity. We                                                                                                                                                                                                                                            |    |

|      | use branch address to index BTB                                                                                                                                                                                                                                                                           | 48 |

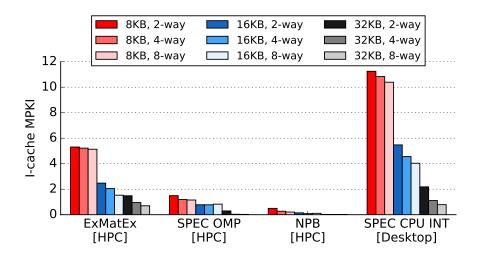

| 4.8  | The average I-cache MPKI values for all benchmark suites. The                                                                                                                                                                                                                                             |    |

|      | cache line is 64 B                                                                                                                                                                                                                                                                                        | 49 |

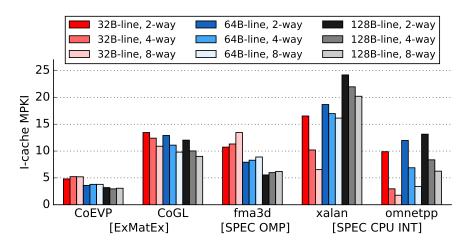

| 4.9  | I-cache MPKI values for some specific benchmarks. The cache size is 16 KB                                                                                                                                                                                                                                 | 49 |

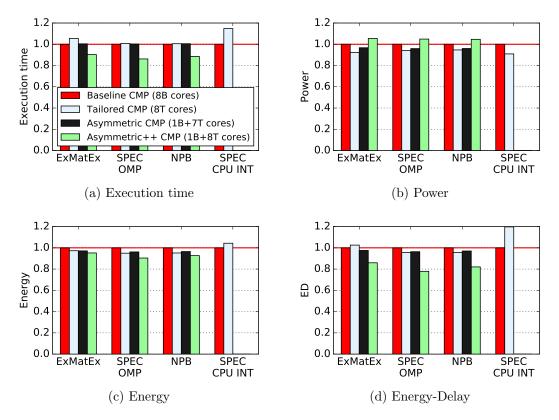

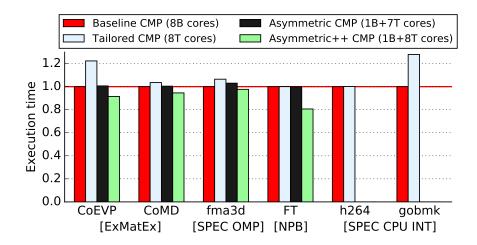

| 4.10 | Normalized execution time, power, energy, and energy-delay (ED) product for different CMP configurations and averaged per benchmark suite. We analyse only cores and L2 caches since the rest of CMP is shared and same for all configurations. Asymmetric++ CMP has the same area budget as Baseline CMP |    |

| 4.11 |                                                                                                                                                                                                                                                                                                           | 52 |

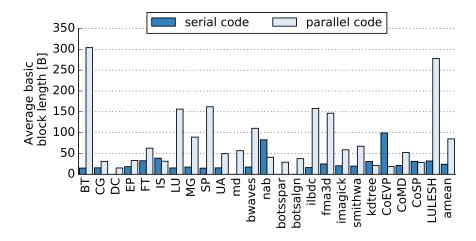

| 5.1  | The average dynamic basic block length in serial and parallel parts of the code                                                                                                                                                                                                                           | 56 |

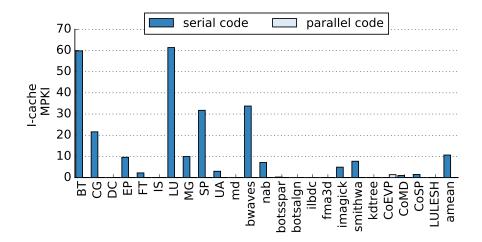

| 5.2  | The I-cache MPKI values in serial and parallel parts of the code using a 32 KB, 8-way associative I-cache with 64 B lines, and LRU replacement policy. The I-cache MPKI values in parallel code are very low                                                                                              | 56 |

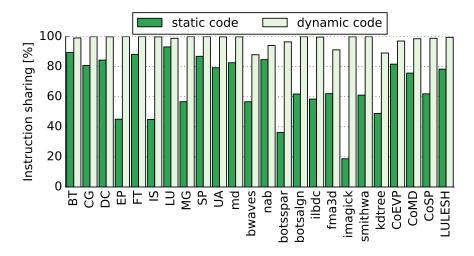

| 5.3  | Percentage of instruction sharing across all threads running on an eight-core CMP per HPC benchmark (parallel sections only)                                                                                                                                                                              | 57 |

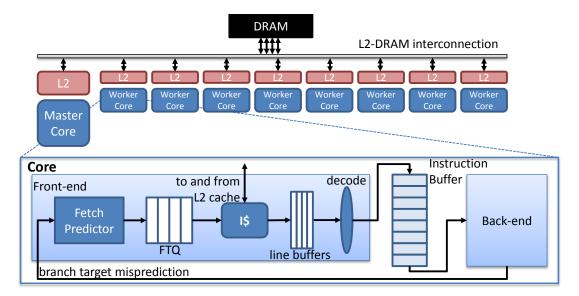

| 5.4  | Baseline ACMP architecture with respect to the instruction part of memory hierarchy.                                                                                                                                                                                                                      | 59 |

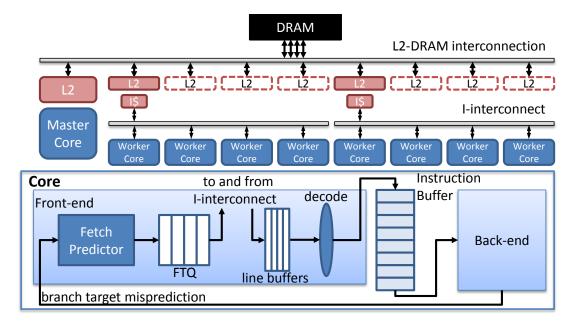

| 5.5  | Shared I-cache ACMP architecture. Master core is not modified                                                                                                                                                                                                                                             |    |

| 5.6  | Naive scaling. Execution time for different levels of sharing a 32 KB I-cache among worker cores. We use four line buffers and a single                                                                                                                                                                   | 00 |

|      | bus as the interconnection network                                                                                                                                                                                                                                                                        | 63 |

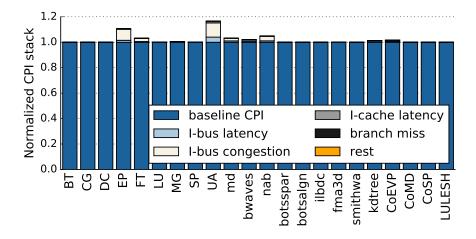

| 5.7  | Naive scaling. Normalized CPI stack per benchmark for the highest level of sharing $(cpc = 8)$                                                                                                                                                                                                            | 63 |

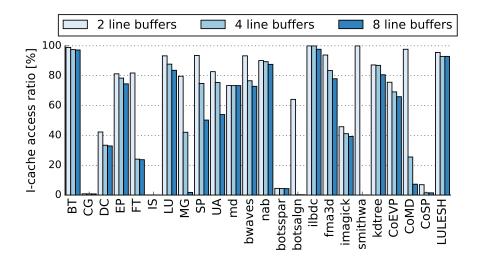

| 5.8  | I-cache access ratio for different number of line buffers. More than eight line buffers does not reduce the I-cache access ratio significantly.                                                                                                                                                           | 64 |

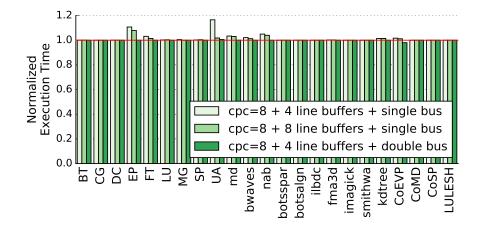

| 5.9  | Trade-off between adding more line buffers and doubling the in-                                                                                                                                                                                                                                           | 04 |

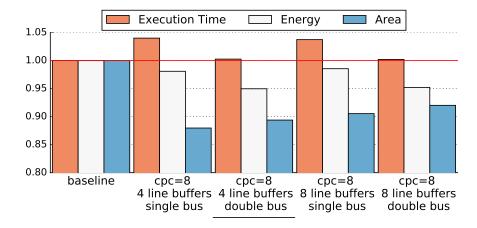

| 0.9  | terconnection bandwidth when a single $16\mathrm{KB}$ I-cache is shared $(cpc=8)$ . The execution times are normalized to the baseline                                                                                                                                                                    | 65 |

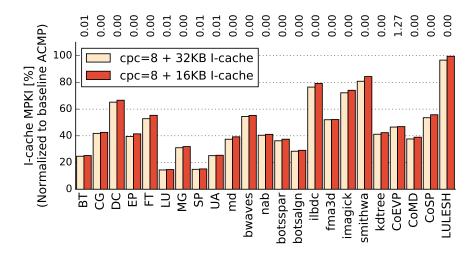

| 5.10 | architecture (private, 32 KB I-caches)                                                                                                                                                                                                                                                                    | 65 |

|      | MPKI values for each benchmark with private I-caches                                                                                                                                                                                                                                                      | 67 |

List of Figures xi

|      | Energy and area savings adding more line buffers and doubling the interconnection bandwidth when a single 16 KB I-cache is shared $(cpc=8)$ . All the values are normalized to the baseline architecture and averaged across the benchmarks | 68<br>69 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.1  | Schematic representation of proposed transparent multi-socket GPU                                                                                                                                                                           |          |

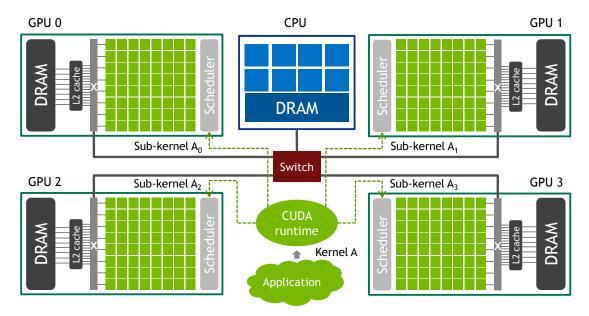

| 0.1  | system consisting of four GPU sockets and one CPU                                                                                                                                                                                           | 74       |

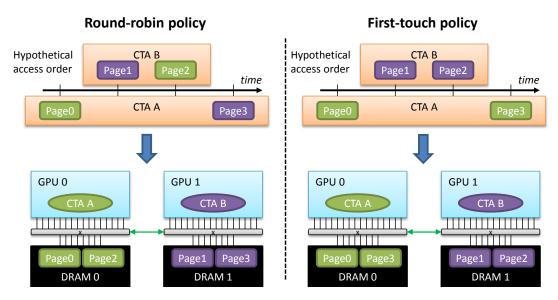

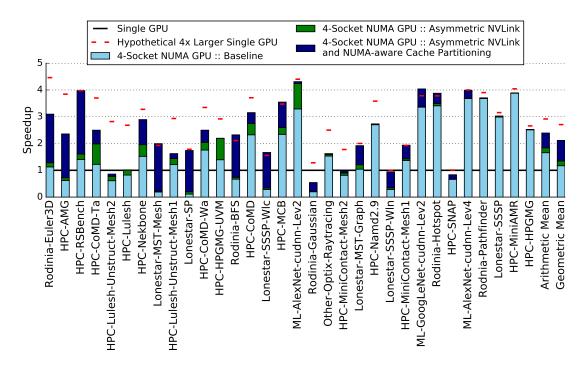

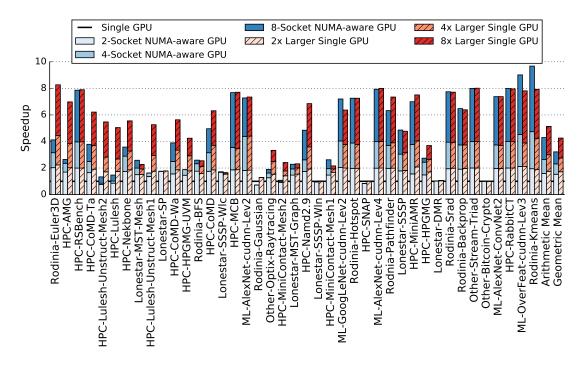

| 6.2  | Comparison of round-robin and first-touch allocation policies on a dual-GPU system.                                                                                                                                                         | 77       |

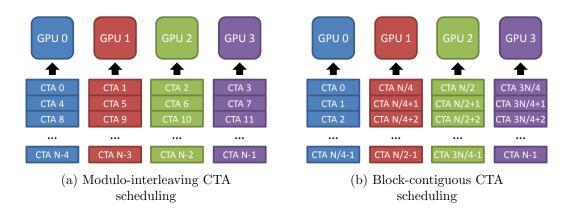

| 6.3  | Comparison of traditional and locality optimized CTA scheduling                                                                                                                                                                             | 78       |

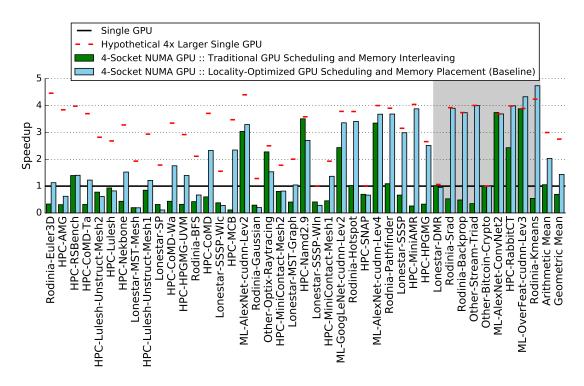

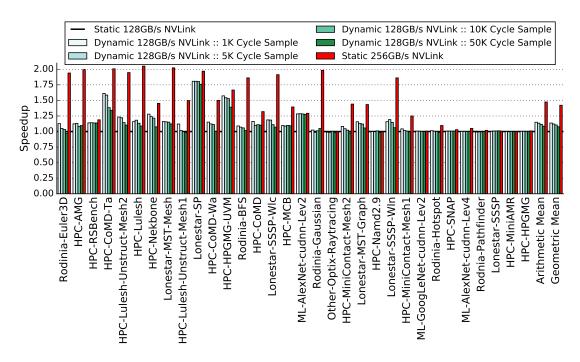

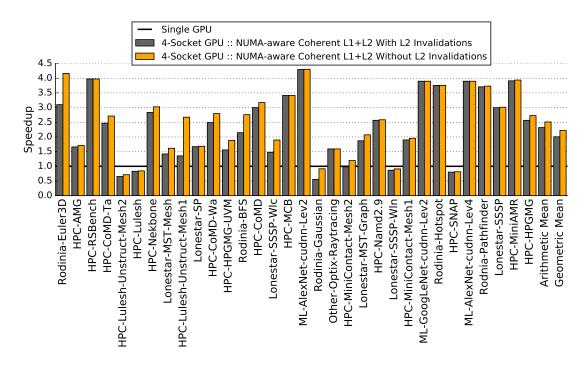

| 6.4  | Performance of a 4-socket NUMA GPU relative to a single GPU and a hypothetical 4× larger (all resources scaled) single GPU. Applications shown in grey achieve greater than 99% of performance                                              | 70       |

| 6.5  | scaling with SW-only locality optimization                                                                                                                                                                                                  | 79       |

| 0.0  | ciency                                                                                                                                                                                                                                      | 80       |

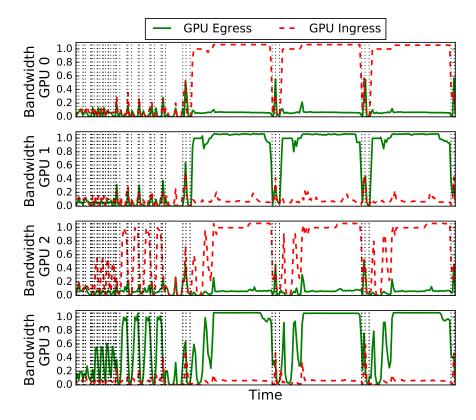

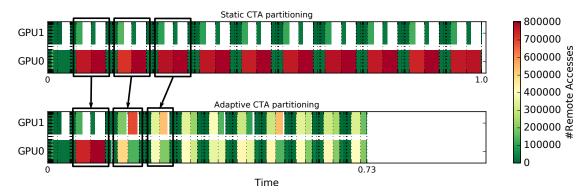

| 6.6  | Normalized link bandwidth profile for HPC-HPGMG-UVM showing asymmetric link utilization between GPUs and within a GPU. Vertical                                                                                                             |          |

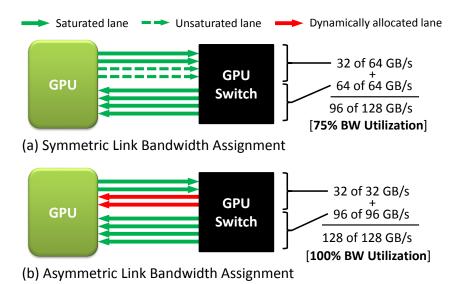

| 6.7  | black dotted lines indicate kernel launch events                                                                                                                                                                                            | 82       |

|      | bandwidth.                                                                                                                                                                                                                                  | 84       |

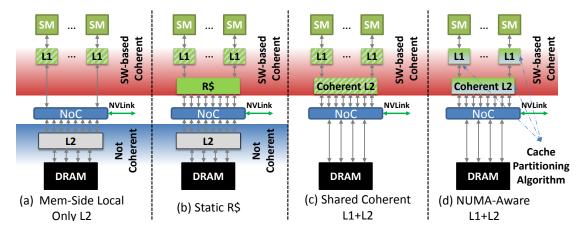

| 6.8  | Potential L2 cache organizations to balance capacity between remote and local NUMA memory systems                                                                                                                                           | 85       |

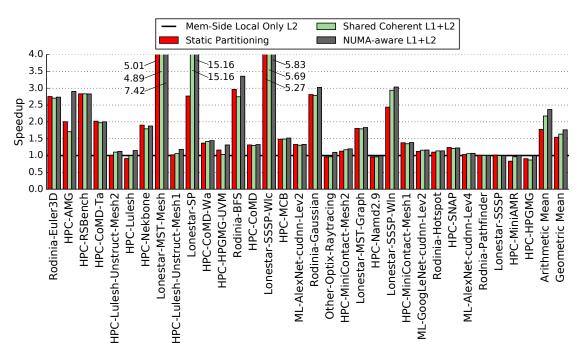

| 6.9  | Performance of NUMA-aware dynamic cache partitioning in a 4-socket GPU compared to memory-side L2 and previously proposed                                                                                                                   |          |

|      | static partitioning                                                                                                                                                                                                                         | 89       |

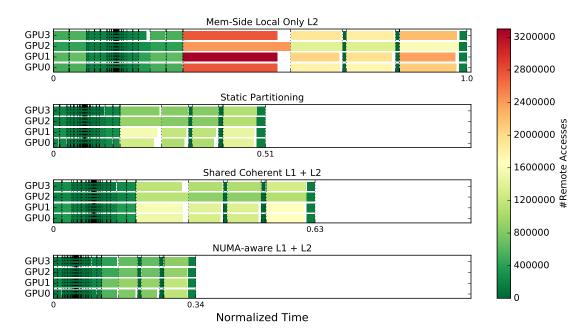

| 6.10 | How different L2 cache organizations shown on Figure 6.8 affect the execution time in case of HPC-AMG. Vertical dotted lines stand for                                                                                                      |          |

| C 11 | kernel launch events while colors show the number of remote accesses.                                                                                                                                                                       | 90       |

| 0.11 | Performance overhead of extending current GPU software based coherence into the GPU L2 caches                                                                                                                                               | 91       |

| 6.12 | Final NUMA-aware GPU performance compared to a single GPU                                                                                                                                                                                   | JI       |

| 0.12 | and 4× larger single GPU with scaled resources                                                                                                                                                                                              | 92       |

| 6.13 | NUMA-aware 1–8 socket GPU scalability compared to hypothetical                                                                                                                                                                              |          |

|      | larger single GPU with scaled resources                                                                                                                                                                                                     | 93       |

| 6.14 | Time line of HPC-Lulesh with 10 time-steps executing on a dual-socket GPU. Vertical dotted lines stand for kernel launch events,                                                                                                            |          |

|      | and color intensity represent the number of remote memory accesses.                                                                                                                                                                         | 95       |

## List of Tables

| 3.1 | Evaluated shared-memory OpenMP benchmarks                                                                                                                                               | 33 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Evaluated CUDA applications with memory footprint and time weighted average number of thread blocks available during execution.                                                         | 34 |

| 4.1 | The average percentage of backward and forward taken branches per benchmark suite                                                                                                       | 39 |

| 4.2 | Size parameters and hardware cost of evaluated branch predictors. Parameter $n$ stands for the number of address bits used to index                                                     |    |

|     | the tables, and parameter $m$ stands for branch history length                                                                                                                          | 44 |

| 4.3 | I-cache, BP, and BTB share in total area and power budget on a Cortex-A9 core level. BP has 12-cycle miss penalty. The numbers are obtained using McPAT and CACTI tools with processing |    |

|     | technology of 40 nm                                                                                                                                                                     | 53 |

| 5.1 | Configuration parameters for the simulated ACMP                                                                                                                                         | 62 |

| 6.1 | Simulation parameters for evaluation of single and multi-socket                                                                                                                         |    |

|     | GPU systems                                                                                                                                                                             | 75 |

| 6.2 | Cache partitioning procedure for NUMA-aware L1 and L2 caches                                                                                                                            | 88 |

## Chapter 1

### Introduction

### 1.1 High Performance Computing

Theory and experimentation have stood as vital tools for solving problems and challenges since the beginning of scientific methodology. Today, major breakthroughs in all areas of science and engineering depend on computational approaches. Scientific computing is widely used in situations where solving a problem using traditional scientific methods may be dangerous, even impossible, too expensive, time-consuming, or too complex. Modeling real systems on a computer, researchers are able to gain new insights in fields such as weather prediction, fluid dynamics, stochastic probability, molecular interaction, pattern recognition, new material characterization, machine learning, etc.

In order to solve even larger problems, with less time and higher accuracy, researchers and engineers turn to *High Performance Computing* (HPC). HPC generally refers to a practice of using clusters of computers, called *compute nodes*, that work together running a particular workload, and thus delivering higher performance than a single desktop computer or workstation. Large clusters of computers form a *supercomputer*, a system with many compute nodes connected through a fast interconnection network with access to a distributed and shared storage system. Today's computer technology is driven by the development of supercomputers with architectures and organizations that moved from traditional sequential machines to parallel and distributes systems. Given that most challenging problems

always require more resources than can be provided by the fastest available supercomputer, the need for a system that provides more performance is continuously present [1].

Supercomputers nowdays stand as a serious long-term investment in research and science. The Top500 site [2] maintains a list of the most powerful supercomputers in the world. In general, supercomputers represent large installations with significant cost of deployment and maintenance. Looking at the order of magnitude values, they cost  $\sim 10$ s of millions US dollars, occupy  $\sim 100$ s of m<sup>2</sup> in area, consume  $\sim 10s$  of MW in power, and provide  $\sim 10s$  of Petaflops performance (10<sup>15</sup> of floating point operations per second). For example, Europe's fastest supercomputer, named Piz Daint [3], achieves theoretical peak performance of 7.8 Petaflops comprising 5272 compute nodes and drawing 1.3 MW of power. With such a high cost of utilizing and running these systems, the current trend in HPC is not only to increase the performance of future supercomputers but also to improve their energy-efficiency (FLOPS per watt). There is a global effort to build the first capable exascale computing system (performance of an Exaflops) which operates in a power envelope of 20 to 30 MW [4]. To reach this goal, the Piz Daint supercomputer would have to improve its performance by  $\sim 100 \times$  but also its FLOPS/W ratio by  $\sim 10 \times$ .

HPC applications implement parallel algorithms to make use of systems such as supercomputers. A programmer is responsible for identifying the parallelism and writing the parallel code using explicit constructs provided by the programming model. The most popular and standardized model for distributed memory architectures is Message Passing Interface or MPI [5]. Typically, an application spawns multiple processes, one process per node, decomposing the computational workload and distributing its data across local memories. Communication between processes is achieved through explicit data movement from the address space of one process to that of another through cooperative operations on each process. Interchangeably switching between computation and communication phases, processes iterate over input data, converging to the solution. In a well designed algorithm, most of the time is spent inside computational phases. Improving the performance of a single compute node directly translates to shorter execution time of the entire application. This thesis focuses on optimizing the hardware budget and improving the performance on a compute node level.

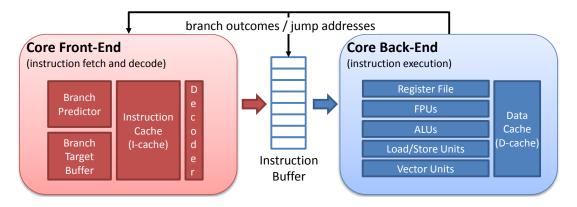

Figure 1.1: High-level overview of a single core pipeline.

### 1.2 Evolution of a Single Compute Node

Initially, compute nodes accommodated one or few single-core processors with local main memory, designed for floating point performance [6]. Throughout most of the 80's and 90's, engineers were able to design more capable CPUs by making use of more available transistors on chip, a driving performance force known as Moore's Law [7]. With more transistors, CPUs became more complex trying to optimize the execution flow and do more work per cycle. Cores were able to commit multiple instructions per cycle through out-of-order execution, speculation, predication, onchip cache memories, data prefetching, etc. As shown in Figure 1.1, general core execution pipeline can be divided into core front-end, responsible for instruction fetching and decoding, and core back-end, in charge of executing and committing instructions. These two mechanisms act as a 'producer' and 'consumer', connected through the instruction buffer. With multiple units tailored for different types of instructions and out-of-order execution, core back-end is capable of consuming more than one instruction per cycle (IPC). To keep these pipeline stages busy, the core front-end also had to be improved with complex branch prediction, instruction prefetching, and decoding more instructions at the time. Many complex features are implemented in today's cores to increase fetch bandwidth, such as multiple branch predictions per cycle [8], instruction alignment [9], branch target buffer [10], trace cache [11], etc. Together with the IPC improvement, as the size of transistors shrunk, power was proportional to the area of the transistors so the entire core could operate at higher frequencies for the same power, a trend known as Dennard's Scaling [12]. Architectural innovations in exploiting instruction level parallelism (ILP) and frequency scaling were the two main sources of continuous improvement of single-core performance.

#### 1.2.1 Multicore Processors

In approximately 2004, processor engineers had reached the transistor size where Dennard's Scaling could not be applied anymore. More transistors were available coming from Moore's Law but it was not possible to keep the power envelope constant anymore. Energy consumption became a new constraint introducing energy-efficiency as a key metric for designs. Thus, major vendors moved to multicore processors giving up on higher clock rates. To exploit this peak performance provided by a multicore CPU, applications had to be rewritten and parallelized by exposing thread level parallelism (TLP).

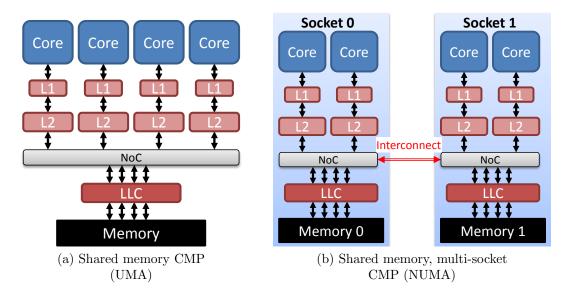

The first chip multiprocessors (CMP) were symmetric, with the same multiple cores interconnected and attached to the shared local memory. This approach simplified the runtime management and user's view of a system given that a running process can be executed on any of the existing cores providing the same performance. With multiple cores on chip, the memory subsystem had to be improved. A small amount of fast memory, or cache, was added per core, keeping data close to the CPU and available for reuse without extra cycles to store and fetch data from slow main memory. Typically, CMPs today implement several levels of cache hierarchy, with the closest ones to the core being private (L1 and L2), and the last one (LLC) being shared. Furthermore, L1 cache is usually separated, with one part storing instructions (I-cache) and another reserved for data (D-cache). Symmetric CMPs with a single main memory are known as Uniform Memory Access (UMA) CMPs since the memory access time does not depend on the memory location. Figure 1.2a depicts a typical UMA CMP. It shows a four-core CMP where each core has private L1 and L2 caches, with all the L2s connected to the shared LLC and main memory through the network on chip (NoC).

With more cores per CMP, UMA organization became unscalable as the memory capacity per core and the memory bandwidth between cores and main memory could not follow the increase in compute performance. One way to address this issue was by introducing multi-socket nodes with Non-Unified Memory Access (NUMA) CMPs. Cores are organized into sockets each with its own local memory. The memory of other socket is accessible but the latency is increased. Figure 1.2b shows a dual-socket CMP with two cores per each socket. A running thread on Socket0 can access the data stored in Memory1 but this remote memory access takes more cycles than accessing local data. Multi-socket NUMA organizations

Figure 1.2: Comparison of UMA and NUMA multicore CPUs.

stand as a favorable design increasing the total number of cores, total memory capacity, and memory bandwidth. Still, it introduces a complexity for users and runtime systems. To extract the maximal performance, the number of remote memory accesses has to be reduced, with processes fetching its data mostly from the local memory.

### 1.2.2 Compute Accelerators

Architects start designing more energy-efficient CMPs with the end of Dennard scaling. This includes workload characterization and appropriate hardware optimization. HPC applications usually consist of sequential and parallel code regions. Cores in a CMP have already been designed to improve scalar performance, with power-hungry pipeline stages able to exploit available ILP. On the other side, parallel code sections in HPC workloads have different characteristics compared to serial code. Relaying on the abundant TLP, and for a given area and power budget, it was more beneficial to implement many low-power cores instead of a few heavyweight ones. According to Amdahl's law [13] and with more cores on a chip and increasing available TLP, the sequential part of the code eventually becomes the bottleneck. To support both serial and parallel code executions, supercomputers start employing accelerators together with the latency-optimized CMPs, forming heterogeneous compute nodes.

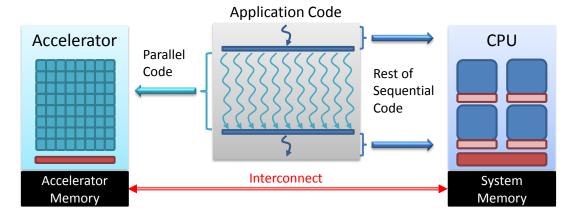

Figure 1.3: Accelerated computing offloads parallel portions of the application to the accelerator, while the remainder of the code still runs on the CPU.

The main idea was to offload the compute intense part of an application to be executed on the accelerator. General overview of the execution flow is shown on Figure 1.3. Accelerators base their compute power and energy-efficiency by exploiting data parallelism, executing the same instructions or tasks on different data portions in parallel. Since the early 2000s, the fastest supercomputers from the Top500 and the most energy-efficient ones from Green500 [14] lists have used various computer accelerators.

ClearSpeed first introduced its CSX600 accelerator designed for HPC applications [15]. It was based on a Single Instruction Multiple Data (SIMD) execution model, with an array of 96 processing elements running under 25 W of power envelope. At that time, rewriting HPC code for a specific hardware was not a popular practice, and manufacturing an HPC accelerator was not profitable for the company. Luckily, video and gaming industry was driving the development of data parallel accelerators. IBM presented its Asymmetric CMP (ACMP) design with the Cell/B.E. and PowerXCell architectures [16] implementing one big and 8 energy-efficient cores. In 2008, supercomputer Roadrunner [17] was ranked first on Top500 and fourth on Green500 list, with 12960 IBM PowerXCell and 6480 AMD Opteron dual-core processors. Following the path, Intel developed its Larrabee [18] and Xeon Phi [19] throughput-oriented CMP with many lean cores targeting both graphics and HPC workloads. NVIDIA and AMD offered their graphical processing units (GPUs) [20] originally designed for multi-dimensional rendering in video games. Today, HPC-optimized GPUs implement massively parallel architectures with thousands of processing units reaching peak performance of  $\sim 10$  Teraflops

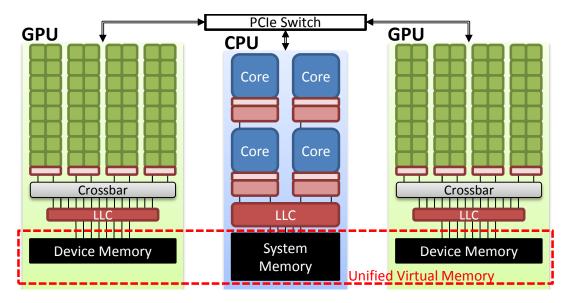

Figure 1.4: Heterogeneous node with one CPU and two GPUs.

and memory bandwidths of  $\sim 1 \, \mathrm{TB/s}$  making them particularly suitable for data parallel HPC workloads [21].

### 1.2.3 Multiple Compute Accelerators on a Single Node

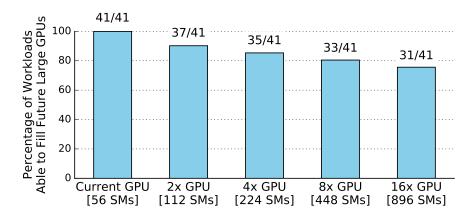

With the increased amount of data to be processed, HPC workloads contain sufficient data parallelism to fill accelerators that are  $2-8 \times$  larger than today's biggest GPU. For that reason, current systems implement nodes with one CMP optimized for serial and multiple devices (many-core accelerators or GPU) for parallel execution, interconnected through PCIe links or some other proprietary low-latency, high-bandwidth interconnect. At the moment, the most energy-efficient supercomputer on Green500 list is NVIDIA's DGX SATURNY, made out of compute nodes with 8 GPUs, for 9462 Megaflops/W. Figure 1.4 presents the example of a heterogeneous compute node with two GPUs deployed as accelerators. The CPU is optimized for single-thread performance and latency, with several levels of cache hierarchy, large control units, large main memory, and low memory bandwidth. Contrarily, the GPUs are designed for parallel performance and throughput, with many simple floating-point and integer units, simplified control logic, and small caches. To provide enough data to this increased amount of processing elements, GPUs have high-bandwidth main memory, typically smaller in capacity compared to the one in CPUs. With multiple physical memories available on a node, the problem of optimal data placement still exists, just as for multi-socket NUMA

CMPs. Current runtime systems lessen the burden on the programmer by allowing different memories to appear as a single unified memory space. Code complexity is reduced since explicit data movement is no longer required. However, to gain the most of performance, developers need to optimize the application by providing data placement hints to the compiler and runtime.

In this thesis, we try to optimize the compute nodes for parallel code execution. The focus is on reducing the execution time as well as power and area consumption through better utilization of available transistors on chip. For many-core accelerators we evaluate the idea of sharing the first level instruction cache (I-cache) among multiple low-power cores. For the applications that provide parallelism even beyond a single GPU accelerator, we study the architectural improvements needed for efficient and transparent multi-GPU executions.

# 1.3 Programming Models for Single Node Architectures

The variety of single node architectures comes with the same variety of programming models. Every time architects introduce performance improvement by exploiting new parallelism, applications had to be rewritten. The vector era of the 1970s and 1980s brought code vectorization in order to exploit vector processors. When commodity scalar processors connected by a network proved to be more cost-effective than vector machines, algorithms were again redesigned for parallel programming using MPI. With CMPs, the next boost in performance came from parallelization across multiple cores sharing a single physical memory. Each MPI process had to be further parallelized spawning multiple threads, typically one thread per core. With the rise of NUMA systems, programming models had to provide the interface to the users for optimal data placement, process and thread scheduling, synchronization, use of specific on-chip memories, etc. Heterogeneous nodes introduced yet another code adaptation, with parallel code being executed on different instruction set architecture (CPU vs GPU) thus requiring different set of compilers and libraries. Code rewriting and tunning for new architectures and programming models stand as a serious decision for HPC users.

#### **Sequential Code OpenMP Parallel Code Program Start** void main() void main() Master Thread int N = ReadInputSize(); **Parallel Region** int N = ReadInputSize(); #pragma omp parallel for FORK for (int i = 0; i < N; i++) for (int i = 0; i < N; i++) HugeComputation(i); HugeComputation(i); Worker Threads Master Thread

Figure 1.5: The OpenMP execution flow.

### 1.3.1 OpenMP for Shared Memory Multicore Processors

As multicore processors emerged, there was a need to provide a portable, standardized, and scalable programming model for users to parallelize their applications. OpenMP [22] stands as an interface, specified for C/C++ and Fortran programming languages, that provides a way for the sequential programs to expose their thread based parallelism. It is designed for multicore, shared memory UMA or NUMA machines. The main idea is to identify the most time consuming parts of a workload, typically loops, and distribute the loop iterations across multiple threads by inserting compiler directives. OpenMP uses the fork-join model of parallel execution. An application starts as a sequential program run by the master thread. At the moment it reaches a directive for creating a parallel region (#pragma omp parallel), the master thread creates a team of worker threads now running in parallel (fork), usually one thread per core. Upon termination, all threads synchronize, leave the parallel region with only the master thread to continue the execution (join). Worker threads do not maintain the exact consistency thus it is a programmer responsibility to ensure the correct update of shared variables by using critical sections, semaphores, or atomic operations. Figure 1.5 compares the sequential and OpenMP version of the same code section. In case of serial code, a single thread iterates N times and performs some long computation for each iteration. Just by inserting #pragma omp parallel for directive, OpenMP version spawns multiple worker threads, running them in parallel. Each thread takes only a subset of iterations in this parallel loop. For example, if we create 8 threads inside the parallel region, thread0 computes only for i in [0, N/8), thread1 for i in [N/8, N/4), etc.

Parallelizing an application using OpenMP may be as simple as inserting oneline compiler directives inside a serial version, but it also provides a rich set of calls for more performance tuning. For example, by setting different environment variables, an advanced user can impose better loop distribution if the default one provides a significant load imbalance. Some applications may prefer to run neighboring threads on the same socket to make use of constructive data prefetching in the shared memory structures (main memory or LLC). To exploit this program behavior, an OpenMP runtime may define proper thread to core binding. Recently, OpenMP added new constructs to support task-based parallelism and efficient execution on vector units [23]. With the appearance of accelerators, runtime now supports the offload of parallel regions to another device, GPU or many-core CMP. Due to its simplicity and support from major hardware and software vendors, OpenMP is today a standard programming model for parallelism on a node level in HPC. In this thesis, we evaluate OpenMP applications running on HPC systems, find some intrinsic properties, and propose better hardware utilization on a CMP level to increase the performance per power and area unit.

### 1.3.2 OpenACC for Programming Accelerators

OpenACC [24] is short for Open Accelerators, the effort of applying directive-based programming to compute accelerators. The idea of OpenACC is similar to OpenMP, with the extension that compiler hints should be portable across accelerators of various kinds. The main advantage of this programming model is performance portability. The most popular accelerators (many-core devices from Intel and ARM, GPUs, FPGAs) have different parallelism profiles, different amounts of SIMD parallelism, number of cores, and different sorts of sharing inside the memory hierarchy. In order to extract performance from a single code version, OpenACC provides flexibility in how that parallelism gets mapped to the target hardware.

Still, with portability comes less performance. The advanced users tend to narrow the gap between peak theoretical and achieved performance, turning to code redesigning and tuning.

#### 1.3.3 CUDA for Programming GPUs

Developed by NVIDIA, the Compute Unified Device Architecture (CUDA) programming model [25] allows a user to program GPUs as compute accelerators where sequential code runs on the CPU (also known as host) and parallel code runs on one or more GPUs (devices). An application written with CUDA is launched on the host, manages physical memories on both the host and device, and invokes kernels which are parallel code sections executed on the device. These kernels are run by many GPU threads grouped in thread blocks or cooperative thread arrays (CTAs). Each block is executed by one SM and does not migrate, while the number of concurrent blocks that can reside on SM depends on available resources (register and on-chip memory usage). Threads within a CTA can synchronize and communicate, while different CTAs can not, and the program correctness should not depend on the order of CTA execution. Different threads and blocks can be distinguished by their unique ID making them easier to identify and distribute the workload. Blocks make a grid which presents a top level abstraction of thread hierarchy. The number of threads per block and the number of blocks in a grid can be set at runtime for each kernel launch. The device itself is consisted of streaming multiprocessors (SM) so that each block of threads is running on one of them. Threads within a block are grouped into warps as a basic unit of scheduling. All threads in a warp execute the same instruction since they share same program counter but operate on different data. This design point is similar to vector units in CPUs, where initial instruction fetching and decoding is the same for all threads in a warp, thus doing it once per warp instead of once per thread saves the energy.

Communication and data transfers between the host and CUDA device is done using global memory. It is the largest but also the slowest one in memory hierarchy on a GPU. Each thread from any block can both read and write to global memory. Beside that, each SM has small programmable shared memory and/or non-programmable D-cache. Proper and extensive use of on-chip shared memory can significantly increase performance of kernels. In GPUs, a prolonged memory access causes a current running warp to stall. The warp scheduler on a SM then picks some other warp that has ready operands for its next instruction. With a huge number of threads running, SMs in a GPU switch between warps hiding the memory latency. This Single Instruction Multiple Threads (SIMT) execution is similar to fine-grained multithreading on CPUs [26, 27], while threads in a warp

execute the instructions like vector units [28]. To provide data to all the running threads, memory hierarchy is designed for bandwidth. Per-SM cache structures filter the memory accesses going to global memory and coalesce potential cache misses.

Until CUDA version 4, users had to explicitly allocate memory on host or device and copy data before they launch a kernel to run on a GPU device. CUDA has supported Unified Virtual Addressing (UVA) since CUDA 4, which provide a single virtual memory address space for all physical memories in the system. This feature simplified the user code complexity by allowing mem-copy calls to be used without exactly knowing where data resides. Still, UVA does not automatically migrate data from one physical location to another. CUDA 6 [29] introduced a concept of Unified Virtual Memory (UVM) where the runtime automatically migrates data from one physical memory to another (CPU or GPU) making any data accessible to the both CPU and GPU(s) using a single pointer. CUDA 8 [30] further improved UVM by enabling on-demand page migration and using system-wide atomic operations. Our optimizations in multi-GPU compute nodes are based on these features.

Extracting the maximal performance from a GPU device requires significant application tuning and knowledge of both programming model and underlying hardware organization. Attractive with the theoretical peak performance they provide, GPUs are the most commonly used accelerators in HPC today. As stated above, the current trend for supercomputers is to have multiple GPU devices per compute node. To utilize them, yet another code rewriting is needed, typically partitioning serial code into multiple contexts (MPI processes or OpenMP threads), one context per GPU. Parallel code is again enclosed into kernels, now launching them on every GPU. This thesis explores the architectural enhancements needed to support efficient and transparent execution on multi-GPU systems.

### 1.4 Thesis Contributions

The main objective of this thesis is to optimize the hardware budget and improve the performance of compute nodes used in HPC. The following are summarized novel contributions of this thesis, while we provide more details in the following chapters.

- We first focus on the HPC code characteristics and core front-end which factors around 30% of core power and area on the emerging lean-core type of processors used in HPC. Separating serial from parallel code sections inside applications, we characterize HPC benchmarks and compare them to a traditional set of desktop integer workloads. HPC applications have biased and mostly backward taken branches, small dynamic instruction footprints, and long basic blocks. Our findings suggest smaller branch predictors (BP) with the additional loop BP, smaller branch target buffers (BTB), and smaller I-caches with wider lines. The difference between serial and parallel code sections in HPC applications points to an ACMP design, with one baseline core for sequential and many HPC-tailored cores designed for parallel code. Without performance degradation, we demonstrate potential power and area saving by 7% and 16% respectively, by avoiding over and under provisioning of hardware resources.

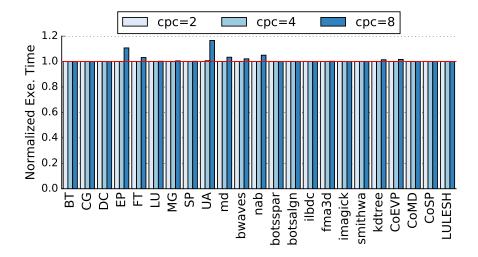

- With the previous findings, we also detect that parallel threads in HPC applications execute the same code at approximately the same time. This makes sharing the core front-end structures a potentially beneficial solution. We explore further tailoring of an ACMP design for HPC by sharing a smaller I-cache among worker cores. Our analysis of the multiple parameters finds the sweet spot on a wide interconnect to access the shared I-cache and the inclusion of a few line buffers to provide the required bandwidth and latency to sustain performance. The evaluation on a rich set of HPC benchmarks shows 11% area saving with 5% energy reduction at no performance cost.

- With more lean cores available on chip, we are entering the area of accelerators and GPUs. Most of the single-GPU optimized workload already contain sufficient data parallelism to fill even larger GPUs than we have to-day. Transparent workload scaling seems attractive from the programmers perspective. We examine the performance of a future multi-socket GPU to understand the effects that NUMA will have when executing applications designed form UMA GPUs. Optimizing GPU microarchitecture for NUMA-awareness is essential to preserve data locality and reduce the inter-socket

Figure 1.6: Thesis timeline.

bandwidth. To overcome this bottleneck we propose two classes of improvements. First, we show that inter-socket links should be dynamically and adaptively reconfigured at runtime to maximize link utilization. Second, we propose that GPU caches should be made NUMA-aware and dynamically adapt their caching policy to minimize NUMA effects. Our NUMA-aware GPU outperforms a single GPU by  $1.5\times$ ,  $2.3\times$ , and  $3.2\times$  while achieving 89%, 84%, and 76% of theoretical application scalability in 2, 4, and 8 sockets designs respectively. We show that multi-socket NUMA-aware GPUs can allow traditional GPU programs to scale efficiently, providing significant room before developers must re-architect applications to obtain additional performance.

### 1.5 Timeline

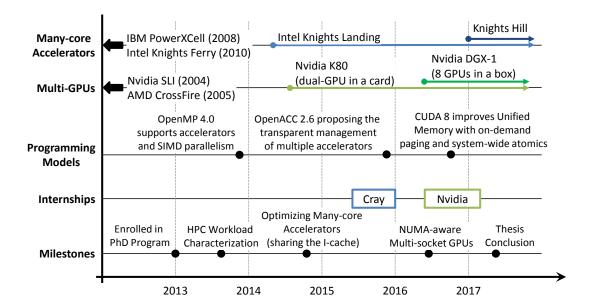

Figure 1.6 gives an overview of the major thesis milestones, within a context of related events coming from the industry. By the time work on this thesis had started, IBM with PowerXCell and Intel with Knights Ferry already have introduced compute accelerators for HPC. OpenMP Advisory Board followed up with support for compute offloading to accelerators and SIMD parallelism for vector units. As Intel continued to improve the single-thread performance of their cores

in Knights Landing, in this thesis we improve the utilization of hardware budget by sharing the I-cache. Multiple accelerators per compute node were already entering the market at that time, like in an example of NVIDIA introducing the K80 as a dual-GPU card, although, multi-GPU solutions were known to improve graphics performance (NVIDIA SLI and AMD CrossFire). By the end of 2015, OpenACC proposes transparent management of multiple accelerators as a feature in their upcoming 2.6 version of specification. Finally, NVIDIA enhance the CUDA to provide Unified Memory with on-demand paging and system-wide atomics. Based on these features, we evaluate NUMA-aware multi-GPU systems as a way of improving the scalability in compute nodes with multiple GPU devices.

The course of this thesis was backed by two industrial internships. The first one at the Cray Research Center (Bristol, UK) for performance analysis and evaluation of multi-core and many-core HPC systems was done from September to December 2015. The second internship was at NVIDIA (Santa Clara, USA) from August to December 2016. Together with the beginning of 2017, it was focused on enabling and improving transparent multi-GPU execution in HPC.

### 1.6 Thesis Organization

The rest of the thesis is organized as follows. The next chapter presents an overview of motivational facts, background, and related work. After that, Chapter 3 provides an overview of methodology we were using throughout of this thesis, describing simulation frameworks and evaluated benchmarks. Chapters 4, 5, and 6 present the results and discuss the contributions of this thesis. Finally, Chapter 7 concludes this work and provides some potential directions of future work.

## Chapter 2

## Background and Related Work

# 2.1 From General-purpose to Specialized Systems-on-Chip

With more transistors per chip coming and single-thread performance reaching its plateau, architects moved to specialized core design to suit particular set of applications. In the mobile industry, ARM's low-power cores [31, 32] have been designed to provide long battery life and efficient support for typical mix of mobile workloads. Although still behind Intel's and IBM's general-purpose cores in terms of brute performance, there is an effort to put ARM's licensed CPUs inside datacenter and HPC systems [33, 34], thanks to their better energy-efficiency. Deep learning applications now rapidly gain attraction, with some companies finding it cost-effective to manufacture accelerators for this type of workloads [35]. Gaming industry develops their own Systems-on-Chip (SoC) giving more realistic experience to the users consuming video-interactive context [36, 37]. Understanding the workload characteristics is important in the design of efficient computer architectures. Focusing on sequential execution, researchers have evaluated desktop SPEC CPU [38] and other server suites to analyze potential improvements for next-generation chip designs [39–41]. In the first part of this thesis, we focus on HPC workload characterization, with the goal of tuning today's CMP microarchitecture to suit the particular features and requirements of HPC applications.

Today's HPC compute nodes are made of CMPs tailored for desktop and server applications. They usually have few heavyweight cores capable of exploiting the available ILP through wide super-scalar out-of-order execution. The core front-end is designed to support large instruction footprints and to predict the outcomes of branches in complex control flows. On the other side, HPC workloads are different, running in parallel, thus demanding throughput-oriented CMPs. Keeping the same power and area budget, a handful of heavy cores are replaced by many lean ones, integrated as an alternative to exploit TLP and data parallelism. For example, Intel's Xeon Phi and IBM's BlueGene/Q [42] CMP architectures integrate many power-efficient lean cores targeting parallel HPC workloads. With the current configuration of the front-end structures, an embedded processor spends 42% of its energy on instruction supply [43]. Instruction fetches and branch predictions consume 30% of the total power in the ARM Cortex-A15 core [44]. McPAT tool for power and area estimations shows that lean cores, such as ARM's Cortex-A9 and Sun's Niagara2, spend 25% of the total core area, and 30% of the total core power on instruction delivery [45]. Therefore, it is important to evaluate microarchitectural optimizations to lessen front-end activity and area which can have significant impacts on overall power consumption.

There is a broad scope of previous application performance analyses run in HPC systems. Most of them evaluate inter-node communication overheads, scalability, bandwidth requirements, and data access behavior [46–48]. Exploiting the available data parallelism, vector processors became particularly useful for HPC applications. A single vector instruction can replace an entire loop, and so the instruction fetch and decode bandwidth needed to keep multiple functional units busy is reduced. Many aspects of the analysis performed in this thesis was done in the past in the context of vector machines [49–51]. Scientific and engineering applications have small instruction footprints, long basic blocks, and low control divergence which makes them suitable for SIMD execution. Nowadays, Intel's Xeon Phi cores [52] or Fujitsu's SPARC64 series of chips [53] implement wide vector units to exploit these code characteristics and gain performance. Our work here revisits these findings considering modern HPC workloads and in the context of CMPs and accelerators made out of lean cores.

GPU devices used as accelerators in HPC systems have completely redesigned

front-end compared to traditional CPUs. Power-hungry branch prediction structures are not implemented, and pipeline stalls caused by prolonged branch resolution are leveraged by running many threads concurrently. A programmer has to be aware of reducing the control divergence among threads in a warp, since they all execute the same instructions at any given cycle. Recent study shows that about 95% of branches executed on GPUs can be correctly predicted either with a bimodal or a branch predictor based on local history tables [54]. The cache hierarchy that services the instruction supply is finely tuned for HPC applications. The first-level I-cache is small (4 KB) with wide cache lines (256 B) [55]. All of the scalar cores in a single SM share one I-cache, with threads fetching and executing the same instruction in lock-step mode every cycle [56]. We show that similar front-end organization should be designed for future CMPs used in HPC, allowing each core to run its thread independently.

Focusing on the microarchitectural changes, there are examples where commodity CPUs have been redesigned to suit better an application domain. A recent study calls for a change in future core design identifying the key micro-architectural needs for emerging scale-out workloads as the opposite of traditional scale-up applications used in data centres [57]. Server applications have large instruction footprints and most stall cycles come from I-cache misses [41]. Because of that, ARM's Cortex-A57 cores, used in micro-servers, have a larger 48 KB I-cache to reduce the impact of I-cache misses [58]. An Intel Xeon Phi core has 512-bit wide vector processing unit so it can exploit the SIMD characteristics of scientific codes [59]. Our findings suggest that a similar core tailoring can be applied to lean-core CMPs used in HPC by redimensioning the existing structures based on application demands.

The first contribution of this thesis covers the HPC workload characterization focusing on the core front-end. We evaluate several OpenMP benchmark suites and compare them with traditional desktop applications, found in SPEC CPU INT. We analyze architecture independent code properties, followed by architecture dependent implications. Our results show that HPC applications expose different code characteristics, quantifying each of them. With those findings, we give recommendations on how to adequately dimension the core front-end structures of lean cores for HPC workloads to get maximal area and power savings without performance impact. Moreover, we analyze the difference between serial and parallel

Figure 2.1: Different CMP configurations.

code sections inside HPC workloads. Not just that HPC cores should be tailored differently from desktop, but also the master core has to be tailored differently from worker cores.

### 2.2 Efficient CMP Design for HPC

As we have mentioned earlier, HPC applications run both in sequential and parallel manner. In case of OpenMP programming model, master thread running on a master core executes the serial code sections and joins the worker threads, which run on worker cores, to execute parallel code regions. To reach an efficient CMP design we need to understand both serial and parallel code in order to improve the utilization of available transistors avoiding over and under provisioning.

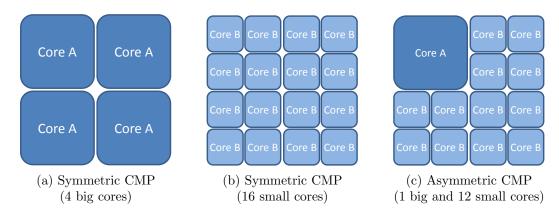

On a CMP level, previous work suggested an Asymmetric CMP (ACMP) design, where multiple single-ISA cores exist on a chip, but with different power, area, and performance characteristics [60]. Let's assume there is a CMP hardware budget (whether it is power, area, or some combination of different factors) equal to 16 core units. Next, we can consider Pollack's rule [61] and assume that core performance increase is proportional to square root of increase in complexity. In other words, if we quadruple the hardware budget in a core, it will deliver 2× more performance. The question is how to distribute the total hardware budget among multiple cores to efficiently execute both serial and paralle code regions in HPC?

Figure 2.1 shows three possible solutions. First two, shown on Figures 2.1a and 2.1b, present Symmetric CMPs (SCMP) with all the cores on chip being

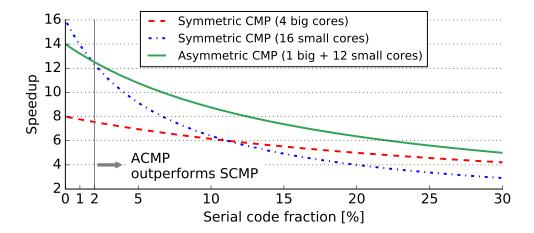

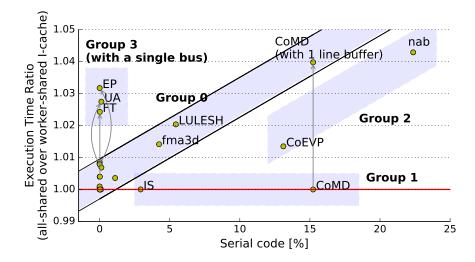

Figure 2.2: Potential speedup obtained by different CMP designs depending on the serial code fraction.

the same in performance. The total hardware budget can be spent either by implementing four big cores (CoreA), each providing  $2\times$  more performance, or by implementing 16 small cores (CoreB), each with  $1\times$  performance. Another option is Asymmetric CMP (ACMP) design, with one big core for executing sequential code, and the rest of small cores for parallel code.

Figure 2.2 shows the potential speedup that different CMP designs can provide depending on the serial code fraction for a parallel workload. An ACMP outperforms both symmetric CMP designs when the application has more than 2% of serial code fraction. As the number of cores on a chip increases, the amount of time spent inside the serial code becomes larger. An ACMP design stands out as a solution capable of efficiently executing both parallel and sequential code regions, combining a latency-oriented core with a set of throughput-oriented cores. In this thesis, we evaluate an ACMP design with one big and eight lean cores. We note that the throughput-designed cores execute the same code at approximately the same time, thus analyze the idea of sharing a single I-cache among these cores. We show that such cache organization does not hurt the performance but saves power and energy.

As soon as we start sharing resources among cores in a CMP, we enter the blurred space between multicore and multithreaded processors. The first papers dealing with simultaneous multithreaded (SMT) processors already identified the shared front-end as one of the major bottlenecks [62]. There have been proposals and products for multithreaded processors with a lower resource sharing degree than

SMT. Conjoined cores [63], CASH [64], IBM Cyclops64 [65], and AMD's Bulldozer module [66] propose a CMP where adjacent cores share some of the hardware structures such as the I-cache, the data cache, and the floating point unit.

All of the previous proposals focus on sharing resources among two adjacent heavy-weight cores, while our intention is to provide a thorough analysis on sharing only the I-cache among many worker cores on an ACMP. Since the rest of the core front-end is not shared, this design improves scaling and it allows sharing among more than two cores. Our work points the limiting factors with more cores sharing an I-cache, with the main objective of increasing performance for the same hardware budget.

The I-cache sharing has also been studied for OLTP workloads [67], which have instruction footprints that exceed the capacity of the I-cache in general-purpose processors. Their design advocates for sharing a larger capacity I-cache to reduce the number of misses in the I-cache. We show that a single shared I-cache, smaller than a private one, reduces the number of I-cache misses due to interthread prefetching, and also leads to area (and power) savings. In their work, the authors focus only on miss analysis not concerning the implication of the proposed design on execution time, as we do here.

Sharing the I-cache among many low-power embedded processors has also been evaluated [68]. Their work is focused on embedded micro-kernels and caches of 1 KB in size. They observe performance improvements up to 60 %, and identify conflicting accesses to the shared I-cache as a potential source of problems. In this paper, we evaluate mechanisms to hide the extra latency involved in conflicting accesses to the shared I-cache and interconnect.

Finally, in the context of HPC workloads, NVIDIA GPU accelerators [69] already use a shared I-cache for all CUDA cores in a SM. Threads in a warp fetch and execute the same instruction in lock-step mode every cycle, which prevents conflicting I-cache accesses and latency variations. We evaluate this approach in a more general way focusing on ACMPs where each thread has its own program counter and executes a separate instruction stream without any constraints.

Decoupling latency-optimized core(s) from throughput-optimized ones leads to a heterogeneous compute node. For serial code, nodes today use general-purpose CPUs while parallel code is offloaded to an accelerator, a many-core CMP or a GPU. Our shared I-cache proposal can be applied to many-core accelerators such as Intel's Xeon Phi. With hardware savings and without performance degradation, this contribution points one way of increasing the performance per area and power unit, the ultimate goal of energy-efficient computing.

# 2.3 More Performance per Compute Node