# Universitat Politècnica de Catalunya

Thesis submitted for the Qualification of Doctor from the Universitat Politècnica de Catalunya

# Advanced analytics through fpga based query processing and deep reinforcement learning

Gorker Alp Malazgirt

Advisor

Dr. Adrian Cristal Kestelman

November 2018

Vita brevis, ars longa, occasio praeceps, experimentum periculosum, iudicium difficile.

### Abstract

Today, advanced analytics is considered to be an important driving force for evolving businesses and societies. Two fields constitute the foundations of advanced analytics, namely databases and predictive analytics using machine learning (ML). Vast streams of structured and unstructured data have been incorporated in databases, and analytical processes are applied to discover patterns, correlations, trends and other useful relationships that help to take part in a broad range of decision-making processes. The amount of generated data has grown very large over the years, and conventional database processing methods from previous generations have not been sufficient to provide satisfactory results regarding analytics performance and prediction accuracy metrics. Thus, new methods are needed in a wide array of fields from computer architectures, storage systems, network design to statistics and physics.

The aforementioned phenomenon has had an epochal influence on the research of predictive analytics using machine learning. Deep learning based machine learning methods have started to surpass rule-based predictive methods by extracting patterns from vast and diverse amounts of data. Unfortunately, there is no such thing as free lunch, deep learning methods require immense amounts of training and learning. Currently, the computational demands of deep learning methods have been one of the most studied methods in all areas of computing sciences from hardware to all the way up to algorithm design.

This thesis proposes two methods to address the current challenges and meet the future demands of advanced analytics. First, we present AxleDB, a Field Programmable Gate Array (FPGA)-based query processing system which constitutes the frontend of an advanced analytics system. AxleDB melds highly-efficient accelerators with memory, storage and provides a unified programmable environment. AxleDB is capable of offloading complex Structured Query Language (SQL) queries from host CPU. AxleDB is designed to be programmable with a set of special instructions, which enable data movement through memory and storage units and can be programmed from the host CPU. The experiments have shown that running a set of TPC-H

queries, AxleDB can perform full queries between 1.8x and 34.2x faster and 2.8x to 62.1x more energy efficient compared to the state-of-the-art Database Management Systems (DBMSs) such as MonetDB, and PostgreSQL on a single workstation node.

Second, we introduce TauRieL, a novel deep reinforcement learning (DRL) based method for combinatorial problems. The design idea behind combining DRL and combinatorial problems is to apply the prediction capabilities of deep reinforcement learning and to use the universality of combinatorial optimization problems to explore general purpose predictive methods. Most of the engineering, data analysis, and business decision problems can be formulated as combinatorial problems where the optimization process can be described as extracting various model parameters from data or distributions and minimizing errors based on an objective. Thus, TauRieL constitutes the backend of an advanced analytics system.

TauRieL utilizes an actor-critic inspired DRL architecture that adopts ordinary feedforward nets to generate a policy update vector v. Then, the update vector improves the state transition matrix that generates the search policy. Furthermore, TauRieL performs online training which unifies training and searches whereas the current state-of-the-art requires substantial training duration and datasets that precedes the search step. The experiments show that TauRieL can generate solutions two orders of magnitude faster and performs within 3% of accuracy compared to the state-of-the-art DRL on the traveling salesman problem (TSP) while searching for the shortest tour. Also, we present that TauRieL can be adapted to the Knapsack combinatorial problem. With a very minimal problem specific modification, TauRieL can outperform a Knapsack specific greedy heuristics.

### Acknowledgements

I am greatly indebted to my advisors Dr. Adrian Cristal and Dr. Osman Unsal for letting me research under their supervision. This thesis would not have been possible without their mentorship, superlative technical guidance and generosity which helped make my time enjoyable while engaging with my research.

I would like to express my deepest thanks and sincere appreciation to my thesis examination panel members and external reviewers for their creative and comprehensive advice until the last draft of my thesis work.

I am grateful to all my colleagues and co-authors at Barcelona Supercomputing Center. Our stimulating discussions, lunchbreaks, sleepless nights and many extracurricular activities will stay as memories to remember for a lifetime.

Finally, I would like to express my sincere gratitude to my family and my grandparents for always showing their love, and imparting to me the importance of education in life. Also, a thousand thanks to all my friends, with whom I have shared moments of joy and sorrow. Their presence has always been significant to me throughout the journey which otherwise might have felt solitary.

This thesis has been supported by Severo Ochoa mobility grant at The Barcelona Supercomputing Center-Centro Nacional de Supercomputación (BSC-CNS), which was accredited as Severo Ochoa Center of Excellence (SEV-2011-0067).

# Contents

| 1        | Inti                             | roducti | on                                                    | 1         |

|----------|----------------------------------|---------|-------------------------------------------------------|-----------|

|          | 1.1                              | Two co  | omponents of advanced analytics systems               | 2         |

|          |                                  | 1.1.1   | The frontend: Query processing                        | 2         |

|          |                                  | 1.1.2   | The backend: a predictive method by combining deep    |           |

|          |                                  |         | reinforcement learning and combinatorial optimization | 5         |

|          | 1.2                              | Thesis  | Contributions                                         | 8         |

|          | 1.3                              | Organ   | ization of the thesis                                 | 10        |

| <b>2</b> | Bac                              | kgrour  | nd                                                    | 11        |

|          | 2.1                              | Query   | processing systems                                    | 11        |

|          |                                  | 2.1.1   | Query processing hardware design                      | 11        |

|          |                                  | 2.1.2   | Designing query processing engines                    | 13        |

|          | 2.2                              | Predic  | tive analytics                                        | 17        |

|          |                                  | 2.2.1   | Background in deep neural networks                    | 17        |

|          |                                  | 2.2.2   | Previous work for solving combinatorial optimization  |           |

|          |                                  |         | problems                                              | 19        |

|          |                                  | 2.2.3   | The impacts of the traveling salesman problem, a well |           |

|          |                                  |         | known combinatorial optimization problem              | 21        |

|          |                                  | 2.2.4   | Targeting TSP using neural networks                   | 21        |

| 3        | $\mathbf{A}\mathbf{x}\mathbf{l}$ | eDB:    | A novel programmable query processing platform        |           |

|          | on i                             | FPGA    |                                                       | <b>25</b> |

|          | 3.1                              | Archit  | ecture of AxleDB                                      | 26        |

|          |                                  | 3.1.1   | Major Components of AxleDB                            | 28        |

|          |                                  | 3.1.2   | The Execution Model of AxleDB                         | 36        |

|   | 3.2  | Illustr | ating the Execution Model of AxleDB by an Example        |    |

|---|------|---------|----------------------------------------------------------|----|

|   |      | Query   |                                                          | 37 |

|   |      | 3.2.1   | Elaborating the Example Query                            | 38 |

|   |      | 3.2.2   | How does AxleDB Process the Example Query?               | 39 |

|   |      | 3.2.3   | Establishing a Data Streaming Path: Elaboration for a    |    |

|   |      |         | Sample Data Path                                         | 44 |

|   | 3.3  | Query   | Processing Accelerators                                  | 45 |

|   |      | 3.3.1   | Filtering Operations, Arithmetic, and Logic Unit $\ \ .$ | 47 |

|   |      | 3.3.2   | Aggregation Unit                                         | 49 |

|   |      | 3.3.3   | Hash-Based Units: Table Join and Group<br>By             | 50 |

|   |      | 3.3.4   | Sorting and Merging Unit                                 | 50 |

|   |      | 3.3.5   | Block-Level MinMax DataBase Indexing Unit                | 50 |

|   | 3.4  | Evalua  | ation Methodology                                        | 51 |

|   |      | 3.4.1   | Configuration of the AxleDB                              | 51 |

|   |      | 3.4.2   | Configuration of Comparison Cases: MonetDB, Post-        |    |

|   |      |         | greSQL and CS<br>tore                                    | 52 |

|   |      | 3.4.3   | Introducing the Benchmarks Methodology                   | 53 |

|   |      | 3.4.4   | Introducing the Evaluation Metrics                       | 55 |

|   | 3.5  | Exper   | imental Results                                          | 55 |

|   |      | 3.5.1   | Evaluating Query Accelerators of AxleDB                  | 55 |

|   |      | 3.5.2   | Overall Performance Analysis                             | 57 |

|   |      | 3.5.3   | A Discussion on the Optimized points of AxleDB in        |    |

|   |      |         | terms of Data Management and Computational Accel-        |    |

|   |      |         | eration                                                  | 62 |

|   |      | 3.5.4   | Evaluating the Performance of AxleDB against Multi-      |    |

|   |      |         | threaded MonetDB                                         | 64 |

|   |      | 3.5.5   | Evaluating the Energy-Efficiency of AxleDB against       |    |

|   |      |         | Multi-threaded MonetDB                                   | 65 |

|   |      | 3.5.6   | Hardware Resource Utilization                            | 68 |

| 4 | Tau  | RieL:   | A Fast Deep Reinforcement Learning Based TSP             |    |

|   | Solv | ver Usi | ing Ordinary Neural Networks                             | 69 |

|   | 4.1  | Reinfo  | orcement Learning Method for TSP                         | 74 |

|   |      |         |                                                          |    |

| 6 | Con | clusio | ns and Future Work                                          | 97 |

|---|-----|--------|-------------------------------------------------------------|----|

|   | 5.2 | Exper  | imental Results                                             | 93 |

|   | 5.1 | Model  | ing the Knapsack Problem and modifying TauRieL              | 91 |

| 5 | Ada | pting  | TauRieL for Knapsack problem                                | 91 |

|   | 4.5 | Exper  | imental results                                             | 81 |

|   |     | struct | ure                                                         | 80 |

|   | 4.4 | Neural | l net architecture, clustering configuration, and the input |    |

|   |     | 4.3.2  | Merging sub tours for the total tour                        | 80 |

|   |     | 4.3.1  | Unsupervised clustering for subtours                        | 79 |

|   | 4.3 | Creati | ng subtours from large graphs                               | 79 |

|   | 4.2 | Unifie | d Training and Searching for the Shortest Tour              | 79 |

|   |     | 4.1.4  | Learning to update the transition matrix                    | 77 |

|   |     | 4.1.3  | Sampling from the transition matrix                         | 77 |

|   |     |        | the Update Vector                                           | 75 |

|   |     | 4.1.2  | Using Actor-Critic Reinforcement Learning to Generate       |    |

|   |     | 4.1.1  | Problem Definition and Notations                            | 74 |

# List of Figures

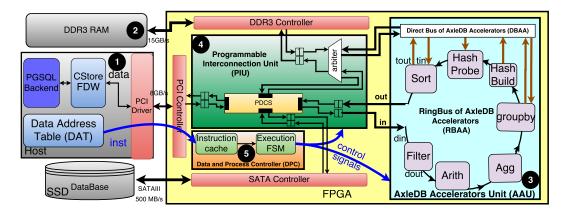

| 3.1 | Overall architecture of AxleDB with its major components.                |    |

|-----|--------------------------------------------------------------------------|----|

|     | • software extensions for DBMS in the host, • Data storage               |    |

|     | units and device controllers, 3 a set of efficient query process-        |    |

|     | ing accelerators, which altogether form AxleDB Accelerators              |    |

|     | Unit (AAU), 4 Programmable Interconnection Unit (PIU) to                 |    |

|     | manage the accesses to the off-chip data storage units, in a             |    |

|     | fully flexible fashion, <b>5</b> Data and Process Controller (DPC) to    |    |

|     | orchestrate the involved modules of AxleDB to process SQL                |    |

|     | queries                                                                  | 26 |

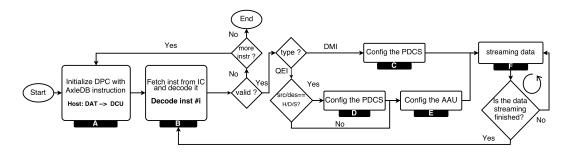

| 3.2 | The flowchart of the execution model in AxleDB. (In this figure:         |    |

|     | H= Host, $S=$ SSD, and $D=$ DDR-3.)                                      | 38 |

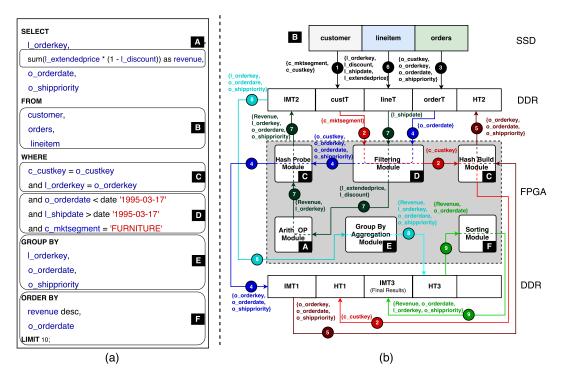

| 3.3 | (a) Example SQL query: Q03, (b) An example query plan                    |    |

|     | of AxleDB to process Q03. To have a simpler figure, $i$ ) we             |    |

|     | partition the tables of the DDR-3 memory into two boxes at               |    |

|     | above and below of the FPGA, although, AxleDB is currently               |    |

|     | attached to a single channel of DDR-3, and $ii)$ we only show            |    |

|     | essential fields of the labels of arrows, excluding the input            |    |

|     | parameters of accelerators, payloads, etc                                | 40 |

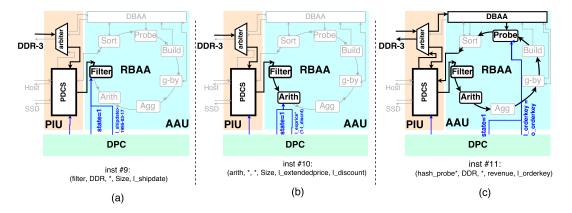

| 3.4 | Establishing the data streaming path $\#7$ by composing to-              |    |

|     | gether different AxleDB instructions $\#9, \#10, \text{ and } \#11.$ The |    |

|     | detailed connections between DPC, AAU, and PIU are shown.                |    |

|     | Among them, the highlighted components/connections repre-                |    |

|     | sent the corresponding parts that are utilized by each AxleDB            |    |

|     | instruction to set up the given data streaming path. The                 |    |

|     | control signals for the PIU and the AAU are generated by DPC.            | 46 |

|     |                                                                          |    |

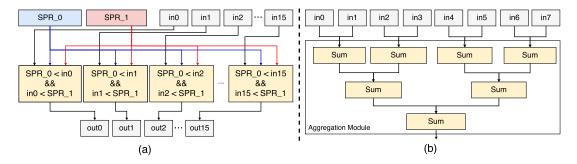

| 3.5  | (a) Filtering blocks that apply the BETWEEN operation to        |    |

|------|-----------------------------------------------------------------|----|

|      | input data using scratch-pad registers (b) SUM aggregation      |    |

|      | using binary fan-in technique                                   | 49 |

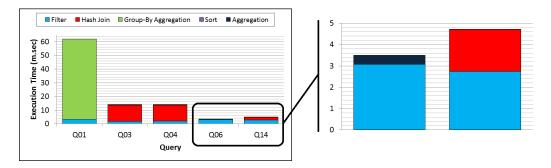

| 3.6  | The total execution time of the queries, partitioned into per-  |    |

|      | accelerator                                                     | 56 |

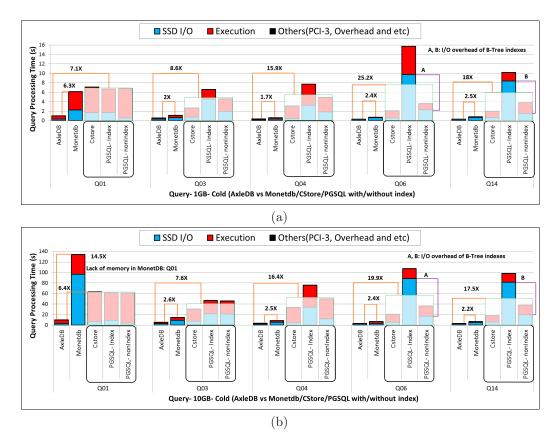

| 3.7  | Total query processing time of the studied benchmarks in        |    |

|      | cold mode, comparing AxleDB vs. MonetDB, CStore, and            |    |

|      | PostgreSQL. (a)1GB scale, (b) 10GB scale. Lower is better       | 58 |

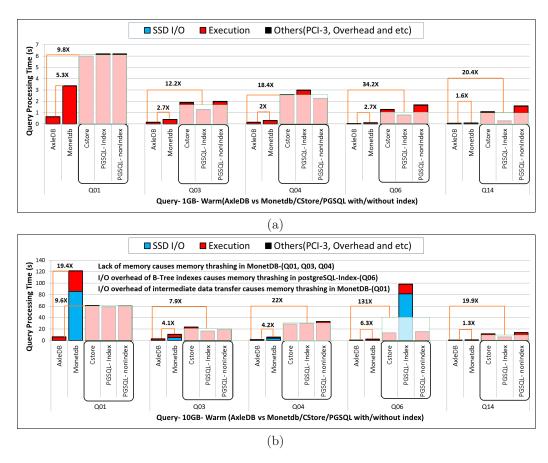

| 3.8  | Total query processing time of the studied benchmarks in        |    |

|      | warm mode, comparing AxleDB vs. MonetDB, CStore, and            |    |

|      | PostgreSQL. (a)1GB scale, (b) 10GB scale. Lower is better. $$ . | 60 |

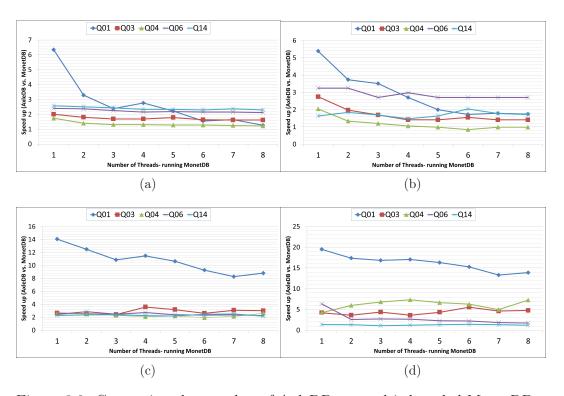

| 3.9  | Comparing the speedup of AxleDB vs. multi-threaded Mon-         |    |

|      | etDB. (a) cold runs in 1GB scale. (b) warm runs in 1GB          |    |

|      | scale. (c) cold runs in 10GB scale. (d) warm runs in 10GB       |    |

|      | scale. y-axis represents the speedup of AxleDB against the      |    |

|      | multi-threaded MonetDB- the relative query processing time,     |    |

|      | as formulated in the Equation 1. Higher is better               | 63 |

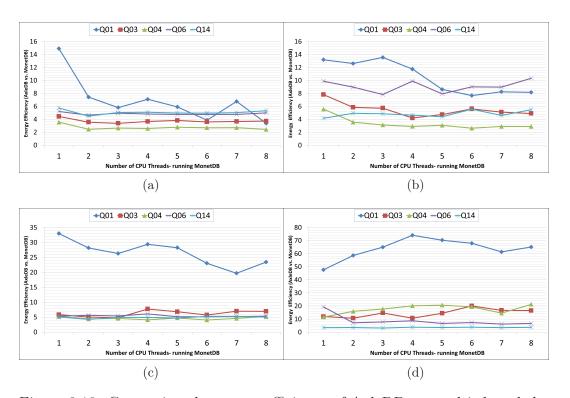

| 3.10 | Comparing the energy efficiency of AxleDB vs. multi-threaded    |    |

|      | MonetDB. (a) cold runs in 1GB scale. (b) warm runs in 1GB       |    |

|      | scale. (c) cold runs in 10GB scale. (d) warm runs in 10GB       |    |

|      | scale. y-axis represents the relative energy efficiency of the  |    |

|      | AxleDB against the multi-threaded MonetDB- the relative         |    |

|      | energy efficiency as formulated in the Equation 3. Higher is    |    |

|      | better                                                          | 65 |

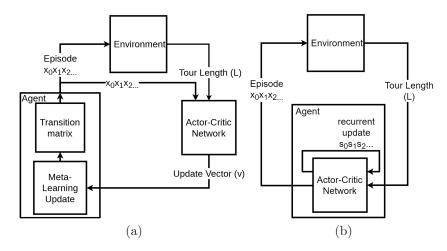

| 4.1  | High level schemas of TauRieL (a) and state-of-the-art Actor-   |    |

| 1.1  | Critic based TSP solver using RNN [17](b)                       | 70 |

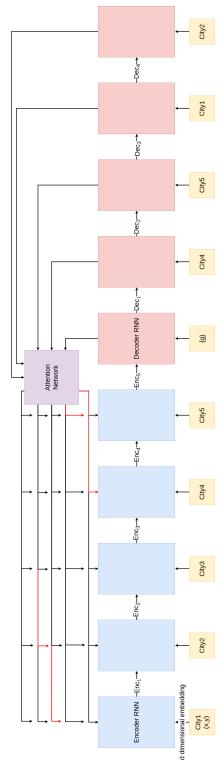

| 4.2  | Ptr-Nets recurrent architecture [131] with attention that is    | ,, |

| 7.2  | employed by NCO [17]                                            | 73 |

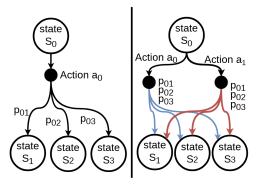

| 4.3  | In TSP, there exists only a single set of action to move from   | 10 |

| T.0  | one state to another (left). There are scenarios where at each  |    |

|      | state there can be more than one action such as directions of   |    |

|      | controller movements in a video game (right)                    | 75 |

|      |                                                                 |    |

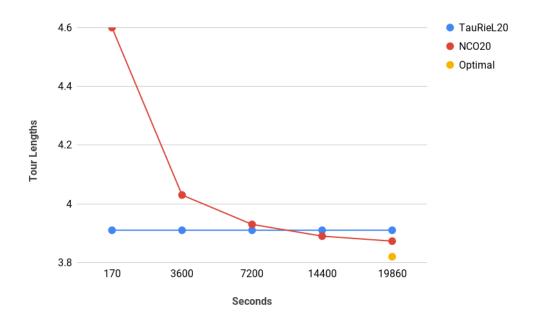

| 4.4 | The average tour length vs training duration for 20-city instances | 85 |

|-----|--------------------------------------------------------------------|----|

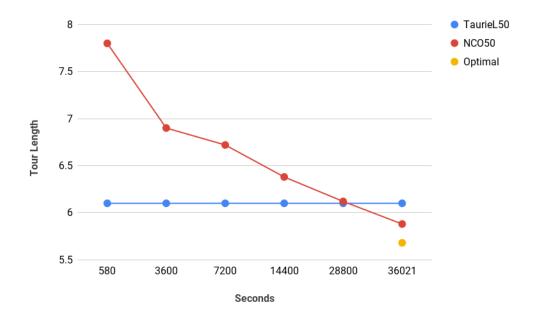

| 4.5 | The average tour length vs training duration for 50-city instances | 85 |

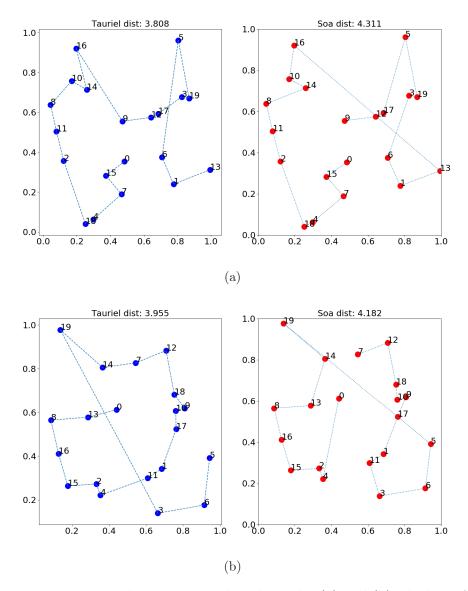

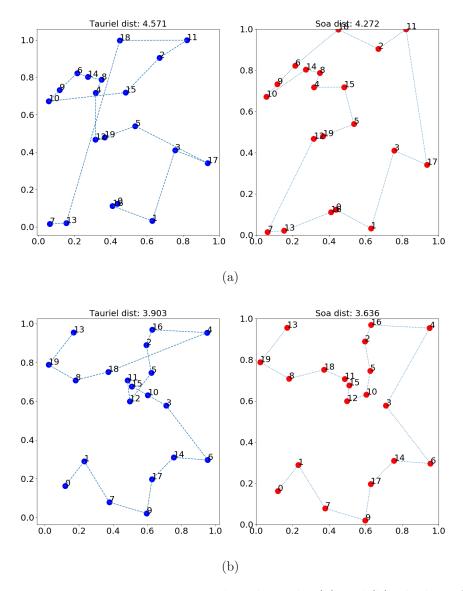

| 4.6 | Two example 20-city tour-length results (a) and (b) which          |    |

|     | perform better than the validation set                             | 87 |

| 4.7 | Two example 20-city tour-length results (a) and (b) which          |    |

|     | perform worse than the validation set                              | 88 |

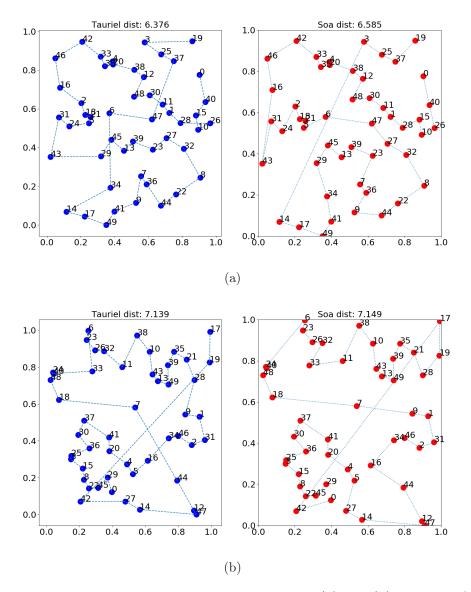

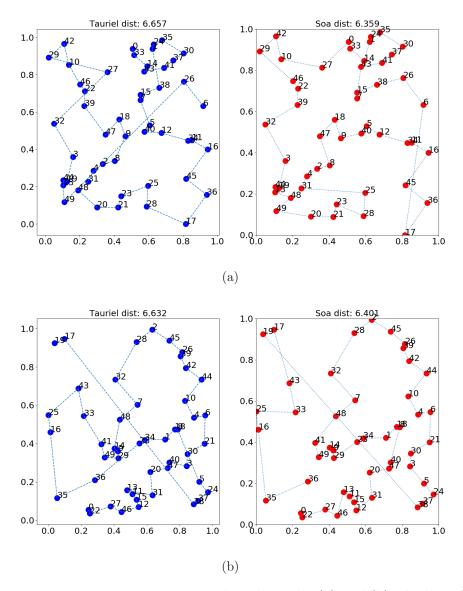

| 4.8 | Two example 50-city tour-length results (a) and (b) which          |    |

|     | perform better than the validation set                             | 89 |

| 4.9 | Two example 50-city tour-length results (a) and (b) which          |    |

|     | perform worse than the validation set                              | 90 |

# List of Tables

| 2.1 | Comparing AxleDB with state of the art platforms, in terms                                                                                                                                                                                                                                                   |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | of accelerators                                                                                                                                                                                                                                                                                              | 14 |

| 2.2 | Comparing TauRieL with previous deep learning based solutions                                                                                                                                                                                                                                                | 23 |

| 3.1 | AxleDB instructions for query execution                                                                                                                                                                                                                                                                      | 34 |

| 3.2 | AxleDB instructions for data movement                                                                                                                                                                                                                                                                        | 35 |

| 3.3 | AxleDB instructions to process the example query, according to the query plan in Figure 3.3 (some of the fields such accelerator-specific parameters are omitted in this table.) The size column shows the size of the data stream for each data path, in terms of the number of rows, in 1 GB scale dataset | 43 |

| 3.4 | Power Consumption of AxleDB components                                                                                                                                                                                                                                                                       | 66 |

| 3.5 | Hardware Resource Utilization of AxleDB                                                                                                                                                                                                                                                                      | 67 |

| 4.1 | Comparison of average tour lengths using the datasets provided by Ptr-Net [131] and A3 algorithm [1] obtained from [131]                                                                                                                                                                                     | 82 |

| 4.2 | Execution times in seconds of single episode and sample step for TSP20 and TSP50 instances                                                                                                                                                                                                                   | 83 |

| 4.3 | Comparison of execution times and tour length gap from optimal between our implementation and NCO [17]                                                                                                                                                                                                       | 84 |

| 4.4 | The $\%$ gap from 50-city Ptr-Net [131] with respect to sample size and the number of training steps                                                                                                                                                                                                         | 86 |

| 5.1 | Comparison of TauRieL's gap from the optimal versus value-<br>to-weight greedy (vwg) for different problem sizes                                                                                                                                                                                             | 94 |

| 5.2 | The execution times in seconds of running TauRieL from |    |

|-----|--------------------------------------------------------|----|

|     | scratch with different item and sample sizes           | 94 |

# List of Symbols and Abbreviations

- $\epsilon$  Update vector rate

- $\gamma$  Discount factor

- $\kappa$  An item in the Knapsack Problem

- $\mu$  The vector that holds the locations of the centroids

- $\nabla_{\theta_{act}}$  The gradient of the expected tour length

- $\phi$  Permutation, a tour in a given graph

- $\pi$  The policy that keeps the decisions between state transitions

- $\theta_{act}$  Parameters of the actor network

- $\theta_{cri}$  Parameters of the critic network

- v The given value of an item in the Knapsack Problem

- A A set of actions  $\{a_1, a_2 \dots\}$

- b The baseline function with respect to the policy

- Cl Cluster representation in the input vector

- D The k-means objective that minimizes distance between the centroids and the elements

- f The function that selects the most likely next state in the transition matrix

- G A given graph that consists of cities

- H The error between the estimations and the baseline

- I Input vector representation to the neural networks

- K The number of episodes that determines the update

- L Total reward

- P Transition probability matrix that determines between two states

- p Probability of a given tour

- R Expected immediate reward after transitioning from a state to another

- S State space in the MDP state space

- T Sample steps

- v The state transition matrix update vector

- x A city in a given graph G

- AAU AxleDB Accelerators Unit

- ASIC Application Specific Integrated Circuit

- BSC Barcelona Supercomputing Center

- CNS Centro Nacional de Supercomputación

- DAT Data Address Table

- DBAA Direct Bus of AxleDB Accelerators

- DBMS Database Management System

- DMI Data Movement Instructions

DNC Differentiable Neural Computer

DPC Data Process Controller

DRL Deep Reinforcement Learning

FDW Foreign Data Wrapper

FIFO First-In-First-Out

FPGA Field Programmable Gate Array

FSM Finite State Machine

GPU Graphics Processing Unit

HBM High Bandwidth Memory

HLS High Level Synthesis

IC Instruction Cache

IP Xilinx Intellectual Property Core

LSTM Long Short Term Memory

MB Megabyte

MDP Markov Decision Process

MIG Memory Interface Generator

ML Machine Learning

ORC Optimized Row Columnar

OS Operating System

PDCS Programmable Data Connection Switch

PGSQL PostgreSQL

PIU Programmable Interconnection Unit

QEI Query Execution Instructions

r Reward which is the negative distance between two cities

RAPL Running Average Power Limit

RL Reinforcement Learning

RTL Register Transfer Level

SATA Serial AT Attachment

SQL Structured Query Language

TSP Traveling Salesman Problem

## Chapter 1

### Introduction

Advanced analytics is considered to be the most important driving force for evolving businesses and societies. Vast streams of structured and unstructured data have been incorporated, and analytical processes are applied to discover patterns, correlations, trends and other useful relationships that help to partially or fully take part in a wide range of decision-making processes [82]. The data being generated has grown at a rapid pace over the years, and conventional database processing methods from previous generations have not been sufficient to provide satisfactory results regarding performance and prediction accuracy [77, 58].

Consequently, the big data explosion has yielded deep learning based machine learning methods to excel. The large-scale training and approximation from the vast amount of data have surpassed rule-based learning systems [60]. However, the successful solutions require long training times and significant computational demands [53]. This thesis addresses some of the current challenges in the scope above and proposes two methods that aim to meet demanding requirements of predictive data analytics. The objectives, contributions and the details of the proposed solutions are presented, and the insights are shared alongside the experimental results and the conclusions.

# 1.1 Two components of advanced analytics systems

There are two fields that constitute the foundations of advanced analytics, namely databases and predictive analytics using Machine Learning (ML). The databases have been evolving in order to support a vast amount of high variety data. Furthermore, emerging applications such as autonomous driving and large-scale scientific experiments have created data at an ever increasing rate [82, 39]. The data is extracted and formatted by database queries and queries are processed by query processing units which present the requested data [119]. This ever-increasing rate of raw data creation and the need for intelligent and timely analysis of this data is a challenge. In this endeavor, databases are considered as the frontend entities of the data analytics tasks that are responsible for storing, preparing and preprocessing the data in a structured way.

Simultaneously, predictive analytics apply ML methods and handle the heavy-duty work of generating insights through inference by rigorously processing the available data. Thus they are classified as the backend entities of the analytics systems [103]. Both the frontend and the backend data analytics domains are heterogeneous and complex structures that are composed of different sub-fields. Thus, in the following two sections, we present the challenges facing the front and backend domains and the approaches towards addressing some of the challenges.

### 1.1.1 The frontend: Query processing

Databases - query processing systems - are capable of storing and querying large amounts of data in various settings from data-centers to autonomous cars [75]. Although there have been alternative general purpose frameworks to databases that do not require explicit data definitions and that hide functions such as data cloning for scalability from the developer [135, 147], these frameworks have not been as successful as replacing databases. The main reason for system architects to prefer databases is due to their ACID

(Atomicity, Consistency, Isolation, Durability) guarantees.

About three exabytes of structured and unstructured data is created and stored in databases each day, and this number is doubling approximately every forty months [81]. Querying enormous amount of data has been a challenge, and new methods have been actively researched and developed for maximizing query processing throughput [5]. Until recently, the majority of query processing research has been targeting software stack on general purpose computing platforms [48] which have also been supported by the Moore's Law that provided performance improvements without major modifications in software [37]. However, the straightforward increase in clock frequencies that led to performance gains has already diminished. Furthermore, powerful uniprocessor general purpose processing platforms have been replaced with multiprocessing architectures. Therefore, homogeneous multiprocessing platforms have been the main choice of computing in database systems in the last decade [37, 56].

Recent advances in specialized hardware accelerators and heterogeneous processing such as Graphics Processing Units (GPUs) [143], Application Specific Integrated Circuits (ASICs) and Field Programmable Gate Arrays (FPGAs) have provided significant improvements in computational power [97]. Also, the massive increase in data sizes, stringent design requirements and the mentioned paradigm shift in the computing domain towards specialized and heterogeneous processing are causing query processing systems to reinvent themselves by adopting a unified domain-specific hardware/software approach [25].

Classical control-flow-based query processing engines deliver lower computational throughput compared to what can be achieved by application-specific hardware. From one side, to alleviate the overheads of data movement, one promising solution is to bring the computation closer to where the data resides, so that more operations can be completed avoiding non-essential data movement [124]. In this method, the gains are two-fold: easing the load on the host CPU for performing database operations, and reducing the negative impact on the performance of high-latency I/O operations. As a result, significant throughput improvements, as well as reduction of I/O

overheads can be achieved [108]. On the other hand, streaming data through highly specialized hardware accelerators in a deeply pipelined fashion can significantly improve the computational throughput of the query processing engine.

FPGAs provide a unique opportunity to build an efficient query processing platform, by constructing a high-throughput execution engine with the additional aim of minimizing overheads of data movement. It is mainly the consequence of; (i) the inherent characteristics of massively parallel and configurable architecture of FPGAs, suitable for data streaming in deep pipelined-style execution (ii) the rise of High-Level Synthesis (HLS) technology, which makes FPGA applications relatively more straightforward to develop compared to low-level languages such as VHDL or Verilog, and (iii) the availability of soft cores that allow rapid generation of interface protocols such as PCIe 3.0 (Peripheral Component Interconnect Express) or SATA-3 (Serial AT Attachment) on FPGAs.

In a nutshell and within the context of the frontend, the objectives of this thesis can be listed as:

- To design a set of energy efficient and high-performance query processing hardware accelerators for FPGAs using high-level synthesis methods for rapid prototyping

- To provide an infrastructure in FPGA that sits between a host CPU and SSD storage, thus bringing computation closer to data and enabling query processing hardware accelerators for efficient, high-performance query processing in a single compute node

Based on the objectives, we present the thesis contributions in Section 1.2.

# 1.1.2 The backend: a predictive method by combining deep reinforcement learning and combinatorial optimization

The second field that constitutes the foundations of analytics is the predictive analytics using deep learning methods. The predictive analytics enable to extract patterns from datasets and aim to provide the best assessment of the likelihood of events whether it be predicting a pedestrian in shortest path in map, grouping photos in folders, or forecasting financial markets. Deep learning architectures are composed of neural networks, densely connected processing elements that are loosely named after the primary information-carrying cells of the brain, the neuron [71].

Deep learning is separated from the rule-based ML systems such that patterns in the data are not extracted based on a set of features [21]. Moreover, deep learning architectures do not necessitate handcrafted feature extraction that in most cases require domain knowledge. Instead, an end-to-end training process which is called supervised learning which exploits the vast amount of labeled input-output data. Using supervised learning deep learning models can extract features and apply transformations to map inputs to outputs [42]. Thus, deep learning frameworks are built from sampling the inputs and probabilistic distributions with expected outputs. However, the end-to-end training procedure requires large amounts of input data for successful outcomes [42].

The trade-off of not requiring handcrafted features while requiring more input data has turned out to be favorable for deep learning architectures [71, 86, 129]. Deep learning algorithms have been shown to outperform heuristics in various application domains. However, the vital necessity for high volumes of data for successful predictions also hinders broad adoption of deep learning in various domains [122, 19, 116]. There does not always exist an adequate amount of data for successful training or high costs, noisy processes and computational limitations hinder the generation of datasets [28, 105].

A critical domain that is affected by the mentioned phenomenon is the combinatorial optimization problems [7]. These problems are computationally challenging either to search for the optimal solutions due to their exponential exploration space or to generate a single feasible solution. Also, the accuracy of predicting combinatorial optimization problems are also affected when available datasets possess a large amount of sub-optimal instances. In this case, although the training is performed successfully, the prediction performance may be unsatisfactory. Nonetheless, there exists a branch in the machine learning field that does not rely on supervised learning methods, namely reinforcement learning (RL).

Deep Reinforcement Learning (DRL) combines deep learning with RL [11]. In essence, RL is a technique that consists of an agent, which is a software program that learns from its environment by taking actions (decisions), collecting rewards and adjusting its behavior based on the rewards. RL utilizes dynamic programming and Markov Decision Process (MDP) methods which allow the agent to explore the environment through taking various actions (exploration), and take advantage of recorded experiences by replaying previous actions (exploitation), by and large stochastically and in a sequential manner [121, 91]. DRL architectures have incorporated complex pattern recognition and approximation capabilities of deep learning for representing agent policies and predicting value functions [86]. The significant difference of RL from supervised learning based deep learning is that RL systems learn from experience by sampling from the state space whereas supervised learning occurs through approximations over labeled datasets [63]. Hence, by representing agents' possible actions as deep neural networks, the whole reinforcement learning can be trained end-to-end that allows DRL architectures to benefit from exploring the available state space and collect experiences whereas the success of deep learning architectures only relies on the given datasets. Furthermore, sequentially exploring the state space yields DRL architectures to target problems that advance sequentially in order to reach a solution, such as planning problems [123]. Henceforth, combinatorial optimization and natural language processing problems can be listed among these types of problems [22, 24]. Although, deep reinforcement learning architectures can

modify internal states and consider output feedbacks, the overall training times of deep reinforcement learning architectures have been as high as deep learning architectures [112].

The main of the advantages of DRL in the scope of this thesis that they are capable of tackling combinatorial optimization problems, which form the basis of the most prediction problems in engineering, data analysis, and business [94]. A solution can be deduced by combining sample space exploration and available nonoptimal datasets. The rewards collected during explorations are then used to extract the parameters by minimizing predetermined error measures concerning an objective function [110, 36]. Hence, the universality of combinatorial optimization problems combined with the strengths of deep reinforcement learning is a promising combination and constitutes our design idea towards designing the predictive analytics backend. Thus in this thesis, the objective towards building a general backend for predictive analytics can be itemized as:

- To develop a deep reinforcement learning method and tackle combinatorial optimization problems

- To apply the proposed method to two different combinatorial optimization problems for displaying generality of the solution

- To eliminate the main weaknesses of deep learning which are the long training durations and the sheer necessity of labeled datasets

Next section presents the contributions of the thesis based on the objectives that we have described in Sections 1.1.1 and 1.1.2.

#### 1.2 Thesis Contributions

The previous chapter introduced the emergence of advanced analytics and their effects on the computing and machine learning landscape. In this thesis, we aim to address the challenges mentioned above and present our contributions. For the analytics frontend, we present the design and the implementation of AxleDB, a novel architecture for managing data movement through hardware accelerators and storage. AxleDB is an FPGA-based query processing system that melds highly-efficient accelerators with memory, storage and provides a unified programmable environment. AxleDB is designed to execute complex Structured Query Language (SQL) queries in full by performing various time-consuming query operations using FPGA based hardware accelerators, while the data movement between storage and compute units are handled with custom move instructions. Designing AxleDB presents the following contributions:

- FPGA based query processing accelerators are presented for filtering, arithmetic and aggregation operations which are designed to speed up database analytics for in-memory databases. Unlike traditional FPGA design methods, our hardware accelerators are composed using High-Level Synthesis (HLS), which enables high-level descriptions of query processing functions to be targeted directly into Register Transfer Level (RTL).

- A unified AxleDB platform is presented that includes query processingspecific accelerators and the efficient data management mechanism to control the flow of data, which effectively enables rapid query processing in the hardware.

The performance and energy efficiency of the AxleDB is tested under various conditions, by running five decision-support TPC-H queries. We compare AxleDB to state-of-the-art software-based DBMS, PostgreSQL, and MonetDB, in the single-threaded and multi-threaded modes in a single compute node. Scaling data for multiple compute nodes has not been investigated in this thesis.

Moreover, for the analytics backend, we propose TauRieL <sup>1</sup>, a DRL based method for solving combinatorial optimization problems, and our contributions can be listed as the following:

- TauRieL searches for optimal solutions given a combinatorial optimization problem by training ordinary deep neural networks in a reinforcement learning setting and can generate solutions two orders of magnitude faster than the state-of-the-art while maintaining similar prediction accuracy.

- TauRieL introduces an explicit state transition matrix that complements the learning process by generating samples solutions from the transition probabilities.

- A clustering and merging scheme is developed in order to divide the given problem into subproblems for coping with the large design space.

The contributions of TauRieL is shown by solving two innately different combinatorial problems, namely the traveling salesman problem (TSP) and the Knapsack problem [94]. We compare the prediction accuracy, training and inference times when the problems start from scratch.

<sup>&</sup>lt;sup>1</sup>A wood-elf character from Hobbit the Movie who possesses superior senses and pathfinding skills compared to humans

### 1.3 Organization of the thesis

In this chapter, we have discussed the emergence of advanced analytics and the future challenges in the domain. Then, we have introduced the two entities, namely databases and predictive analytics using deep learning. Also, we classify and identify their roles as the front and backend of advanced analytics. Before explaining the objectives of the front and backend, we have introduced the motivations and the challenges.

After listing the objectives for each part, we have presented the contributions in Section 1.2. In the next chapter, we scrutinize and present the background works. Chapters 3 presents the details and the experimental results of AxleDB. Chapter 4 starts by reiterating the problem at hand and introduces TauRieL. The background, the search algorithm, and the preliminary results are shown on TSP. The future work which we discuss in Chapter 5 will enlarge Chapter 4 by introducing the Knapsack problem. Chapter 6 finalizes the thesis by presenting conclusions.

### Chapter 2

### Background

In this Chapter, we discuss the relevant state-of-the-art of data analytics front end (Query Processing, Section 2.1) and backend (Predictive Analytics, Section 2.2). We also comment on the thesis advances beyond this state-of-the-art, wherever appropriate.

### 2.1 Query processing systems

### 2.1.1 Query processing hardware design

There have been two main efforts to implement query processing on hardware, namely ASIC-based and FPGA-based solutions [141, 62]. The work in [141] presents an ASIC-based method with heterogeneous compute tiles which manipulate rows and handle query processing operations in a coarse grain way. In order to manipulate streams of data according to the given query, the authors present spatial and temporal planning which enables/disables compute units along a predefined data path.

The most significant difference between full custom ASIC design compared to HLS-based FPGA designs is the flexibility. HLS is the process of generating low-level cycle accurate RTL specifications from high-level structures which are generally in C/C++. Different sizes of memory or compute structures from database columns can be optimized by extending or shrinking data sizes in the high-level source code. Next, these structures are programmed

onto the logic and memory blocks of the FPGAs [30]. Consequently, HLS-based FPGA designs are a more flexible and productive solution for rapid design. However, ASIC-based solutions excel in performance compared to FPGA-based solutions because FPGA hardware provides programmable logic and memory blocks, and these blocks must be programmed efficiently for the required functionality. On the other hand, ASICs can be designed from scratch, maximally tailored for the application at hand [115].

While the HLS methods propose hardware generation from high-level programming languages such as C/C++, Glacier [88] compiles VHDL code from algebraic expressions which adds additional steps in the system design because algebraic expressions must be created from SQL expressions or they are taken directly from a query planner. Our proposed method in this thesis binds accelerators to SQL operators semantically. Then, the query plan is made accordingly.

Accelerator affinity with its host is one of the essential components in the hardware accelerator domain. Loosely coupled accelerators can execute independently from their host processors, and this loose coupling allows them to service to different processors. On the other hand, highly coupled accelerators are attached to a particular system and cannot be used by any other service. The authors of [95] discuss efficient methodologies for decoupling query processing hardware from a general purpose host computer this in contrast to in-memory database acceleration where the memory of the accelerators is controlled by a host system as in AxleDB developed in this thesis [111].

Runtime reconfiguration capabilities of FPGAs have allowed runtime query processing customization. Authors of [34] have built a database operations library which at runtime forms the data path based on the given SQL query. They have focused on data filtering operations. The main advantage of runtime reconfiguration is to eliminate the synthesis of queries if the available runtime operator library can execute the given query. The flexibility that HLS provides is at compile time rather than runtime. Hence, there is a possibility to combine runtime reconfiguration with HLS technology such as the newest Xilinx SDAccel system design tool [2]. Although FPGA based processing systems

could be enhanced by the use of dynamic reconfiguration, the reconfiguration requires additional glue logic on FPGA and a predetermined selection of the functionality that will be modified during the runtime. AxleDB does not employ runtime reconfiguration. Instead, it is designed to be programmable via a set of instructions for handling different database queries.

#### 2.1.2 Designing query processing engines

Previous studies have looked into designing efficient query processing engines, employing vector architectures [49], ASICs [142], GPUs [104] or CPUGPU-FPGA [50, 9] proposals. On the other hand, other approaches either used FPGAs statically [27, 96], or leveraged dynamic reconfiguration to better fit the requirements of each query [16, 66, 149]. We differ from these works by following a static but programmable approach in query processing and data management, as we can support as many operations as we need, without requiring runtime reconfiguration. The industry has also invested in a few products, IBM Netezza [59] and XStream Data dbX [113], which offer full DBMS solutions.

We compared AxleDB with a set of state-of-the-art FPGA/ASIC-oriented query processing platforms: Ibex [139], Q100 [142], BlueDBM [61] Sukhwani et al. [119] and Jaeyoung et al. [35]. Ibex [139] is a database storage engine that is equipped with a limited set of query processing operations, working directly with data inside SSD. Q100 [142] proposes domain-specific database processors, but without supporting data management from off-chip storage. BlueDBM [61] proposes a system architecture with flash-based storage and in-store processing capabilities, but it is not specialized for query processing. Sukhwani et al. [119] present an FPGA-based query processing engine that is attached to a DBMS via PCIe-3 with a data compression capability. Jaeyoung et al. [35] present a smart SSD that incorporates it with memory and low power embedded processing units inside the SSD controller. Although the computation is closer to the storage, the compute blocks are not specialized for query processing and necessitate a more constrained programming style for the processors such as for prevention of register spilling. The work in

Table 2.1: Comparing AxleDB with state of the art platforms, in terms of accelerators

|             | AxleDB   | Ibex     | Q100     | BlueDBM | Sukhwani<br>et al. | Jaeyoung et al. | Ziener<br>et al. |

|-------------|----------|----------|----------|---------|--------------------|-----------------|------------------|

| filter      | <b>√</b> | <b>√</b> | <b>√</b> | ×       | <b>√</b>           | <b>√</b>        | <b>√</b>         |

| aggregation | <b>√</b> | <b>√</b> | <b>√</b> | ×       | ✓                  | ✓               | <b>√</b>         |

| hash join   | <b>√</b> | <b>√</b> | ×        | ✓       | ✓                  | ×               | <b>√</b>         |

| merge join  | ×        | ×        | <b>√</b> | ×       | ×                  | ×               | <b>√</b>         |

| order by    | ✓        | ×        | <b>√</b> | ×       | ✓                  | ×               | <b>√</b>         |

| DB indexing | ✓        | ×        | ×        | ×       | ×                  | ×               | ×                |

| compression | ×        | ×        | ×        | ×       | ✓                  | ×               | ×                |

[119] presents a query processing system that efficiently uses partial dynamic reconfiguration capabilities for on-the-fly query processing.

Table 2.1 lists the embedded accelerators for each of the studied platforms. AxleDB currently covers most of the necessary modules to run complex queries, although operations such as pattern matching or compression are not supported yet. On the other hand, as illustrated in Section 4, we proposed a novel and efficient accelerators for many important SQL query primitives using modern HLS tools. Although the hash join, sorting and indexing engines that are used in AxleDB are out of the scope of the thesis, we present and compare all the features with state of the art in 2.1. The detailed explanation of the blocks above can be found in [111].

Ibex: AxleDB differs from Ibex in two ways. First, Ibex does not provide any programmable data movement support. Also, the set of hardware accelerators are limited. AxleDB both provides data move instructions and also provides aggregation and sorting. In complex queries, ibex fallbacks to the host CPU. Thus, there may be scenarios where the fallbacks can be separated in query execution and creating a lot of data movement between the accelerators and the CPU. AxleDB supports software fallbacks when as the last step in the query schedule. Hence, if given SQL query provides it, AxleDB sends operands to the host CPU which results in the final product after the last operation is executed in the host CPU.

Q100: AxleDB differs from Q100 in micro-architecture and ISA design. Instructions of AxleDB are centered around data movement and initiating

the accelerators, whereas Q100 has SQL-style instructions. The authors based their micro-architecture design on the sensitivity analysis of TPC-H queries. However, the off-chip bandwidth experiments have shown that query execution speeds are affected to a greater extent. In contrast, our platform is designed to maximize the available off-chip bandwidth by explicit data movement instructions. Thus, this allows finer grain data movements for execution. Also, as Q100 is tailored as a composition of a particular purpose (ASIC) blocks, thus, extending the blocks can be an expensive process.

BlueDBM: Its single node consists of flash storage, accelerator hardware in FPGA, flash controller and network interface. Data requests are sent from the host with minimum kernel overhead. Specialized accelerators process the data retrieved directly from flash storage, bypassing DRAM. AxleDB also supports different types of data movement, allows data streaming among the host, SSD, DDR-3, and accelerators. AxleDB is specialized for database query processing using an efficient set of query processing accelerators, whereas BlueDBM does not support the performing of such complex SQL queries. BlueDBM has a distributed structure that allows them to scale up more processing nodes, providing a larger address space. This capability is not yet supported in AxleDB, through multiple nodes of AxleDB platform can be enabled, this procedure requires additional modifications such as data partitioning and query scheduling [44].

Sukhwani et al.: [119] present an FPGA-based query processing engine. The engine is attached to a DBMS via PCIe-3. The supported functionality of the accelerator is filtering, join and sorting. To improve the throughput, the data is compressed by the host. Therefore, the decompression is the first step in the query processing pipeline on FPGA and processed queries are sent back in decompressed form. The authors do not provide any indexing mechanisms, and all queries that are sent to the accelerator require a full table scan. Also, the join and sorting units are not streaming based. Thus they use onboard DRAM for storing intermediate results. In the query pipeline, the filtering units always come before the join/sort units. Necessary data is read from the DRAM of the host. Thus, this requires additional data movement from external storage to DRAM by either the host or the accelerator. In AxleDB,

the data movement and acceleration instructions allow processing blocks to execute in any order. Hence, it is possible to utilize a join/sort unit before filtering. AxleDB is designed to interface external memory directly and stores intermediate data in FPGA's memory.

Jaevoung et al.: [35] present a smart SSD that incorporates SSD storage with memory and computing resources inside the SSD controller. This design allows internal aggregate I/O bandwidth to be 5X higher than fastest SAS and SATA architectures. The Smart SSD architecture presented consists of embedded processors that are on the SSD host interface controller. They are coupled with DRAM and SRAM memories for intermediate data storage. NAND memory arrays inside SSDs allow parallel access. Contrary to Smart SSD, AxleDB is designed to work on an FPGA, and it is connected to an SSD via SATA port. This allows the design of specialized accelerators on the FPGA rather than general purpose embedded processors. In two cases, smart SSDs can fail to exploit the advantages of its architecture, because these scenarios might not require extensive communication between the embedded processors and the SSD units. The first case is when the embedded processors require data communication between the host, and the utilization of the SSDs are very low. Next, the general purpose local memories of the embedded processors do not satisfy the memory requirements for the problem at hand and it causes register spilling and decrease the performance. In these two cases, specialized accelerators can provide better results compared to general purpose embedded processors of the smart SSD.

Ziener et al.: [16] present a query processing platform that leverages the partial dynamic reconfiguration capability of FPGAs to fit the requirements of each query better on-the-fly. Query primitives such as filtering, aggregation, hash join, and sorter are gathered in a library while supporting both columnand row-oriented data storage formats. However, this work does not follow a direct-SSD-coupled approach that diminishes the overall throughput, which can suffer from data offloading and partial reconfiguration overheads.

#### 2.2 Predictive analytics

In this section, we aim to present the relevant information about predictive analytics and correspondingly allow readers to get acquainted with the foundations which can be categorized into three. First, in the next section, we first describe deep neural networks and reinforcement learning which enable prediction through exploration of the state space and learning from available datasets. Second, Section 2.2.2 presents the combinatorial optimization problems which lie in the heart of many engineering and scientific settings. Thus, we scrutinize previous works that aspired to produce optimal results tailored for particular combinatorial optimization problems. Finally, we target TSP which is a well known combinatorial optimization problem, and it has been discussed to be a hard problem for classical and quantum computing [134]. Hence, in Section 2.2.3 we introduce previously published that target TSP. Under those circumstances, a successful TSP solver could provide a step closer to a general predictive analytics system by transforming the given problem to TSP or a variant of it. However, the transforming process is not in the scope of the thesis, the problem reduction techniques have been well studied [70]. Therefore, in Section 2.2.4, we explain the existing deep learning based efforts that target TSP and compare and contrast with our proposed method in this thesis.

#### 2.2.1 Background in deep neural networks

Deep learning allows to extract complex patterns and function approximations and to map an input to output without any pre-processing, namely the enigmatic feature extraction processes [57]. The training process is called supervised learning, and the backpropagation is the underlying method. Backpropagation algorithm in an optimization setting minimizes generic loss metrics (e.g., squared loss, cross entropy) by modifying the gradients [72]. Convolutional Neural Networks and Recurrent Neural Networks are one of the most successful architectures that have provided breakthrough results in image processing, natural language processing, etc. through supervised learning [148, 76]. Furthermore, the design process of these architectures

concentrates on amending neural networks as opposed to tailoring heuristics for application specific purposes. Also, previous works have shown that a well tuned neural network can be reused liberally as high-level feature extractors [52].

Recently, Differentiable Neural Computer (DNC), a deep learning architecture which differs from previous networks has been proposed [45]. The main characteristic of this model [45] is that the authors provide an external memory matrix complementing the Long Short Term Memory (LSTM) cell state [55]. Thus, the external memory matrix is trained to support the existing recurrent neural network. The authors show that the hybrid model can be trained as a regular neural network including the external memory matrix. The examples demonstrate solutions to problems such as finding the shortest path and solving moving blocks puzzle. Although the proposed architecture possesses a built-in memory structure that resembles a random access memory, the proposed solution can still be classified as a supervised learning architecture.

Unlike a general purpose computer, the most suitable environment for DNC [45] to excel is when the amount of data to predict, classify or infer an algorithm is high. Also, the DNC solution suffers from high training duration and performs poorly when the final algorithm to reach unclear, or the result requires interactions with the environment [121]. For situations that do not favor the DNC, DRL architectures that combine reinforcement learning and neural networks, are shown to perform well [85, 86, 129].

Reinforcement learning (RL) is a method that consists of an agent, which is a software program that learns from its environment by taking actions (decisions) and adjusting its behavior based on rewards. RL representations have utilized dynamic programming and Markov Decision Processes (MDP) which model the agent and its interactions with the environment through describing actions and states. In almost all cases, there is an agent that takes different actions (exploration), and take advantage of recorded experiences by replaying previous actions (exploitation). Furthermore, the actions by large are stochastic, partially observable and happen in a sequential manner [121, 91].

DRL architectures have incorporated complex pattern recognition and approximation capabilities for the agents and the rewards from the environment by employing neural networks [86]. Hence, agents make decisions either through maximizing future rewards from experience or by extracting policy mechanisms based on state action patterns [85, 90]. Thus, the significant difference of RL from supervised learning is that RL systems learn from experience whereas supervised learning occurs through approximations over labeled datasets [63, 71].

# 2.2.2 Previous work for solving combinatorial optimization problems

Combinatorial optimization is a branch of mathematical optimization, and it has been a cornerstone research field with various application domains from biotech, finance to manufacturing. Many problems are arising in this field that does not yield optimal solutions with polynomial-time algorithms, and this constitutes the main reason for continuing interests and contributions. A set of reducible problems described by Karp et al. [64] laid the foundations of combinatorial problems, and subsequent research on dealing with computationally intractable algorithms through approximation methods with empirical performance estimates [40].

Designing approximate methods for combinatorial optimization problems can be classified into three. These are exact solutions, approximations of exact solutions and the design of heuristics. The exact solutions have been proposed through designing mathematical programming methods such as Simplex Method [12]. Generally, exact solution methods have scaled poorly due to computational costs. Thus, approximations of exact solutions have been proposed [12]; Lagrangian relaxation and approximations on the upper bound and the optimality gap are among the best-known methods [20].

Third and the most popular method has been designing heuristics which are designed to generate useful solutions without any guarantees for the optimum. Traditional heuristic design can be divided into three subclasses. The first class of methods is called the constructive method where the heuristics are

constructed from null and finalize when a feasible solution is found, such as the nearest neighbor heuristic [32, 107]. The second method is called the improvement heuristics where the heuristic tries to develop better results by improving current solution based on rules. N-opt heuristic for TSP problem can be given as an example [51, 15]. The third method is called a hybrid which unites the previous two methods. Heuristics tend to exploit local improvements with constructive searches [14, 109].

Though heuristic approaches have been shown to work well, each approach requires domain knowledge and application specific tailoring. Specifically, each heuristic requires tailored configurations which are in essence the problem representation and the playout operations that result in the next step of the heuristic. These configurations vary widely from choosing suitable abstract data types and containers to computational costs of next-state playout.

Throughout the years, metaheuristics have emerged as a class where they allowed a mixture of stochasticity and exact solution proposals that can be applied directly to sample space. Furthermore, more generic algorithmic recipes allowed metaheuristics to span a range of optimization problems. Evolutionary computation, simulated annealing, and tabu search are known examples in this area [41].

Hybrid metaheuristics have also been researched for compensating for weaknesses of the constructive improvement heuristics. Authors in [74] propose hybrid simulated annealing and tabu search metaheuristics for solving TSP. They explored local neighboorhood search for sub tours with tabu search whereas global search has been complemented using temperature-based simulated annealing. Towards providing more generality, four parameters are defined that are proposed as the only parameters for customization for different problems. Thus, application heuristics parameters such as epoch length, candidate solutions and cool time are defined regarding global variables such as the number of cities, standard deviation.

Another hybrid method [118] combines construction heuristics such as nearest neighbor search and tour improvement such as Lin–Kernighan [ref] local search with evolutionary computing for TSP [133]. Crossover operations which are the essential operations in evolutionary computation use an edge

based crossover operation where similar tour paths are promoted to be explored in the gene pool [92]. The authors have shown suboptimal results for the larger input sets of the TSPLIB library.

# 2.2.3 The impacts of the traveling salesman problem, a well known combinatorial optimization problem

Solving combinatorial optimization problems has an immense impact in all fields. For example, TSP which is a well known combinatorial optimization problem has been developed for solving a wide array of practical and theoretical problems. Examples include the use of TSP in music for conjunct melody generation in computer-aided composition, as well as for forming automatic playlists and track/artist suggestions - now used by Spotify and Tidal [102]. TSP heuristics have also been used for diffractometer guidance in X-ray crystallography [22]; and for Telescope scheduling in exoplanet discovery [67] as well as in galaxy imaging [26]. It can also be applied to bioinformatics as a genome ordering problem by posing the ordering as a path traveling through each gene marker [4] or as a clustering problem to solve gene expression clustering [31]. Last but not least, it can be leveraged for its original application of finding the shortest tour in a classic map, for example as a Traveling Good Samaritan Problem for the Meals for Wheels charity program in Atlanta [15].

#### 2.2.4 Targeting TSP using neural networks

Previously, TSP algorithms have employed neural networks in order to complement local search heuristics [114, 132]. Authors in [114] use Kohonen networks and devise a TSP solver. Self-organizing nature of Kohonen networks iteratively executes and tries to map neurons which are dispersed onto the 2-D Euclidean plane to the cities. At each iteration, neurons attempt to decrease the distance between the cities in the neighborhood region which is a parametric set that consists of the nearby cities. The learning rate and the neighborhood function are the hyperparameters. Because the number of neurons is higher than the cities, the algorithm presents an ordering mechanism

for selecting the best fit neurons that represent the cities.

The requirements of the vast amount of customization in optimization problems and recent advancements in neural network architectures have caught the attention of machine learning community. Vinyals et al. have proposed pointer networks which are attention based sequence-to-sequence learning architectures and presented results on TSP [131]. Without significant hyperparameter explorations, proposed architecture has managed to generate competitive results for other problems such as delaunay triangulation. However, the problem sizes have not been as large as state-of-the-art [8] which have employed TSP specific local search moves [118] and provided optimal solutions up to thousands of cities.

Bello et al. [17] recently proposed a TSP solver RL framework based on neural networks. Pointer-networks have been employed for policy gradient and expected tour length prediction. The sequential nature of the framework resembles tour construction algorithms. Stochastic sampling and the actor-critic architecture updates the expected tour length with the current policy (on-policy), and the gradient updates are worked out using reinforce algorithm [137]. Also, a separate neural network for tour exploration incorporates an expected reward based value iteration approximation. All neural networks are constructed using pointer networks [131]. Both pre-training and random initialization of the weights are realized as the initial starting state. The framework presents improved tour lengths and execution times compared to Christofides and supervised learning methods [29, 131].

The authors of [65] present a deep Q-learning [85] and a graph embedding based solution to target combinatorial optimization problems. Given a problem as the graph, they first perform function mappings such as belief propagation that learns feature vectors from latent variable models. Then, the learned embeddings allow learning a construction graph building heuristic. The Q-learning allows constructing the solution based on the reward which is defined as the change in the cost function among the candidates. A helper function is also employed that helps to satisfy the constraints of the combinatorial optimization from the partial solution throughout the construction process.

Table 2.2: Comparing TauRieL with previous deep learning based solutions

|                        | TauRieL  | Vinyals [131] | Bello [17] | Khalil [65] | Kool [69] |

|------------------------|----------|---------------|------------|-------------|-----------|

| Feed Forward Nets      | <b>√</b> | ×             | ×          | ×           | ✓         |

| Recurrent Nets         | ×        | ✓             | ✓          | <b>√</b>    | X         |

| Supervised Learning    | ×        | ✓             | <b>√</b>   | ✓           | <b>√</b>  |

| Reinforcement Learning | <b>√</b> | ×             | <b>√</b>   | ✓           | <b>√</b>  |

| Policy Based RL        | <b>√</b> | ×             | ✓          | ×           | <b>√</b>  |

| Value Based RL         | ×        | ×             | ×          | <b>√</b>    | X         |

| Input Encoder          | ×        | ✓             | <b>√</b>   | <b>√</b>    | <b>√</b>  |

| Output Decoder         | ×        | <b>√</b>      | <b>√</b>   | <b>√</b>    | ✓         |

Kool [69] proposes a TSP solver framework based on the attention model [130]. The attention mechanism consists of the input encoder and output decoder. The input encoder uses multiple attention mechanisms to compute the embeddings of the input nodes. Given an input set, the output decoder calculates a probability distribution over the input nodes using attention. The decoder includes a context embedding mechanism which includes all the node embeddings in addition to the graph embedding is defined as the mean of all the node embeddings that are generated at each hidden attention layer. In order to calculate the output probabilities of the next city in the permutation, the decoder requires the embeddings of the start city as well as the graph embeddings which displays that proposed solution is permutation variant similar to recurrent neural network based solutions. Although the results for 50 and 100 cities have improved compared to Bello et al. around 2% and 1% respectively, the reported training times have been higher than Bello et al. [17].

We compare TauRieL and the aforementioned deep learning based methods in Table 2.2. The row in the table present the features that are specific to each proposed method. For each feature, the differences and similarities of each method can be explained below:

Feed Forward, and Recurrent Nets: Although Kool [69] and TauRieL are the two architectures with feedforward layers, Kool [69] also employs attention networks that are more complicated than the conventional feedforward neural nets. Thus the attention networks are dominant blocks in the presented architecture. However, TauRieL only uses conventional feedforward neural networks, and its architectural complexity is the lowest among all the proposed methods. The rest of the proposed solutions are based on recurrent neural nets. Vinyals [131] and Bello [17] employ almost identical architectures and Khalil [65] suggests an architecture that resembles unrolled recurrent neural nets. Regarding architecture complexity, the recurrent nets surpass feedforward nets.

Supervised and Reinforcement Learning: Vinyals [131] proposes to train its network with supervised learning on various sizes of TSP problems, and Bello [17] extends this network by first training the network with supervised learning and applying REINFORCE [121] training in a reinforcement learning setting. Khalil [65] employs supervised training for generating graph embedding and then uses reinforcement learning to training the deep Q network. Similar to Bello [17], Kool [69] and TauRieL uses REINFORCE [121] algorithm to train the neural networks.

Policy and Value-Based RLs: All the works that we list in Table 2.2 except Khalil rely on policy based methods where the neural networks represent the policy. Khalil [65] employs neural networks in order to represent and approximate the Q-score [121] for constructing the graph sequentially from the embeddings for the problem at hand such as TSP.

Input and Output Decoders: All the works except TauRieL and Khalil [131] employ input-output decoder neural networks. The works proposed by Vinyals [131], Bello [17] and Kool [69] are inspired by language attention nets and seq-to-seq models [130, 120] which employ recurrent neural networks for encoding the input words sequentially and decoding for inference. Khalil [65] presents an embedding algorithm that is inspired by word2vec [84] architecture and aims to generate a vector space from graphs. TauRieL proposes to represent the latent exploration space by storing state transition probabilities explicitly in a state transition matrix. Thus, it does not make use of input encoders or output decoders.

#### Chapter 3

# AxleDB: A novel programmable query processing platform on FPGA

In this chapter, AxleDB which is one of the main contributions of this thesis is presented. AxleDB is a FPGA query processing platform which encapsulates database-specific hardware accelerators with memory and storage in a unified programmable environment. In the next section, we introduce the overall architecture of the AxleDB. The overall architecture also includes describing AxleDB's major components. In the following section, an example query is presented to show how its components are utilized to process the example query. Section 3 introduces the FPGA based filtering, arithmetic, logic and aggretgation hardware accelerators. Those accelerator units, which are the most important components of AxleDB, are presented in depth. The rest of the accelerators are introduced and briefly described as they are not in the scope of the thesis. The experiments are presented in Section 4. This section begins with evaluating the performance of the query accelarators in scope. The rest of the experimental results include system-level comparisons of AxleDB to the state-of-the-art.

Figure 3.1: Overall architecture of AxleDB with its major components. • software extensions for DBMS in the host, • Data storage units and device controllers, • a set of efficient query processing accelerators, which altogether form AxleDB Accelerators Unit (AAU), • Programmable Interconnection Unit (PIU) to manage the accesses to the off-chip data storage units, in a fully flexible fashion, • Data and Process Controller (DPC) to orchestrate the involved modules of AxleDB to process SQL queries.

#### 3.1 Architecture of AxleDB

The main principle of the proposed database query processing platform, AxleDB, is to essentially move database computations closer to where the data resides, to obtain high performance in a flexible and programmable environment. Figure 3.1 shows the overall architecture of AxleDB. AxleDB resides between the host machine that runs the DBMS, and the database storage in an SSD. In the host, we primarily targeted to use PostgreSQL [98], one of the most popular open source relational DBMS. However, the infrastructure of AxleDB was designed to be software-agnostic and could be ported to other DBMS, e.g., MonetDB [87].