# Layout Regularity

# for

# **Design and Manufacturability**

## Marc Pons Solé

Directors: Francesc Moll i Jaume Abella

Tesi presentada per obtenir el títol de Doctor per la Universitat Politècnica de Catalunya Programa: Enginyeria Electrònica

Barcelona, 08-07-2012

To my Mother, Loles.

# Contents

| Contents i   |              |                                            |                                                  |           |  |  |

|--------------|--------------|--------------------------------------------|--------------------------------------------------|-----------|--|--|

| A            | cknov        | wledgn                                     | nents                                            | v         |  |  |

| $\mathbf{A}$ | Abstract vii |                                            |                                                  |           |  |  |

| 1            | Intr         | troduction                                 |                                                  |           |  |  |

|              | 1.1          | Histor                                     | y of technology scaling                          | 1         |  |  |

|              | 1.2          | 2 Integrated circuit manufacturing process |                                                  | 3         |  |  |

|              |              | 1.2.1                                      | Overview                                         | 3         |  |  |

|              |              | 1.2.2                                      | Lithography                                      | 4         |  |  |

|              |              | 1.2.3                                      | Resolution enhancement techniques                | 7         |  |  |

|              |              | 1.2.4                                      | Electroplating and chemical mechanical polishing | 7         |  |  |

|              | 1.3          | Challenges of semiconductor industry       |                                                  |           |  |  |

|              |              | 1.3.1                                      | Manufacturing challenges                         | 11        |  |  |

|              |              | 1.3.2                                      | Design challenges                                | 17        |  |  |

|              | 1.4          | Layout regularity solution                 |                                                  | 19        |  |  |

| 2            | Rel          | ated w                                     | vork                                             | <b>21</b> |  |  |

|              | 2.1          | The need for layout regularity             |                                                  | 21        |  |  |

|              |              | 2.1.1                                      | Regularity for manufacturing                     | 21        |  |  |

|              |              | 2.1.2                                      | Regularity for design                            | 24        |  |  |

|              | 2.2          | P. Regular layout fabrics                  |                                                  |           |  |  |

|   |     | 2.2.1                | Gate Arrays                                                                        | 6 |  |  |

|---|-----|----------------------|------------------------------------------------------------------------------------|---|--|--|

|   |     | 2.2.2                | Standard Cells                                                                     | 1 |  |  |

|   |     | 2.2.3                | Structured ASICs 3'                                                                | 7 |  |  |

|   | 2.3 | Existin              | ng layout analysis tools                                                           | 9 |  |  |

|   |     | 2.3.1                | Standard DFM flow                                                                  | 0 |  |  |

|   |     | 2.3.2                | Mentor Graphics DFM tools                                                          | 1 |  |  |

|   |     | 2.3.3                | Systematic manufacturing variability models 42                                     | 2 |  |  |

|   |     | 2.3.4                | Evaluating layout regularity                                                       | 4 |  |  |

|   | 2.4 | Thesis               | works motivation                                                                   | 5 |  |  |

| 3 | Uni | que co               | ntributions of the thesis 4'                                                       | 7 |  |  |

|   | 3.1 | VCTA                 | regular fabric                                                                     | 7 |  |  |

|   | 3.2 | VCTA                 | automation tool                                                                    | 8 |  |  |

|   | 3.3 | FOCSI                | I layout regularity metric tool                                                    | 9 |  |  |

|   | 3.4 | Thesis               | dissemination                                                                      | 9 |  |  |

|   |     | 3.4.1                | Books                                                                              | 9 |  |  |

|   |     | 3.4.2                | Conferences                                                                        | 0 |  |  |

|   |     | 3.4.3                | Scientific Reports                                                                 | 1 |  |  |

|   |     | 3.4.4                | Workshops 5                                                                        | 1 |  |  |

| 4 | Eva | aluation framework 5 |                                                                                    |   |  |  |

|   | 4.1 | Compu                | itation resources                                                                  | 3 |  |  |

|   | 4.2 | Electro              | onic design automation tools $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 54$ | 4 |  |  |

|   |     | 4.2.1                | Commercial tools                                                                   | 4 |  |  |

|   |     | 4.2.2                | Data treatment                                                                     | 4 |  |  |

|   |     | 4.2.3                | C programming                                                                      | 5 |  |  |

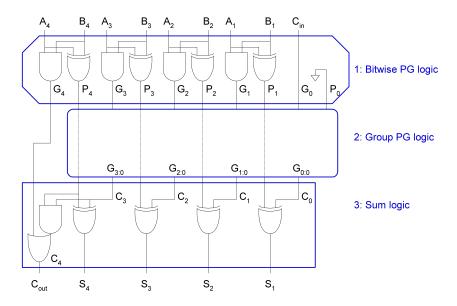

|   | 4.3 | Benchi               | mark circuits and evaluations                                                      | 5 |  |  |

|   |     | 4.3.1                | Circuits                                                                           | 5 |  |  |

|   |     | 4.3.2                | Technology nodes                                                                   | 8 |  |  |

|   |     | 4.3.3                | Layout versions                                                                    | 9 |  |  |

|   |     | 4.3.4                | Evaluations                                                                        | 0 |  |  |

| 5 | VC' | CTA regular fabric 63 |                                                                                     |     |

|---|-----|-----------------------|-------------------------------------------------------------------------------------|-----|

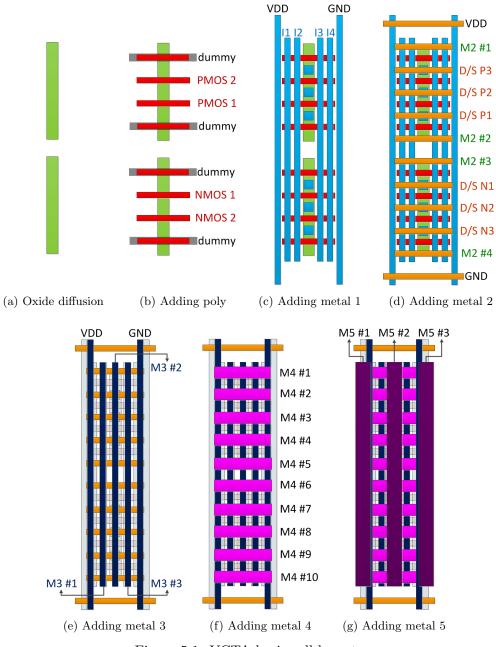

|   | 5.1 | VCTA                  | physical design                                                                     | 64  |

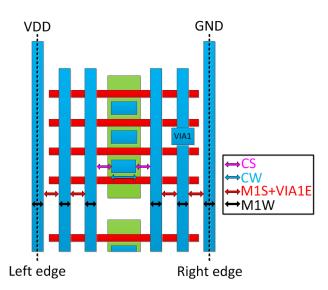

|   |     | 5.1.1                 | Maximizing layout regularity                                                        | 64  |

|   |     | 5.1.2                 | Basic cell Front-end design                                                         | 64  |

|   |     | 5.1.3                 | Basic cell Back-end design                                                          | 68  |

|   |     | 5.1.4                 | Basic cell configuration                                                            | 70  |

|   | 5.2 | VCTA                  | Basic cell impact on design                                                         | 71  |

|   |     | 5.2.1                 | Basic cell parameters                                                               | 71  |

|   |     | 5.2.2                 | Basic cell impact on area and routability                                           | 72  |

|   |     | 5.2.3                 | Basic cell impact on energy and delay $\ldots \ldots \ldots \ldots$                 | 81  |

|   | 5.3 | VCTA                  | manual layouts evaluation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 84  |

|   |     | 5.3.1                 | 32-bit adders evaluation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 85  |

|   |     | 5.3.2                 | Delay-locked loop evaluation                                                        | 90  |

|   | 5.4 | Conclu                | sion                                                                                | 97  |

| 6 | VC  | CTA Automation 99     |                                                                                     |     |

|   | 6.1 | VCTA                  | Physical Design Flow                                                                | 100 |

|   |     | 6.1.1                 | Flow overview                                                                       | 100 |

|   |     | 6.1.2                 | VCTA Grouping                                                                       | 101 |

|   |     | 6.1.3                 | VCTA Place                                                                          | 114 |

|   |     | 6.1.4                 | VCTA Routing                                                                        | 115 |

|   |     | 6.1.5                 | VCTA Layout Generation and Verification                                             | 123 |

|   | 6.2 | Result                | s and Simulations                                                                   | 125 |

|   |     | 6.2.1                 | Manual VCTA versus Automatic VCTA Flow                                              | 125 |

|   |     | 6.2.2                 | Standard Flow versus VCTA Flow                                                      | 125 |

|   | 6.3 | Conclu                | sion                                                                                | 130 |

| 7 | FOO | CSI La                | yout Regularity Metric                                                              | 133 |

|   | 7.1 |                       |                                                                                     |     |

|   |     | 7.1.1                 | Problem Statement                                                                   | 134 |

|   |     | 7.1.2                 | Layout Regularity Definition                                                        | 135 |

|   |     |                       |                                                                                     |     |

|               |        | 7.1.3  | FOCSI Proposal                     | . 136 |

|---------------|--------|--------|------------------------------------|-------|

|               |        | 7.1.4  | Single Layout Layer FOCSI          | . 137 |

|               |        | 7.1.5  | Complete Layout FOCSI              | . 137 |

|               | 7.2    | FOCS   | I for single layers                | . 138 |

|               |        | 7.2.1  | Granularities considered           | . 138 |

|               |        | 7.2.2  | ISCAS'85 layout results            | . 138 |

|               | 7.3    | FOCS   | I for the complete layout          | . 144 |

|               |        | 7.3.1  | FOCSI Layout Area sizing selection | . 145 |

|               |        | 7.3.2  | ISCAS'85 layout results            | . 146 |

|               | 7.4    | FOCS   | I regularity and variability       | . 148 |

|               |        | 7.4.1  | Variability model                  | . 148 |

|               |        | 7.4.2  | ISCAS'85 layout results            | . 150 |

|               | 7.5    | Conclu | usion                              | . 152 |

| 8             | Con    | clusio | n                                  | 155   |

|               | 8.1    | Summ   | ary of contributions               | . 156 |

|               | 8.2    | Future | e works                            | . 157 |

| Bi            | ibliog | graphy |                                    | 161   |

| $\mathbf{Li}$ | st of  | Figur  | es                                 | 169   |

| Li            | st of  | Table  | S                                  | 172   |

## Acknowledgments

The thesis started thanks to the collaboration project "Variations-Aware Circuit Designs for Microprocessors" between the Intel Barcelona Research Center and the Electronic Engineering Department of the Universitat Politècnica de Catalunya. Then it was supported by the 2008 FI-B 00557 grant from the Generalitat de Catalunya and after by the FPU AP2007-04125 grant from the Spanish Ministry of Education and Science, the European Community's Seventh Framework Programme (FP7/2007-2013) under grant agreement number 248538 (Synaptic project) and by MODERN project of the Spanish Ministry of Science and Innovation (ENIAC-120003 and PLE2009-0024).

I would like also to thank the HiPICS research group (SGR 1497) from the Electronic Engineering Department and the ARCO research group (SGR 1250) from the Computer Architecture Department, both from the Universitat Politècnica de Catalunya, the Barcelona Supercomputing Center, and the Centre Suisse d'Électronique et de Microtechnique (CSEM), from Neuchâtel in Switzerland, that helped me during my thesis.

## Abstract

In nowadays nanometer technology nodes, the semiconductor industry has to deal with the new challenges associated to technology scaling. On one hand, process developers face increasing manufacturing cost and variability, but also decreasing manufacturing yield. On the other hand, circuit designers and electronic design automation (EDA) developers have to reduce design turnaround time and provide the tools to cope with increasing design complexity and reduce the time-to-market. In this scenario, closer collaboration between all the actors involved is required. New approaches considering both design and manufacturing need to be explored. These are the so called design for manufacturability (DFM) techniques.

A DFM trend that is becoming dominant is to make circuit layouts more regular and repetitive. The regular layout fabrics are based on the configuration of a simplified mask set, therefore reducing the manufacturing cost. Moreover, a reduced number of layout patterns is used, allowing better process variability control and optimization. Hence, regularity reduces layout complexity and therefore design complexity, allowing faster time-to-market.

In this thesis, we explore forcing maximum layout regularity focusing on future technology nodes, with increasing design and manufacturability issues, where we expect layout regularity to be mandatory. With this objective, we have developed a new regular layout fabric called Via-Configurable Transistor Array (VCTA). The physical design is fully explained involving layout and geometrical

ABSTRACT

considerations for transistors and interconnects.

Initially, VCTA layouts developed manually have been evaluated in terms of manufacturability, but also in terms of area, energy and delay. For digital design, 32-bit binary adders designed with VCTA have been compared to standard cell layouts. For analog design, a delay-locked loop design using VCTA has been compared to its full custom version.

We have also developed a physical synthesis tool that allows us to obtain VCTA circuit layouts in an automated way. Developing our own automation tool lets us controlling all the decisions made during the physical design flow to ensure that maximum layout regularity is respected. In this case the work is based on several algorithms, for instance for routing, that we have oriented to the area optimization of the layouts.

Finally, in order to demonstrate the benefits of layout regularity, we have proposed a new layout regularity metric called Fixed Origin Corner Square Inspection (FOCSI). It is based on the geometrical inspection of the patterns in the layouts and it allows designers to compare regularity of designs but also how their regularity will impact their manufacturability. The FOCSI layout analysis tool can be used to optimize manufacturability.

## Chapter 1

## Introduction

Integrated circuits are more and more present in our life. From personal computers to smart-phones, or hidden electronics in cars, we are all using integrated circuits in our daily life. There are infinite examples. As layout minimum feature sizes shrink, more elements can be integrated in a single chip allowing new applications and capabilities. However, this is a challenging trend that requires enormous efforts from the semiconductor industry including manufacturers, designers and electronic design automation (EDA) developers.

In section 1.1 we first present an historical overview of technology scaling. Then, in section 1.2 we explain the integrated circuit manufacturing flow. In section 1.3 we detail the resulting challenges that have to be faced to fulfill the requirements of nowadays nanometer technologies. Finally, in section 1.4 we introduce the concept of layout regularity that is a possible solution for the semiconductor industry and that is the focus of the thesis.

### 1.1 History of technology scaling

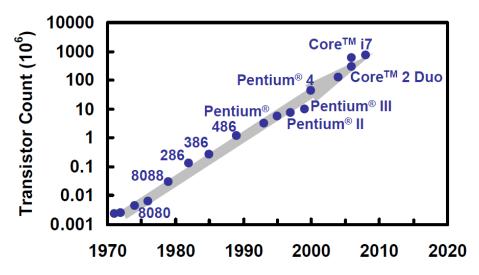

Moore's Law, first proposed in 1965 by Gordon Moore, one of Intel's co-founders, predicted that every year the number of transistors in a chip will double. Ten years later, in 1975, it was modified so that from 1980 the number of transistors will double every two years. Up to now Moore's law is still being followed. In a way it is a self-fulfilling prophecy as it is not based on fundamental arguments, but the semiconductor industry is making enormous efforts to accomplish this goal. A good example of these efforts is depicted in Figure 1.1 that shows the continuous increasing evolution of the number of transistors in Intel's processors.

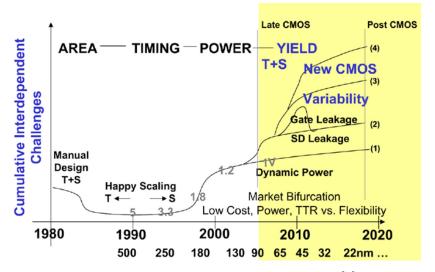

In Figure 1.2 are shown the scaling challenges faced by the semiconductor industry from the manual design to nowadays. Based on a robust manufacturing process and on the appropriate EDA tools, in the first years of technology scaling, named the years of "happy" scaling, designers dealt with energy, delay and area problems. However, when reaching the deep submicron era, for technologies under 100 nm, new issues arose related to yield, defined as the percentage of good circuits over the total number manufactured. In particular, manufacturing variability is now one of the major challenges. Therefore new design for manufacturability (DFM) approaches coming both from designers and manufacturers sides, and allowed by EDA developers, are required [1, 2].

Figure 1.1: Moore's Law continues. Source: Intel.

Figure 1.2: Technology scaling challenges [3].

### 1.2 Integrated circuit manufacturing process

#### 1.2.1 Overview

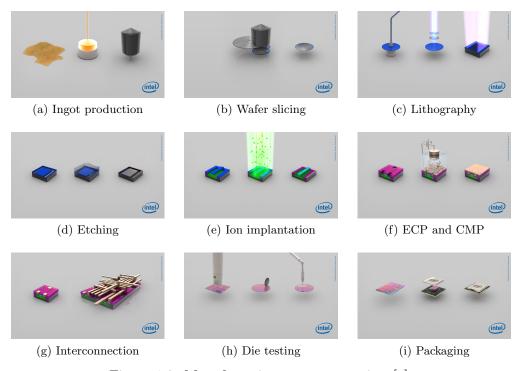

Today's CMOS technology nodes with minimum feature sizes reaching 22 nm and below involve multi-disciplinary manufacturing processes like ingot production, lithography, ion implantation, electroplating (ECP) or chemical-mechanical polishing (CMP). Each of these steps of the process require strict manufacturing control and are very challenging for deep submicron technologies. Figure 1.3 illustrates in a schematic way several of the steps involved in the manufacturing process flow from sand to the final encapsulated chip.

Typically, the integrated circuit manufacturing flow can be divided in three parts [4]:

- FEOL: front-end of line, for the manufacturing of transistors (PMOS and NMOS). Accurate control of transistor channel length and width, oxide thickness and dopant placement are amongst the main challenges during this step.

- MEOL: middle-end of line, for pre-metallic dielectric (PMD) and contacts

between transistors and interconnects. PMD isolates the FEOL from the back-end of line (BEOL explained next) and protect transistors. For this step the variability affects metal width and thickness as well as interlayer dielectric thickness.

• BEOL: back-end of line, for the rest of the interconnect metal layers and the vias connecting them. The goal is to create circuit functionality by interconnecting transistors and providing ground and power supplies. As for MEOL, variations appear in metal width and thickness as well as interlayer dielectric thickness, but concerning the upper metal layers.

Figure 1.3: Manufacturing process overview [5].

#### 1.2.2 Lithography

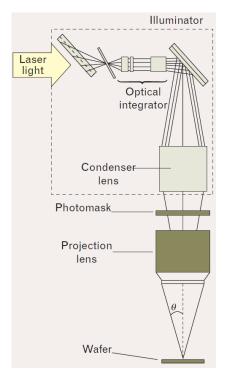

Lithography is used to obtain in the silicon wafers the small patterns of circuit layouts. It is based on projecting the pattern through a mask (including the shapes four times bigger than the desired shapes) on a photo-sensitive layer on the top of the wafer. The photo-sensitive layer (also called resist) is then developed. If the resist is positive, the illuminated parts are eliminated. On the other hand, if the resist is negative, the non illuminated parts are eliminated. The remaining resist is then used as a protection for etching or implantation. Figure 1.4 shows the projection lithography system.

Figure 1.4: Projection lithography system [6].

The source of light is a monochrome laser treated with an illuminator to tune the angular content of light before traversing the photomask or reticle. The refracted light is then treated by a projection lens to reach the resist and form the image desired in the wafer. As traversing the reticle is equivalent to a Fourier Transform, the projection lens acts as a 2D Inverse Fourier Transform. Finally the resist detects light intensity.

The resolution of the image obtained using lithography is limited by the numerical aperture (NA) of the projection lens, by the wavelength of the laser source ( $\lambda$ ) and by the Rayleigh constant ( $k_1$ ), following equation (1.1). A 0.6

value for the  $k_1$  parameter is required to ensure high pattern fidelity.

$$resolution = k_1 \cdot \frac{\lambda}{NA} \tag{1.1}$$

Added to this complex system, the lithography tool presents non-idealities. For instance, light intensity (also referred as dose) and distance to the resist (also referred as focus) vary. For dose, the variation observed in patterns of the layout depends on the slope of the light intensity when going from illuminated to non-illuminated zones. Ideally, the slope should be infinite at the edges of the patterns for maximum resolution. However, this is not the case for real tools and a variation in light intensity will cause a variation in the printed shapes. For the distance to the resist, there is an ideal distance, or optimum focus, where all light waves coming from different angles have the intended phase offset relative to each other and this way form a projection of the desired image on the reticle. However, when the position of the resist varies, generating defocus, the image also varies. Mask has also imperfections associated to its own manufacturing process.

Figure 1.5: Sub-wavelength lithography gap. Source: Intel.

#### 1.2.3 Resolution enhancement techniques

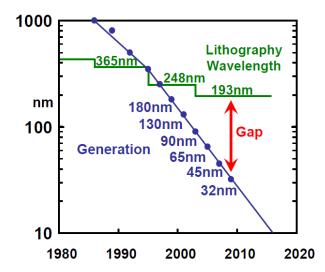

The conventional way to allow good resolution and, therefore, acceptable manufacturability when scaling down technologies, was to reduce the source of light wavelength ( $\lambda$ ). However, for the last five technology nodes spanning from 90 nm to 22 nm the same 193 nm wavelength argon fluoride laser source is still being used due to the delays and challenges in developing, first, the fluorine 157 nm lithography systems, that was abandoned, and, second, the 13.4 nm extreme ultraviolet lithography (EUVL), that is expected to be available in 2013. Figure 1.5 shows the gap between lithography wavelength and critical feature sizes.

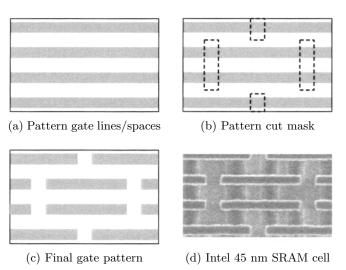

Therefore, for advanced technology nodes, these sub-wavelength lithography technologies require advanced resolution enhancement techniques (RETs) that allow reducing  $k_1$  factor to values near 0.25 while maintaining good pattern fidelity. Amongst them there are techniques such as phase-shift mask (PSM), optical proximity correction (OPC) or double pattern technology (DPT). The principles of DPT, PSM and OPC are depicted in Figures 1.6, 1.7 and 1.8. Immersion lithography has also been introduced in last technology nodes to obtain an ultrahigh numerical aperture (NA) that also increase lithography resolution. However, these techniques are not effective for complex circuits with arbitrary layout patterns [7, 8, 9] and manufacturing variability still appears in effects like corner rounding or line-end shortening. For instance, for the widely used standard cell approach, considering a library of 1000 standard cells, there are approximately 2 million possible configurations to arrange a pair of standard cells. This large number of possible arrangements makes RETs computationally difficult.

#### 1.2.4 Electroplating and chemical mechanical polishing

Another process steps that will influence circuit variability are electroplating (ECP) and chemical mechanical polishing (CMP), that are very correlated and are used for metal deposition and planarization.

Figure 1.6: Double Patterning process flow [10].

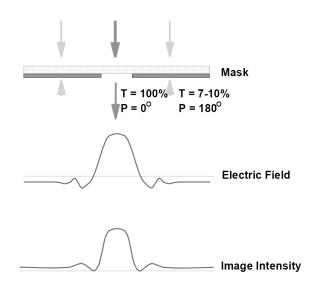

Figure 1.7: Phase Shift Mask. PSM lithography improves pattern fidelity by darkening the edges of shapes through destructive interference of light using a mildly translucent photomask. T is the amount of light that trespasses the photomask. P is its phase. [11]

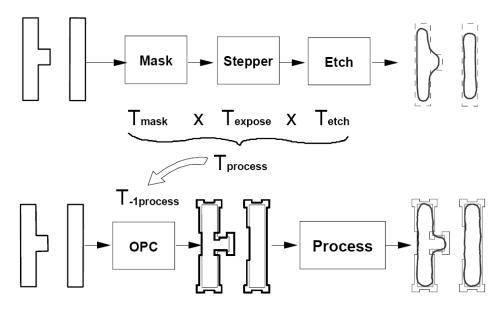

Figure 1.8: Optical Proximity Correction. OPC begins by characterizing the patterning operation and all its inaccuracies from various sources. This mathematical description of the process is used in iterative optimization routines to pre-distort the mask shapes to compensate for known, systematic, and modeled patterning inaccuracies. [11]

#### 1.2.4.1 Electroplating

Patterned trenches for wires and vias are filled with copper using ECP. It is based on an electro-chemical copper deposition where the wafer acts as a cathode and solid copper as an anode in a plating solution containing copper ions, the electrolyte. Four chemical additives have to be adjusted to control the copper growth in the trenches [4]. These additives are:

- Suppressors, to restrain local growth.

- Chloride ions, to facilitate the suppressor adsorption.

- Accelerators, to enable local growth acceleration.

- Levelers, to reduce surface topography.

The control of these additives is critical to avoid the formation of voids in the resulting vias and wires. Moreover, different patterns of the trenches with different metal densities systematically produce variations in the thickness of the copper grown.

#### 1.2.4.2 Chemical mechanical polishing

Chemical Mechanical Polishing (CMP) is used for planarization of metal layers after ECP. The excessive metal is etched away applying rotating pressure in a mechanical way with a pad while adding abrasive particles to the surface of the wafer. Therefore it is a combination of mechanical and chemical processes.

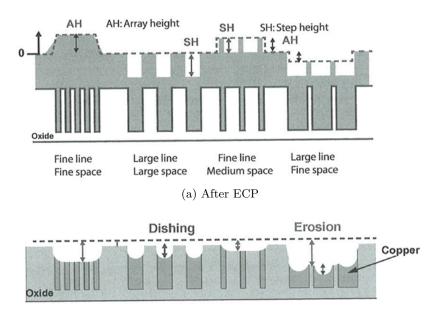

Due to surface irregularities because of different metal growth from ECP, the result of CMP is not a perfectly planar wafer (Figure 1.9). Effects like scratches, under polishing, dishing and erosion appear. Then, when applying lithography over this surface, focus variability occurs and leads to process variations in the upper metal layers. These variations will impact wires and vias behaviors.

(b) After CMP

Figure 1.9: Electroplating and Chemical Mechanical Polishing interactions [4].

#### 1.2.4.3 Metal filling

Metal characteristics will vary substantially depending on layout and intra-layer density variations, neighborhood layout patterns and the underlying topology. That is why, to deal with variability arising from ECP–CMP interactions, dummy metal features in free spaces of the layers are added to obtain density of the materials as uniform as possible. In that way, metal growth is more uniform and so will be the resulting planarization. However as density will remain variable depending on the circuit designed, planarization variability will still occur.

### 1.3 Challenges of semiconductor industry

The semiconductor industry is facing increasing challenges related to the integrated circuit manufacturing process but also to the design productivity. Regarding the manufacturing process, critical issues are equipment cost, as well as mask cost, and the manufacturing variability an yield. Regarding design productivity, the problem is centered on the time-to-market and also on cost. Turnaround time required to obtain working circuits is increasing because of circuit variability, as well as is increasing the EDA tools computational effort required to deal with design complexity.

#### 1.3.1 Manufacturing challenges

#### 1.3.1.1 Manufacturing cost

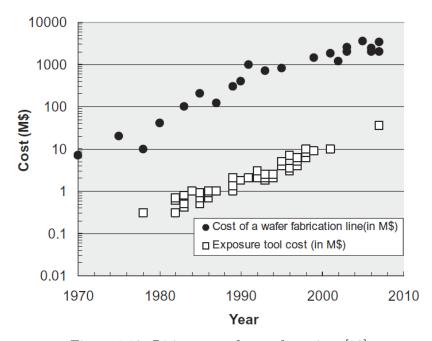

The major contributor to manufacturing cost is equipment cost. In Figure 1.10 we can see how the wafer fabrication line cost (that includes the lithography exposure tools cost) has increased exponentially over the years of technology scaling. Nowadays, the cost can reach more than \$4 billion.

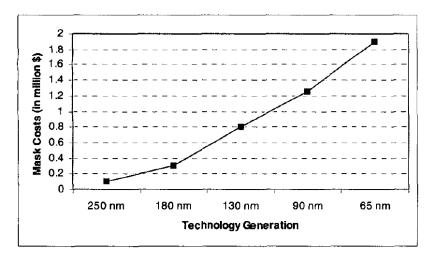

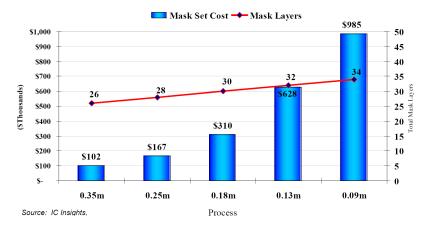

Mask cost is also critical as new masks are required for each of the designs developed. Figures 1.11 and 1.12 show how the mask cost of the standard cell approach increases with every technology node, associated to the mask complexity increase, in terms of the number of mask layers. The mask cost has increased from \$102 thousand dollars, for a 350 nm design, to almost \$2 million, for a 65 nm design.

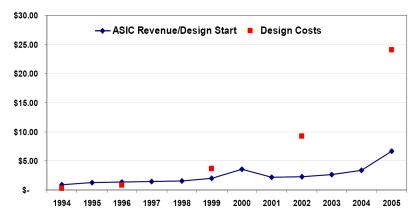

To illustrate the cost challenge faced by the semiconductor industry, in Figure 1.13 we can see how design costs surpass revenues for application specific integrated circuits (ASICs). New approaches are required.

Figure 1.10: Rising cost of manufacturing. [12]

#### 1.3.1.2 Manufacturing variability

Due to the limitations of the different steps involved in the manufacturing process, transistor and interconnect parameters vary. For integrated circuits, process variations are defined as the deviation from the expected nominal value of the characteristics of these transistors or interconnects. This deviation is calculated from a large number of samples.

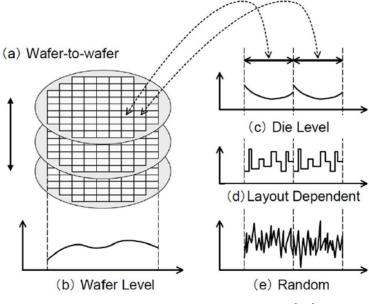

Depending on the mechanism involved, we can observe different scales of process variations, such as within-die (WID), die-to-die (D2D) and wafer-to-wafer (W2W). Process variations can also be classified depending on their behavior: they can be systematic or random variations. The resulting parameter varia-

Figure 1.11: Rising cost of a CMOS standard cell mask set. [7]

Figure 1.12: Mask layers and cost per technology node. [13]

Figure 1.13: Average revenue and design costs per year. [13]

Figure 1.14: Variability classification [14].

tion from the nominal value will come from the combination of both deviations. Variability classification is depicted in Figure 1.14.

The systematic deviation component models the parameter variations that can be predicted by manufacturing environment and layout geometry (Figure 1.14 from (a) to (d)). This component is due to unintentional shifts in process conditions and to lithography tools [15]. On one hand, regarding process conditions, the systematic deviation includes the D2D and the W2W parameters variations. It also includes the WID variations that depend on the position and orientation of the device or the interconnect on the die. In general, for process conditions, the difference between the systematic deviation levels for the parameters of two devices in the same die will be smaller than the one of two devices in different dies. Similarly, the level of deviation between devices close to each other will be lower than the one of devices in separate regions of the same die.

On the other hand, due to lithography tools limitations, depending on the particular layout neighborhood, shapes will also be affected by different variations. Models for these mechanisms have been investigated and can be applied to predict the amount of variations related to them (e.g., dose and focus variability models).

The random deviation component models the parameter variations that are uncorrelated with the position on the die and that are not deterministic (Figure 1.14 (e)). This component is related to atomic-level differences between devices [15]. For instance, because of the random dopant placement in the transistor channel that shows no correlation between different devices even if they are one next to each other, threshold voltage variations can be considered random and independent for each device. In fact, the random dopant placement in small-geometry devices is especially important because it causes mismatch between neighboring transistors [16]. These variations are modeled with a normal (or Gaussian) distribution because any variable that is the sum of a large number of independent factors is likely to be normally distributed. Note that the goal of manufacturers is to find the models for these variations, nowadays considered as random, to be able to predict them and treat them as systematic variations.

#### 1.3.1.3 Manufacturing yield

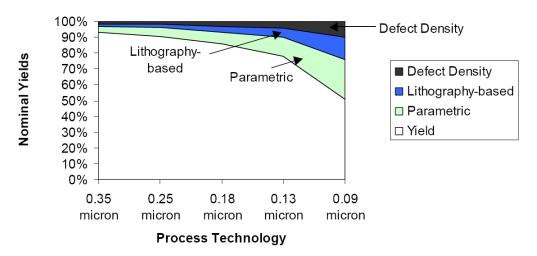

As explained before, integrated circuits yield can be defined as the percentage of good circuits manufactured over the total. Figure 1.15 shows the detailed components of yield loss for different technologies. On one hand, defect-density related problems are caused by actual errors with the silicon, such as when a contaminating particle is introduced during fabrication. This component is not related to variability issues. However, for the other two components of yield loss, variability is a major concern. Most of the lithography based failures occur when there are defects on the masks or due to layout pattern dependent issues. In this case, systematic variability is the origin of yield loss. Parametric yield loss, on the other hand, occurs because the manufactured chip does not meet a design parameter, like frequency or power dissipation. In this case, yield loss can be caused by design errors but also because of random and systematic variability.

Figure 1.15: Yield factors for different process technologies. [17]

In order of importance, first, we have the parametric yield loss (25% for 90 nm). Second, we have systematic lithography based failures (15% of yield loss for 90 nm). Finally, we have random defect-density related problems (10% of yield loss for 90 nm). Chip yields are expected to drop from over 90% for 350nm to around 50% or less for 90nm. Furthermore, this trend will continue for next technology nodes [18].

### 1.3.2 Design challenges

#### 1.3.2.1 Design cost

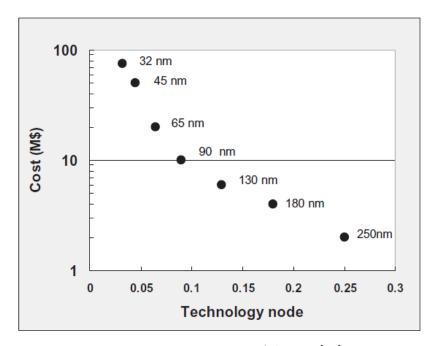

As well as manufacturing cost, design cost has also increased considerably due to technology scaling. In Figure 1.16 we can see how it is reaching \$75 million for the 32 nm technology node. In fact it is directly related to the difficulties in design verification that require increasing turnaround time. Even if efforts to improve verification tools have been invested, designs are not anymore directly working on the first tapeout like for past technology nodes.

Figure 1.16: Rising cost of design. [12]

#### 1.3.2.2 Design turnaround time

Manufacturing variability leads to variations in performance and power consumption of circuits. A large variety of numbers can be found in the literature for the impact on power and performance of process variations in different sorts of circuit. For instance, considering only transistor variations in a wafer, about 30% variation in chip frequency and 20x variation in chip leakage have been observed [19]. Other predictions show that process variations for gates and wires result in a maximum 40% circuit performance variation and a 55% circuit power dissipation variation [20]. In the field of microprocessor functional units, some results have been published for different adder implementations showing variations on both power and performance around 20% [15]. Other authors assume a 10-15% delay variation for single gates [21].

This power and performance unpredictability is taken into account by designers by adding pessimistic guard bands to ensure that the design meets the specifications. Therefore, more design iterations are required. In fact, unpredictability can cause two kinds of problems. On one hand, if variability in power and performance is overestimated, the design guard bands lead to an increase in the design effort as stated before. However, on the other hand, underestimating the variability will relax design requirements but will also require an increase in the manufacturing effort to ensure acceptable yield. In both cases, this will represent an increase in the cost and the time-to-market that can be critical for the success of the product.

#### 1.3.2.3 Design complexity

With technology scaling, the capabilities of integration are increased. Therefore design complexity is also increased. Also, the amount of design rules in layout is increasing for advanced technology nodes due to lithography limitations. As explained before, RETs like OPC or DPT are not effective for complex layouts with arbitrary layout patterns. The verification tools show also limitations. The challenge faced by EDA developers is here to provide the tools to cope with design complexity in an efficient way to reduce the design effort and also the time-to-market and their associated costs. Important efforts have to be invested in synthesis and analysis tools to take profit of the scaling benefits.

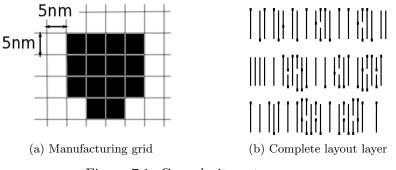

#### 1.4 Layout regularity solution

Layout regularity can be defined as the repetitivity of layout patterns or layouts blocks in the design. Depending on the granularity, it can be referred as microregularity (for repetitivity at pattern level, for small sizes of layout) or as macroregularity (for repetitivity at block level, for higher sizes of layout). The goal is to design with a reduced set of layout bricks (e.g., patterns or blocks), making small configuration changes to generate different circuits, with the objective of tackling with manufacturing and design challenges for nanometer technologies. Regular layouts require a simplified mask set, therefore reducing the manufacturing cost and allowing better process control. Moreover, layout complexity reduction also reduces design complexity and therefore the design time.

In the 2011 edition of the International Technology Roadmap for Semiconductors (ITRS [20]), that is nowadays the reference for technology scaling needs, it is stated: **Cost-effective product manufacturing also requires continu**ous improvements in the area of design for manufacturability, specifically areas such as design to minimize performance/power variability, lithography-friendly designs (regular layout styles consistent with increasingly more restrictive design rules), and design for testability and reliability.

Layout regularity is a DFM technique to address the manufacturing and design challenges in advanced technology nodes and it is the solution that we have adopted in the thesis.

## Chapter 2

## **Related work**

Layout regularity was first introduced in the early 1980s. At that time, the issue addressed was from the design side. In fact, designing integrated circuits required reducing layout complexity as no EDA tools were available. However, nowadays, layout regularity is also focused on manufacturability issues, that were not critical in the past. In section 2.1 we explain why layout regularity is becoming mandatory to tackle nowadays design and manufacturing challenges. The first regular layout fabrics and how they have evolved to nowadays fabrics are explained in section 2.2. Then, in section 2.3 we describe the existing layout analysis tools that can be used to evaluate manufacturability. Finally, in section 2.4 we justify the thesis works based on the related works presented.

### 2.1 The need for layout regularity

#### 2.1.1 Regularity for manufacturing

#### 2.1.1.1 Reducing manufacturing cost

The cost reduction due to layout regularity is based on reducing the mask cost. Regularity allows design with a reduced set of masks, that can be reused in their majority for different designs. Only the masks devoted to the configuration of the particular circuit vary from one design to the other.

#### 2.1.1.2 Reducing manufacturing variability

Improving layout regularity is arising as a possible solution for manufacturers to reduce systematic variability [22, 12, 23, 24, 25]. Regular designs are composed by a reduced number of layout patterns in silicon and also in metal. Therefore, layout and intra-layer density variations are minimized thus reducing the manufacturing process variations associated to electroplating (ECP) and chemical mechanical polishing (CMP). Moreover, the number of possible layout neighborhoods is also reduced. The main benefit is the reduction of the amount of systematic process variations by allowing RETs (like OPC or DPT explained before) to more effectively mitigate lithography printability issues. Only a few layout patterns need to be optimized for manufacturability and therefore better process variability control can be achieved.

#### 2.1.1.3 Improving manufacturing yield

Every two years a technology node starts at the first small circuit or transistor fabrication [26]. Then, huge investments are required in order to reach commercial chips yield. For deep sub-micron technologies the initial yield is around 15-20% and the time-to-market can last three years before reaching maximum chip yield around 50-60% [27, 28, 29].

In the first year the major part of the yield improvement takes place, then the improvement slows down every year. For the sake of illustrating this evolution we will consider that a 70% of the yield improvement occurs in the first year, 18% during second year, and 12% in the last year. In the case of regular layouts considering DFM techniques, we expect that this behavior can be compressed to one year.

Regarding the initial yield increase of regular layout proposals, we have to examine the different factors causing yield loss as explained before. For parametric yield loss (25% for 90 nm), once the design will be optimized, we hope the yield loss for regular designs will be lower than the one for standard designs because of

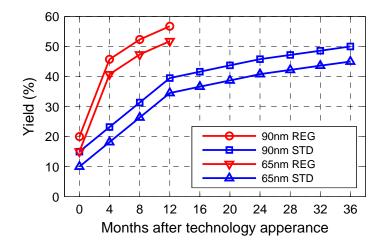

Figure 2.1: Yield predictions for standard (STD) and regular (REG) approaches. We have considered that the regular design initial yield is increased by a 5% and that yield improvement rate is increased by a 1.5 factor over a year

the manufacturing variability reduction that will increase design predictability. For systematic lithography based failures (15% of yield loss for 90 nm), regular designs are expected to perform much better than standard. In fact, by forcing layout regularity in both devices and interconnects, regular structures will reduce systematic yield losses associated to lithography tools and resolution enhancement techniques as we have explained. Finally, for random defect-density related problems (10% of yield loss for 90 nm), it is possible that regular designs perform worse than standard due to the area overhead that can be introduced by enforcing regularity. In any case, it is the less important contributor to yield loss and it is not expected to grow noticeably as opposed to the other sources of yield loss. Considering the hypothesis presented above, we have assumed that regular designs will have a little advantage in front of standard designs in terms of yield. That is why we have considered a 5% initial yield improvement in order to illustrate regular layout benefits.

We also analyze the yield improvement rate over time. The difference in speed between regular designs and standard yield evolutions is because regular is based on the repetition of a reduced set of basic blocks. The yield improvement over time is accelerated because only a reduced number of layout patterns has to be optimized. That is why we have considered that yield improvement rate for regular designs is increased by a given factor. Note that such ratio depends strongly on the process technology and the manufacturer so it may vary a lot across different technologies and manufacturers. We have set such factor to 1.5 for the sake of illustrating potential benefits of regular designs on yield.

Based on the assumptions explained about yield evolution, initial yield level and yield improvement rate, Figure 2.1 shows predicted yield evolution for the 90 nm and 65 nm technology nodes compared to the expected yield evolution of regular layout design techniques. We can see how it is very likely that regular designs provide high yield after one year of development for a given technology node (i.e., 65 nm) when the standard approach provides acceptable yield for the previous technology node (i.e., 90 nm), that has appeared two years before but has been developed during three years. Although this is just a rough evaluation of yield, it illustrates the advantages of regular layouts with respect to standard design.

#### 2.1.2 Regularity for design

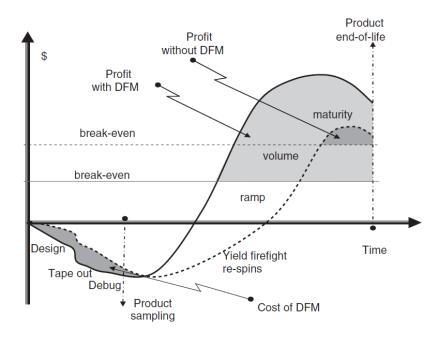

To illustrate the benefits of layout regularity from the point of view of design, we will refer to Figure 2.2 that compares the life cycle of a design with and without including DFM techniques like improving layout regularity. In summary, we can see how DFM is predicted to reduce the time-to-market and therefore to increase the profit.

#### 2.1.2.1 Reducing design cost

As we can see in Figure 2.2, a higher design effort is required at the beginning of the life cycle using a regular fabric, because the bricks to be repeated and the way to configure them have to be developed. However, once the fabric bricks defined, the design cost is reduced because less design re-spins are required (also referred as turnaround time, see next subsection). Furthermore, as the fabric complexity is reduced because of the reduced set of bricks, the portability of

Figure 2.2: Economics of DFM. Dashed line represents the design without DFM. Solid line is for the design deploying DFM. [12]

designs is increased. For instance, when scaling down one technology, the work to develop the fabric will be also reduced.

## 2.1.2.2 Reducing turnaround time

Layout regularity reduces manufacturing variability. Therefore circuit unpredictability is mitigated and design guard bands can be better estimated. This is the reason why design effort and turnaround time are reduced with layout regularity. It is indicated in Figure 2.2 as the phase of yield firefight re-spins where you can see that the DFM design curve has a higher slope than the standard design curve.

#### 2.1.2.3 Reducing complexity

Layout regularity reduces the amount of design possibilities by imposing stricter design rules and methodologies to generate the circuits. Therefore, EDA tools have to deal with less complex designs and can be optimized. For instance, as we have explained previously, RETs become more effective in reducing manufacturing variability when improving layout regularity, but RETs also become easy and fast to achieve if compared with the resources and time spent on correcting and optimizing masks for irregular layouts [13]. Therefore the time-to-market can be reduced, such as in SRAM designs. Even if the design of the SRAM cell is critical, SRAM designs get to the market long before conventional logic designs because only one cell has to be optimized.

## 2.2 Regular layout fabrics

The first regular fabric proposals are gate arrays (GAs) which tackle the lack of EDA tools in the 1980s. Another set of proposals consist of standard cells which address the design of large complex integrated circuits. Finally, we introduce structured ASICs which focus on increasing regularity to mitigate manufacturing variability [30, 31].

## 2.2.1 Gate Arrays

### 2.2.1.1 Gate Matrix

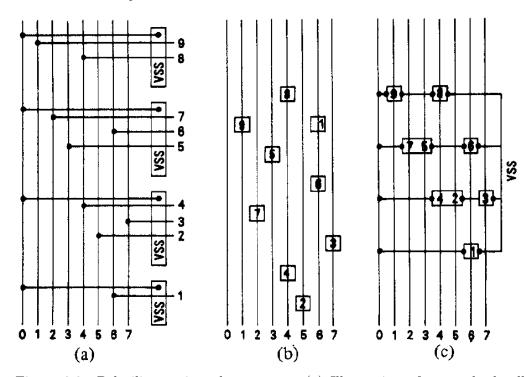

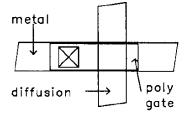

Regular designs were first considered in the early 1980s as a systematic approach to chip layout when EDA tools were in development and did not have nowadays capabilities. Some of the first proposals are based on the concept of gate matrix (GM) where the regular intersection of rows and columns provide transistors and interconnections. There are two types of such structures that are shown in Figures 2.3 and 2.4. First, polysilicon oriented structures, where polysilicon columns, in which transistors are placed, are connected using metal rows to implement the function [32]. Second, there are metal oriented structures, where the intersection of metal rows, containing polysilicon gates, and diffusion columns generate transistors already connected [33].

In both cases, transistor regularity is achieved. However, interconnect regularity is not taken into account because interconnections are configured depending

on the functions synthesized.

Figure 2.3: Polysilicon oriented structure. (a) Illustration of a standard cell configuration. (b)Polysilicon lines (matrix columns) which correspond to the inputs and outputs of the circuit with the transistors placed on their gating line. (c) The transistors have been grouped (matrix rows) and the interconnections are made with metal or diffusion. [32]

Figure 2.4: Metal oriented MOS transistor. [33]

The physical design of these GM proposals involves solving the gate matrix layout problem (GMLP) for instance using a constructive genetic algorithm (CGA) [34]. The main objective is to minimize the area of the final layout by arranging the circuit transistors in the GM. The number of metal rows used (also referred as routing tracks) as well as the total wire length are included in the cost factors of the solution.

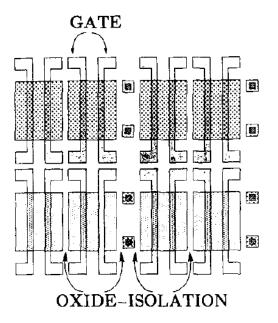

#### 2.2.1.2 High-Density Gate Arrays

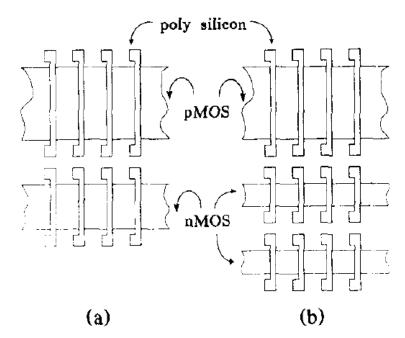

High-density gate arrays (HDGAs) are an evolution of GAs [35]. They are based on the optimized implementation of the structures called sea-of-transistors and sea-of-gates. The basic cells of the sea-of-gates structure proposal are gates from four to eight transistors isolated by means of oxide isolation as shown in Figure 2.5. For sea-of-transistors all transistors of the same type P or N share the same diffusion. This structure is depicted in Figure 2.6. Some circuits require transistors of different sizes and transistor gates usually share the same input. That is the reason why the common-gate HDGA structure presented on Figure 2.7 has been proposed with transistors of different sizes.

For HDGAs, transistor regularity is achieved if no different transistor sizes are considered. Interconnect regularity is not ensured because of the configuration of the wires like for GM.

Figure 2.5: Typical example of a Sea-of-Gates architecture. [35]

Figure 2.6: Sea-of-Transistors design. (a) Typical example of a Sea-of-Transistors architecture (b) Sea-of-Transistors architecture with multiple NMOS transistors. [35]

Figure 2.7: The common-gate HDGA architecture. [35]

The physical design is determined by routability requirements [36]. Routing is performed over the basic cells, therefore routing tracks positions are reserved during the cell design depending on the circuit needs. Routing algorithms are oriented to avoid routing congestion and discouraging interconnections over potential input and output positions of the cells. For placement, min-cut heuristics are used to minimize the number of interconnections that will cross the cells (to minimize routing congestion), and distances of interconnections are minimized using a quadratic metric.

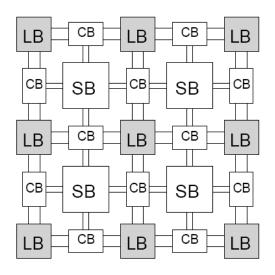

#### 2.2.1.3 Field Programmable Gate Arrays

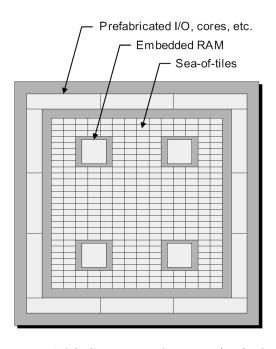

Nowadays GAs have evolved into FPGA. The basic structure is conformed by logic blocks (LB), including Lookup Tables (LUTs) and Flip-Flops (FFs) plus the programming overhead, that are interconnected using routing blocks, consisting of connection boxes (CB) and switch boxes (SB) [37]. A possible structure is shown in Figure 2.8. The performance, power and area costs compared to the standard cell approach are in general too high because of the reconfigurability capability that it offers.

FPGA structure has a smaller degree of transistor regularity than the previous structures presented because of the use of different basic blocks with its own layout. However, interconnect regularity is achieved having prefabricated wires all along the circuit that only have to be programmed depending on the function to be implemented.

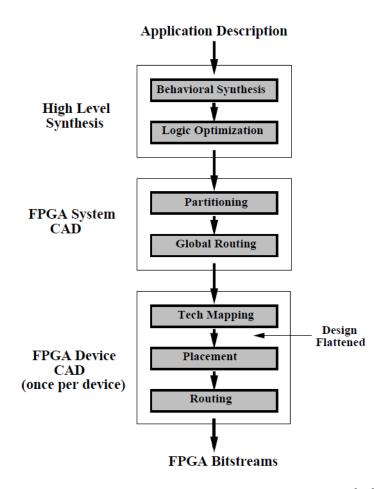

The configuration of an FPGA involves a reconfigurable computing synthesis flow that can be seen in Figure 2.9. The application description is usually described in a hardware description language (e.g., VHDL or Verilog) that is translated into a gate level netlist through the high level synthesis. Then, depending on the FPGA system, this netlist is divided into blocks that meet the FPGA resources defining the global routing that will be required between them. Then, the blocks are mapped into the FPGAs resources and are placed and routed minimizing the total design wire length of all design interconnections. The bit-

Figure 2.8: FPGA architecture example. [37]

stream is the configuration data to be loaded into the FPGA. There are also libraries of optimized circuit blocks bitstreams that can be directly loaded into the FPGA.

## 2.2.2 Standard Cells

With increasing circuit complexity, GAs also evolved into the standard cell design in parallel to the FPGA approach. Along with semiconductor manufacturing advances, standard cell methodology was responsible for allowing designers to scale ASICs from comparatively simple single-function integrated circuits (of several thousand gates), to complex multi-million gate devices (systems-on-chip).

A standard cell is a group of transistor and interconnect structures, which provides a boolean logic function (like NAND, NOR, XOR, inverters) or a storage function (flip-flop or latch). Ensuring that all standard cells have the same height, the resulting chip layout is composed, in a structured way, by rows of standard cells.

Nowadays, the major issue of this technique is that it is based on a too large library of standard cells. This results, like we have seen previously, on an extreme

Figure 2.9: Reconfigurable Computing Synthesis Flow. [38]

layout irregularity because of the multiple ways of arranging the standard cells, and thus, on DFM and RETs inefficiencies.

#### 2.2.2.1 Regular Logic Bricks

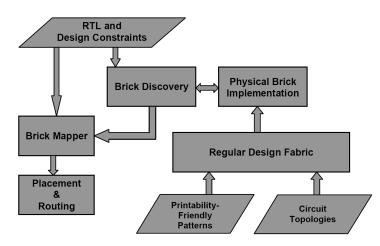

Reducing the number of standard cells of your library, you can have great benefits. This is the basic idea used by one of the most promising approaches to exploit regular designs that is being developed at the Carnegie Melon University. It is based on the concept of regular "Logic Bricks" [39] and obtains similar results to the standard cell approach in terms of area and performance but with a limited set of standard cells that are chosen to synthesize a given block. This way, the number of critical layout patterns are minimized and regularity is improved. The "Logic Bricks" discovery is shown in Figure 2.10. Moreover this reduced number of layout patterns inside of the bricks allows layout "pushed-rules" that are less pessimistic than common design rules leading to an area reduction [8, 40].

The experiments performed for the 65nm technology node for the implementation of an ARM9 microprocessor, using only 16 types of bricks, show a 6.67% increase in silicon area utilization and the same timing.

The transistor as well as the interconnect regularities are in this case function dependent, because they depend on the "Logic Bricks" selected to synthesize the function of the circuit. Therefore, the full chip regularity is not ensured. This kind of designs is an intermediate point between the ASIC approach and the fully regular designs. "Logic bricks" exploit the trade-off between area, power, performance and layout regularity.

#### 2.2.2.2 Standard cells with improved regularity

The regularity of standard cell designs has been improved by Intel or AMD using polysilicon dummy features [41]. Regular structures for transistors also using dummies reduce the stress-induced performance variations [42]. Layout uniformity has also been shown to reduce yield loss associated to critical area [43]. Other works at Tela Innovations using gridded design rules have been shown to

Figure 2.10: Logic Bricks Discovery. Before the physical design flow (Brick Mapper and Placement and Routing), Logic Bricks are selected depending on the circuit under study and the manufacturability requirements. [8]

reduce gate critical dimension variability by 4x to 16x by improving polysilicon regularity [44]. Similar works are being developed in our research group in the frame of the Synaptic project [45].

Regularity improvements mainly focus on the polysilicon layer because regularity also helps reducing process variations and the transistor channel length variability is dominant in the energy and delay functional yield. However interconnects still remain irregular and this leads to a larger number of different masks to be redesigned, only affordable in large productions.

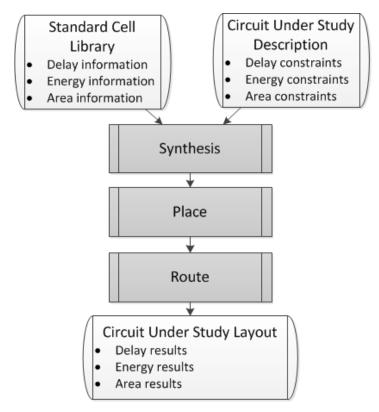

## 2.2.2.3 Standard cell physical design flow

Including more or less regularity, all the standard cell approaches presented in this section use the same physical design flow that is the classical flow approach evolved from the 80's [46, 47]. Several tools are required to obtain the final layout of the circuit designed (a list of tools can be found in chapter 4 including tools for library characterization, logic synthesis and place and route). A summarized physical design flow is depicted in Figure 2.11.

First, designers need to choose the logic functions that will be included in the

Figure 2.11: Standard cell physical design flow.

standard cell library (usually combinational and sequential cells) and also how many drives will be considered for each (the same function can be implemented with different transistor sizings so that it can be used in paths that require more or less strength). One standard cell is then associated to each of the functions with a given drive. From the logic description of these functions as well as from their cell layouts, that need to be designed one by one, the library characterization is performed in order to obtain the library files containing the geometric (including area) and also energy and delay information of each of the cells.

As explained before, note that standard cell layouts have fixed height (defined by the number of routing tracks, of height depending on the technology) and variable width, but always multiple of the technology routing pitch. All these constraints are required for later place and route. Usually, cells are divided into two zones, one containing PMOS transistors and the other containing NMOS, with polysilicon lines drawn vertically, that for compaction reasons try to be aligned respecting the inputs of the transistors to be able to share these vertical polysilicon lines between pull-up and pull-down networks. For doing that, techniques like input ordering (finding Euler Paths) and transistor folding are used (with their implications on transistor sizing).

The next step in the standard flow is logic synthesis. Having as input the circuit description (for instance in VHDL format) and the cell descriptions, the synthesizer can select the standard cells that will be used for the given circuit and generate the circuit netlist, so that the resulting circuit can meet the energy, delay and area constraints fixed by the designer.

Once the circuit netlist is synthesized, place and route is performed by taking into account the cell input and output positions (also called circuit pins) as well as energy and delay estimations for cells but also for interconnects. What is required for this step is that each of the input and output pins are on-grid, respecting the technology pitches for all layout layers so that the routing wires are always also on-grid. In a way, this is a hard constraint but it allows that each of the cells can be placed next to each other without routing overlaps, and it also diminish the enormous amount of routing possibilities for complex circuits. Special filler cells are required to obtain the final layout, because placed standard cells can have free spaces between them that need to be filled. These spaces are also multiple of technology pitch and therefore the filler cells widths are chosen accordingly.

Finally, the layout can be evaluated to verify that energy, delay and area results meet the desired constraints for the circuit.

Figure 2.12: The structured ASIC concept. An array (sea) of tiles is prefabricated across the face of the chip. Structured ASICs also typically contain additional prefabricated elements, which may include configurable general-purpose I/O, microprocessor cores, gigabit transceivers, embedded (block) RAM, and so forth. [31]

## 2.2.3 Structured ASICs

Another class of regular layout fabrics are structured ASICs (SAs) [31]. They are constructed using an array of identical basic tiles that contain the logic (see Figure 2.12). The different types of SAs can be classified depending on their regularity granularity that is defined by the elements included in the tile. For instance, the tile can be composed by gates, multiplexers, lookup tables, buffers, etc. The condition that has to be ensured is that all functions can be synthesized with the elements included in the tile.

#### 2.2.3.1 NAND-based regular structure

One possibility is to consider a tile composed by a single two inputs NAND gate [48, 49] with which all functions can be implemented only configuring the interconnections.

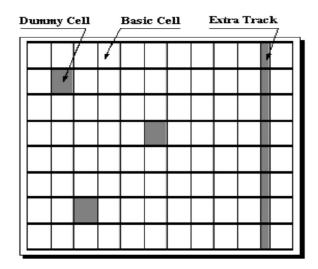

In this proposal, transistor regularity is high, because of the use of a single basic cell (except in the zones where "dummy cells" are included). However, interconnect regularity is very poor. There are different densities of metals because of the difficulties in routability when customizing the wires for the function to be synthesized. Interconnect presents zones of higher density in "extra tracks" and "dummy cells" and zones less congested in the rest of the layout.

Regarding the physical design flow (that can be performed using the classical standard cell flow), some problems may appear in routability due to the use of the single NAND gate as basic cell. Empty "dummy cells" and "extra tracks" are possible solutions to place wires when congestion is detected. Figure 2.13 shows the resulting layout.

Figure 2.13: Layout with "dummy cells" and "extra tracks". [48]

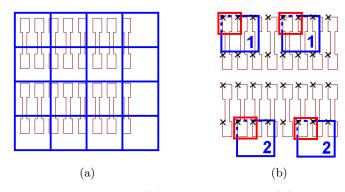

## 2.2.3.2 Via-Configurable Logic Blocks

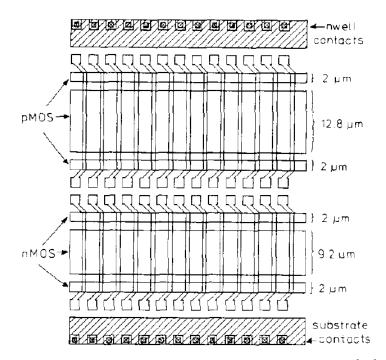

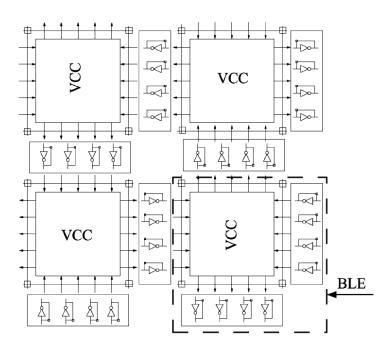

Another possibility is to consider a tile or basic logic element (BLE) composed by via-configurable logic blocks [50]. In particular, a BLE consists of two types of blocks: a via-configurable functional cell (VCC), containing the combinational logic needed for functions, and two via-configurable inverter arrays, containing inverters (see Figure 2.14).

Experiments performed for the 180nm technology node on 20 large benchmarks ranging from 1.5 k to 17 k nodes showed that this via-configurable design technique presents overheads in all three metrics of area, performance and power compared to standard cell design. The area increases in average by 116%. It shows 33% performance degradation and consumes 17% more power than the standard cell design.

This via-configurable logic blocks design fabric has high transistor regularity, but limited by the use of two different blocks with different compositions and layouts. Interconnect regularity is complete because all the routing channels are implemented and configured using vias.

Regarding the physical design flow, it is similar to the FPGA approach, but the configuration can be done only once. The functions are mapped to the combinational cell and the inverter cells perform the buffer connections with the surrounding tiles. In fact, the cells have prefabricated transistors, contacts and M1 wires and only the M1-M2 mask has to be configured depending on the function to be synthesized, thus reducing mask costs. In this proposal, the routing method is an important issue, as it is for all regular designs, because of the limited set of vias that can be configured [51].

## 2.3 Existing layout analysis tools

In this section we present the existing layout analysis tools that can be used to evaluate circuit manufacturability. We will first explain the standard DFM flow to address manufacturability issues. Then, we will give an overview of the tools

Figure 2.14: Via-configurable logic block. [50]

from Mentor Graphics, that are the most widely DFM tools used. Then, we will explain other methodologies to estimate systematic manufacturing variability, for which no commercial tools are available, and that we found in the literature. These methodologies include the evaluation of lithography proximity and coma effects variability, and also the modeling of mechanical stress variability. Finally we present how the two-dimensional Fourier Transform has been used to evaluate layout regularity.

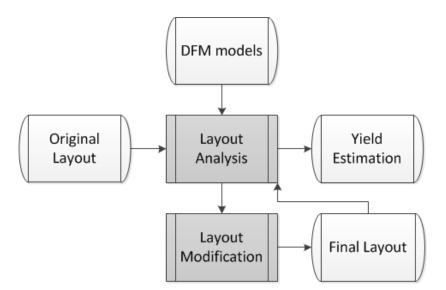

## 2.3.1 Standard DFM flow

Figure 2.15 summarizes the standard DFM flow to improve designs manufacturing yield. Layout analysis tools use DFM models to estimate manufacturing yield and to identify the layout modifications required to improve manufacturability. DFM refers to the action of making modifications to the target design in order to minimize critical manufacturing operations that can cause yield losses.

Figure 2.15: DFM standard flow.

## 2.3.2 Mentor Graphics DFM tools

References to Mentor Graphics tools can be found in [52]. Following the standard DFM flow, they provide a set of tools to analyze the layout, to modify it in order to improve design yield, and even to predict the printability of particular patterns by simulating lithography tools and resolution enhancement techniques.

Regarding layout analysis, Calibre YieldAnalyzer performs two kind of layout evaluations. First, the CAA (Critical Area Analysis) and then the CFA (Critical Feature Analysis). CAA is used to detect opens and shorts that can cause random yield losses associated to random particles. For this step, the distributions of random dust particles in the given process are required. On the other hand, CFA uses the design rules check (DRC) environment to check recommended rules and detect where the layout patterns can cause systematic yield losses. The set of recommended rules depends again on the particular process and does not always comprehend the whole set of possible layout patterns in a layout.

Also for layout analysis, Calibre CMPAnalyzer evaluates the impact of chemical mechanical polishing (CMP) to predict planarity variability. In that way, designers can detect thickness and resistance variability caused by decreasing linewidths. CMP models are required for this analysis and are checked again using the DRC environment.

For layout modification, Calibre YieldEnhancer uses the results of Calibre YieldAnalyzer to modify the layout in order to improve the estimated yield results. It allows automatic via doubling, via extensions and enclosures, as well as growing polygons to a minimum size.

YieldEnhancer also includes the SmartFill algorithm which goal is to modify metal filling shapes added for CMP issues. SmartFill modifies the layout to reduce resistance variability while minimizing the number of fill shapes added.

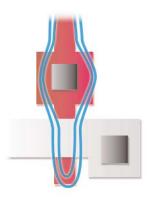

Finally, for printability simulation, Calibre LFD (Litho-Friendly Design) in combination with Calibre Workbench is used to predict the printability of designed layouts and to find lithographic hotspots. These tools are based on models for the lithography system (lens, masks and photoresist), also including the impact of resolution enhancement techniques (like OPC) in order to simulate the resulting layout shapes. Varying particular parameters of the lithography system (like dose and focus) the tool provides a graphical representation of the final shapes in the layout giving the process variations (PV) bands. These PV bands represent the range in which the final shapes are predicted to be (see Figure 2.16). In fact, "what you see is not anymore what you get" for deep submicron technologies. However, the simulation of complex circuit layouts requires and important computational effort.

## 2.3.3 Systematic manufacturing variability models

Transistor channel length variations and threshold voltage variations are major sources of circuit performance unpredictability [53, 54]. We explain next the models found in the literature that can be applied to estimate their manufacturing variability.

Figure 2.16: PV bands of a poly gate. Active layer in grey, poly layer in red, PV band of the poly layer in blue.

#### 2.3.3.1 Channel length variations: proximity and coma effect

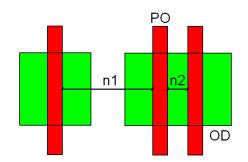

Models for systematic variations of channel length (L) variability can be found in [55] taking into account proximity and coma effects. Basically, proximity and coma effects models associate to each channel a percentage of L variation depending on the layout neighborhood on both sides of the feature to be printed. The models are based on the inspection of the layout to the left and to the right of the feature in order to define the kind of neighborhood that the channel has. They measure the distances to the first polysilicon line in each direction. Figure 2.17 depicts an example of distances n1 to the left and n2 to the right. The difference between both is that for proximity effect left side and right side distances are equivalent in their impact on variations but for coma effect they are not. The models include tables with the nominal amount of process variations for each case and the final percentage variation for L can be obtained by setting the maximum percentage range of variations. The final result is the expected L for each of the transistors on the layout. The entire circuit L distribution can then be characterized by its mean  $\mu$  and its standard deviation  $\sigma$ .

## 2.3.3.2 Threshold voltage variations: mechanical stress

Models for silicon mechanical stress due to shallow trench isolation (STI) are included in the BSIM4 transistor models [56]. Transistor performance is affected

Figure 2.17: Proximity and coma effect model measurements

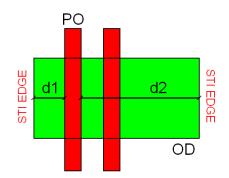

Figure 2.18: STI stress model measurements

depending on the shape of the oxide diffusion area and on the position of the device inside this area. In particular, threshold voltage (Vth) varies depending on the distances from the channel to the edge of the diffusion (where the STI begins). Figure 2.18 shows an example for the measurement of these d1 and d2 distances. The relative impact also depends on the dimensions of the transistor. Transistors with wider channel will be less affected.

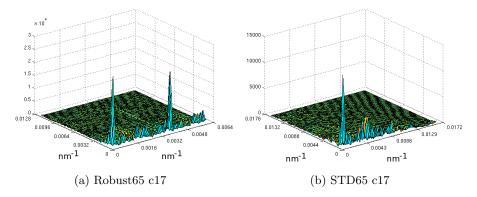

## 2.3.4 Evaluating layout regularity

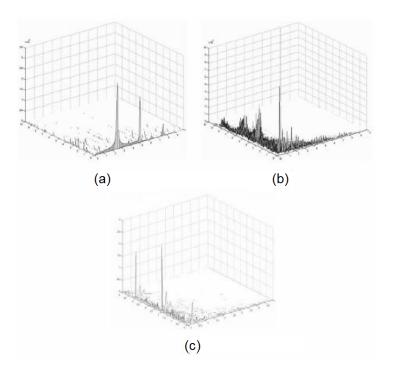

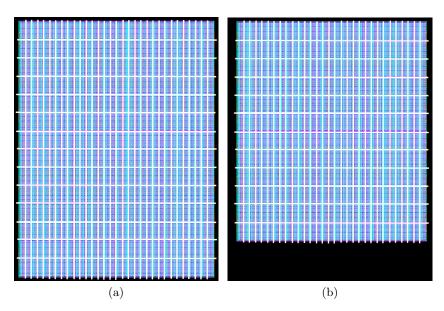

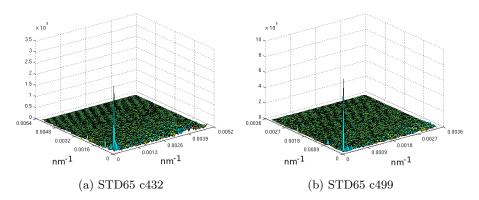

To the best of our knowledge, the only method that has already been used for this purpose is the visual comparison of a two-dimensional Fourier transform. It has been used in [8] to compare the degree of regularity of: (a) a polysilicon layer of an SRAM array, (b) logic implemented using standard cells and (c) logic implemented using a regular fabric. Since a regular layout utilizing a small number

Figure 2.19: 2-D FFT spatial frequency analysis for (a) SRAM (b) standard cells (c) regular fabric [8].

of layout patterns is expected to have a finite number of frequency components the comparison is based on the number of frequency components obtained by the Fourier transform. By graphical inspection (see Figure 2.19) it can be seen that the SRAM and regular fabric layouts are more regular than the standard cells. However, the graphical inspection of the Fourier graphs does not give enough information to find out which of the two regular layouts is more regular than the other because the two frequency responses are similar.

## 2.4 Thesis works motivation

In this chapter we have justified the use of layout regularity to address nowadays scaling challenges from the design and also manufacturing sides. Then we have presented the existing regular layout fabrics starting from the GAs developed in the early 1980s. Finally, we have presented the way the semiconductor industry copes with manufacturing issues using different EDA tools for DFM. These are the works that have inspired our research.

The study of the existing regular fabrics has shown how comprehensive regularity is not achieved for any of the proposals. Some are irregular at transistor level, other at interconnect level. For technologies with increasing design and manufacturing challenges, a new regular fabric with comprehensive regularity is required to maximize the regularity benefits in terms of DFM.

The study of the different physical design approaches for the existing regular fabrics has also been useful to understand the problems that have to be faced when automating this physical design. In particular, related to partitioning, placing and routing the circuits. We have seen how the physical design depends on the fabric specificities, specially on the degree of layout regularity considered. Those steps have to be addressed when developing a new regular fabric.

From the study of the different layout analysis tools, we realized that none of them measures layout regularity directly. Only the two-dimensional Fourier transform is a graphical representation giving an intuitive and qualitative measure of regularity. However it does not quantify regularity. Layout regularity can be used as a figure of merit of the design as it has been shown to improve manufacturability. Therefore there is the need of a new layout analysis tool to measure regularity.

## Chapter 3

# Unique contributions of the thesis

When reaching the deep submicron era, increasing manufacturing and design challenges need to be addressed. For this purpose, the thesis works are focused on the emerging DFM regular layout design techniques. The main contributions of the thesis are explained in the following subsections. First, we have proposed a new regular fabric called Via-Configurable Transistor Array (VCTA). Second, we have developed a synthesis tool to automate the VCTA regular fabric physical design. Third, we have proposed an analysis tool to measure layout regularity. The list of publications in chronological order related to these works is also given at the end of the chapter.

## 3.1 VCTA regular fabric

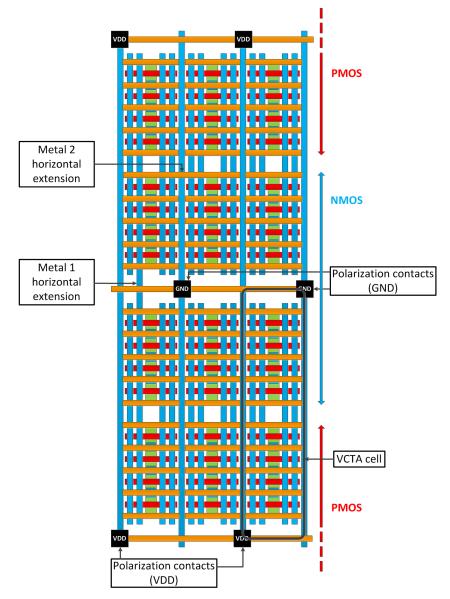

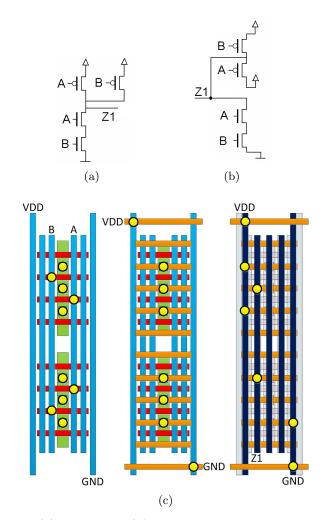

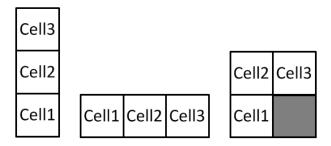

We have named our new regular fabric Via-Configurable Transistor Array (VCTA) and it is based on maximizing layout regularity focusing future technology nodes with extreme manufacturability and design issues. The objective is to maximize the regularity benefits in terms of DFM. With this purpose, VCTA uses a single basic cell containing transistors and interconnects that are configured using vias to obtain the functionality desired. Regularity constraints for the front-end and the back-end design as well as the via-configuration strategy of the fabric dictate the VCTA basic cell design. Chapter 5 is devoted to this part of the thesis.

The first proposal with a full-adder layout was presented in the "IEEE International Workshop on Design For Manufacturability and Yield" held in conjunction of the ITC 2007 in Santa Clara, US. Then, a poster including 32-bit adders was presented in Nice, France, in the "Workshop on Process Variability: New Techniques for the Design and Test of Nanoscale Electronics" held in conjunction of the DATE 2009. In 2010, a paper including the benefits of using VCTA in terms of manufacturing variability reduction was presented in Madrid, Spain, at the "IEEE/IFIP International Conference on VLSI and System-on-Chip". In 2011, a second paper was defended in the "International Conference on Design and Test of Integrated Systems in Nanoscale Technology" in Athens, Greece, this time applying VCTA to a delay locked-loop design from an ultra wideband transceiver and demonstrating the acceleration of the design time using VCTA while maintaining circuit functionality.

## 3.2 VCTA automation tool

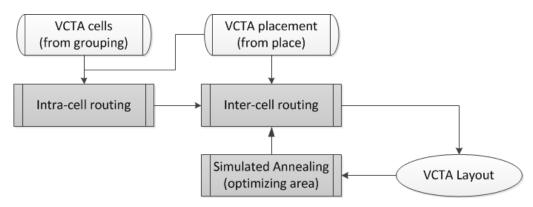

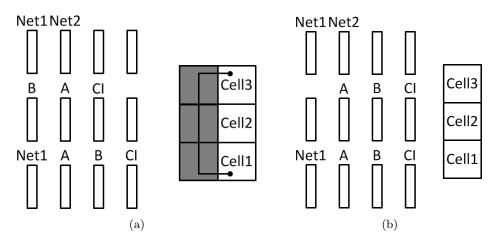

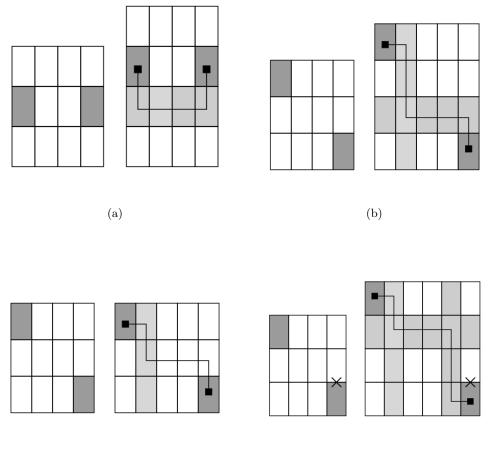

Designing with VCTA implies a specific physical design flow. Having the standard cell tools available, the first option was to adapt these tools to the physical design of the new VCTA fabric. However adapted EDA synthesis tools and algorithms were required. That is why we developed our own VCTA automation steps including transistor grouping, intra and inter-cell routing or congestion treatment. Starting from a transistor netlist, the grouping step objective is to map the transistors inside of the VCTA cells (it is equivalent to a partitioning step). Then these cells are placed and routed respecting VCTA constraints and focusing on minimizing the area of the final layouts. Chapter 6 is devoted to this part of the thesis.

For this part of the thesis, a paper was defended in 2011 in Taipei, Taiwan, in the "IEEE International SOC Conference".

## 3.3 FOCSI layout regularity metric tool

To satisfy the lack of an EDA tool to evaluate the benefits of layout regularity, we have developed a layout regularity metric tool named Fixed Origin Corner Square Inspection (FOCSI). No other layout regularity metrics are available. FOCSI is unique because it is able to order layouts in terms of regularity. FOCSI extracts the number of different layout generators for the selected layout layer so that, the lower this number is, the higher is the regularity of the layer. Then, the results for all the layers can be merged to calculate a complete layout regularity measure. In this way, layout designers can evaluate their layouts in terms of regularity. Finally, we have also linked FOCSI results to layout manufacturing variability to demonstrate the benefits of regular layout by proposing a variability model that makes use of the Monte Carlo analysis. FOCSI layout analysis tool can therefore be used to optimize layouts in terms of manufacturability. Chapter 7 is devoted to this part of the thesis.

For this last contribution, we have made a one year stage in the CSEM research center in Switzerland. A paper has been published for this topic in International Conference on Design, Automation & Test in Europe 2012.

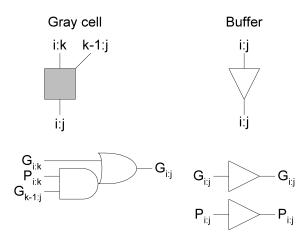

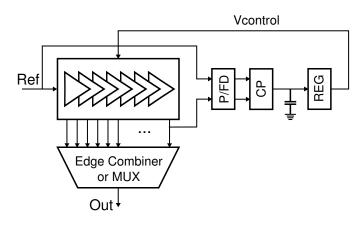

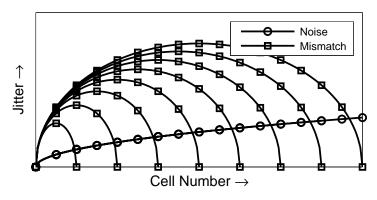

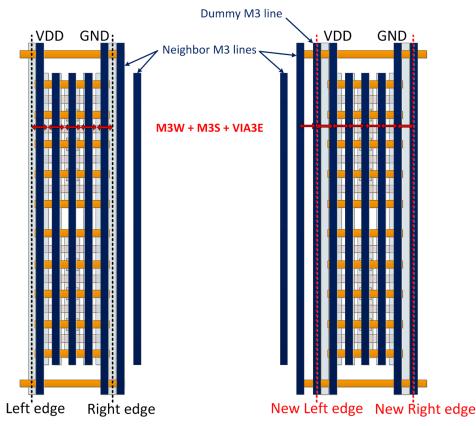

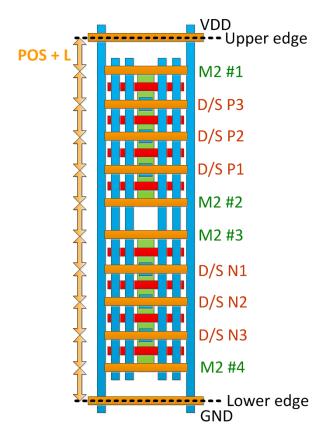

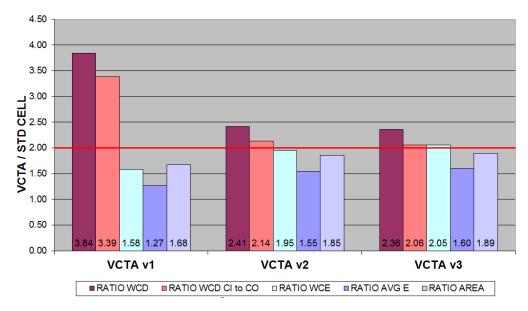

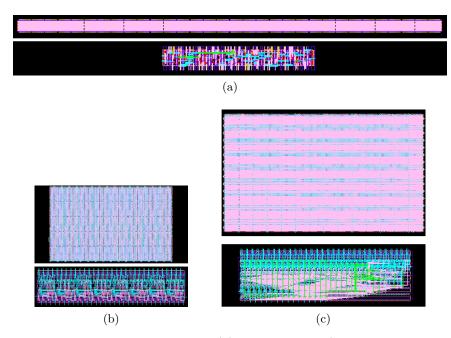

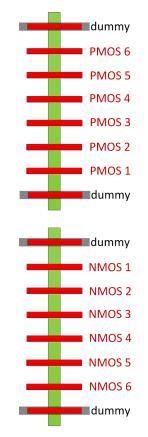

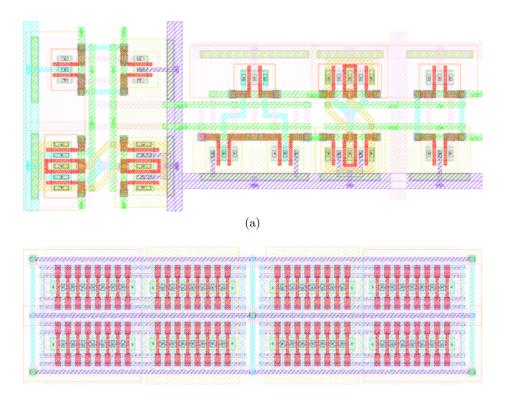

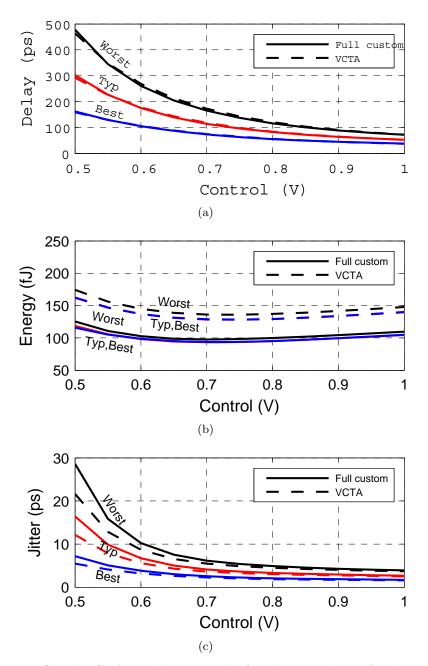

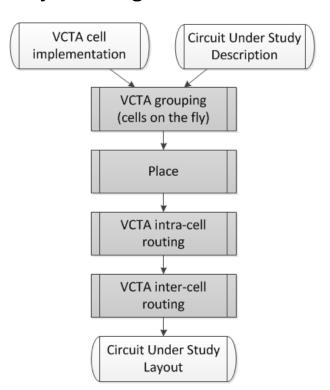

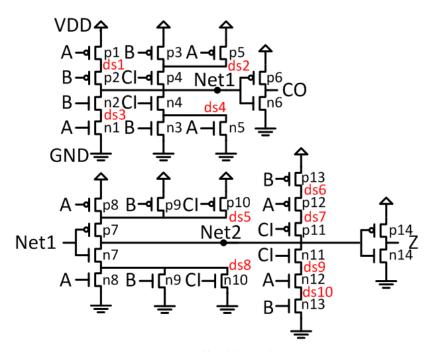

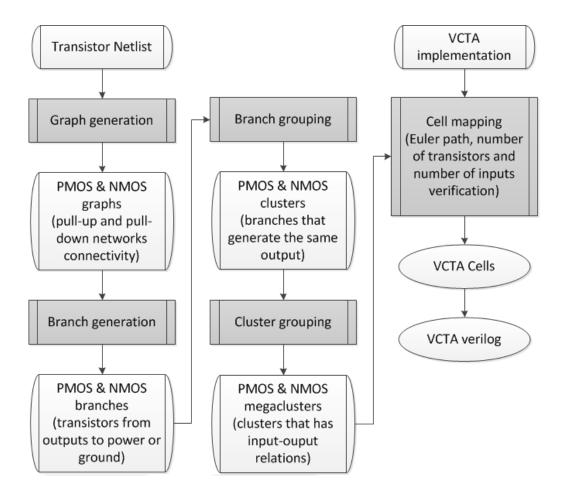

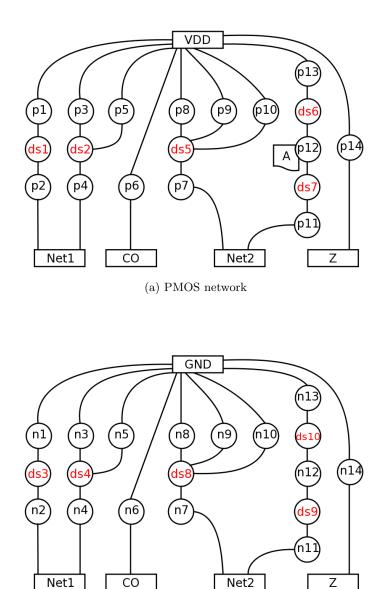

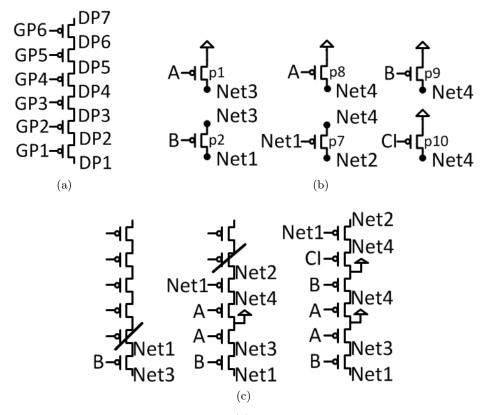

## 3.4 Thesis dissemination