ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons:

ADVERTENCIA. El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons:

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

BY NC ND

# **UAB** Universitat Autònoma de Barcelona

Escola d'Enginyeria

Departament d'Arquitectura de Computadors i Sistemes Operatius

# Execution strategies for memory-bound applications on NUMA Systems

Thesis submitted by **Josefina Lenis** for the degree of philosophae Doctor by the Universitat Autònoma de Barcelona, under the supervision of Dr. Miquel Àngel Senar, developed at the Computer Architectures and Operating Systems department, PhD program in Computer Science (research line: High Performance Computing)

Barcelona, October 2018

# Execution strategies for memory-bound applications on NUMA Systems

Thesis submitted by **Josefina Lenis** for the degree of philosophae Doctor by the Universitat Autònoma de Barcelona, under the supervision of Dr. Miquel Àngel Senar, developed at the Computer Architectures and Operating Systems department, PhD program in Computer Science (research line: High Performance Computing).

Supervisors

Dr. Miquel Àngel Senar

Phd Student

Josefina Lenis

## Ackowledgements

First of all I want thank my advisor Miquel. Thanks to his support and guidance I discover a strength that I did not know that I have. His actions and advice marked me and became an example of fine academic work.

During my stay in the USA I fell in love with a small city called Eugene in the state of Oregon. Where I still have very goods friends. The main responsible converting that time in an amazing experience was the Dr. Sameer Shende. To whom I will always be deeply thankful for his kindness and warm-hearted spirit. He invited me to work with his team, an incredible smart and capable group of people, where I faced several challenges and I've learned a lot. Thank you for the technical and moral support Sameer!

I want to thank each member of the Computer and Operating Systems Department. In particular the people that stood by me in numerous occasions: Eduardo Cesar, Anna Sikora -thank you for always encourage me to continue, your words and kind gestures help me more than I can express-, Remo Suppi, Lola Rexachs, Emilio Luque and Gemma Roque. My fellow colleagues during some of this time Albert Gutierrez, Aprigio Bezerra, Francisco Cruz, Javi Navarro, Francisco Borges, Javier Panadero, Ferran Badosa, Hugo Meyer, Cecilia Jaramillo, Joe Carrión, Laura Espinola and Jorge Villamayor.

A special mention for a close friend of mine in this PhD adventure: Àlex Chacón: I have no words to describe my gratitude to you. Your help was priceless. Thanks for your advices, your feedback, your extensive knowledge, for being there and for everything you have done for me. I truly admire you. I do not want to forget of my awesome friends Marcela Castro, Claudia Rosas y Pili Gomez. Thanks for listening and thanks for remind me what truly matter.

To my beloved husband Diego, my partner, my companion, my pillar and my rock. Thank you for supporting the long nights, for listening rehearsal my presentations, for help me handle the stress, for taking care of me when I needed the most, I love you.

To my family, my dad and my mom, my examples of sacrifice, hard-work and enormous

heart. To my unconditional siblings, nieces and nephews, the Flanders family: Juan P., María, Emma, David, Caro, Charly, Juan F., Agus, Gonzalo, Facu, Guille y Román. I love you and I miss you all.

Last but not least, I want to thanks all my friends that in one way or an other helped this work to come through: Nuni, Fede, Andrés, Bet, Petra, Pedro, Prass and Gero.

## Abstract

Over the last several years, many sequence alignment tools have appeared and become popular thanks to the fast evolution of next generation sequencing (NGS) technologies. Obviously, researchers that use such tools are interested in getting maximum performance when they execute them in modern infrastructures. Today's NUMA (Non-Uniform Memory Access) architectures present major challenges in getting such applications to achieve good scalability as more processors/cores are used. The memory system in NUMA systems shows a high complexity and may be the main cause for the loss of an application's performance. The existence of several memory banks in NUMA systems implies a logical increase in latency associated with the accesses of a given processor to a remote bank. This phenomenon is usually attenuated by the application of strategies that tend to increase the locality of memory accesses. However, NUMA systems may also suffer from contention problems that can occur when concurrent accesses are concentrated on a reduced number of banks. Sequence alignment tools use large data structures to contain reference genomes to which all reads are aligned. Therefore, these tools are very sensitive to performance problems related to the memory system. The main goal of this study is to explore the trade-offs between data locality and data dispersion in NUMA systems. We introduced a series of methodical steps to characterize NUMA architectures and to help understand the potential of the resources. With this information we designed and experimented with several popular sequence alignment tools on two widely available NUMA systems to assess the performance of different memory allocation policies and data partitioning and replication strategies. We find that there is not one method that is best in all cases. However, we conclude that memory interleaving is the memory allocation policy that provides the best performance when for applications that used a large centralized data structured on a large number of processors and memory banks In the case of data partitioning and replication, the best results are usually obtained when the number of partitions used is greater, and in some cases, combined with an interleave policy.

#### Resumen

Durant els últims anys, moltes eines d'alineament de seqüències han aparegut i s'han popularitzat gràcies a la ràpida evolució de les tecnologies de Next Generation Sequencing (NGS). Evidentment, els investigadors que utilitzen aquestes eines estan interessats en obtenir el màxim rendiment quan les executen en infraestructures modernes. Actualment, les arquitectures NUMA (accés a la memòria no uniforme) presenten grans reptes en aconseguir que aquestes aplicacions tinguin una bona escalabilitat a mesura que s'utilitzen més processadors/nuclis. El sistema de memòria dels sistemes NUMA mostra una gran complexitat i pot ser la causa principal de la pèrdua del rendiment d'una aplicació. L'existència de diversos bancs de memòria en sistemes NUMA implica un augment lògic de la latència associada als accessos d'un processador donat a un banc remot. Aquest fenomen sol estar atenuat per l'aplicació d'estratègies que tendeixen a augmentar la localitat d'accés a la memòria. Tanmateix, els sistemes NUMA també poden patir problemes de contenció que es poden produir quan els accessos concurrents es concentren en un reduït nombre de bancs. Les eines d'alineació de seqüències utilitzen grans estructures de dades per contenir genomes de referència als quals totes les lectures estan alineades. Per tant, aquestes eines són molt sensibles als problemes de rendiment relacionats amb el sistema de memòria. L'objectiu principal d'aquest estudi és explorar les compensacions entre la localitat de dades i la dispersió de dades en els sistemes NUMA. Hem introduït una sèrie de passos metòdics per caracteritzar arquitectures NUMA i per ajudar a comprendre el potencial dels recursos. Amb aquesta informació, hem dissenyat i experimentat diverses eines d'alineació de seqüència populars en dos sistemes NUMA àmpliament disponibles per avaluar el rendiment de les diferents polítiques d'assignació de memòria i les estratègies de partició i replicació de dades. Trobem que no hi ha un mètode que sigui millor en tots els casos. Tanmateix, es conclou que la intercalació de memòria és la política d'assignació de memòria que proporciona el millor rendiment quan s'utilitza una gran quantitat de processadors i bancs de memòria. En el cas de

la partició i la replicació de dades, els millors resultats solen obtenir-se quan la quantitat de particions que s'utilitza és més gran, de vegades combinada amb una política interleave.

#### Resumen

En los últimos años, muchas herramientas de alineadores de secuencias han aparecido y se han hecho populares por la rápida evolución de las tecnologías de secuenciación de próxima generación (NGS). Obviamente, los investigadores que usan tales herramientas están interesados en obtener el máximo rendimiento cuando los ejecutan en infraestructuras modernas. Las arquitecturas NUMA (acceso no uniforme a memoria) de hoy en día presentan grandes desafíos para lograr que dichas aplicaciones logren una buena escalabilidad a medida que se utilizan más procesadores/núcleos. El sistema de memoria en los sistemas NUMA muestra una alta complejidad y puede ser la causa principal de la pérdida del rendimiento de una aplicación. La existencia de varios bancos de memoria en sistemas NUMA implica un aumento lógico en la latencia asociada con los accesos de un procesador dado a un banco remoto. Este fenómeno generalmente se atenúa mediante la aplicación de estrategias que tienden a aumentar la localidad de los accesos a la memoria. Sin embargo, los sistemas NUMA también pueden sufrir problemas de contención que pueden ocurrir cuando los accesos concurrentes se concentran en un número reducido de bancos. Las herramientas de alineadores de secuencia usan estructuras de datos grandes para contener genomas de referencia a los que se alinean todas las lecturas. Por lo tanto, estas herramientas son muy sensibles a los problemas de rendimiento relacionados con el sistema de memoria. El objetivo principal de este estudio es explorar las ventajas y desventajas entre la ubicación de datos y la dispersión de datos en los sistemas NUMA. Hemos introducido una serie de pasos metódicos para caracterizar las arquitecturas NUMA y ayudar a comprender el potencial de los recursos. Con esta información, diseñamos y experimentamos con varias herramientas de alineación de secuencias populares, en dos sistemas NUMA ampliamente disponibles para evaluar el rendimiento de diferentes políticas de asignación de memoria y estrategias de replicación y partición de datos. Encontramos que no hay un método que sea el mejor en todos los casos. Sin embargo, concluimos que aplicar interleave a la memoria es la política de alocación

de memoria que proporciona el mejor rendimiento cuando se utiliza una gran cantidad de procesadores y bancos de memoria. En el caso de la partición y replicación de datos, los mejores resultados se obtienen generalmente cuando el número de particiones utilizadas es mayor, a veces combinado con una política de interleave.

## Contents

| 1 | Introduction            |                                         |    |  |  |  |  |  |  |

|---|-------------------------|-----------------------------------------|----|--|--|--|--|--|--|

|   | 1.1                     | Introduction                            | 2  |  |  |  |  |  |  |

|   | 1.2                     | Contribution                            | 3  |  |  |  |  |  |  |

|   | 1.3                     | Related work                            | 4  |  |  |  |  |  |  |

|   | 1.4                     | Thesis Structure                        | 6  |  |  |  |  |  |  |

| 2 | HPC Systems             |                                         |    |  |  |  |  |  |  |

|   | 2.1                     | Introduction                            | 9  |  |  |  |  |  |  |

|   | 2.2                     | Brief history of parallel architectures | 9  |  |  |  |  |  |  |

|   | 2.3                     | Parallel Architectures                  | 11 |  |  |  |  |  |  |

|   |                         | 2.3.1 Shared-memory system              | 11 |  |  |  |  |  |  |

|   |                         | 2.3.2 Distributed-memory systems        | 13 |  |  |  |  |  |  |

|   |                         | 2.3.3 Hybrid systems                    | 13 |  |  |  |  |  |  |

|   | 2.4                     | Study Case: NUMA Systems                | 14 |  |  |  |  |  |  |

|   |                         | 2.4.1 Our Infrastructure                | 15 |  |  |  |  |  |  |

|   | 2.5                     | Measuring performance                   | 16 |  |  |  |  |  |  |

|   |                         | 2.5.1 Definitions                       | 16 |  |  |  |  |  |  |

|   |                         | 2.5.2 Performance tools                 | 18 |  |  |  |  |  |  |

| 3 | Analysis Methodology 22 |                                         |    |  |  |  |  |  |  |

|   | 3.1                     | Introduction                            | 23 |  |  |  |  |  |  |

|   | 3.2                     | Calculating Theoretical Bandwidth       | 24 |  |  |  |  |  |  |

|   | 3.3                     | Measuring Latency                       | 25 |  |  |  |  |  |  |

|   | 3.4                     | Measuring Bandwidth                     | 26 |  |  |  |  |  |  |

|   | 3.5                     | Measuring Contention                    | 31 |  |  |  |  |  |  |

|   | 3.6                     | Creating a guideline                    | 33 |  |  |  |  |  |  |

| 4 | Sequ                    | uencing aligners                        | 36 |  |  |  |  |  |  |

|              | 4.1 | Introdu  | uction                                        | 37 |  |  |

|--------------|-----|----------|-----------------------------------------------|----|--|--|

|              | 4.2 | Motiva   | ation                                         | 37 |  |  |

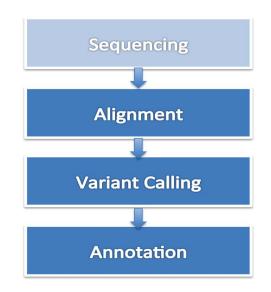

|              | 4.3 | NGS V    | Workflows                                     | 38 |  |  |

|              |     | 4.3.1    | Sequencing                                    | 38 |  |  |

|              |     | 4.3.2    | Alignment                                     | 40 |  |  |

|              |     | 4.3.3    | Variant calling                               | 41 |  |  |

|              |     | 4.3.4    | Annotation                                    | 42 |  |  |

|              | 4.4 | Sequer   | nce Aligners                                  | 43 |  |  |

|              |     | 4.4.1    | Burrows Wheeler Aligner                       | 44 |  |  |

|              |     | 4.4.2    | Bowtie2                                       | 45 |  |  |

|              |     | 4.4.3    | Genome Multitool 3                            | 45 |  |  |

|              |     | 4.4.4    | Scalable Nucleotide Alignment Program         | 45 |  |  |

| 5            | Exp | eriment  | tation                                        | 48 |  |  |

|              | 5.1 | Perform  | mance of sequence aligners on NUMA systems    | 49 |  |  |

|              | 5.2 | Alloca   | tion Strategies and Data Partitioning         | 51 |  |  |

|              |     | 5.2.1    | Analysis of memory allocation                 | 51 |  |  |

|              |     | 5.2.2    | Data partitioning and replications strategies | 52 |  |  |

|              | 5.3 | Experi   | mental Results                                | 54 |  |  |

|              |     | 5.3.1    | Analysis of memory allocation policies        | 55 |  |  |

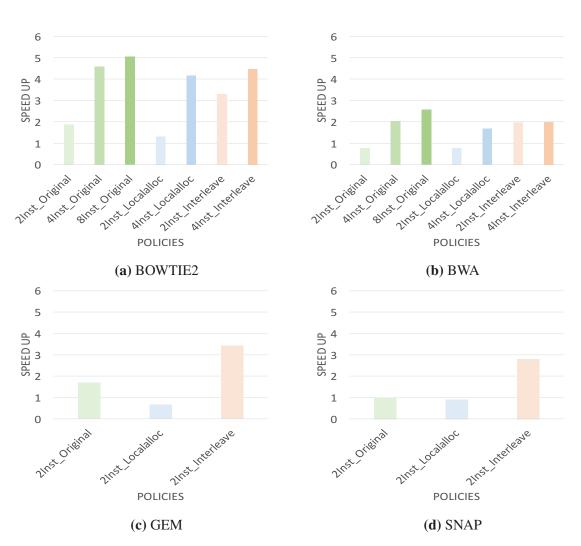

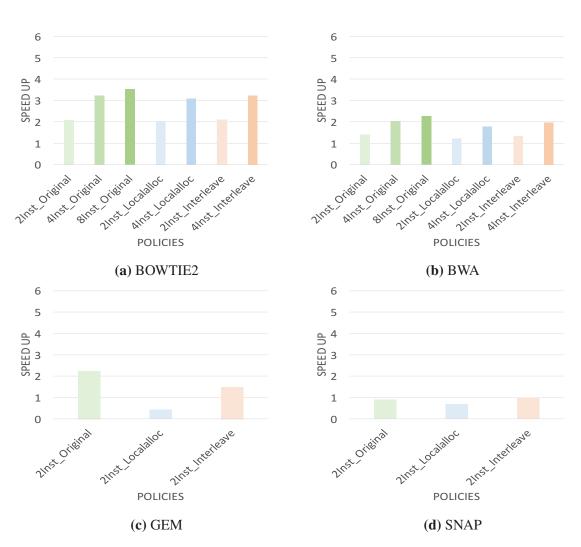

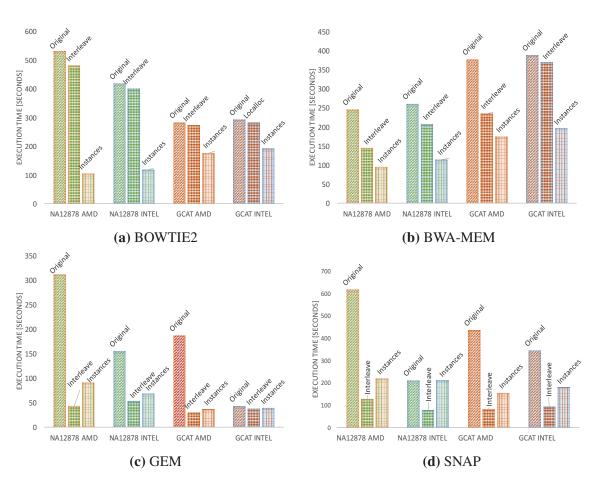

|              |     | 5.3.2    | Data partitioning and replication strategies  | 59 |  |  |

|              |     | 5.3.3    | Summary results                               | 63 |  |  |

|              | 5.4 | Annex    | ed results                                    | 66 |  |  |

| 6            | Con | clusions | s and Future lines                            | 71 |  |  |

|              | 6.1 | Conclu   | usions                                        | 72 |  |  |

|              | 6.2 | Future   | Lines                                         | 73 |  |  |

| Bibliography |     |          |                                               |    |  |  |

# **List of Figures**

| More's Law vs Number of cores Source [1]                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A UMA architecture provides each CPU core (C1-C4) the same memory                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| access latency and bandwidth. Source [2]                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A NUMA architecture connects different NUMA nodes (Nodes 1-4) - typically        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| multicore CPUs (C1-C4) - via interconnect links (Link), to enable a single       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| logically shared global memory Source [2]                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| In a distributed-memory model, the memory is physically and logically dis-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tributed among the individual processing units (P1-P3), e.g., CPUs. Accessing    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| data from remote memory locations requires to initiate a data transfer protocol, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| such as point-to-point communication provided by the MPI. Figure source: [2]     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

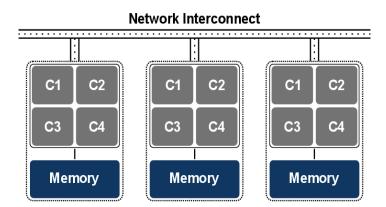

| In hierarchical systems the distributed- and shared-memory model are com-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bined. In the depicted case three UMA-based shared-memory nodes are              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| connected via a network connection, however, NUMA systems can be used in         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| a similar manner. Figure source: [2]                                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

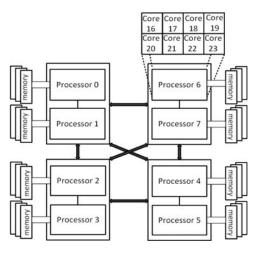

| Schematic diagram of the AMD Opteron 6376 architecture (Abu-Dhabi)               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

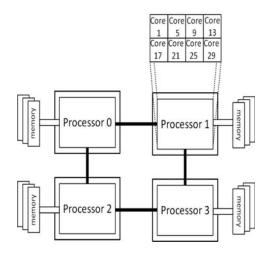

| Schematic diagram of the Intel Xeon E5 4620 architecture (Sandy Bridge) .        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

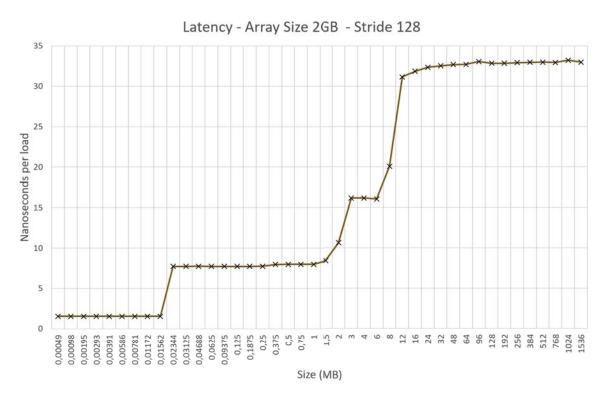

| Latency profile of AMD Opteron 6376 using lmbench                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

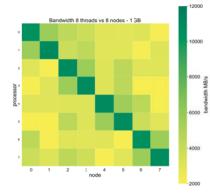

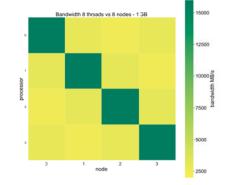

| All possible bandwidth values for one-processor execution on AMD system .        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All possible bandwidth values for one-processor execution on Intel system        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

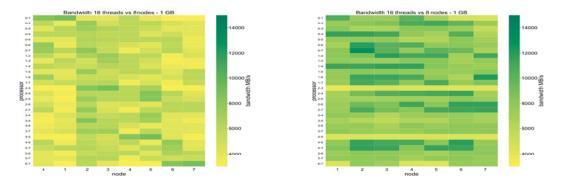

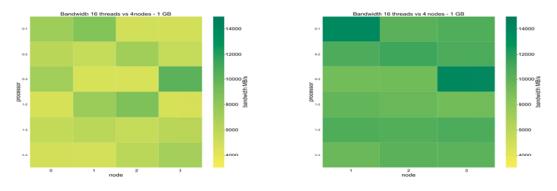

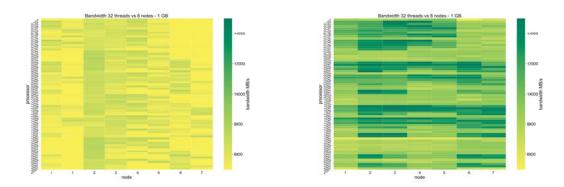

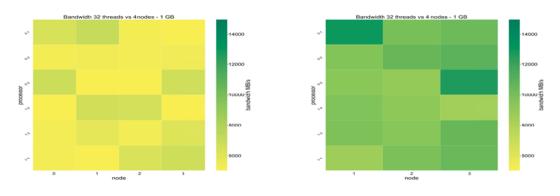

| BW measures for all systems using 16 threads                                     | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BW measures for all systems using 32 threads                                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

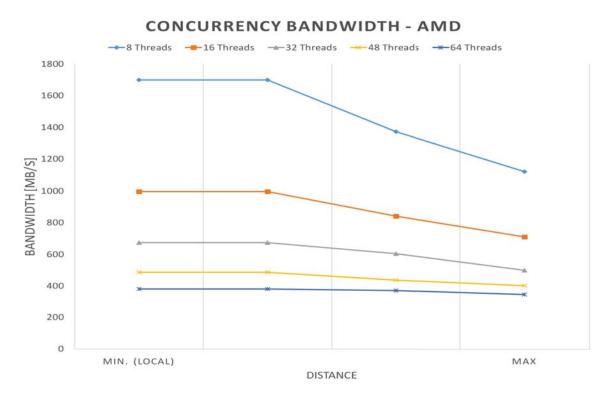

| Concurrency stress test on AMD system                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

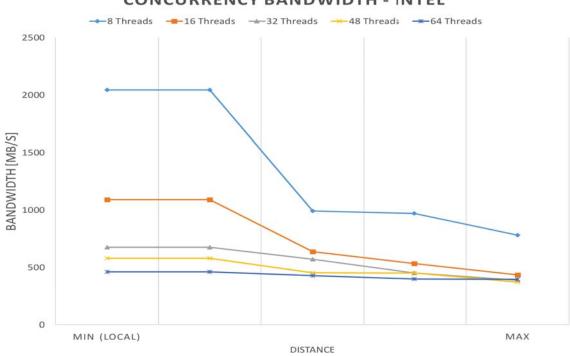

| Concurrency stress test on Intel system                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

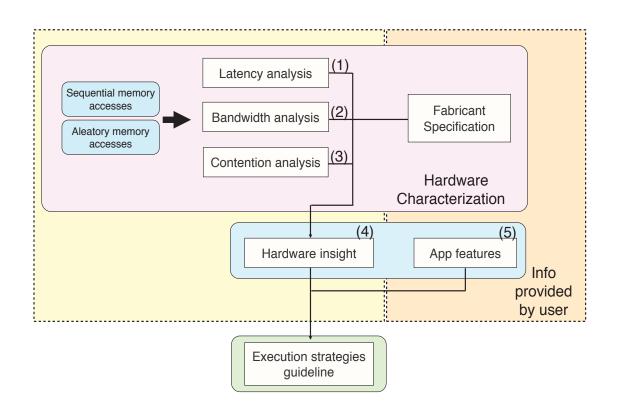

| Methodology to obtain a guideline of NUMA execution strategies                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Standard variant calling workflow                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

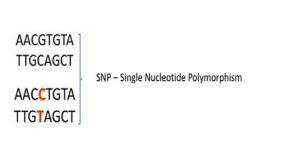

| Single-nucleotide polymorphism                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                  | A UMA architecture provides each CPU core (C1-C4) the same memory access latency and bandwidth. Source [2] A NUMA architecture connects different NUMA nodes (Nodes 1-4) - typically multicore CPUs (C1-C4) - via interconnect links (Link), to enable a single logically shared global memory. Source [2] In a distributed-memory model, the memory is physically and logically distributed among the individual processing units (P1-P3), e.g., CPUs. Accessing data from remote memory locations requires to initiate a data transfer protocol, such as point-to-point communication provided by the MPI. Figure source: [2] In hierarchical systems the distributed- and shared-memory model are combined. In the depicted case three UMA-based shared-memory nodes are connected via a network connection, however, NUMA systems can be used in a similar manner. Figure source: [2] |

| 4.3  | Types of SNP                                                             | 42 |

|------|--------------------------------------------------------------------------|----|

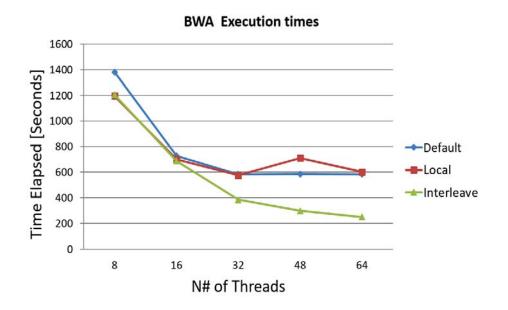

| 5.1  | Scalability study for BWA-ALN on AMD architecture                        | 50 |

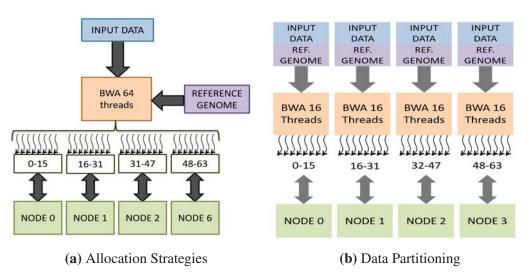

| 5.2  | Experimentation approaches                                               | 51 |

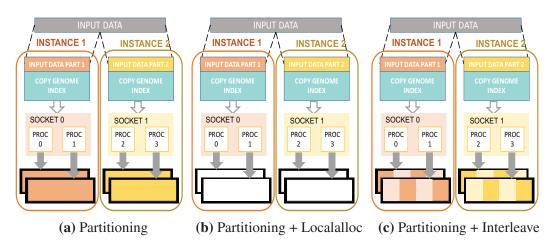

| 5.3  | Hybrid experimentation                                                   | 54 |

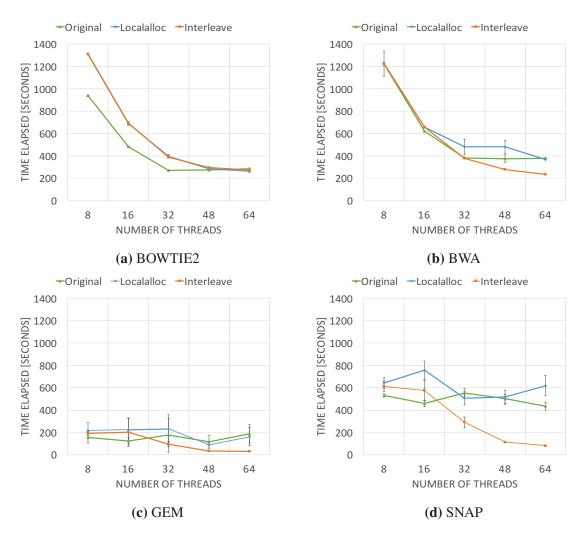

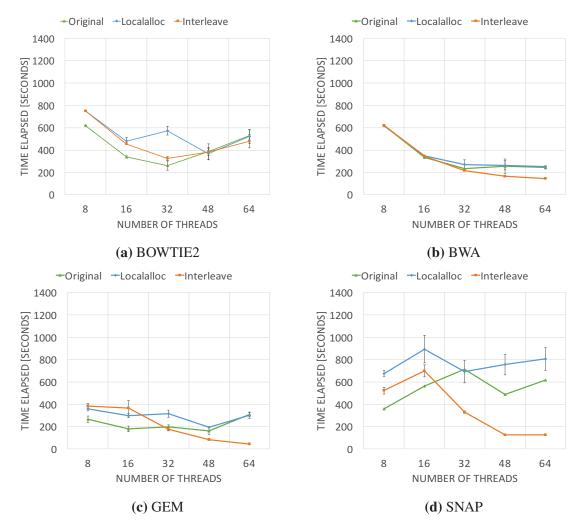

| 5.4  | Different memory allocation policies. The lower the better. Arch: AMD.   |    |

|      | Dataset: GCAT Synthetic Input                                            | 56 |

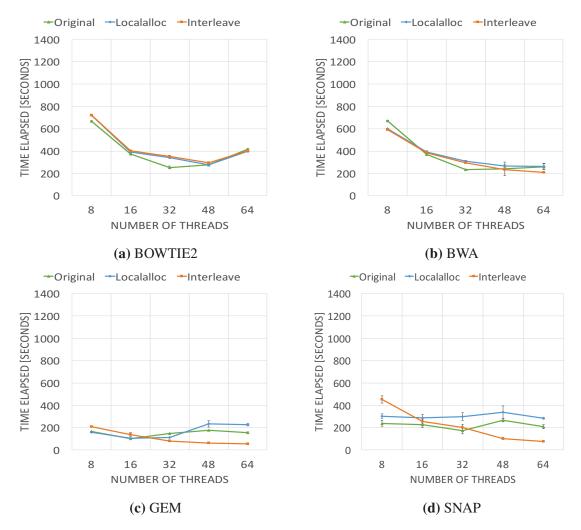

| 5.5  | Different memory allocation policies. The lower the better. Arch: INTEL. |    |

|      | Dataset: GCAT Synthetic Input                                            | 57 |

| 5.6  | Different memory allocation policies. The lower the better. Arch: AMD.   |    |

|      | Dataset: NA12878 Real Input                                              | 58 |

| 5.7  | Different memory allocation policies. The lower the better. Arch: INTEL. |    |

|      | Dataset: A12878 Real Input                                               | 59 |

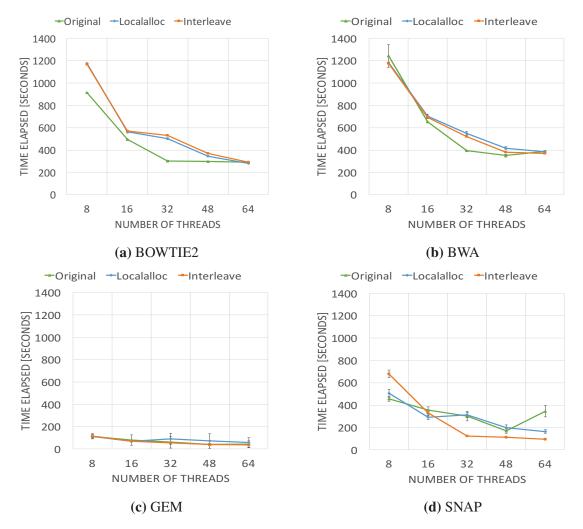

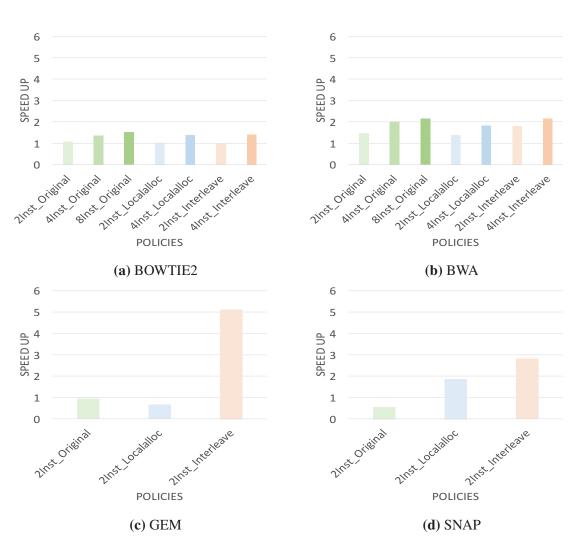

| 5.8  | Different memory allocation policies. The lower the better. Arch: AMD.   |    |

|      | Dataset: GCAT Synthetic Input                                            | 62 |

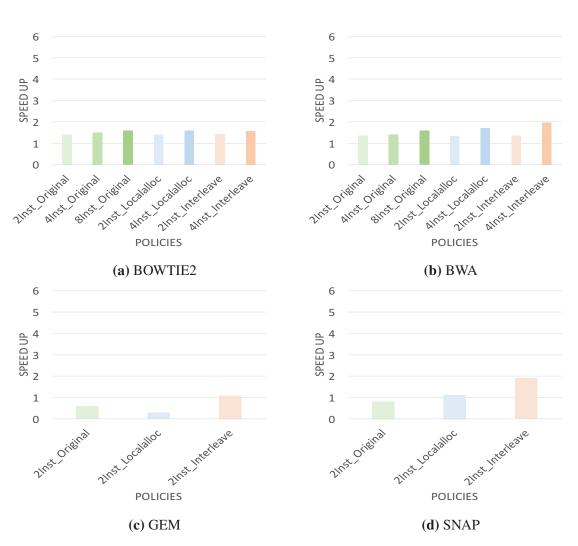

| 5.9  | Different memory allocation policies. The lower the better. Arch: INTEL. |    |

|      | Dataset: GCAT Synthetic Input                                            | 63 |

| 5.10 | Different memory allocation policies. The lower the better. Arch: AMD.   |    |

|      | Dataset: NA12878 Real Input                                              | 64 |

| 5.11 | Different memory allocation policies. The lower the better. Arch: INTEL. |    |

|      | Dataset: A12878 Real Input                                               | 65 |

| 5.12 | Execution times: Summary results for all aligners. The lower the better  | 66 |

## **List of Tables**

| 3.1 | Processor and memory information of the architectures used             | 24 |

|-----|------------------------------------------------------------------------|----|

| 3.2 | STREAM's vector kernels                                                | 27 |

| 5.1 | Detailed information about the aligners.                               | 54 |

| 5.2 | Instances created for each aligner                                     | 61 |

| A3  | Execution times for BOWTIE2 using different memory allocation policies | 67 |

| A4  | Execution times for BOWTIE2 using data partitioning                    | 68 |

| B5  | Execution times for BWA-MEM using different memory allocation policies | 68 |

| B6  | Execution times for BWA-MEM using data partitioning                    | 69 |

| C7  | Execution times for GEM using different memory allocation policies     | 69 |

| C8  | Execution times for GEM using data partitioning                        | 69 |

| D9  | Execution times for SNAP using different memory allocation policies    | 70 |

| D10 | Execution times for SNAP using data partitioning                       | 70 |

# Introduction

"Self-control means wanting to be effective at some random point in the infinite radiations of my spiritual existence."

- Franz Kafka

#### **1.1 Introduction**

NUMA (Non-Uniform Memory Access) systems have become increasingly common with the passage of time. Nowadays practically any HPC facility, research center or university has these systems in its infrastructure. Despite its complex hardware design, programs and applications do not have to be adapted to run on them (unlike other hybrid or semi-hybrid systems such as accelerators or GPUs). This feature is possibly one of its great advantages but at the same time its Achilles heel. Due that when applications are not aware of the hardware where they run on, they end up making sub-optimal use of resources. Writing parallel programs that exhibit good scalability is far from easy. Studying the physical characteristics of a NUMA architecture is key to understanding the impact that these can have on the performance of the applications that are run on. However, if programmers wrote extremely optimal and architecture-dependant code, they would narrow the machines where such code could be executed on, so it is not a feasible solution either. Our initial hypothesis is that somewhere between these two points there is the proper balance: where the advantages surpass the drawbacks, by applying execution strategies to applications to optimize their execution time without loosing flexibility.

In this research we propose a benchmark suite to characterize NUMA architectures, through a set of well-known benchmarks. This information helps to see the limitations of our system for applications that intensively use the memory system, either in idealistic scenarios with purely sequential access patterns or unfavorable scenarios where accesses are completely random. The acquired knowledge is translated into a guideline for final users of NUMA system, in order to develop NUMA execution strategies for memory bound applications. One main aspect of our proposal is that the user can take benefit of the architecture while improving the performance of the application used without modifying a single line of code.

To validate the NUMA execution strategies based on our methodology, we designed an experimentation using real memory bound applications: genomic mappers. Most mappers take advantage of parallelization techniques in order to reduce the computational demands involved in the alignment of millions of reads onto a reference sequence. Numerous software tools have been developed in recent years and many studies have evaluated their performances through several comparison criteria. In general, comparison studies have focused on mapper sensitivity and mapper accuracy, while computational and time requirements have received comparatively less attention.

Our proposed NUMA execution strategies mitigate two major drawbacks of these systems: the latency of remote data accesses and the concurrence of multiple threads contending for

a single shared resource. We executed the mappers using different techniques of memory allocation like interleave but we also introduce a proposal based multiple instances to reduce the intense usage of interconnection bus. As a result we obtained improvements in the mappers performance of up to 5x. We also provide an easy to follow guideline for the final user to understand the architecture been used and make the most of it.

#### **1.2** Contribution

As a result of this study we published three papers:

- 1. Josefina Lenis and Miquel Àngel Senar "On the Performance of BWA on NUMA Architectures." TrustCom/BigDataSE/ISPA (3) 2015: 236-241 (PBIO) [3]

- Josefina Lenis and Miquel Àngel Senar "Optimized Execution Strategies for Sequence Aligners on NUMA Architectures." Euro-Par Workshops 2016: 492-503 (PBIO) [4]

- Josefina Lenis, Miquel Àngel Senar "A performance comparison of data and memory allocation strategies for sequence aligners on NUMA architectures." Cluster Computing 20(3): 1909-1924 (2017) [5]

In our first work, we analyzed the performance of BWA-ALN, (Burrows-Wheeler Aligner) [6], where we detected scalability problems exhibited by BWA-ALN, and we proposed simple system-level techniques to alleviate them. We obtained results up to 4-fold speed higher than the original BWA-ALN multithread implementation.

In the second paper, we extended the study to other popular aligners from the literature. We analyzed performance problems of four aligners that constitute representative examples of the two most commonly used algorithmic strategies: hash tables and Burrow Wheeler Transform (BWT). The aligners under study were: BWA-MEM [7] (a newer version of BWA-ALN especially suited to dealing with longer reads), BOWTIE2 [8] (an ultrafast and memory-efficient tool for aligning sequencing reads to long reference sequences), GEM (GEnome Multi-tool) [9] and SNAP (Scalable Nucleotide Alignment Program ) [10]. These aligners are widely used by the scientific community and real production centers, and frequently updated by developers. Although all the aligners under study take advantage of multithreading execution, they exhibit significant scalability limitations on NUMA systems. Data sharing between independent threads and irregular memory access patterns constitutes performance-limiting factors that affect the studied aligners. We have applied various memory allocation

policies as well as several data distribution strategies to these aligners and we have obtained promising results in all cases, reducing memory-bound drawbacks and increasing scalability.

In the last paper, we also extend our previous results by expanding our comparison study to two different NUMA systems, one based on Intel Xeon and the other one based on AMD Opteron, and by introducing a hybrid execution strategy that combines both data partitioning and memory allocation policies.

#### 1.3 Related work

Since the emergence of the NUMA architectures in the 80s, there has been studies of the asymmetric accesses in these systems. Since then, NUMA systems have changed a lot compared to the old ones. And while many of the fundamental concepts that have been studied for decades remain, there are many others that need to be revised in order not to fall into fallacies when it comes to predicting the performance of applications in these systems.

Both researchers and programmers a like, have helped to broaden the understanding of these systems and improve their use. Mainly through performance models, libraries, data mapping tools and threads.

Between the most outstanding studies three great categories can be described:

#### Threads and data mapping tools

Challenges in memory access on NUMA systems have been addressed by some approaches that tried to optimize locality at the OS level. The AutoNUMA patches for Linux [11] implement locality-driven optimization along two main heuristics. First, the threads migrate toward nodes holding the majority of the pages accessed by these threads. Second, the pages are periodically unmapped from a process address space and, upon the next page fault, migrated to the requesting node.

Carrefour [12] [13] is another recent tool that consists of a memory-placement algorithm for NUMA systems that focuses on traffic management. As in our approach, Carrefour focuses on memory congestion as the primary source of performance loss in current NUMA systems. It places memory so as to minimize congestion on interconnecting links for memory controllers. By using global information and memory-usage statistics, Carrefour applies three main techniques: memory collocation (to move memory to a different node so that accesses are likely local), replication (copying memory to several nodes so that threads from each node can access it locally) and interleaving (moving memory so that it is distributed evenly among all nodes).

AsymSched [14] is a dynamic thread and memory placement algorithm for Linux, that takes into account the bandwidth asymmetry in NUMA systems. AsymSched is based on 3 techniques: thread migration, full memory migration and dynamic memory migration.

In the three mentioned cases (AutoNUMA, Carrefour and AsymSched), memory management mechanisms are implemented in the Linux kernel and require a patch to be applied to the virtual memory layer. Our work, however, focuses on the evaluation of techniques that can be applied at the application level and therefore don't require root permissions to be applied to any NUMA system.

#### **Application characterization tools**

An interesting tool is Tabarnac [15], that not only identifies under-performance memory access patterns but also can provide with a solution of how to improve the source code of the program. Tabarnac is only used with benchmarks where a clear access pattern can be identified. However when complex combination of access pattern happen simultaneously, can't offer a solid solution.

In [16] Majo et. al provides a series of guide-lines software-developer-oriented to achieve an efficient use of NUMA systems. In this paper is remarked how the access pattern of a program have a huge impact in the overall performance.

#### Hardware characterization tools

In [17] the authors present a comprehensive study of 2 NUMA processors: Intel (Sandy Bridge-EP) and AMD (Bulldozer). They proposed a set of benchmarks to perform an indepth analysis of current ccNUMA multiprocessor systems with processors. One of the most important contribution of this work is related to the specification of the cache-coherent protocols used by the different manufacturers.

#### **NUMA Performance Models**

Similar study to our work, Braithwaite et al. [18], who propose an "Empirical Memory-Access Cost Model in Multicore NUMA ARchitecture". Using STREAM benchmark [19][20] and LMBENCH [21], the author develops a benchmarking methodology, who through simple task-scheduling experiments to improves the performance of applications. Our study extends

this notion and also considers contention problems, not only memory-access cost due latency or memory bandwidth. We also consider the importance of executing programs in instances as a possible outcome prediction of our model.

The performance model Roofline [22] is designed to assist in software development and optimization by providing detailed and accurate information about machine characteristics. The Roofline model is a visually performance model used to relate computational performance with the memory capacities of architectures. The Roofline model helps to find possible bottlenecks and to identify the performance boundaries for a given processor, however does not provide any solution on how to solve such issues. An extended version of the Roofline [23] to NUMA systems was presented by Lorenzo et al. In this work, the model was extended to show the dynamic evolution of the execution of a given code. In it, is successfully shown the impact of thread migration. Although this work is a useful tool to understand and characterize the behaviour of the execution of parallel codes, only is tested with computational-bound applications.

#### Mappers enhancer tools

Genome alignment problems have been considered by Misale et al. [24]. The authors implement a framework to work under BOWTIE2 and BWA to improve the local affinity of the original algorithm. Herzeel et al. [25] replaces the pthread-based parallel loop in BWA with a Cilk *for* loop. Rewriting the parallel section using Cilk removes the load imbalance, resulting in a factor 2x performance improvement over the original BWA.

In both cases - Misale et al. and Herzeel et al. - the source code of the applications -aligners- are modified, which might be a costly action and dependent on the application version. Abuin et. al. [26] presented a big data approach to solving BWA scalability problems. They introduce a tool named BigBWA that enables them to run BWA on several machines although it does not provide a clear strategy for dividing the data or setting the number of instances. In contrast, our approach can be applied to different aligners with minimal effort and, although not tested yet, it can be easily applied to distributed memory systems. Our work is complementary to all the works mentioned above.

#### 1.4 Thesis Structure

The thesis is structured as follows: In chapter 2 we explain briefly the history of parallel systems then we describe the basic concepts of NUMA architectures and provide concrete

details of the two systems used in our experiments. In chapter 3 we present our methodology to characterize the NUMA systems and obtain *NUMA Performace Aspects*. Chapter 4 introduces the problem of sequence alignment and a behavioral characterization of aligners used in this study. In chapter 5 we describe in detail the NUMA execution strategies proposed to validate our methodology, we also explained all scenarios used to evaluate the performance improvement of aligners under study and analyzed the results obtained in our experiments . Finally, in chapter 6 there is the conclusions and the future lines of work.

# **2** HPC Systems

"In the fight between you and the world, second the world."

- Franz Kafka

#### 2.1 Introduction

This chapter briefly reviews some fundamental concepts related to high performance computing. In particular, we present an introduction to the basic elements that characterize the architectures of current computers. The description starts from the analysis of the dominant architecture in current microprocessors and finishes by briefly reviewing the computer architectures that are commonly used to solve computationally complex problems. This sets the base to discuss NUMA architectures advantages and drawbacks in depth. Finally, a brief review of all the HPC performance tools used and evaluated during this study.

#### 2.2 Brief history of parallel architectures

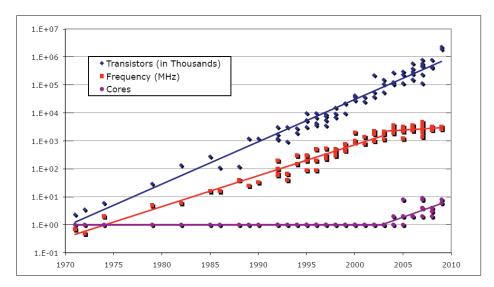

In 1965 Gordon Moore predicted that the number of transistors in an integrated circuit followed a progression in which that value doubled every 18 months. This prediction, known as Moore's Law, has been fulfilled since then and continues in force. Translated in terms of performance, this prediction has meant a constant increase in the computing capacity of successive generations of microprocessors thanks to the increase in the frequency of its clock and the integration of architectural solutions such as the parallelism at the instruction level that decreased the latency of the memory system. In this way, sequential programs could be executed more quickly and this gain could be achieved transparently for the programmer. The progression in the improvement of the performance of the computers was altered at the beginning of the last decade by the physical limitations that derived from the problems of heat dissipation and consumption exhibited by the microprocessors. As of 2004, these limitations stopped the increase in the frequency of the processors that instead of having a single processing unit (control unit plus logical arithmetic unit) by chip, they had several of them grouped in an entity called core.

In the 2.1 the evolution of the integration levels of the processors, their frequencies and the number of cores is shown [1]. Evolution in time of the number of transistors per chip (blue), the frequency (red) and the number of cores per processor (purple).

The architecture of a multicore processor is based on the existence of two or more execution cores within a single processor. The operating system perceives each of its execution core as a discrete logic processor with all its associated execution resources. Multicore processors perform more work per cycle, are able to operate at a lower frequency, and present

Figure 2.1: More's Law vs Number of cores Source [1]

improvements in the performance of calculation activities and bandwidth intensive.

The emergence of multicore processors has meant, however, a paradigm shift from the point of view of improving the execution of applications. This improvement is no longer achieved automatically by the effects of increases in the clock frequency, but must be achieved by conveniently exploiting the inherent parallelism offered by the new processors in the form of multiple cores integrated in single device.

However, unlike single-core processors, much of the responsibility for better performance now falls on the shoulders of programmers. The era where programmers relied on hardware designers to make their programs faster has ended [27]. The performance improvements in the new generations of computers will depend on the changes that are introduced in the applications and in the system tools so that the computing capacity provided by the multicore systems is exploited.

Currently Moore's law is fulfilled at the level of cores in addition to the level of transistors. The increase in the average of cores is shown, since the appearance of the multicore architectures in 2004, in Supercomputers (infrastructures composed of thousands of multicore processors). The increase in cores has doubled every two years since the emergence of multicore processors in 2004 [28]

The limits that separate high-performance computing from ordinary computing are rather arbitrary, since HPC refers merely to calculations that are made on computers more powerful than the standards [1]. With 500 u\$s today you can buy a laptop that have more computing capacity, more main memory and a hard drive with more space than a computer of 1000000

u\$s in the year 1985 [27].

#### 2.3 Parallel Architectures

The parallel architectures are defined under the MIMD (Multiple Instruction Multiple Data) paradigm, where different instruction flows are applied to several data streams. In this section we will review the 3 broad categories that parallel architectures are normally classified into:

- Shared-memory systems

- Distributed-memory systems

- Hierarchical (hybrid) systems

#### 2.3.1 Shared-memory system

In shared memory systems, all CPUs (one or more) share the one physical memory address space. Within this category there are 2 important set of shared-memory systems that have a different performance and different complexity:

- Uniform Memory Access (UMA): where latency and bandwidth are the same for all processors and all memory locations.

- Non-Uniform Memory Access (NUMA) in this case the memory is physically distributed through several processors but logically shared, so the memory addresses are global. Memory access times vary depending on the processor and the memory location that is intended to access.

For this paradigm the most popular programming libraries include OpenMP[29], Cilk[30] and Pthreads[31].

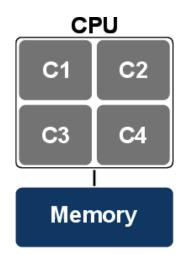

#### UMA

The most simple layout of parallel system is the UMA. Processors access memory through the shared bus as seen in Figure 2.2. As stated before, all CPUs have the same latency and bandwidth when accessing memory. This is why are known as Symmetric multiprocessor (SMP) where systems use this centralized memory approach, where each processor is connected to a shared bus. This shared bus handles all accesses to main memory and I/O. Communication

between CPUs is implicit and transparent. All these characteristics makes it a very easy to program for. Converting a serial code into a parallel code on UMA architecture requires a minimal effort. However, this symmetric pattern does not scale properly, there is a limited number of CPUs that can be added to a UMA architecture without turning the shared bus into a bottleneck. In order to maintain scalability of memory bandwidth with CPU number, non-blocking crossbar switches can be built that establishes point-to-point connections between sockets and memory module but at the cost of giving up the UMA principle [32].

**Figure 2.2:** A UMA architecture provides each CPU core (C1-C4) the same memory access latency and bandwidth. Source [2]

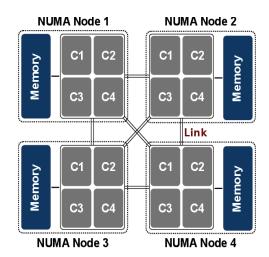

**Figure 2.3:** A NUMA architecture connects different NUMA nodes (Nodes 1-4) - typically multicore CPUs (C1-C4) - via interconnect links (Link), to enable a single logically shared global memory. . Source [2]

#### NUMA

In NUMA systems, the main memory is physically distributed across the processors but, logically, this set of main memories appears as only one large memory, so the accesses to different parts are done using global memory addresses [1]. A processor and its respective memory are called a NUMA node. A program running on a particular processor can also access data stored in memory banks associated with other processors in a coherent way but at the cost of increased latency compared to accessing its own local memory bank. In general, parallel applications that may run using multiple processors are not usually designed taking the NUMA architecture into account, mainly because is still a shared-memory system and processors do not explicitly communicate with each other so communication protocols are hidden within the system. However in NUMA architectures that can have a high cost in

**Figure 2.4:** In a distributed-memory model, the memory is physically and logically distributed among the individual processing units (P1-P3), e.g., CPUs. Accessing data from remote memory locations requires to initiate a data transfer protocol, such as point-to-point communication provided by the MPI. Figure source: [2]

performance if the data is not allocated in an optimal fashion as too many remote access may occur.

#### 2.3.2 Distributed-memory systems

In parallel distributed-memory computers, processing units do not share memory but each has its own memory address space as shown in Figure 2.4. This model originates from a time where a CPU contained a single processing core. Such a setup is typically not found anymore in today's cluster systems due to the advent of multicore CPUs. However, the model still serves well as an introduction to distributed computing, as the concepts are still applicable[2]. When a parallel program is executed, the compute nodes exchange information between them by passing messages that are transferred over interconnection networks (Gigabit Ethernet, Infiniband, etc). The dominant programming standard in this type of systems is MPI [33], although there are other alternatives such as co-Array Fortran[34], GASnet[35], Charm++ [36] among others. In distributed-memory system there are no longer race conditions to access main memory however the communication between process becomes explicit and need to be handled fully by the programmer. This increases significantly the programming complexity.

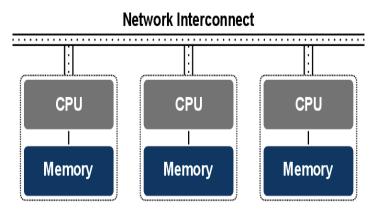

#### 2.3.3 Hybrid systems

Nowadays, no system is purely shared-memory or strict distributed-memory, most configurations are combination of both. Commonly composed by a layout of NUMA architectures

**Figure 2.5:** In hierarchical systems the distributed- and shared-memory model are combined. In the depicted case three UMA-based shared-memory nodes are connected via a network connection, however, NUMA systems can be used in a similar manner. Figure source: [2]

connected over fast network interface, as shown in Figure 2.5. The programming approach is also hybrid: using MPI for the inter-node communication and OpenMP for intra-node executions. The concept behind hybrid systems is broader than just multicore computers connected via network, it is also used to name any system layout that mixes available programming paradigms on different hardware layers. An example could be a cluster built from nodes that contains, besides the "usual" multicore processors, additional accelerator hardware, ranging from application-specific add-on cards to GPUs (graphics processing units), FPGAs (field-programmable gate arrays), ASICs (application specific integrated circuits), co-processors, etc.[32]

#### 2.4 Study Case: NUMA Systems

NUMA arrived as a solution to bottlenecks produced by the intensive access to the single memory bus present on Symetric Multi-Processor (SMP) systems. To profit from the scalability provided by NUMA systems, applications need to be aware of the hardware they are running on and the memory allocation policies applied by the operating system. Memory pattern accesses that imply memory transfers from non-local banks will negatively impact the overall execution time due to the distance penalty of remote memory banks. A second issue that can also increase execution time is contention; applications employing large numbers of threads and storing all data in a single bank, generate a race between threads, congesting the connection links and downgrading access times -local and remote- to memory.

A processor and its respective memory bank is called NUMA domain or NUMA node, and

we will use these terms indistinctly along this thesis. Other clarification that needs to be done respect naming it is related to which part of the NUMA node we are referring to. For example if we say "threads are bound to NUMA node 0" we mean the processor but if the phrase changes to "data is placed on NUMA node 0" we mean the memory bank.

#### 2.4.1 Our Infrastructure

As an example of NUMA systems, we can see the following two Figures (Figure 2.6 and Figure 2.7) that represent the two architectures we employed in this study, one manufactured by AMD and the other by Intel.

**Figure 2.6:** Schematic diagram of the AMD Opteron 6376 architecture (Abu-Dhabi)

**Figure 2.7:** Schematic diagram of the Intel Xeon E5 4620 architecture (Sandy Bridge)

The first system, shown in Figure 2.6, is a four-socket AMD Opteron Processor 6376, with each socket containing 2 dies packaged onto a common substrate referred to as a Multi-Chip Module (MCM). Each die (processor) consists of 8 physical cores that share a 6 MB Last Level Cache (LLC) and a memory bank. Only one thread can be assigned to one core and, therefore, up to 64 threads can be executed simultaneously. The system has 128GB of memory, divided into 8 modules of 16GB DDR3 1600 MHz each. The second architecture (Figure 2.7) is an Intel Xeon CPU E5 4620 -also four-socket. Each socket contains an 8 core-processor and a 16 MB LLC. The total number of cores is 32. 64 threads can be executed simultaneously using HyperThread technology. This system also has a memory of 128 GB, but it is divided into 4 modules of 32GB DDR3. 1600MHz each.

Nodes are connected by links - HyperTransport (AMD) and QuickPath Interconnect (Intel). Memory bandwidth for both cases depend on the clock, the width of the interconnection links (number of bits that can be sent in parallel in a single transfer), the data rate (single or double), and the actual bandwidth between memory controller and the DDR3 memory modules [18].

### **Allocation Policy**

Linux operating system uses Node Local allocation as the default allocation policy when the system is up and running. Node Local allocation means that when a program is started on a CPU, the data requested by that program will be allocated to a memory bank corresponding to its local CPU.

Specifying memory policies for a process does not cause any memory allocation [37]. Allocation policy takes effect only when a page is first requested by a process. This is known as the first-touch policy, which refers to the fact that a page is allocated based on the effective allocation policy when a process first uses a page in some fashion. Despite the default Linux policy, a programmer can set an allocation policy for its program using a component of NUMA API [38] called libnuma. This user space shared library can be linked to applications and provides explicit control of allocation policies to user programs. The NUMA execution environment for a process can also be set up by using the *numactl* tool [38]. *Numactl* can be used to control process mapping to cpuset and restrict memory allocation to specific nodes without altering the program's source code.

A popular memory allocation policy is interleave where memory pages are allocated between selected nodes in a round-robin fashion. The idea behind it is that all used node all accessed equally as opposed to all the traffic being concentrated on one node.

# 2.5 Measuring performance

In this section, in first place we will enunciate the definitions of the metrics used during this work and later we will describe all the performance monitoring tools used and/or test for this work.

## 2.5.1 Definitions

When we think about computer performance we think of the effectiveness that a computer system complete a task. Depending on the context, 'effectiveness' may involve one or more of the following concepts:

• Short time for a given computational work

- High throughput (rate of processing work)

- Energetic efficiency of computing resource(s)

- High availability of the computing system or application

- Fast (or highly compact) data compression and decompression

- Short data transmission time

In HPC time is the most important criteria to define a system performance. The computer that performs the same amount of work in the shortest time is the fastest.[27] The execution time of a program is measured in seconds. In order to improve performance for a given application, it is necessary to monitor, analyze and tune the critical elements involved in the execution.

#### **Execution Time**

It is the measure that shows how long it takes to execute a process. It is defined as the interval between the start of the execution and the end of it. For parallel executions, the end of the execution is given when the last thread or parallel process that composes the application ends.

#### SpeedUp

It is a metric that characterizes the gain of running a program in parallel. Let T(n,1) be the run-time of the fastest known sequential algorithm and let T(n,p) be the run-time of the parallel algorithm executed on p processors, where n is the size of the input.

$$Speedup(n) = \frac{T(n,1)}{T(n,p)}$$

(2.1)

### **Parallel efficiency**

It is obtained from the division between the Speedup and the number n of computing elements with which the application is executed (see equation 2.2). The value of the efficiency can vary between 0 and 1. Being 1 an ideal value that represents that the application is completely parallel.

$$Parallelefficiency = \frac{Speedup(n)}{n}$$

(2.2)

## 2.5.2 Performance tools

In this section we will describe the tools used to measured the behavior of benchmarks and the applications tested as validation that later we will be discussed in chapters 3 2. Two important features present in performance tools are: profiling and tracing. As stated Sameer Shende in [39].

"To understand the behavior of the parallel program, we must first make its behavior observable. To do this, we regard the execution of a program as a sequence of actions, each representing some significant activity such as the entry into a routine, the execution of a line of code, a message communication or a barrier synchronization. Performance analysis based on profiling and tracing involves three phases:

- instrumentation or modification of the program to generate performance data,

- measurement of interesting aspects of execution which generates the performance data and

- analysis of the performance data.

••

In the following subsections we will provide a brief description of the hardware counters used and the tools we rely on to do our research.

### **Hardware Counters**

Hardware counter are extra logic added to the CPU that track low-level operations or events that happen within the processor [40]. Traditional hardware performance counters measure only values on a single core. A chip package has many resources which are package-wide and thus need a separate performance reporting mechanism. The shared socket-wide values are called Offcore events are per-core values on their way to the uncore [41].

For all the experiments performed in this work we measured the basic hardware given by perf tool [42]. These are:

- **context-switches:** when a task needs to be change for while ensuring that the tasks do not conflict. A high number of contest switches could impact negatively the performance of an application.

- **CPU-migrations:** when a task is moved from one computing environment to another.

- **page-faults:** when a running program accesses a memory page that is not currently mapped by the memory management unit

- **cycles :** usually, the time required for the execution of one simple processor operation such as an addition; this time is normally the reciprocal of the clock rate.