# UNIVERSIDAD DE CANTABRIA

Departamento de Tecnología Electrónica, Ingeniería de Sistemas y Automática

# **TESIS DOCTORAL**

# TEST BASADO EN SENSORES DE CORRIENTE INTERNOS PARA CIRCUITOS INTEGRADOS MIXTOS (ANALÓGICOS-DIGITALES)

Memoria presentada para optar al grado de

## DOCTOR EN CIENCIAS FÍSICAS POR LA UNIVERSIDAD DE CANTABRIA

por Román Mozuelos García,

Licenciado en Ciencias Físicas,

Santander, 2009

DfT para Circuitos SC 223

# Capítulo 6

#### DFT PARA CIRCUITOS DE CAPACIDADES CONMUTADAS

En este capítulo se presenta un método de test basado en el análisis de la carga extraída y suministrada al nudo de referencia o tierra virtual de los circuitos de capacidades conmutadas (SC). Para ello se integra junto al CUT un bloque, denominado sensor de carga, que realiza el muestreo dentro del chip de la carga con objeto de obtener una buena resolución de la magnitud medida. Se describe el diseño del sensor, como se acopla al circuito bajo test y se caracterizan las prestaciones de dicho sensor de carga. También se realiza una evaluación de fallos del funcionamiento del sensor frente a un conjunto de fallos inyectados en el CUT para estimar la calidad del método de test.

#### 6.1 INTRODUCCIÓN

Los circuitos analógicos convencionales hacen amplio uso de las resistencias para realizar sus funciones analógicas basándose:

- 1. En la relación entre resistencias para establecer la función de transferencia de los amplificadores y los convertidores ADC y DAC.

- 2. En la magnitud de la resistencia para la curva de transferencia de los convertidores corriente a tensión y tensión a corriente.

- 3. En el producto de una resistencia por un condensador (RC) para fijar la respuesta en frecuencia de filtros activos, generadores de señal, etc...

En la tecnología MOS es relativamente fácil implementar llaves, pequeños condensadores y amplificadores operacionales, pero es difícil fabricar resistencias con una buena precisión. Esta limitación se evita debido al hecho de que una resistencia se puede emular utilizando una llave CMOS controlada por una señal periódica y un condensador. Esto significa que las

resistencias pueden ser eliminadas completamente y los productos RC se transforman en un cociente de capacidades. A los circuitos que utilizan esta técnica se les conoce como circuitos de capacidades conmutadas (SC) [All84]. De este modo, la manipulación de las tensiones muestreadas y la implementación de la función analógica del sistema se llevan a cabo mediante la transferencia de carga entre condensadores flotantes.

Los circuitos de capacidades conmutadas vienen siendo utilizados extensivamente desde hace años y su diseño es una materia bien establecida [Bro79]. Sin embargo, la aplicación de estrategias de diseño-para-test (DfT) como método para facilitar su verificación está menos desarrollada.

En este capítulo se propone un método de diseño para test basado en el análisis de los paquetes de carga que circulan por el circuito SC. Primero se presenta el diseño de un circuito sensor que muestrea los paquetes de carga y realiza un primer tratamiento dentro del circuito bajo test para proporcionar una tensión analógica de salida fácilmente analizable por un sencillo equipo de test. A continuación realizamos un estudio de la influencia de la inclusión del sensor de carga en las prestaciones de un circuito de prueba sencillo, como es un integrador no-inversor paralelo SC.

Para validar el método de test se ha fabricado el sistema formado por el integrador y el sensor de carga con la posibilidad de activar un conjunto reducido de defectos en el integrador. De este modo se comprueba como el sensor es capaz de discriminar entre el circuito libre de fallos y los circuitos defectuosos.

Finalmente se analiza la aplicación del sensor de carga a un circuito más complejo como es el caso de un convertidor serie analógico-digital, simulando el efecto del sensor sobre el funcionamiento del ADC, realizando una evaluación de fallos para comprobar la detección de circuitos defectuosos y estudiando la utilización del sensor de carga como herramienta alternativa para obtener las prestaciones de linealidad del convertidor.

## 6.2 DISEÑO PARA TEST (DFT)

El diseño para test (DfT) se ha definido en el dominio digital como la técnica que permite mejorar la controlabilidad y la observabilidad de las señales internas del circuito. En el mundo analógico se puede considerar que el DfT es cualquier técnica, procedimiento o estrategia que de lugar a una mejora del test off-line y/u on-line. Esto, al igual que en el mundo digital, se suele traducir en estrategias para mejorar el control y la observación de nudos internos del circuito [Vin98].

Entre las ventajas del DfT se encuentran:

- 1. Habilita la aplicación de métodos de test tradicionales a los módulos internos de los sistemas integrados. Para hacer el diseño complejo manejable, se suele dividir el circuito original en sus bloques funcionales o macros.

- 2. El DfT permite reducir el tiempo de test y mejorar la cobertura de fallos.

3. Aunque el objetivo primordial del DfT es reducir el coste del test también tiene otras ventajas durante las etapas de diseño y fabricación ayudando, por ejemplo, a depurar y verificar el diseño.

Aunque, normalmente el DfT sólo está habilitado durante la etapa de test requiere añadir módulos adicionales al circuito bajo test. Por lo tanto su uso conlleva, además de un incremento de área, un cierto impacto sobre las prestaciones del CUT.

El DfT no elimina la necesidad de generar señales externas y observar los resultados del test a diferencia de un BIST, sin embargo el incremento de área es sensiblemente inferior en el caso del DfT que el del BIST.

## 6.2.1 Formas de DfT genéricas

Las técnicas de diseño para test genéricas no utilizan las propiedades específicas del circuito bajo test y son aplicadas a diferentes clases de circuitos. Su principal objetivo es aislar los bloques funcionales o macros en los sistemas integrados embebidos de tal modo que se puedan acceder a sus entradas, observar sus salidas y aplicar un conjunto de test funcionales [Fas88].

En este sentido, hay diferentes aproximaciones que se basan en alguna de estas técnicas; Uso de multiplexores para conectar todas las entradas/salidas a un mismo cable o bus, método de by-pass donde las macros que no están siendo verificadas se reconfiguran para establecer un camino entre el exterior del chip y las entradas/salidas del macro bajo test, utilización de registros de desplazamiento analógicos o uso de un bus de test analógico.

Uso de multiplexores. Para aumentar la controlabilidad y la observabilidad, el circuito se particiona y los componentes se aíslan a nivel de macro. Se usan multiplexores analógicos implementados con llaves y se añaden buffers para asegurar que ninguna señal se carga más de lo necesario debido a estas modificaciones [Wag89]. Algunas veces, no sólo se observa la salida del CUT sino también alguno de sus nudos internos o puntos de test. La introducción de multiplexores en el camino de la señal puede dar lugar a la degradación de las prestaciones del circuito

**Sw-Opamp.** Este método se basa en la reconfiguración de un amplificador operacional en un módulo seguidor de tensión (sw-opamp). El sw-opamp en modo test utiliza una tercera entrada, diferente de las propias del amplificador operacional, para el seguidor de tensión. Esto permite mejorar la inyección de estímulos al bloque analizado del CUT y facilita el procesado de su salida al hacer trasparentes los restantes módulos que no están en test. Esta estructura fue originalmente propuesta en [Bra93] y posteriormente los autores la aplicaron al test de un lazo de enganche de fase (PLL) [Bra95].

Varias implementaciones CMOS se estudian en [Vaz96a][Vaz96b] junto con el impacto en las prestaciones del circuito que conlleva la adaptación del amplificador operacional al circuito sw-opamp.

**Registros de desplazamiento digitales.** En los circuitos mixtos, se puede utilizar los esquemas digitales de DfT para facilitar el test de los bloques analógicos accediendo a las señales de las interfaces A/D y D/A por medio una cadena scan digital diseñada para monitorizar los componentes analógicos y no el circuito entero [Ast92][Fla93].

Llevando un poco más lejos este método de test, los componentes digitales pueden ser utilizados para generar los test de los convertidores D/A y para observar las salidas de los convertidores A/D en sistemas con capacidad de procesamiento de señal (DSP), permitiendo análisis complejos de las señales [Ter93].

**Registros de desplazamiento analógicos.** Dado el éxito de las técnicas scan en circuitos digitales, donde la controlabilidad y observabilidad de los nudos se mejora conectándoles a un registro de desplazamiento, se ha extendido este procedimiento a los circuitos analógicos. En los circuitos analógicos se han diseñado registros para desplazar tensiones (VBIST) y corrientes (IBIST).

La estructura VBIST utiliza bloques de muestreo y retención (S&H) formados por un amplificador operacional y un condensador para almacenar la tensión [Wey90]. Un conjunto de llaves conectan a la etapa de S&H bien el nudo muestreado del CUT, aislado por medio de un buffer, o bien la etapa anterior de S&H para implementar la operación de desplazamiento hasta el pin de test de salida. Una segunda implementación busca reducir el área de la estructura VBIST eliminando las etapas de S&H [Wur93] conectando a través buffers uno por uno los nudos del CUT a una línea de salida.

El IBIST muestrea la corriente del CUT utilizando técnicas propias de los circuitos de corrientes conmutadas (SI) [Wey92]. Las corrientes se copian en celdas de memoria SI y se desplazan hacia el pin de salida.

Los principales problemas de estos dos métodos de test (VBIST e IBIST) es el error que se acumula en la magnitud muestreada durante la propagación de la señal a través de las diversas etapas, un incremento de área significativo y una velocidad de operación relativamente baja. Además, el DfT no mejora la controlabilidad ya que sólo procesa las salidas del CUT.

Bus de test analógico. Uno de los métodos importantes para mejorar la accesibilidad de un sistema electrónico es hacer uso de un bus de test. Un bus de test analógico es un cable que permite interconectar varios nudos del circuito por medio de llaves de transmisión CMOS, lo que acota el número de pines externos de test de entrada y salida que es necesario añadir al chip. El primer articulo que describe el uso sistemático de un bus analógico controlando las llaves CMOS a través de una cadena scan digital fue [Fas88]. Estos primeros buses consistían en una línea conectada directamente [Yun94][Par93] o por medio de un buffer [Van89] al pin de test. Posteriormente, el ancho de banda de la señal procesada en el bus de test ha ido mejorando hasta alcanzar los 100MHz para lo cual se mantiene una capacidad reducida y constante en los nudos observados del CUT [Sun95a].

En 1999, el estándar 1149.1 "IEEE Standard Test Access Port and Boundary-Scan Architecture" [IEEE1149.1] que describe el bus de test para módulos digitales se expandió para dar cobertura a las bloques analógicos dando lugar al IEEE P1149.4 [IEEE1149.4]. El nuevo estándar especifica un bus analógico de dos cables (o cuatro si la señal es diferencial) y un conjunto de módulos analógicos de acceso controlados por un registro de desplazamiento compatible con el 1149.1. La infraestructura utiliza el principio de forzar/medir para realizar medidas de baja frecuencia en un entorno con presencia de ruido digital [Oss99]. Una medida típica consistiría en aplicar un valor conocido de corriente o tensión DC+AC a un nodo del circuito a través de una de las líneas analógicas del bus y medir el resultado en otro punto del CUT utilizando la otra línea del bus. Ejemplos de la utilización del bus se encuentran en la página web del grupo de trabajo que lo ha desarrollado [Gro09] como el uso del IEEE1149.4 en un diseño comercial [Sun01].

Entre las ventajas del bus de test analógico IEEE1149.4 se encuentran la gran variedad de medidas que permite realizar en el CUT y la implementación de un soporte adecuado para obtener medidas robustas. El hecho de ser un estándar permite reutilizar los módulos de un diseño a otro y utilizar un método de test unificado para los niveles de componente, circuito integrado y placa de circuito impreso [Sun95b][Dim06]. Entre las desventajas se encuentra el incremento de área, el limitado rango de frecuencias a las que es aplicable y su impacto en el circuito bajo test.

*Test basado en oscilación.* El test de oscilación (OBT) reconfigura el circuito transformándolo en un oscilador durante la etapa de test donde la variación en los parámetros de oscilación (frecuencia, amplitud, nivel de continua) respecto al valor esperado se utiliza para determinar si el CUT es defectuoso o no [Ara99a].

Obtener un oscilador en CUT con ganancia superior a la unidad puede ser tan simple como añadir una llave entre la entrada y la salida. Sin embargo, si la ganancia es inferior a la unidad es necesario añadir un comparador digital o un inversor en el camino de realimentación. El método ha sido utilizado para realizar el test, entre otros circuitos mixtos, de amplificadores operacionales [Ara96a], filtros [Ara99b][Zar00][Mas06] y convertidores ADC y DAC [Ara96b][Hue03].

La ventaja de este método es que no requiere estímulos externos de test y utiliza un conjunto sencillo de medidas en la evaluación ya que se reduce a los parámetros de oscilación (frecuencia y amplitud) [Hue06]. Sin embargo, una de las dificultades para aplicar este método de test consiste en la necesidad de construir un oscilador robusto que garantice una oscilación sostenida y predecible sin alterar la estructura del CUT ni los valores de sus componentes.

Dado que el DfT no requiere un generador de estímulos, para convertir el OBT en un BIST únicamente es necesario incluir un módulo de evaluación junto al CUT. La medida de la frecuencia de oscilación puede ser implementada con un contador, la integración de la señal sinusoidal de oscilación nos permite obtener por una parte su nivel de continua DC y por otra

la amplitud si procesamos su versión rectificada. Todas estas operaciones se pueden realizar instantáneamente en un periodo de oscilación utilizando un modulador de primer orden  $\Sigma\Delta$  con sobremuestreo para digitalizar la señal y un contador [Vaz02].

#### 6.2.2 DfT para capacidades conmutadas

Los métodos de diseño para test desarrollados para circuitos analógicos de capacidades conmutadas se pueden clasificar en dos grandes categorías; DfTs basado en códigos donde se monitorizan nudos internos del circuito para detectar defectos sin interrumpir su funcionamiento y DfTs basados en reconfiguración donde la testabilidad del sistema se mejora incorporando la habilidad para reorganizar sus componentes en más de una configuración durante el test

#### 6.2.2.1 DfT basado en códigos

Los DfTs basados en códigos emplean esquemas utilizados para la detección "on-line" y el diseño de circuitos tolerantes a fallos [Vaz91][Hue93a][Mir96][Cha91]. Se genera un dato redundante que codifica diversas señales internas el circuito. Estas señales son analizadas con módulos diseñados expresamente para verificar que se encuentran dentro de los límites esperados y que los fallos no han corrompido el código.

Dado que tanto el generador de código como el analizador de la respuesta se integran dentro del chip, estos métodos permiten realizar el test en paralelo al funcionamiento del circuito. A este grupo pertenecen:

Circuitos diferenciales. La redundancia inherente a los circuitos diferenciales se puede utilizar para facilitar el test [Har97][Ste96][Kol95]. Se colocan módulos verificadores a las salidas de cada etapa del filtro, es decir, a la salida de sus amplificadores operacionales. Este módulo se diseña para eliminar el modo común en sus entradas y ser sensible a los fallos que corrompen el modo diferencial del circuito. Normalmente está compuesto por una etapa diferencial con un tercer transistor configurado en modo diodo controlado por el modo común.

También, basado en el análisis de las señales diferenciales, en [Mir96][Lub00] se propone utilizar un bloque analógico simple capaz de monitorizar varias etapas a la vez y proporcionar una indicación digital de error. Partiendo del estudio de un filtro implementado por una etapa biquad, extienden su aplicación a placas formadas por varios circuitos mixtos donde hacen uso del bus de test IEEE 1149.1.

**Replicación y comparación.** Una de las formas más sencillas de realizar el test on-line es integrar dos copias del mismo circuito (manejadas por la misma señal de entrada) y analizar las salidas que proporcionan. Un circuito comparador debe decidir cuando las señales son iguales o no. Este concepto se ha aplicado a circuitos de capacidades conmutadas en [Vaz91]. La desventaja de la duplicación del circuito completo son los requerimientos adicionales de área y potencia, mayores del 100%.

*Etapa extra*. Para aliviar los problemas inherentes a la técnica de duplicación completa, se ha propuesto la duplicación de una sola etapa de circuito en diversos filtros de capacidades conmutadas [Hue93b][Vaz95].

La etapa adicional se puede programar utilizando llaves para alterar el valor de los condensadores con objeto de que pueda replicar la funcionalidad de las diferentes etapas del circuito original en varias configuraciones de test. Una lógica de control activa unos multiplexores analógicos que permiten excitar con la misma señal de entrada tanto la etapa original del circuito como el módulo añadido en del DfT. Al mismo tiempo un mecanismo de comparación determina si la diferencia entre la salida de ambos bloques está dentro del límite tolerable para un circuito libre de fallo.

Las limitaciones de este método radican en el área adicional requerida y en el marginal efecto que tienen el circuito de conmutación sobre las prestaciones del filtro SC.

Suma de códigos. En sistemas digitales, la utilización de códigos de suma sirve para la detección on-line de errores y su corrección [Hua84]. Esta técnica se ha extendido a filtros analógicos y a circuitos que pueden ser descritos como sistemas de variables de estado en [Cha91]. La idea consiste en crear una nueva variable de estado como combinación de las variables originales. Se diseña un circuito de detección de error que implementa la nueva función y cuya salida se compara con la combinación adecuada de las señales internas del circuito bajo test.

En [Yoo97] los autores presentan un algoritmo que genera el vector de código optimo para el circuito de detección de error y que permite establecer el límite en la magnitud de la señal de error que clasifica a un circuito como defectuoso.

Pseudo-replicación. Esta técnica está orientada a circuitos SC no diferenciales y que contienen un solo camino para la propagación de la señal [Vin97]. La pseudo-replicación busca fallos en los componentes pasivos del circuito y se basa en la idea de cómo la funcionalidad de un filtro viene dada por el cociente de los condensadores, doblar o dividir por la mitad el valor de los condensadores no debería afectar a las prestaciones del circuito. Aprovecha que normalmente los condensadores del circuito están formados por varios elementos unitarios para construir dos filtros idénticos durante la etapa de test con diferentes valores absolutos de capacidades. Dado que los fallos deberían afectar de diferente forma a ambos filtros, se añade un módulo como observador analógico para detectar la desviación en su comportamiento. El método de Pseudo-replicación requiere parar el funcionamiento normal del circuito y pasar a modo test.

#### 6.2.2.2 DfT basado en reconfiguración

El test basando en reconfiguración requiere añadir una red de conmutación y la creación de un modo de test, en el cual el circuito se reconfigura con una funcionalidad diferente para la que fue diseñado.

El método más sencillo busca aumentar la controlabilidad y observabilidad de las señales internas del circuito [Som94]. Mientras que un segundo tipo reorganiza los bloques del circuito para obtener un sistema más fácilmente testable [Vaz94][Duf97][Hue02a], la respuesta de este circuito modificado se usa de guía para determinar si el circuito es defectuoso.

Al modificar la estructura del circuito bajo test, la reconfiguración es incompatible con la realización de un test on-line. Sin embargo, es posible convertir el método de test en un BIST añadiendo un generador de estímulos y un circuito que analice la respuesta del CUT.

Las siguientes las propuestas de diseño para test se pueden encuadrar en este grupo.

Aislamiento de la etapa de test. La aproximación básica es similar a la utilizada en los circuitos digitales, el circuito se divide en varios bloques de tal modo que las entradas y salidas puedan ser directamente controlables y observables.

Mientras se está analizando una etapa del circuito los restantes bloques se configuran como seguidores de tensión. De tal modo que los módulos previos propagan la señal de entrada adecuada al modulo bajo test y las etapas que están después dirigen la salida hacia un nodo observable [Som94][Ren96].

Es decir, la reconfiguración simplemente mejora el acceso a los bloques del circuito sin alterarlos. Esto se logra utilizando un control adicional de las llaves del circuito SC para transformar el circuito conmutado en un amplificador continuo cuya ganancia viene dada por la relación entre los condensadores

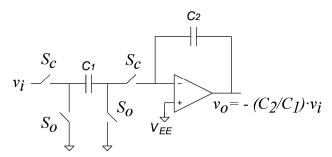

Figura 6.1. Reconfiguración para el aislamiento de la etapa

Por ejemplo, considerando el integrador de la figura 6.1, se cierra el conjunto de llaves  $S_C$  que propagan la señal mientras que todas las llaves conectadas al nudo de tierra  $S_O$  permanecen abiertas.

Esta aproximación de test complica la lógica de control de las llaves y no garantiza que todos los fallos que puedan causar un funcionamiento erróneo del circuito sean detectables cuando se reconfigura el sistema para evaluar cada etapa por separado.

*Biquads programables.* Otra técnica basada en el control de las llaves del circuito SC ha sido propuesta por [Vaz94] para realizar el test de filtros SC cuando sus elementos constituyentes son etapas biquad universales. En este esquema DfT, durante el modo de funcionamiento normal los biquad realizan el tipo de filtro para el que han sido diseñados (paso bajo, paso alto

o paso banda). En modo de test, las llaves se reconfiguran para provocar la cancelación de polos y ceros manteniendo la información de los parámetros del circuito que determinan su funcionalidad. De este modo todos los biquads del filtro se convierten en etapas de ganancia constante donde salida del último módulo se compara con la esperada para un amplificador de ganancia equivalente (con polaridad opuesta) que se añade al circuito bajo test. La comparación se realiza sumando ambas señales, si el valor difiere de los cero voltios esperados por más de un margen dado el circuito es clasificado como defectuoso.

La principal limitación de este concepto es la dificultad de realizar una cancelación exacta de los polos y ceros, aunque dependiendo de la sensibilidad de los parámetros una cancelación aproximada puede ser efectiva.

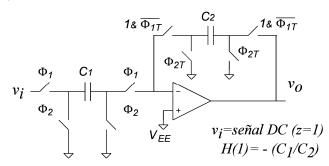

Verificación de los valores de los componentes. Este método se basa en el hecho de que en los circuitos de capacidades conmutas los cocientes de los condensadores son más importantes que sus valores absolutos [Duf97]. El DfT reconfigura los circuitos SC para convertirlos en amplificadores de tensión. Así, en el modo de test, la nueva función de transferencia depende del cociente de dos condensadores y por tanto la medida de la ganancia en continua es sensible a la aparición de defectos en los condensadores. En el integrador, el DfT requiere insertar alguna llave más en el circuito SC para obtener un amplificador conmutado (figura 6.2).

Figura 6.2. Reconfiguración para la verificación de los valores de los componentes

Una idea similar se utiliza para detectar fallos paramétricos tanto en filtros [Vin00] como en un convertidor analógico-digital [Cho04] implementados con circuitos SC. Durante el modo de test, el sistema se reconfigura en un convertidor analógico-digital que mide el cociente entre todos los condensadores del circuito (ADCRC) [Cho00]. La medida se realiza digitalmente y alcanza una precisión de 14 bits equivalente al 0.01%. De este modo se obtiene la función de transferencia de los filtros y las prestaciones estáticas del ADC

Test basado en oscilación. La reconfiguración de los circuitos para dar lugar a un oscilador se ha aplicado a filtros de capacidades conmutadas de alto orden dividiendo el sistema en módulos de segundo orden [Hue02a][Hue02b]. Se utiliza un elemento de realimentación no lineal para convertir al filtro de segundo orden en un oscilador implementado con un comparador con niveles de tensión de salida predefinidos [Hue99]. Esto permite utilizar el parámetro de la amplitud de la oscilación para ayudar a relajar la precisión de la medida de la frecuencia de oscilación.

#### 6.3 MÉTODO DFT PROPUESTO

Dentro de los aspectos de los circuitos analógicos que influyen el estudio del DfT y deben ser tenidos en cuenta a la hora del diseño están:

- 1. La falta de un modelo de fallos adecuado para circuitos analógicos dificulta la validación de la propuesta de test. Por ello, se desarrolla un modelo específico para los circuitos de capacidades conmutadas.

- 2. Los DfT digitales solo necesitan detectar defectos puntuales que se pueden modelar adecuadamente por un modelo de fallos catastrófico. Sin embargo en los circuitos analógicos hay que detectar tanto fallos catastróficos como fallos paramétricos donde la asunción de un fallo simple no siempre es suficiente. Los fallos paramétricos que consideraremos serán desviaciones el los valores absolutos de los condensadores del circuito.

- 3. Las señales analógicas internas del circuito no siempre se pueden transportar hacia una salida fácilmente, por lo cual nuestro DfT realiza un primer procesado de la información dentro del chip proporcionando una tensión analógica que refleja la transferencia de la carga dentro del CUT.

- 4. El DfT debe ser aplicable al mayor conjunto de circuitos de capacidades conmutadas posibles por lo que el método de muestreo debe permitir monitorizar varios nudos del CUT a la vez.

En los circuitos de capacidades conmutadas, el amplificador operacional se combina con llaves y condensadores para completar el repertorio de los componentes necesarios en el procesamiento de la información analógica. En estos circuitos el moviendo de la carga almacenada en los condensadores se establece desde los amplificadores operacionales al nudo de referencia o tierra virtual. Las llaves controladas por varias subfases del reloj del sistema controlan estos movimientos.

El método de test propuesto utiliza la carga suministrada o extraída de la tensión de referencia del circuito SC, para posteriormente analizar si este es defectuosos o no. Por tanto, se necesita un circuito cuya tensión de salida sea proporcional a la carga muestreada. El circuito también tiene que garantizar que la tensión del nudo de muestreo se mantiene a la tensión de referencia o tierra virtual  $V_{EE}$ , con objeto de no perturbar la función analógica del CUT y degradar sus prestaciones lo menos posible.

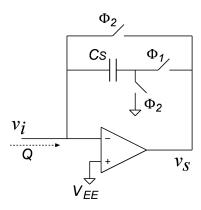

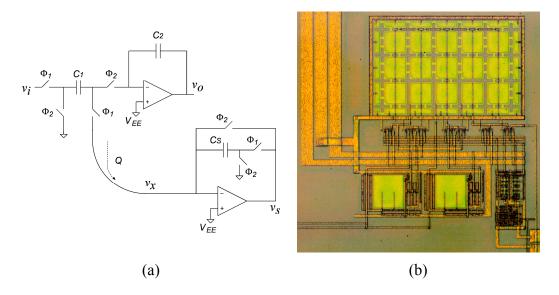

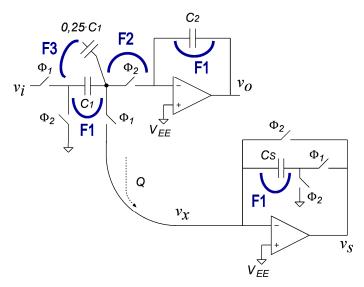

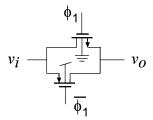

El esquemático del sensor de carga propuesto se muestra en la figura 6.3. Para cada una de las dos fases de reloj se obtiene un circuito equivalente. Durante  $\phi_2$  el amplificador operacional está configurado como un seguidor de tensión, así que el condensador  $C_S$  se descarga y se fuerza la tensión de referencia en el nudo de muestreo  $(v_{in})$ . Durante la otra fase  $(\phi_I)$ , la carga muestreada es almacenada en  $C_S$  manteniendo la tensión del nudo " $v_{in}$ " a la tierra virtual  $V_{EE}$  siempre que el amplificador operacional no se sature.

DfT para Circuitos SC 233

Figura 6.3. Esquemático del sensor de carga

En el circuito libre de fallo, la carga almacenada en el sensor debe estar entre unos límites fijados por los modelos tecnológicos proporcionados por el fabricante del chip.

$$v_s^{NO-defect} \in \left(-\frac{Q_{MIN}^{NO-defect}}{C_S} + V_{EE}, -\frac{Q_{MAX}^{NO-defect}}{C_S} + V_{EE}\right)$$

(1)

Donde  $Q_{MIN}^{NO\_defect}$  y  $Q_{MAX}^{NO\_defect}$  es, respectivamente, la carga mínima y la carga máxima producida en el circuito libre de fallo. Estos límites se utilizan como niveles de detección en la evaluación de fallos, dado que una tensión del sensor fuera de ellos permite la identificación del circuito como defectuoso.

El sensor de carga se utiliza en el método de diseño para test (DfT) para permitir el acceso a los nudos internos de los bloques empotrados dentro de los circuitos integrados. Varios nudos pueden ser muestreados al mismo tiempo y el sensor convertirá la suma de todas las cargas a tensión, acotando así el incremento de área del método de test. Todos los nudos muestreados deben verificar dos condiciones; estar conectados a llaves controladas por la misma subfase de reloj y que las llaves tengan uno de sus extremos conectado a la tierra virtual  $V_{\it EE}$ .

#### 6.4 ESTUDIO DE UN INTEGRADOR SC

El método de test basado en el muestreo de magnitudes internas del chip puede extenderse a los circuitos de capacidades conmutadas. Mientras que para los circuitos continuos la medida de la corriente dinámica permite obtener información sobre el correcto funcionamiento del chip [Lec02], en los circuitos SC el parámetro a monitorizar es la transferencia de carga al nudo de tierra virtual del sistema.

El integrador es uno de los bloques básicos más importantes de los sistemas de procesado. Su principal uso es la realización de filtros activos aunque aparece en muchas otras aplicaciones. El integrador se ha elegido para realizar un primer estudio del método de test basado en el monitorizado de la transferencia de carga en circuitos SC, dado que el reducido número de componentes permite realizar un análisis más sencillo del sensor de carga.

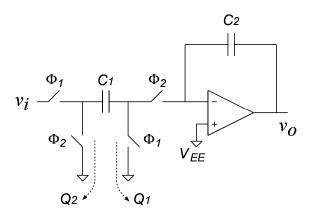

El circuito diseñado es una traslación directa del integrador continuo donde la resistencia se ha sustituido por un condensador y un conjunto de cuatro llaves (figura 6.4).

Figura 6.4. Integrador no inversor paralelo de capacidades conmutadas

Un problema importante en los circuitos SC son las capacidades parásitas de las llaves MOS, de las interconexiones y de las placas superiores e inferiores de los mismos condensadores. El efecto de estas capacidades parasitas es alterar la respuesta en frecuencia del circuito. Para aliviar este problema se utilizan configuraciones de llaves duales de tal modo que todo momento ambos extremos de los condensadores estén conectados bien directamente a la tierra del sistema bien a un nudo de baja impedancia [Mar79].

Suponiendo  $V_{IN}>0$  la placa izquierda del condensador C1 se carga a la tensión de entrada durante la fase de reloj  $\Phi_1$ . Conmutando las llaves en la fase  $\Phi_2$ , C1 se descarga a cero enviando la carga hacia el nudo de tierra virtual  $V_{EE}$ . Por tanto, el circuito es un integrador no inversor paralelo tipo I cuya función de transferencia, magnitud y la fase vienen dadas por la tabla 6.1 [Bru75][Bro79].

| Integrador no inversor paralelo                                | Función de<br>transferencia                               | <b>Magnitud</b> $\left H(e^{j\omega T})\right $                                       | <b>Fase</b> $Arg H(e^{j\omega T})$   |

|----------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------|

| Tipo 1 LDI $H^{oe}$<br>LossLess Discrete<br>Integrator         | $H^{oe}(z) = \frac{C_1}{C_2} \frac{z^{-1/2}}{1 - z^{-1}}$ | $\frac{\omega_0}{\omega} \left( \frac{\omega T_{/2}}{sen \frac{\omega T}{2}} \right)$ | $\frac{\pi}{2}$                      |

| Tipo 1 DDI $H^{oo}$<br>Direct-Transform<br>Discrete Integrator | $H^{oo}(z) = \frac{C_1}{C_2} \frac{z^{-1}}{1 - z^{-1}}$   | $\frac{\omega_0}{\omega} \left( \frac{\omega T/2}{sen \frac{\omega T}{2}} \right)$    | $\frac{\pi}{2} - \frac{\omega T}{2}$ |

Tabla 6.1. Características del integrador SC

La frecuencia de ganancia unidad del integrador SC, asumiendo que la frecuencia de operación es mucho menor que la del reloj  $f \ll f_{clk}$ , viene dada por  $f_o = \frac{1}{2\pi} \frac{C_1}{C_2} f_{clk}$ .

El circuito de prueba utiliza el mismo diseño del amplificador operacional tanto para el integrador como para el sensor de carga y se corresponde con el bloque descrito en el apartado 4.4 de la Tesis. Las llaves están formadas por un transistor NMOS y un transistor PMOS controlados por la misma fase de reloj pero con polaridades opuestas. El módulo

DfT para Circuitos SC 235

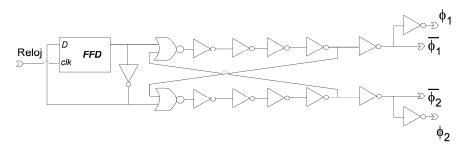

digital que genera las fases de reloj no solapadas es una estructura clásica basada en el retraso de propagación de la señal a través de una cadena de inversores (figura 6.5).

Figura 6.5. Circuito digital para generar las fases de reloj no solapadas

En el integrador hay dos llaves que envían la carga (Q1 y Q2) la nudo de referencia ( $V_{EE}$ ). Esta carga puede ser utilizada como parámetro para detectar el funcionamiento defectuoso del CUT. El sensor de carga se ha acoplado a la llave controlada por la fase  $\Phi_1$  dado que al estar más próxima al amplificador operacional permite monitorizar mejor su comportamiento.

La figura 6.6 muestra el esquemático final del circuito y una fotografía del chip resultante. El circuito ha sido fabricado utilizando la tecnología de pozo N de Austria Micro Systems 0.6μm [Moz04a].

Figura 6.6. Integrador SC con el sensor de carga (a) esquemático (b) fotografía del chip

La disposición de los bloques muestra dos amplificadores de transconductancia en la parte inferior, uno forma parte del integrador y el otro del sensor de carga. En la parte superior se encuentran quince condensadores de tamaño unitario rodeados de elementos dummy para mejorar su emparejamiento, trece condensadores conectados en paralelo, de un picofaradio cada uno, constituyen la capacidad de realimentación del integrador C2 y se utiliza un elemento capacitivo tanto para el condensador del integrador C1 como para la capacidad de muestreo del sensor de carga CS. Las llaves están situadas entre los condensadores y los amplificadores de transconductancia. En un extremo inferior izquierdo se encuentra el circuito encargado de generar las fases de reloj.

Considerando que el amplificador operacional se comporta como un bloque ideal y despreciando el efecto de las capacidades parasitas, el circuito sensor convierte la carga en tensión de acuerdo a la ecuación (5)

$$v_{s} = -\frac{1}{C_{S}} \cdot \int_{\phi 1} I_{DD} \cdot dt + V_{EE} = -\frac{Q}{C_{S}} + V_{EE}$$

(2)

El condensador CS debe ser elegido cuidadosamente para prevenir la saturación del amplificador operacional durante el modo de funcionamiento normal del CUT.

#### 6.4.1 Influencia del sensor de carga en el CUT

Las no idealidades del amplificador operacional pueden afectar tanto a las prestaciones del CUT como a las del sensor de carga. Para una ganancia de lazo abierto A y una tensión de offset  $V_{offset}$ , la tensión en el nudo de muestreo en vez de permanecer en  $V_{EE}$ , se degrada de acuerdo a (3)

$$v_x = \frac{A}{1+A} \cdot V_{EE} + V_{offset} - \frac{Q}{(1+A) \cdot C_S}$$

(3)

Mientras que la tensión a la salida del sensor es

$$v_s = \frac{A}{1+A} \cdot V_{EE} + V_{offset} - \frac{A \cdot Q}{(1+A) \cdot C_S}$$

(4)

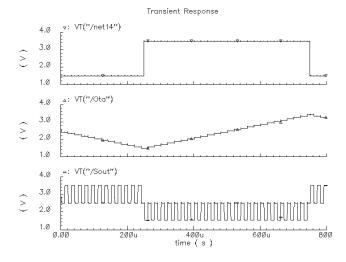

Figura 6.7. Simulación del integrador con el sensor de carga

La figura 6.7 muestra la simulación de la respuesta del integrador a un pulso de tensión en la entrada proporcionando una salida triangular cuya pendiente viene dada por la relación de los condensadores del integrador y el periodo de la señal de reloj (T). A partir de la función de transferencia del circuito:

$$\frac{v_o}{v_i}(w) = \frac{C_1}{C_2} \frac{e^{-jT/2}}{j \cdot w \cdot T} \tag{5}$$

El valor de la pendiente de la señal de salida viene dado por la ecuación

237

Pendiente =

$$\frac{C_1}{C_2} \frac{1}{T} v_i = \frac{1pF}{13pF} \cdot \frac{1}{20us} \cdot 1V = 3846 \frac{V}{s}$$

(6)

Siendo la amplitud de la salida del sensor de carga igual a

$$v_s = -\frac{Q}{C_S} + V_{EE} = \frac{(v_i - V_{EE}) \cdot C_1}{C_S} + V_{EE} = 3.5V \leftrightarrow 1.5V$$

(7)

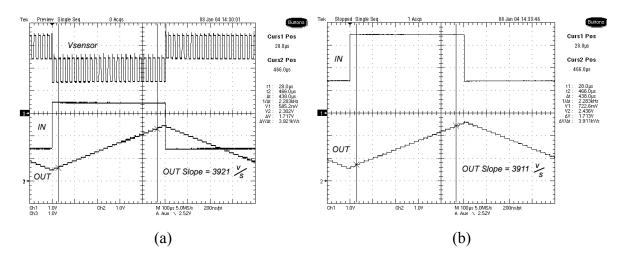

Valores que coinciden con los datos obtenidos experimentalmente según mostrados en la figura 6.8a.

Figura 6.8. (a) Medidas del la salida del integrador y del sensor de carga (b) Salida del integrador fabricado sin el sensor de carga

El efecto del sensor sobre las prestaciones del integrador es muy pequeño, como se puede comprobar a través del valor de la pendiente de salida obtenida de otro circuito integrador fabricado sin incluir el sensor de carga (figura 6.8b). Las medidas, realizadas en las mismas condiciones que en la figura 6a, muestran una mínima diferencia en la pendiente de salida de ambos circuitos.

La presencia del sensor de carga degrada ligeramente la relación señal-ruido a la salida del integrador. Lo cual se comprueba, al aplicar a la entrada del integrador una señal sinusoidal y analizar la señal de salida, que también es otra señal sinusoidal con un desfase de 90 grados, dado que

$$v_o(t) = -\frac{C_1}{C_2} \frac{1}{T} \int v_i(t) \cdot dt = -\frac{C_1}{C_2} \frac{1}{T} \int A \cdot sen(\omega t) \cdot dt = \frac{A \cdot C_1}{C_2 \cdot T \cdot \omega} \cos(wt)$$

(8)

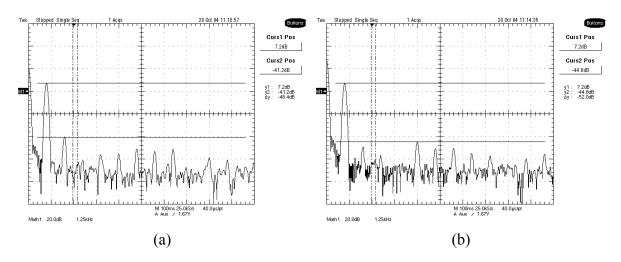

El margen dinámico libre de espurios o armónicos (SFDR) disminuye desde los 52 dB para el circuito integrador sólo hasta los 48 dB cuando el sensor de carga está realizando el test junto a él, como se muestra en la figura 6.9.

Figura 6.9. Espectro de la salida del integrador SC para una entrada sinusoidal con fin=1kHz y fclock=100kHz: (a) Chip con el sensor de carga, (b) Chip sin el sensor de carga

#### 6.4.2 Detección de fallos

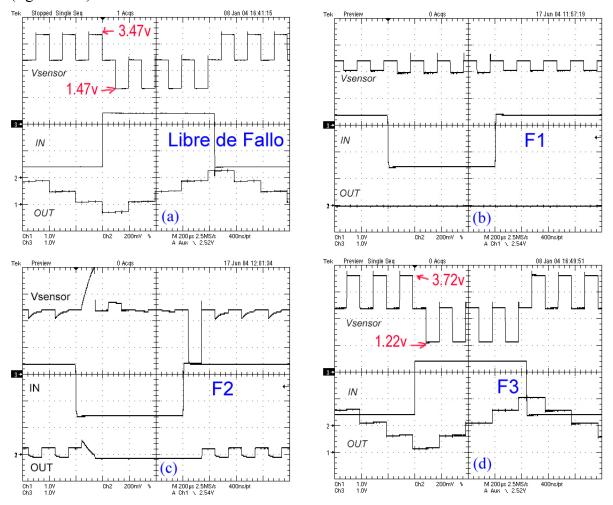

Para analizar la viabilidad del sensor de carga como herramienta de detección de circuitos defectuosos se ha fabricado un chip donde es posible inyectar tres tipos de fallos en el integrador SC, seleccionando uno de ellos cada vez, a través de un multiplexor analógico [Moz04b].

Figura 6.10. Fallos insertados en el integrador SC y en el sensor de carga

Estos fallos son (figura 6.10);

- 1. F1: Fallo que cortocircuita todos los condensadores del integrador y del sensor de carga.

- 2. F2: Cortocircuito de la llave conectada a la entrada inversora del amplificador operacional y controlada por la fase  $\Phi_2$ .

- 3. F3: Desviación de un 25% en el valor del condensador C1.

DfT para Circuitos SC 239

Las medidas realizadas muestran que todos los defectos son detectables por el sensor de carga (figura 6.11).

Figura 6.11. Detección de fallos (a) Circuito libre de fallo (b) Integrador con F1 (c) Integrador con F2 (d) Integrador con F3

Los fallos catastróficos son fácilmente detectables por el sensor, como el cortocircuito entre los condensadores (F1) y el corto entre los extremos de la llave (F2). En ambos casos la forma de onda de la salida del sensor se desvía fuertemente del valor esperado para el circuito libre de fallo.

También el fallo paramétrico (F3) consistente en la desviación del valor nominal del condensador C1 se puede detectar. Mientras que en el circuito libre de fallo (figura 6.11a) la salida del sensor es una señal que abarca entre 1.47 voltios y 3.47 voltios, la habilitación del defecto aumenta su amplitud un 25% hasta obtener tensiones entre 1.22 voltios y 3.72 voltios (figura 6.11d).

#### 6.5 ANÁLISIS DE UN CONVERTIDOR ADC ALGORÍTMICO SC

Con objeto de estudiar la viabilidad de la aplicación del sensor de carga a un circuito SC más complejo se ha realizado un análisis por simulación de un convertidor analógico-digital.

#### 6.5.1 Descripción del CUT

El ADC algorítmico elegido es un sistema compacto que requiere un área pequeño y un consumo de potencia bajo puesto que realiza la conversión de forma serie haciendo uso repetido de un bloque sencillo [Mcc77]. La principal desventaja de esta estructura es la baja velocidad de conversión al necesitar "n" pulsos de reloj para obtener una salida digital de "n" bits de resolución.

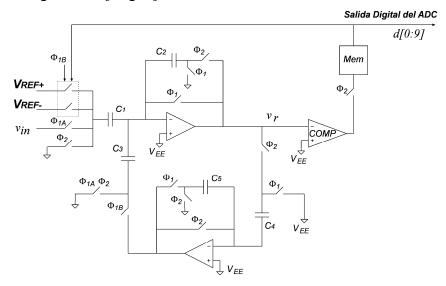

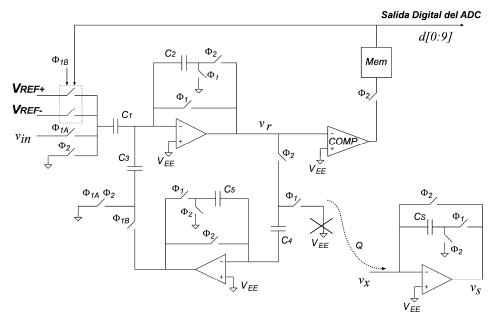

Una versión simplificada del esquemático utilizando la tecnología de capacidades conmutadas se muestra en la figura 6.12 [Nag93].

Figura 6.12. Esquemático del ADC algorítmico

El circuito está formado por una unidad aritmética, una etapa de muestreo y retención, un comparador de tensión y un bit de memoria. La unidad aritmética es capaz de multiplicar una tensión analógica por dos y a la vez sumarla a una tensión de referencia.

Se han publicado diversas técnicas para minimizar la influencia de las no-idealidades de los componentes del convertidor como el desacoplo de los condensadores, la tensión de offset del comparador, la ganancia finita del amplificador operacional y la inyección de carga debido a la conmutación de las llaves [Ono88][Son88][Tsu93]. Sin embargo, el diseño del ADC de prueba se ha mantenido lo más sencillo posible para poder realizar un mejor análisis de las prestaciones del sensor de carga.

La conversión del ADC comienza con la unidad aritmética muestreando la tensión de entrada y dando lugar a una tensión de salida  $v_r(0)$  igual a  $v_{in}$ , la cual se evalúa respecto al nivel de referencia del comparador  $V_{EE}$  para decidir el bit más significativo (MSB). Al mismo tiempo la salida de la unidad aritmética es almacenada en la etapa de muestreo y retención. En el segundo ciclo de reloj, el módulo de muestreo y retención alimenta la unidad aritmética con el residuo del primer ciclo  $v_r(0)$ , el cual se multiplica por dos y se le añade la tensión de referencia mayor  $V_{REF+}$  o la tensión de referencia menor  $V_{REF-}$  dependiendo del valor del MSB. El resultado es un nuevo residuo  $v_r(1)$  que se compara con  $V_{EE}$  para codificar el siguiente bit. Este proceso se repite una vez para cada bit de resolución del convertidor.

En términos generales, el algoritmo de conversión viene dado por:

$$v_r(n+1) = 2 \cdot v_r(n) - V_{REF}(n+1)$$

(9)

Donde  $v_r(0) = v_{in}$  y

$$V_{REF}(n+1) = \begin{cases} V_{REF+} & \text{if} \quad d(n) = 1\\ V_{REF-} & \text{if} \quad d(n) = 0 \end{cases}$$

(10)

La salida digital del ADC se construye de acuerdo a

$$d(n) = \begin{cases} 1 & if \quad v_r(n) \ge V_{EE} \\ 0 & if \quad v_r(n) < V_{EE} \end{cases}$$

$$\tag{11}$$

Siendo,  $V_{EE}$  la tensión de referencia o tierra virtual cuyo valor es igual a

$$V_{EE} = \frac{(V_{REF+} + V_{REF-})}{2}$$

(12)

La salida del convertidor es una secuencia serie de bits comenzando con d(0) (MSB).

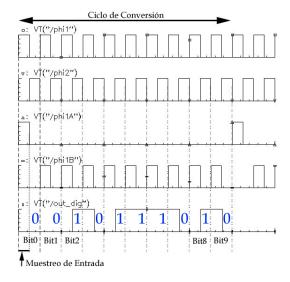

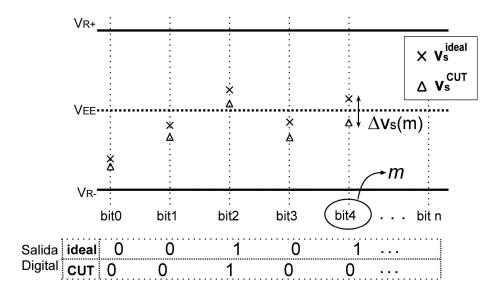

Figura 6.13. Secuencia temporal de un ADC de 10 bits. El Bit0 es el MSB y el Bit9 el LSB

La secuencia temporal de la conversión se muestra en la figura 6.13. Phi1  $(\phi_1)$  y phi2  $(\phi_2)$  constituyen los relojes no solapados que controlan al operación del ADC. Las fases phi1A  $(\phi_{1A})$  y phi1B  $(\phi_{1B})$  son subconjunto de los relojes básicos. La entrada es muestreada durante  $\phi_{1A}$  y los bits del ADC son codificados durante  $\phi_2$ . Durante los pulsos phi1B  $(\phi_{1B})$  la unidad aritmética procesa la tensión de residuo almacenada en la etapa de muestreo y retención.

#### 6.5.2 Acoplo del sensor de carga

El punto de muestreo escogido para el sensor de carga se muestra en la figura 6.14. Está localizado entre la salida de la unidad aritmética y la entrada de la etapa de muestreo y retención. Este nudo es el más sensible del ADC dado que la capacidad almacenada en el condensador C4, es el parámetro utilizado para decidir si la salida digital es "0" o "1", se transfiere directamente al sensor de carga [Moz04a].

Figura 6.14. Esquemático del ADC algorítmico con el sensor de carga

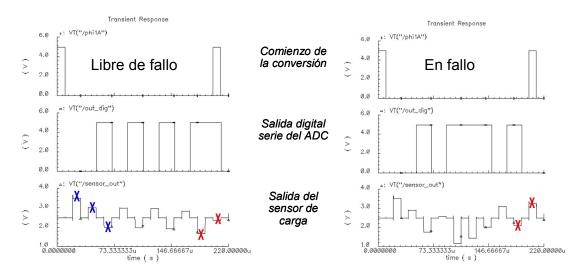

La figura 6.15a muestra la simulación del ADC llevando a cabo una conversión de diez bits de una entrada cuya tensión es 1.5V. Dado que las tensiones de referencia  $V_{REF+}$  y  $V_{REF-}$  son 4V y 1V respectivamente, el nivel de decisión utilizado por el comparador ( $V_{EE}$ ) se establece en 2.5V. El código digital de salida se corresponde con "0010101011" (171 en decimal).

Figura 6.15. Simulación de la salida digital del ADC y la salida analógica del sensor de carga para (a) circuito libre de fallo (b) desviación en C3

La figura 6.15a también ilustra el método de test utilizado para detectar fallos en el CUT analizando la salida del sensor de carga. La señal phi1A ( $\phi_{1A}$ ) marca el inicio de la conversión, "Out\_dig" es la salida del elemento de memoria del ADC y "Sensor\_out" es la salida analógica del sensor de carga. Durante la subfase  $\phi_2$  la salida del sensor se mantiene a la tierra virtual de sistema  $V_{EE}$ . Es durante la fase  $\phi_1$  que la salida del sensor proporciona información sobre si el CUT es defectuoso o no. Con las diez tensiones de salida del sensor de

carga correspondientes a los diez bits de la conversión se puede establecer una firma para el circuito libre de fallo (6.15a). La figura 6.15b muestra el comportamiento del ADC cuando se introduce una desviación del 10% en un condensador de la unidad aritmética. El cambio en la salida del sensor permite la detección de este fallo.

#### 6.5.3 Influencia del sensor de carga en el ADC

La integración del sensor de carga junto al CUT tiene una pequeña influencia en las prestaciones del ADC. La figura 6.16 muestra la simulación del convertidor con y sin el sensor de carga. Se puede observar una variación de un LSB en el bit quince de la conversión cuando se compara el ADC con el sensor de carga (señal "out\_dig\_sen") frente al ADC sólo (señal "out\_dig").

Figura 6.16. Influencia del sensor de carga en la resolución del ADC

#### 6.5.4 Salida del sensor de carga vs. INL del ADC

Es posible establecer una relación entre la No-Linealidad Integral (INL) y la no-Linealidad Diferencial (DNL) del convertidor con el voltaje de salida del sensor de carga. Esta relación es de gran interés cuando no aparecen errores lógicos en la salida digital del ADC o estos errores son pequeños, debido a que el sensor de carga permite una caracterización precisa de las prestaciones del ADC.

En el esquemático del convertidor mostrado en la figura 6.14, durante la subfase de reloj  $\phi_2$ , la tensión a la salida de la unidad aritmética almacena la carga del condensador C4 de acuerdo a (13)

$$v_r(n) = -\frac{Q}{C_A} + V_{EE} \tag{13}$$

En la subfase  $\phi_1$ , el condensador C4 se descarga y la carga se transmite al sensor. Esto relaciona la salida del sensor con la unidad aritmética según (14),

$$v_s(n) = \left(V_{EE} - \frac{Q}{C_s} \cdot v_r(n)\right) + V_{EE}$$

(14)

La codificación de la salida del ADC se puede obtener del sensor de carga a través de (15)

$$d(n) = \begin{cases} 1 & if \quad v_s^{CUT}(n) < V_{EE} \\ 0 & if \quad v_s^{CUT}(n) \ge V_{EE} \end{cases}$$

$$(15)$$

La desviación entre la salida del sensor del CUT analizado y la esperada para el ADC ideal se puede obtener en función del error entre el valor actual de la tensión de la unidad aritmética y su valor esperado para el caso ideal de la ecuación (16)

$$\Delta v_s(n) = v_s^{CUT}(n) - v_s^{ideal}(n) = -\frac{C_4}{C_S} \cdot \Delta v_r(n)$$

(16)

La linealidad del ADC se obtiene cuantificando los efectos que las no-idealidades que los bloques del ADC introducen en la tensión de entrada. Estas imperfecciones se reflejan en cambios en el voltaje de residuo que puede ser calculado a partir del algoritmo de conversión (9).

$$\Delta v_r(n) = 2^{n-1} \cdot \Delta v_{in} \tag{17}$$

El INL se define como la desviación de la tensión de entrada frente a su caso ideal en unidades LSB donde el bit menos significativo viene dado por el rango de tensión de entrada dividido por el número de pasos del convertidor. Por tanto, el INL se puede obtener de la variación de la tensión de salida del sensor de carga mostrada en (16)

$$INL = -\frac{v_s^{CUT}(NBIT) - v_s^{ideal}(NBIT)}{\frac{V_{REF+} - V_{REF-}}{2}}$$

(18)

Donde NBIT es la resolución del convertidor A/D en bits,  $\left(V_{REF+} - V_{REF-}\right)$  es el rango total de entrada, y se utiliza en el sensor de carga  $C_S = C_4$ . La ecuación (18) describe la linealidad del ADC donde la precisión de los comparadores y las etapas de ganancia equivalen a un error en la entrada inferior a un LSB. En este caso la tensión de la unidad aritmética (residuo) en la codificación del último bit es inferior al rango de entrada del comparador y puede ser corregido con un simple circuito digital que añada o reste un bit [Had92]. Un defecto del proceso de fabricación puede dar lugar a un mayor error en los bloques del convertidor llevando los amplificadores operacionales de la unidad aritmética y del circuito de muestreo y retención a saturación, por tanto una expresión más general de la ecuación (18) sería:

$$INL = \frac{v_s^{CUT}(m) - v_s^{ideal}(m)}{\frac{V_{REF+} - V_{REF-}}{2}} \cdot 2^{NBIT-m}$$

(19)

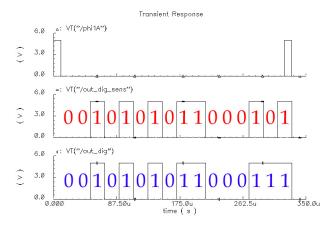

Donde "m" es el bit más significativo en el cual la salida digital del ADC se desvía del valor esperado para el convertidor ideal. Es decir,  $v_s^{CUT}(m)$  es la salida del sensor para la primera etapa de conversión localizada en el lado opuesto de la tensión de referencia  $V_{EE}$  que el esperado para la tensión ideal  $v_s^{ideal}(m)$ . El proceso se ilustra en la figura 6.17.

DfT para Circuitos SC 245

Figura. 6.17. Identificación del parámetro "m" a través del procesado de la salida del sensor de carga para (X) ADC bajo test ( $\Delta$ ) ADC ideal

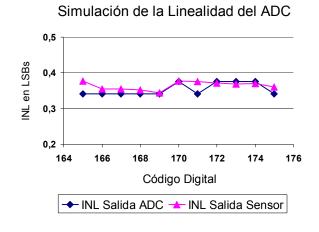

Para verificar la ecuación (19) se ha llevado a cabo un experimento consistente en estimar la no-linealidad integral del ADC por medio del código digital (INL Salida ADC) y la obtenida a través del sensor de carga (INL Salida Sensor). El resultado se muestra en la figura 6.18.

Figura 6.18. INL obtenido de la salida digital del ADC y de salida analógica del sensor de carga

En esta simulación, primero, se obtienen las tensiones de entrada donde se producen transiciones para cada código de salida considerando un ADC ideal de diez bits. A estas tensiones se les denomina  $v_{in}^{ideal}(code)$  donde el código varía desde 0 hasta  $2^{\text{NBIT}}$ -1. Se logra aplicando un barrido de la tensión de entrada al ADC donde la salida se codifica a partir del algoritmo ideal de conversión.

Para cada  $v_{in}^{ideal}(code)$ , se obtiene el conjunto de tensiones de salida del sensor de carga a partir de la ecuación (16) dando lugar a un conjunto de tensiones analógicas  $v_s^{ideal}[code, n]$  con "n" variando desde 0 hasta NBIT-1.

La curva "INL Salida ADC" se obtiene simulando un nuevo barrido de la tensión de entrada para la descripción eléctrica (SPICE) del ADC utilizado como circuito bajo test, para encontrar las tensiones que producen las transiciones de los códigos digitales de salida  $v_{in}^{CUT}(code)$ . Estos valores se comparan con los esperados para el convertidor ideal y las desviaciones se dibujan en el gráfico.

Los datos de la curva "INL Salida Sensor" se calculan de la ecuación (19) tomando como  $v_s^{CUT}[code, n]$  la salida del sensor de carga integrado junto al CUT y simulado para los valores  $v_{in}^{ideal}(code)$ .

Como se puede apreciar en el gráfico 6.18 ambas curvas son iguales. Por tanto, la salida del sensor de carga permite caracterizar algunas de las prestaciones del convertidor. La ventaja de este nuevo método es que sólo es necesario medir para valores discretos de la tensión de entrada  $v_{in}^{ideal}(code)$ , en vez de hacer un barrido para encontrar  $v_{in}^{CUT}(code)$ , acortando el tiempo de test.

#### 6.5.5 Evaluación de Fallos

El DfT propuesto se ha evaluado como un test estructural. El test estructural requiere modelos de fallos que describan con precisión los posibles defectos que aparecen en el proceso de fabricación para poder analizar la viabilidad del método de test.

Se ha considerado un modelo de fallos catastrófico [Mil89] que incluye cortocircuitos entre la puerta, drenador y fuente de los transistores, junto con circuitos abiertos en los contactos de los terminales de fuente y drenador. También se ha incluido el circuito abierto de puerta dado que es el fallo con mayor probabilidad de aparecer de todos los circuitos abiertos [Xue94].

Los cortocircuitos se han modelado como resistencias de  $100\Omega$  mientras que los circuitos abiertos con una resistencia de  $10M\Omega$  en paralelo con un condensador de 1fF. Aunque en [Cha94][Aru08] se ha demostrado que los fallos de circuito abierto de puerta dependen fuertemente de la tecnología y de la topología del layout del circuito, este modelo ampliamente utilizado facilita la convergencia del simulador eléctrico y sus resultados repetitivos permiten evaluar la eficiencia del método de test propuesto.

Los fallos inyectados en los diferentes bloques del ADC son:

1. Cuatro fallos por condensador. Dado que los condensadores ocupan un gran porcentaje del layout de los circuitos de capacidades conmutadas, es razonable asumir que un gran porcentaje de los defectos puede aparecer en ellos. Los fallos que dan lugar los defectos en los condensadores se pueden agrupar en tres categorías: cortocircuitos, circuitos abiertos y variaciones paramétricas. Un corto es causado principalmente por un agujero en el oxido entre las dos placas del condensador o por cortocircuitos entre las líneas de conexión. Los circuitos abiertos se pueden deber a errores en las máscaras que resultan en la perdida de contactos en la placa superior.

Las variaciones paramétricas del valor de capacidad pueden ser debidas a cambios locales en la anchura del oxido, errores de grabado o ruptura de las interconexiones en los elementos unitarios que forman el condensador. Por tanto, además de los fallos de circuito abierto y cortocircuito entre sus terminales, se han considerado variaciones positivas y negativas del diez por ciento de su capacidad nominal.

2. Seis fallos por cada llave CMOS (figura 6.20). Los cuales consisten en un circuito abierto entre los terminales de entrada y salida de la llave y cinco cortocircuitos entre la entrada, salida, señal de control y señal de control invertida.

Figura 6.20. Esquemático de las llaves del ADC

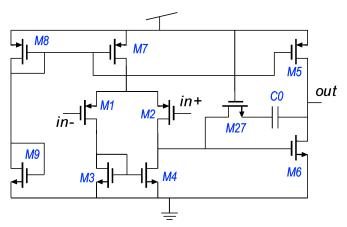

3. Para cada amplificador operacional del ADC (figura 6.21), se utiliza un modelo de fallos a nivel de transistor que consta de diecisiete cortocircuitos y veintiséis circuitos abiertos.

Figura 6.21. Esquemático del amplificador operacional del ADC

Los fallos se consideran detectados cuando inducen una variación a la salida del sensor mayor que 50 milivoltios respecto a la tensión esperada para el circuito libre de fallo. Este límite permite tener en cuenta el efecto de la dispersión de los parámetros de fabricación y la resolución de la medida.

El efecto de los fallos también se analiza por medio de su influencia en la salida digital del ADC con objeto de comparar la bondad del método de test propuesto con respecto a otro test más tradicional. En este caso el fallo se considera detectado si existe una variación mayor o igual que un bit (1 LSB) en la palabra de salida del convertidor.

Como vector de test para llevar a cabo el análisis estructural se utiliza una señal de continua de  $v_{in} = 1.5V$ . Debido a la estructura algorítmica del convertidor, los diferentes bloques son excitados con un amplio rango de tensiones durante las sucesivas etapas de la conversión.

#### 6.5.5.1 Simulación de fallos de los condensadores del ADC

Cada fila de la tabla 6.2 se corresponde con una simulación de un fallo en uno de los condensadores del convertidor, excepto la primera y última fila que se corresponden con el circuito libre de fallos y cuyos valores son utilizados como referencia.

En la parte izquierda se encuentran los resultados para los sucesivos valores de los 8 bits más significativos de la salida digital del ADC, cuando la desviación respecto al libre de fallo "00101010" es mayor de un LSB el dato se muestra en rojo y el circuito se clasifica como defectuoso. En la parte derecha se muestran los sucesivos valores de tensión obtenidos en la simulación SPICE para la salida analógica del sensor de carga. El dato se resalta cuando la desviación respecto al valor esperado es mayor que 50 milivoltios y el convertidor se considera defectuoso con que diverja uno solo de los datos analógicos.

| Fallos catastróficos en los condensadores del ADC algoritmico SC |      |                     |      |   |      |      |      |      |                              |       |       |       |       |       |       |       |

|------------------------------------------------------------------|------|---------------------|------|---|------|------|------|------|------------------------------|-------|-------|-------|-------|-------|-------|-------|

|                                                                  |      | Nivel de detección= |      |   |      | 1    | LSB  |      | Tensión umbral de detección= |       |       |       | 0,050 | V     |       |       |

| fallo                                                            | bit0 | bit1                | bit2 |   | bit4 | bit5 | bit6 | bit7 | sen0                         | sen1  | sen2  | sen3  | sen4  | sen5  | sen6  | sen7  |

| Libre de fallo                                                   | 0    | 0                   | _    |   | 5    | 0    | 5    | 0    | 3,504                        | 3,007 | 2,012 | 3,033 | 2,064 | 3,136 | 2,271 | 3,550 |

| d+10%_c1                                                         | 0    | _                   |      | 0 | 5    | 0    | 5    | 0    | 3,604                        | 3,057 | 1,961 | 3,082 | 2,012 | 3,183 | 2,213 |       |

| d-10%_c1                                                         | 0    | _                   | _    |   | 5    | 0    | 5    | 0    | 3,404                        | 2,957 | 2,062 | 2,983 | 2,114 | 3,086 | 2,321 |       |

| short_c1                                                         | 0    | _                   | _    | _ | 0    | 0    | 0    | 0    | 0,000                        | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 |       |

| open_c1                                                          | 0    | 0                   | 0    | 0 | 0    | 0    | 0    | 0    | 2,501                        | 2,505 | 2,514 | 2,531 | 2,565 | 2,633 | 2,770 |       |

| d+10%_c2                                                         | 0    | 0                   |      | 5 | 5    | 5    | 5    | 5    | 3,504                        | 3,208 | 2,555 | 1,120 | 0,975 | 0,655 | 0,002 | 0,005 |

| d-10%_c2                                                         | 0    | 0                   | 5    | 5 | 0    | 0    | 5    |      | 3,504                        | 2,806 | 1,549 | 2,296 | 3,641 | 3,053 | 1,993 | 3,095 |

| short_c2                                                         | 0    | 0                   |      | 0 | 0    | 0    | 0    | 0    | 0,000                        | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 |       |

| open_c2                                                          | 0    | 5                   |      | 5 | 0    | 5    | 0    | 5    | 3,504                        | 0,996 | 4,004 | 0,996 | 4,004 | 0,996 | 4,004 | 0,996 |

| d+10%_c3                                                         | 0    | 0                   | ·    | 5 | 0    | 0    | 5    | 0    | 3,413                        | 2,795 | 1,671 | 2,364 | 3,624 | 3,178 | 2,368 |       |

| d-10%_c3                                                         | 0    |                     |      | 5 | 5    | 5    | 5    | 5    | 3,616                        | 3,311 | 2,634 | 1,128 | 1,129 | 1,130 | 1,134 | 1,143 |

| short_c3                                                         | 0    | 0                   | 0    | 0 | 0    | 0    | 0    | 0    | 0,000                        | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 | 0,000 |       |

| open_c3                                                          | 0    |                     |      | 0 | 0    | 0    | 0    | 0    | 4,994                        | 4,994 | 4,994 | 4,994 | 4,994 | 4,994 | 4,994 | 4,993 |

| d+10%_c4                                                         | 0    | 0                   | 0    | 5 | 5    | 5    | 5    | 5    | 3,604                        | 3,278 | 2,561 | 0,982 | 0,822 | 0,470 | 0,001 | 0,001 |

| d-10%_c4                                                         | 0    | 0                   |      | 5 | 0    | 0    | 5    | 0    | 3,404                        | 2,775 | 1,644 | 2,317 | 3,528 | 2,999 | 2,047 | 3,043 |

| short_c4                                                         | 0    | 5                   |      | 5 | 0    | 5    | 0    | 5    | 1,984                        | 4,409 | 0,985 | 4,468 | 0,985 | 4,468 | 0,985 |       |

| open_c4                                                          | 0    | 5                   |      | 5 | 0    | 5    | 0    | 5    | 2,501                        | 2,498 | 2,502 | 2,498 | 2,502 | 2,498 | 2,502 |       |

| d+10%_c5                                                         | 0    |                     |      | 5 | 0    | 0    | 5    | 0    | 3,504                        | 2,824 | 1,587 | 2,349 | 3,733 | 3,240 | 2,344 | 3,724 |

| d-10%_c5                                                         | 0    | 0                   | 0    | 5 | 5    | 5    | 5    | 5    | 3,504                        | 3,230 | 2,621 | 1,268 | 1,273 | 1,283 | 1,305 |       |

| short_c5                                                         | 0    |                     |      | 5 | 0    | 5    | 0    | 5    | 1,984                        | 4,409 | 0,985 | 4,468 | 0,985 | 4,468 | 0,985 |       |

| open_c5                                                          | 0    | 0                   |      | 0 | 0    | 0    | 0    | 0    | 2,528                        | 2,637 | 2,637 | 2,637 | 2,636 | 2,637 | 2,637 | 2,637 |

| Libre de fallo                                                   | 0    | 0                   | 5    | 0 | 5    | 0    | 5    | 0    | 3,504                        | 3,007 | 2,012 | 3,033 | 2,064 | 3,137 | 2,272 | 3,552 |

Tabla 6.2. Simulación considerando fallos en los condensadores del ADC

Se aprecia que el sensor de carga detecta todos los fallos inyectados en los condensadores dado que producen una variación mayor que el nivel umbral fijado en 50 milivoltios en alguno de los valores de la tensión de salida del sensor que constituye la firma del circuito bajo test.

Sin embargo, los fallos que modelan una variación del 10% del condensador C1 conectado a la entrada del convertidor, no inducen ningún cambio en la palabra digital de salida del ADC. Esto es debido a que cambia en la misma proporción las tensiones de referencia del ADC ( $V_{REF+}$  y  $V_{REF-}$ ) y su entrada analógica ( $v_{in}$ ). Este fallo degrada las prestaciones del convertidor dado que afecta al rango de salida del amplificador operacional de la unidad aritmética y es detectable a través de la variación en la tensión de salida del sensor de carga cuando se está codificando el bit más significativo.

#### 6.5.5.2 Simulación de fallos de las llaves del ADC

De los 81 fallos simulados en las llaves del convertidor, el sensor de carga detecta todos excepto uno. Este cortocircuito entre la salida del elemento de memoria digital y la tierra virtual convierte a la llave CMOS en una llave NMOS. El fallo tampoco es detectable a través de la salida digital del ADC.

Hay otros cuatro fallos que no afectan a la palabra de salida del ADC. Todos ellos son cortocircuitos entre la entrada y salida de llaves conectadas a la salida de un amplificador operacional. Los fallos solo podrían ser detectados durante la subfase de reloj que abre las llaves afectadas. Sin embargo, debido al diseño del circuito, en esta subfase ambos extremos de las llaves están a la misma tensión, Por tanto, los cien ohmios que modelan el fallo ni afectan a la funcionalidad de circuito ni se reflejan en los diez bits de resolución del ADC. Esta degradación del comportamiento del ADC se puede observar por medio del sensor de carga.

#### 6.5.5.3 Simulación de fallos de los amplificadores operacionales del ADC

Todos los fallos de cortocircuito simulados en cada amplificador operacional se detectan por medio del sensor de carga, mientras que la salida del ADC no detecta uno de ellos (cortocircuito drenador fuente del transistor M9). Es un cortocircuito que modifica la corriente de polarización del amplificador degradando su respuesta en frecuencia.

Entre todos los fallos de circuito abierto simulados en cada amplificador operacional, el sensor de carga no detecta cinco de ellos. Los fallos son circuitos abiertos de puerta de transistores cuya tensión no varía con el tiempo. Como el fallo de circuito abierto se modela con una resistencia de  $10~\text{M}\Omega$ , la tensión de polarización del transistor no se ve afectada. Tampoco la salida digital del convertidor es sensible a estos fallos. Además, hay otros dos fallos de circuito abierto que no afectan a los diez bits de salida del ADC pero son detectables por el sensor de carga.

## Cobertura de fallos del ADC algoritmico SC

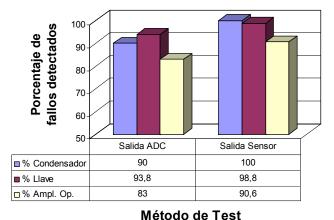

Figura 6.22. Cobertura de fallos del ADC algorítmico obtenida por medio de la salida del ADC y la salida del sensor de carga

La gráfica 6.22 resume las figuras de cobertura. Las columnas "Salida ADC" corresponden al estudio del efecto de los fallos en la salida digital del convertidor, mientras que las columnas marcadas con "Salida Sensor" hacen referencia a la detección mediante el análisis de la salida del sensor de carga.

La fila "Condensador" hace referencia a las simulaciones donde los fallos se han inyectado en los condensadores del convertidor. La fila "Llave" considera los fallos incluidos en las llaves del CUT y la última fila "Amp. Op." toma en cuenta los fallos en los dos amplificadores operacionales del ADC.

El sensor de carga no sólo detecta todos los fallos que generan códigos erróneos en el convertidor algorítmico, sino que también permite detectar algunos otros fallos que, aunque no producen un error lógico, degradan prestaciones del ADC tales como la no-linealidad integral (INL), la no-linealidad diferencia (DNL), el tiempo de asentamiento, el consumo de corriente, etc.

#### 6.6 CONCLUSIONES

En este capítulo se presenta un módulo que permite muestrear y procesar la transferencia de carga dentro de los circuitos de capacidades conmutadas con objeto de proporcionar un indicador del correcto funcionamiento del circuito bajo test.

El sensor de carga se ha diseñado y fabricado junto a un integrador inversor paralelo para caracterizar su comportamiento y se ha podido comprobar que la inclusión del sensor tiene una influencia mínima en las prestaciones del circuito bajo test. En el mismo chip se ha integrado un sistema que permite habilitar tres fallos en el integrador bajo test para observar la respuesta del sensor a cada uno de ellos.

Este método de test estructural se ha estudiado realizando una simulación de fallos sobre un convertidor analógico-digital algorítmico. Se utiliza un modelo de fallos catastrófico a nivel de transistor que incluye cortocircuitos, circuitos abiertos y desviaciones en las capacidades del ADC [Moz03][Moz04b][Moz05].

La aproximación de test propuesta se ha comparado con un test más tradicional como es el análisis de la palabra de salida digital del convertidor. Se ha comprobado que la cobertura de fallos obtenida de la salida del sensor de carga es ligeramente mayor que la del test funcional.

También, se ha estudiado un método para relacionar el conjunto de tensiones que aparecen a la salida del sensor de carga durante el proceso de conversión con una de las prestaciones estáticas del ADC como es la no-linealidad integral.

#### **BIBLIOGRAFÍA**

[All84] P.E. Allen, E. Sánchez-Sinencio, "Switched Capacitor Circuits," New York: Van Nostrand Reinhold Company, 1984

[Ara96a] K. Arabi, B. Kaminska, "Oscillation-test strategy for analog and mixed-signal integrated circuits," IEEE VLSI Test Symposium, 1996, pág. 476–482 [Ara96b] K. Arabi, B. Kaminska, J. Rzeszut, "BIST for D/A and A/D converters," IEEE Design & Test of Computers, vol.13, no 4, 1996, pág. 40-49

- [Ara99a] K. Arabi, B. Kaminska, "Oscillation-based test method for testing an at least partially analog circuit," United States Patent 6005407, diciembre 1999

- [Ara99b] K. Arabi, B. Kaminska, "Oscillation-test methodology for low-cost testing of active analog filters," IEEE Transactions on Instrumentation and Measurement, vol. 48, no 4, 1999, pág. 798-806

- [Aru08] D. Arumí, R. Rodríguez-Montañés, J. Figueras, "Experimental characterization of CMOS interconnect open defects," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 27, nº 1, enero 2008, pág. 123-136

- [Ast92] P. Astrachan, T. Brooks, J. Everett, W. Law, K. McIntyre, C. Nguyen, C. Weng, "Testing a DSP-based mixed-signal telecommunications chip", IEEE International Test Conference, 1992, pág. 669-677

- [Bra93] A.H. Bratt, R.J. Harvey, A.P. Dorey, A.M.D. Richardson, "Design-for-test structure to facilitate test vector application with low performance loss in non-test mode," Electronics Letters, vol. 29, no 16, 5 agosto 1993, pág. 1438-1440

- [Bra95] A.H. Bratt, R.J. Harvey, A.P. Dorey, A.M.D. Richardson, "A design-for-test structure for optimising analogue and mixed signal IC test", Proceedings European Design and Test Conference, 1995, pág. 24-33

- [Bro79] R.W. Brodersen, P.R. Gray, D.A. Hodges, "MOS switched capacitor filters," Proceedings of the IEEE, vol. 67, no 1, enero 1979, pág. 61-75

- [Bru75] L. Bruton, "Low-sensitivity digital ladder filters," IEEE Transactions on Circuits and Systems, vol. 22, n° 3, marzo 1975, pág. 168-176

- [Cha91] A. Chatterjee, "Concurrent error detection in linear analog switched-capacitor state variable systems using continuous checksums," IEEE International Test Conference, 1991, pág. 582-591

- [Cha94] V.H. Champac, A. Rubio, J. Figueras, "Electrical model of the floating gate defect in CMOS ICs: Implication on IDDQ testing," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 13, no 3, marzo 1994, pp 359-369

- [Cho00] W. Choi, R. Harjani, B. Vinnakota, "Optimal test-set generation for parametric fault detection in switched capacitor filters," Asian Test Symposium, 2000, pág.72-77

- [Cho04] W. Choi, B. Vinnakota, R. Harjani, "A digital DfT technique for verifying the static performance of A/D converters," Proceedings of the IEEE Custom Integrated Circuits Conference, 2004, pág. 207-210

- [Dim06] D. Gizopoulos, "Advances in Electronic Testing: Challenges and Methodologies," Springer, 2006

- [Duf97] C. Dufaza, H. Ihs, "Test synthesis for DC test and maximal diagnosis of switched-capacitor circuits," IEEE VLSI Test Symposium, 1997, pág. 252-260

- [Fas88] P.P. Fasang, D. Mullins, T. Wong, "Design for testability for mixed analog/digital ASICs," IEEE Custom Integrated Circuits Conference, 1988, pág. 16.5/1-16.5/4

- [Fla93] E. Flaherty, A. Allan, J. Morris, "Design for testability of a modular, mixed signal family of VLSI devices," IEEE International Test Conference, 1993, pág. 797-804

- [Gro09] IEEE 1149.4 Mixed-Signal Test Bus Working Group, http://grouper.ieee.org/groups/1149/4/

- [Had92] K. Hadidi, G.G. Temes, "Error analysis in pipeline A/D converters and its applications," IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 39, no 8, agosto 1992, pág. 506-515

- [Har97] R. Harjani, B. Vinnakota, "Analog circuit observer blocks," IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 44, no 3, marzo 1997, pág. 154-163

- [Hue93a] J.L. Huertas, A. Rueda, D. Vazquez, "Improving the testability of switched-capacitor filters," Analog Integrated Circuits and Signal Processing, vol. 4, no 3, noviembre 1993, pág. 199-213

- [Hue93b] J.L Huertas, A. Rueda, D. Vazquez, "Testable switched-capacitor filters", IEEE Journal of Solid-State Circuits, vol. 28, no 7, julio 1993, pág. 719-724

- [Hue99] G. Huertas, D. Vazquez, A. Rueda, J. Huertas, "Effective oscillation-based test for application to a DTMF filter bank," IEEE International Test Conference, 1999, pág. 549-555.

- [Hue02a] G. Huertas, D. Vazquez, E. Peralias, A. Rueda, J.L. Huertas, "Practical oscillation-based test of integrated filters," IEEE Design &Test of Computers, vol. 19, no 6, diciembre 2002, pág. 64-72

- [Hue02b] G. Huertas, D. Vazquez, E. Peralias, A. Rueda, J.L. Huertas, "Testing mixed-signal cores: Practical oscillation-based test in an analog macrocell," IEEE Design &Test of Computers, vol. 19, no 6, diciembre 2002, pág. 73-82

- [Hue03] G. Huertas, D. Vázquez, A. Rueda, J.L. Huertas, "Oscillation-based test in bandpass oversampled A/D converters," Microelectronic Journal, vol. 34, nº 10, octubre 2003, pág. 927-936

- [Hue06] G. Huertas, D. Vázquez, A. Rueda, J.L. Huertas, "Oscillation-based test in mixed-signal circuits," Springer, 2006

- [Hua84] K.H. Huang, J.A. Abraham, "Algorithm-based fault tolerance for matrix operations," IEEE Transactions on Computers, vol. 33, no 6, junio 1984, pág. 518-528

- [IEEE1149.1] "IEEE standard test access port and boundary-scan architecture," IEEE Std. 1149.1, 2001

- [IEEE1149.4] "IEEE standard for a mixed-signal test bus," IEEE Std. 1149.4, 2000

[Kol95] V. Kolarik, S. Mir, M. Lubaszewski, B. Courtois, "Analog checkers with absolute and relative tolerances," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 14, no 5, mayo 1995, pág. 607-612

- [Lec02] Y. Lechuga, R. Mozuelos, M. Martinez, S. Bracho, "Built-in dynamic current sensor for hard-to-detect faults in mixed-signal ICs," Design, Automation and Test in Europe, 2002, pág. 205-211

- [Lub00] M. Lubaszewski, S. Mir, V. Kolarik, C. Nielsen, B. Courtois, "Design of self-checking fully differential circuits and boards," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 8, n° 2, abril 2000, pág. 113-128

- [Mar79] K. Martin, A.S. Sedra, "Strays-insensitive switched-capacitor filters based on bilinear Z-transform," IEEE Electronics Letters, vol. 15, no 13, 21 junio 1979, pág. 365-366

- [Mas06] Masood-ul-Hasan, Y. Sun, "Oscillation-based test structure and method for OTA-C filters," IEEE International Conference on Electronics, Circuits and Systems, 2006, pág. 98-101

- [Mcc77] R.H. McCharles, V.A. Saletore, W.C. Black, D.A. Hodges, "An algorithmic analog-to-digital converter," International Solid State Circuits Conference, 1977, pág. 96-97

- [Mil89] L. Milor, V. Visvanathan, "Detection of catastrophic faults in analog integrated circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 8, nº 2, febrero 1989, pág. 114-130

- [Mir96] S. Mir, M. Lubaszewski, B. Courtois, "Unified built-in self-test for fully differential analog circuits," Journal of Electronic Testing, vol. 9, no 1-2, agosto 1996, pág. 135-151

- [Moz03] R. Mozuelos, Y. Lechuga, M. Martínez, S. Bracho, "SC algorithmic ADC test with a built-in charge sensor," Design of Circuits and Integrated Systems Conference, 2003, pág. 231-236

- [Moz04a] R. Mozuelos, Y. Lechuga, M. Martínez, S. Bracho, "Characterization of an SC ADC by a built-in charge sensor," IEEE International Mixed Signal Testing Workshop, 1994, pág. 122-126

- [Moz04b]R. Mozuelos, Y. Lechuga, M.A. Allende, M. Martínez, S. Bracho, "Experimental evaluation of a built-in current sensor for analog circuits," Design of Circuits and Integrated Systems, 2004, pág. 96-100

- [Moz05] R. Mozuelos, Y. Lechuga, M. Martínez, S. Bracho, "Test of a switched-capacitor ADC by a built-in charge sensor," Microelectronics Journal, vol. 36, no 12, diciembre 2005, pág. 1064- 1072

- [Nag93] K. Nagaraj, "Efficient circuit configurations for algorithmic analog to digital converters," IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing, vol. 40, no 12, diciembre 1993, pág. 777-785

- [Ono88] H. Onodera, T. Tateishi, K. Tamaru, "A cyclic A/D converter that does not require ratio-matched components," IEEE Journal of Solid-State Circuits, vol. 23, no 1, febrero 1988, pág. 152-158

- [Oss99] A. Osseiran, "Analog and mixed-signal boundary scan A guide to the IEEE 1149.4 test standard," Kluwer Academic Publishers, Boston, 1999

- [Par93] K.P. Parker, J.E. McDermid, S. Oresjo, "Structure and metrology for an analog testability bus," IEEE International Test Conference, 1993, pág. 309-317

- [Ren96] M. Renovell, F. Azais, Y. Bertrand, "The multi-configuration: A DFT technique for analog circuits," IEEE VLSI Test Symposium, 1996, pág. 54-59

- [Som94] M. Soma, V. Kolarik, "A design-for-test technique for switched-capacitor filters," IEEE VLSI Test Symposium, 1994, pág. 42-47

- [Son88] B. Song, M.F. Tompsett, K.R. Lakshmikumar, "A 12-bit 1-Msample/s capacitor error-averaging A/D converter," IEEE Journal of Solid-State Circuits, vol. 23, nº 6, diciembre 1988, pág. 1324-1333

- [Ste96] N.J. Stessman, B. Vinnakota, R. Harjani, "System-level design for test of fully differential analog circuits," IEEE Journal of Solid-State Circuits, vol. 31, no 10, octubre 1996, pág. 1526-1534

- [Sun01] S. Sunter, K. Filliter, W. Joe, P. McHugh, "A general purpose 1149.4 IC with HF analog test capabilities," IEEE International Test Conference, 2001, pág. 38-45

- [Sun95a] S. Sunter, "A low cost 100 MHz analog test bus," IEEE VLSI Test Symposium, 1995, pág. 60-65

- [Sun95b] S. Sunter, "The P1149.4 Mixed Signal Test Bus: costs and benefits," IEEE International Test Conference, 1995, pág. 444-450

- [Ter93] E. Teraoka, T. Kengaku, I. Yasui, K. Ishikawa, T. Matsuo, H. Wakada, N. Sakashita, Y. Shimazu, T. Tokuda, "A built-in self-test for ADC and DAC in a single-chip speech CODEC," IEEE International Test Conference, 1993, pág. 791-796