# Digital design and experimental validation of high-performance real-time OFDM systems

#### Ph.D. Dissertation

Josep Oriol Font Bach

Centre Tecnològic de Telecomunicacions de Catalunya (CTTC) e-mail: oriol.font@cttc.cat

Ph.D. Thesis Advisors: Dr. Antonio Pascual Iserte Associate Professor Departament de Teoria del Senyal i Comunicacions (TSC) Universitat Politècnica de Catalunya (UPC) e-mail: antonio.pascual@upc.edu

> Dr. Nikolaos Bartzoudis Senior Researcher Centre Tecnològic de Telecomunicacions de Catalunya (CTTC) e-mail: nikolaos.bartzoudis@cttc.cat

Barcelona, July 2013

M'han dit les veus assenyades que era inútil cansar-me; però a mi un somni mai no em cansa, i malgrat la meva barba sóc infant en la mirada.

Lluís Llach, Vida (1979)

Well I'm sorry but I'm not interested in gold mines, oil wells, shipping or real estate What would I liked to have been? Everything you hate.

Jack White, The Union Forever (2001)

iv

### Abstract

The goal of this Ph.D. dissertation is to address a number of challenges encountered in the digital baseband design of modern and future wireless communication systems. The fast and continuous evolution of wireless communications has been driven by the ambitious goal of providing ubiquitous services that could guarantee high throughput, reliability of the communication link and satisfy the increasing demand for efficient re-utilization of the heavily populated wireless spectrum. To cope with these ever-growing performance requirements, researchers around the world have introduced sophisticated broadband physical (PHY)-layer communication schemes able to accommodate higher bandwidth, which indicatively include multiple antennas at the transmitter and receiver and are capable of delivering improved spectral efficiency by applying interference management policies.

The merging of Multiple Input Multiple Output (MIMO) schemes with the Orthogonal Frequency Division Multiplexing (OFDM) offers a flexible signal processing substrate to implement the PHY-layer of various modern wireless communication systems. This is mainly due to the fact that this technology combination is able to provide increased channel capacity and robustness against multipath fading channels. Additionally, Orthogonal Frequency Division Multiple Access (OFDMA) is augmenting the capacities of the MIMO-OFDM technology to serve various mobile subscribers at the same time. A prominent scheme proposed to capitalize the benefits of diversity is the closed-loop MIMO communications, where the receiver is providing information to the transmitter related to the current channel conditions by means of a dedicated feedback channel. In the transmitter, the Channel State Information (CSI) is exploited to adapt at run-time the transmission and, thus, take advantage of the capacities provided by MIMO-OFDM(A).

The increased performance and flexible PHY-layer features of communication systems featuring MIMO-OFDM come at a cost of an increased computational load at baseband. Thus, innovating algorithmic, design and implementation solutions are required to provide the required PHY-layer schemes. Indeed, many levels of innovation are required to pass from a high-level model-based description of the system and its embedded algorithms to their digital realization. In fact, innovating digital design techniques aiming at maximizing the parallelization and resource re-utilization of the baseband Digital Signal Processing (DSP) algorithms have to be employed towards this end, in order to efficiently realize advanced PHY-layer schemes based on the MIMO-OFDM technology.

The Field-Programmable Gate Array (FPGA) custom-processing devices were selected for realizing the proof-of-concept developments of the thesis. When facing the real-time implementation of custom bit-intensive DSP architectures, FPGAs satisfy a trade-off between performance and flexibility, whilst providing the proof-of-concept environment, where innovating Register Transfer Level (RTL)-design techniques can be realistically validated. Moreover, a custom Hardware Description Language (HDL) coding approach was adopted to optimally define the processing demanding RTL designs.

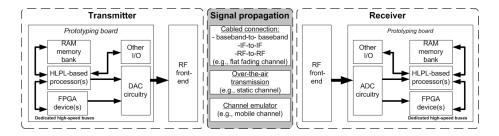

An important aspect of the presented PHY-layer prototyping is the utilization of real-life operating conditions, hardware specifications, constraints and mobile channel propagation conditions. This was made feasible by using the GEDOMIS<sup>®</sup> testbed. GEDOMIS is a high capacity signal generation and signal processing platform that enables the end-to-end real-time prototyping of multi-antenna wireless communication systems.

In order to support the complex development cycle it was introduced an iterative design, implementation and verification methodology, covering all the required steps from the definition of the system requirements and high-level modelling to the comprehensive evaluation of the resulting prototype based on a realistic hardware-setup.

The core contribution of this thesis is the simplification and optimization of a number of DSP operations that form part of certain baseband building blocks, which are encountered in modern OFDM-based communication systems. This not only allowed to meet the stringent real-time performance requirements, but also enabled the intelligent re-utilization, resource sharing or parallelization of the processing and memory resources available at the target FPGA devices.

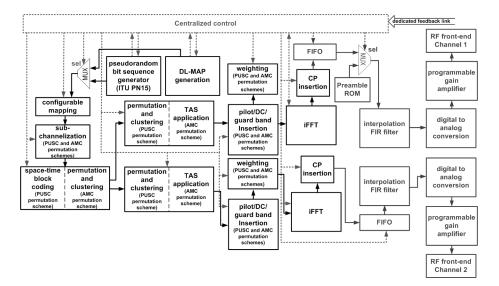

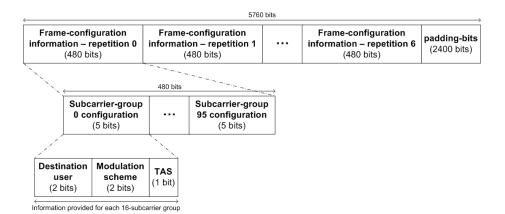

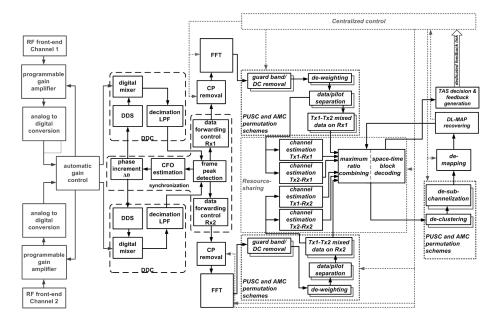

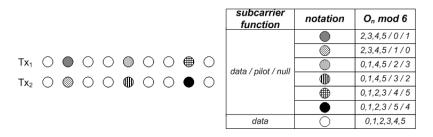

Two representative use cases detail this core contribution and underlined the suitability of the proposed development flow. The first use case is a 2x2 MIMO closed-loop PHY-layer scheme, based on the mobile Worldwide Interoperability for Microwave Access (WiMAX) wireless communication standard and featuring a Transmit Antenna Selection (TAS) mechanism. The second use case implements a 3rd Generation Partnership Project (3GPP) Long Term Evolution (LTE)-based macrocell/femtocell interference-management scheme.

### Resum

Aquesta tesi doctoral té com a objectiu abordar diversos reptes que es presenten en el disseny digital en banda base per a sistemes de comunicació sense fils moderns i futurs. La ràpida i continua evolució que han experimentat les comunicacions sense fils ha estat promoguda per l'ambiciós objectiu de proveir de serveis omnipresents capaços de garantir un alt rendiment i la fiabilitat dels enllaços de comunicació, tot satisfent el creixent requeriment per a la reutilització eficient de l'atapeït espectre radioelèctric. Per tal de fer front als requeriments de rendiment sempre creixents, investigadors d'arreu del món han proposat sofisticats esquemes de comunicació de capa física (PHYsical-layer, PHY), capaços d'acomodar un elevat ample de banda, incloent també de forma indicativa l'ús de múltiples antenes tant al transmissor com al receptor i millorant l'eficiència espectral mitjançant l'aplicació de principis per a la gestió de la interferència.

La combinació d'esquemes multi-antena (Multiple Input Multiple Output, MIMO) amb la Multiplexació per Divisió Ortogonal de Freqüència (Orthogonal Frequency Division Multiplexing, OFDM) ofereix un medi flexible de processat del senyal per a la implementació de la capa física de diversos sistemes de comunicacions sense fils moderns. Això és degut al seu potencial per a proveir d'una major capacitat de canal i protecció envers els diferents retards i pèrdues introduïdes per les transmissions sobre canals multi-trajectòria. Addicionalment, la Divisió Ortogonal de Freqüència d'Accés Múltiple (Orthogonal Frequency Division Multiple Access, OFDMA) augmenta les capacitats de la tecnologia MIMO-OFDM permetent servir simultàniament a diversos subscriptors mòbils. Un esquema MIMO prominent que permet capitalitzar els beneficis de la diversitat és el de llac tancat, on el receptor proveeix Informació sobre l'Estat del Canal (Channel State Information, CSI) al transmissor mitjançant un enllaç de retorn dedicat. El transmissor explota la CSI per a adaptar la transmissió dinàmicament i així poder aprofitar completament les capacitats de la tecnologia MIMO-OFDM(A).

L'elevat rendiment i les capacitats flexibles de la capa física dels sistemes de comunicació que utilitzen MIMO-OFDM impliquen un augment de la càrrega computacional en banda base. Conseqüentment, calen solucions innovadores a nivell algorítmic, de disseny i d'implementació per tal de proveir els esquemes de capa física requerits. De fet, es requereix d'innovació en diversos estrats per a passar de la descripció d'alt nivell del sistema i els algorismes que el formen (i.e., modelat) a la seva realització digital. Concretament, cal utilitzar tècniques de disseny digital innovadores que tinguin com a objectiu maximitzar el paral·lelisme i la reutilització de recursos per a la implementació dels algorismes de Processat Digital del Senyal (Digital Signal Processing, DSP), permetent així assolir una realització eficient d'esquemes avançats de capa física basats en la tecnologia MIMO-OFDM.

Els dispositius Matriu de Portes Programables (Field-Programmable Gate Array, FPGA), caracteritzats per possibilitar un processament a mida, es van escollir per a realitzar els desenvolupaments de prova de concepte de la tesi. Quan es considera la implementació en temps real d'arquitectures a mida d'alt rendiment per al DSP, les FPGAs proveeixen d'alta capacitat computacional i flexibilitat, oferint doncs un entorn ideal per a la validació experimental de tècniques innovadores de disseny a Nivell de Transferència de Registres (Register Transfer Level, RTL). Concretament, s'ha escollit una aproximació basada en la creació de codi a mida usant un Llenguatge de Descripció de Maquinari (Hardware Description Language, HDL), que permet definir de forma òptima aquells dissenys RTL que presenten elevats requeriments de computació.

Un aspecte important del propotipat de capa física que es presenta és la utilització de condicions realistes d'operació, d'especificacions i restriccions de maquinari i de condicions de propagació en canals mòbils. Això va ésser possible gràcies a la utilització del banc de proves GEDOMIS<sup>®</sup>. GEDOMIS és una plataforma d'alta capacitat per a la generació i processat del senyal, que permet el prototipat complet en temps real de sistemes multi-antena de comunicacions sense fils.

Per tal de suportar el complex cicle de desenvolupament es va introduir una metodologia iterativa de disseny, implementació i verificació, cobrint totes els passos des de la definició dels requeriments i modelat d'alt nivell del sistema fins a la validació exhaustiva dels prototipus resultants mitjançant una plataforma realista.

La contribució central de la tesi és la simplificació i optimització de diverses operacions de DSP que formen part de blocs arquitecturals de la banda base, que es troben als sistemes moderns de comunicació basats en OFDM. Això no només va permetre de satisfer els estrictes requeriments de rendiment impostats per la seva operació en temps real, sinó que ha habilitat la reutilització intel·ligent, compartició o paral·lelització dels recursos de processament i d'emmagatzemament proveïts pels dispositius FPGA escollits per a la seva implementació.

Dos casos d'ús detallen aquesta contribució central, subratllant la conveniència del flux de desenvolupament proposat. El primer cas d'us és un esquema MIMO de llaç tancat, basat en l'estàndard de comunicacions sense fils WiMAX mòbil i emprant un mecanisme de Selecció d'Antena Transmissora (Transmit Antenna Selection, TAS). El segon cas d'ús implementa un esquema de gestió de la interferència en un escenari macro-cel·la/femto-cel·la basat en l'estàndard 3GPP LTE.

### Resumen

La presente tesis doctoral tiene como objetivo principal abordar varios retos que se presentan en el diseño digital en banda base para sistemas de comunicación inalámbrica modernos y futuros. La rápida y continua evolución que han experimentado las comunicaciones inalámbricas ha estado promovida por el ambicioso objetivo de proveer de servicios omnipresentes capaces de garantizar un elevado rendimiento y la fiabilidad de los enlaces de comunicación, a la vez que se satisface el creciente requerimiento para la reutilización eficiente del saturado espectro radioeléctrico. Con el fin de hacer frente a los requisitos de rendimiento siempre crecientes, investigadores de alrededor del mundo han propuesto sofisticados esquemas de capa física (PHYsical-layer, PHY), capaces de acomodar un elevado ancho de banda, incluyendo también de forma indicativa el uso de múltiples antenas tanto en el transmisor como en el receptor y mejorando la eficiencia espectral mediante la aplicación de principios para la gestión de la interferencia.

La combinación de esquemas multi-antena (Multiple Input Multiple Output, MIMO) con la Multiplexación por División de Frecuencias Ortogonales (Orthogonal Frequency Division Multiplexing, OFDM) of rece un medio flexible de procesamiento de señal para la implementación de la capa física de varios sistemas de comunicación inalámbrica modernos. Esto es debido a su potencial para proveer de una mayor capacidad de canal y protección frente los diferentes retardos y pérdidas introducidas por las transmisiones sobre canales multitravectoria. Adicionalmente, la División de Frecuencias Ortogonales de Acceso Múltiple (Orthogonal Frequency Division Multiple Access, OFDMA) aumenta las capacidades de la tecnología MIMO-OFDM permitiendo servir simultáneamente a varios suscriptores móviles. Un esquema MIMO prominente que permite capitalizar los beneficios de la diversidad es el de lazo cerrado, donde el receptor provee Información sobre el Estado del Canal (Channel State Information, CSI) al transmisor mediante un enlace de retorno dedicado. El transmisor explota la CSI para adaptar la transmisión dinámicamente y así poder aprovechar completamente las capacidades de la tecnología MIMO-OFDM(A).

El elevado rendimiento y capacidades flexibles de la capa física de los sistemas de comunicación que usan MIMO-OFDM implican un aumento de la carga computacional en banda base. Consecuentemente, se necesitan soluciones innovadoras a nivel algorítmico, de diseño e implementación para poder proveer los esquemas de capa física requeridos. De hecho, se requiere de innovación en varios estratos para pasar de la descripción de alto nivel del sistema y los algoritmos que lo forman (i.e., modelado) a su realización digital. Concretamente, es necesario utilizar técnicas de diseño digital innovadoras que tengan como objetivo maximizar el paralelismo y la reutilización de recursos para la implementación de los algoritmos de Procesamiento Digital de Señal (Digital Signal Processing, DSP), permitiendo así obtener una realización eficiente de esquemas avanzados de capa física basados en la tecnología MIMO-OFDM.

Los dispositivos Matriz de Puertas Programables (Field-Programmable Gate Array, FPGA), caracterizados por posibilitar un procesamiento a medida, se escogieron para realizar los desarrollos de prueba de concepto de la tesis. Cuando se considera la implementación en tiempo real de arquitecturas a medida de alto rendimiento para el DSP, las FPGAs proveen de alta capacidad computacional y flexibilidad, ofreciendo así un entorno ideal para la validación experimental de técnicas innovadoras de diseño a Nivel de Transferencia de Registros (Register Transfer Level, RTL). Concretamente, se ha seleccionado una aproximación basada en la creación de código a medida usando un Lenguaje de Descripción de Hardware (Hardware Description Language, HDL), que permite definir de forma óptima aquellos diseños RTL que presentan elevados requisitos de computación.

Un aspecto importante del prototipado de capa física que se presenta es la utilización de condiciones realistas de operación, de especificaciones y restricciones de hardware y de condiciones de propagación en canales móviles. Esto fue posible gracias a la utilización del banco de pruebas GEDOMIS<sup>®</sup>. GEDOMIS es una plataforma de alta capacidad para la generación y procesamiento de señal, que permite el prototipado completo en tiempo real de sistemas multi-antena de comunicación inalámbrica.

Para soportar el complejo ciclo de desarrollo se introdujo una metodología iterativa de diseño, implementación y verificación, cubriendo todos los pasos desde la definición de los requerimientos y modelado de alto nivel del sistema hasta la validación exhaustiva de los prototipos resultantes mediante una plataforma realista.

La contribución central de la tesis es la simplificación y optimización de varias operaciones de DSP que forman parte de bloques arquitecturales de la banda base, que se encuentran en los sistemas modernos de comunicación basados en OFDM. Esto no solo permitió satisfacer los estrictos requisitos de rendimiento impuestos por su operación en tiempo real, sino que ha posibilitado la reutilización inteligente, compartición o paralelización de los recursos de procesamiento y almacenamiento provistos por los dispositivos FPGA escogidos para su implementación.

Dos casos de uso detallan esta contribución central, subrayando la conveniencia del flujo de desarrollo propuesto. El primer caso de uso es un esquema MIMO de lazo cerrado, basado en el estándar de comunicaciones inalámbricas WiMAX móvil y empleando un mecanismo de Selección de Antena Transmisora (Transmit Antenna Selection, TAS). El segundo caso de uso implementa un esquema de gestión de la interferencia en un escenario macro-celda/femto-celda basado en el estándar 3GPP LTE.

### Acknowledgements

This is probably the most complicated text to be produced in a thesis. First, it is the only portion you are sure that everyone will read (experts in the field or not). Moreover, you will be judged by what you say or rather for what you don't say. Also, is the only portion of text where only few etiquette rules apply (as you will see I am mixing different languages and non-formal expressions). But more importantly, it is where you are openly revealing your inner thoughts, feelings and gratitude towards relevant people. Let the feast begin!

Primero de todo, quiero agradecer la gran oportunidad que me han dado mis dos co-directores. No solo me habéis obsequiado con vuestro conocimiento e infinita paciencia, sino que me habéis hecho de padres en este fascinante mundo que es la investigación. Junto a vosotros he crecido personal y profesionalmente. Por si fuera poco, me he divertido mucho a vuestro lado (ya sea en Berlín, en Madrid, en Barcelona o en Castelldefels) y sé que nuestros caminos se cruzarán muchas veces más en el futuro. Toni, tu capacidad de aprender cosas nuevas, tu pasión por hacerlo y tus muchas habilidades como profesor nunca dejaran de maravillarme. Además, tu alegría se contagia y no puede ser mejor compañera de trabajo. Níxo, θαυμάζω την ιχανότητα ηγεσίας και τη σαφήνειά με την οποία βλέπεις τα πράγματα (όχι μόνο σε επαγγελματικό επίπεδο). Είσαι ένα πρόσωπο που εμπλουτίζει όσους γνωρίζει. Σε σένα δεν έχω βρει μόνο χάποιο για να χοιτάζω προς τα εμπρός, αλλά ένα αληθινό φίλο. Σε χάθε περίπτωση να θυμάσαι ότι έχω το βίντεο με το ζεϊμπέχιχό σου.

Vull agrair al CTTC les moltes facilitats que m'ha ofert: no només he tingut accés al millor equipament que un enginyer pugui desitjar, sinó que m'ha proveït d'un entorn de treball immillorable – càlid i estimulant, tot rodejat d'excel·lència científica i tècnica. Quiero agradecer especialmente a Ana Pérez y a Miguel Ángel Lagunas por introducirme en el desarrollo de sistemas MIMO y por el empuje y ánimos que me han ofrecido en todo momento. També vull agrair particularment l'imprescindible ajuda tècnica, professional i personal que m'ha donat el Miquel Payaró aquests darrers anys.

També m'agradaria donar les gràcies al José López i al Javier Arribas pels esforços de revisió; amb el darrer he tingut la sort de compartir bones estones a un recent viatge a Sophia-Antipolis (la seva elevada experiència i entusiasme per la recerca aplicada han donat peu a bons consells per acabar de retocar el text).

Aquesta tesi s'ha enriquit notablement gràcies a les aportacions dels companys amb qui he tingut la sort de treballar al CTTC. Vull començar destacant al David López, amb qui he pogut comptar en tot moment (podríem dir que tot va començar a Budapest...); per si això fos poc, la seva ajuda ha resultat fonamental a les llargues hores que hem passat al laboratori. Voglio ringraziare soprattutto l'amicizia e il supporto (su molti fronti) che Sor Paolo Dini mi ha offerto. Alla fine non siamo riusciti a costruire un quadro comune per la ricerca, ma (indipendentemente da ciò che accadrà in futuro) quello che abbiamo guadagnato è molto più importante, caro amico. Cal també una menció especial al Xavier Artiga, Marco Miozzo, Lluís Parcerisa i David Pubill pels molts àpats i litres de cafè que hem pres junts mentre canviàvem el món. Evidentment, també vull agrair especialment l'ajuda a la resta d'equip de BeFEMTO-EngU: Luís Blanco, Marc Molina, Pepe Rubio i Jordi Serra. Igualment, vull mencionar l'ajuda del Lluís Ventura durant els meus primers mesos al CTTC. Al José Núñez li he d'agrair una llarga col·lecció de pel·lícules de sèrie B que m'han ajudat a evadir-me quan semblava que la tesi podia amb mi. Per acabar, vull donar les gràcies al Josep Mangues per l'ajuda i consells rebuts, ja sigui durant la meva petita incursió a la tercera capa o posteriorment.

Com no podria ser d'una altra manera, la part més personal d'aquest text havia de començar amb tu; Anna, crec que molt poca gent pot dir que ha tingut la sort de trobar a la persona que el complementa, aquella ànima a qui un sembla ser predestinat (allò que en diuen l'amor de la seva vida). Ets la meva millor amiga, la meva companya i qui em dóna la força per a voler superar-me, per a evitar caure en el conformisme i la immobilitat que comporten la quotidianitat de la vida adulta. Sé que el nostre vincle és molt especial i que es fa més fort cada dia, creixent juntament amb el nostre fill. Sento que junts tot ho podem. Com diu el Jules "two can be complete without the rest of the world".

I arribem al més petit de casa, però també el més important de tots. Jac, encara que se que trigaràs molt de temps a comprendre realment el significat d'aquestes quatre ratlles, vull dir-te que la meva felicitat va néixer amb el primer batec del teu cor. Veure't créixer i aprendre de forma tant vertiginosa, però agafat de la meva mà, és fascinant i, sens dubte, el què dóna sentit al meu dia a dia. No deixis mai que et convencin de que hi ha res que no pots aconseguir. I no abaixis el cap davant de ningú, sé que arribaràs allà on potser jo no he sabut, petit Indy. T'estimo més del que mai hauria cregut de ser capaç!

Pares, he tingut la sort de créixer al vostre costat. No només m'heu guiat, animat, ajudat i deixat volar quan així ho he volgut, sinó que m'heu estimat incondicionalment, descobert el món i, encara ara, protegit sota la vostra ala. Sé que aquesta tesi us farà més contents, si cap, a vosaltres que a mi; jo estaré content si mai arribo a acostar-me al què vosaltres representeu per a mi. I tu, cap de trons, ja hauries de saber com d'important ets per a mi. Tens moltes més qualitats, habilitats i força de la que ets capaç de veure; sinó perquè et penses que el teu germà gran sempre ha volgut assemblar-se a tu? Escriu poeta, pensa filòsof, però sobretot no dubtis de que meravellaràs al món, Madrona. Avis, malgrat ja no sigueu aquí, vull dir-vos heu sigut una part fonamental de la meva vida. Espero que les vostres creences siguin certes i que, en algun lloc incorpori, us hagueu retrobat i es tornin a sentir les vostres afectuoses renyines.

Vull acabar donant les gràcies a la resta de la meva (per sort) gran família. Tenías razón *Totoy*, eres un buen tío. Montse gràcies per fer-me sentir com un fill més a casa teva. A l'Eva i a l'Iñaki (més ben dit, als pares del Roc) els he d'agrair especialment les moltes hores i afecte que han dedicat al Jac (fins us perdono el tema de l'espanyol!).

# Contents

| Acronyms       |      |                                                             |    |  |  |

|----------------|------|-------------------------------------------------------------|----|--|--|

| 1 Introduction |      |                                                             |    |  |  |

|                | 1.1  | Thesis overview                                             | 8  |  |  |

| <b>2</b>       | The  | PHY-layer development ecosystem                             | 9  |  |  |

|                | 2.1  | Introduction to the PHY-layer development ecosystem         | 9  |  |  |

|                |      | 2.1.1 Fundamental research                                  | 10 |  |  |

|                |      | 2.1.2 Realistic PHY-layer modelling                         | 14 |  |  |

|                |      | 2.1.3 PHY-layer implementation and prototyping              | 19 |  |  |

|                |      | 2.1.4 Large-scale IC production                             | 30 |  |  |

|                |      | 2.1.5 Synopsis                                              | 32 |  |  |

|                | 2.2  | Motivation                                                  | 34 |  |  |

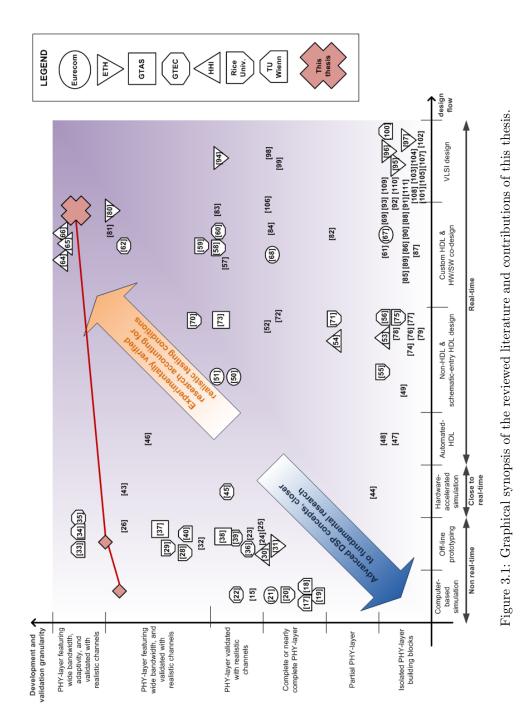

| 3              | Rela | ated work and contribution                                  | 37 |  |  |

|                | 3.1  | Preamble                                                    | 37 |  |  |

|                |      | 3.1.1 Definition of basic nomenclature                      | 37 |  |  |

|                |      | 3.1.2 Research groups used as a primary reference           | 39 |  |  |

|                | 3.2  | Review of related work                                      | 41 |  |  |

|                |      | 3.2.1 Advanced PHY-layer modelling initiatives              | 41 |  |  |

|                |      | 3.2.2 PHY-layer implementation and prototyping efforts      | 45 |  |  |

|                |      | 3.2.3 Efficient design targeting IC-technology              | 55 |  |  |

|                | 3.3  | Objectives, assumptions and conditions for the developments | 61 |  |  |

|                | 3.4  | Contribution                                                | 67 |  |  |

| 4              | Des  | ign, implementation and verification methodology            | 73 |  |  |

|                | 4.1  |                                                             | 73 |  |  |

|                |      | -                                                           | 74 |  |  |

|                | 4.2  |                                                             | 76 |  |  |

|                |      |                                                             | 76 |  |  |

|                |      |                                                             | 77 |  |  |

|                |      | -                                                           | 84 |  |  |

|                | 4.3  |                                                             | 85 |  |  |

|                | 4.4  |                                                             | 88 |  |  |

|                |      | -                                                           | 89 |  |  |

|                |      |                                                             | 90 |  |  |

|                |      |                                                             | 92 |  |  |

|                |      |                                                             | 94 |  |  |

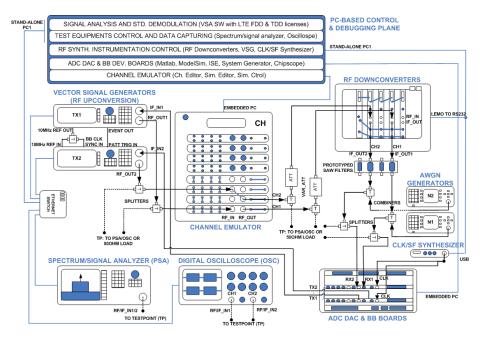

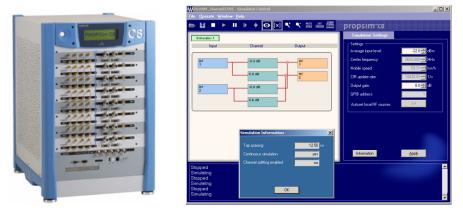

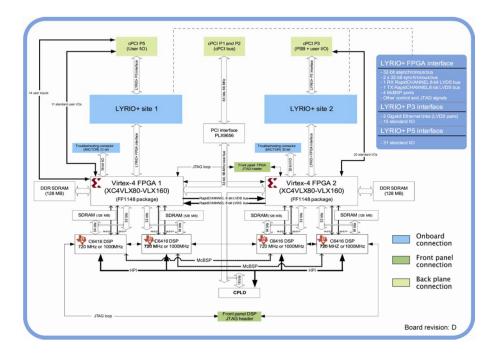

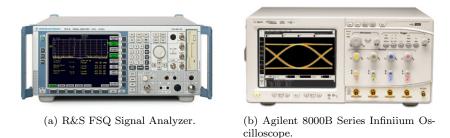

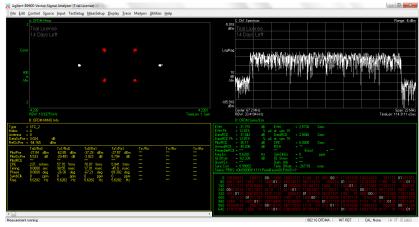

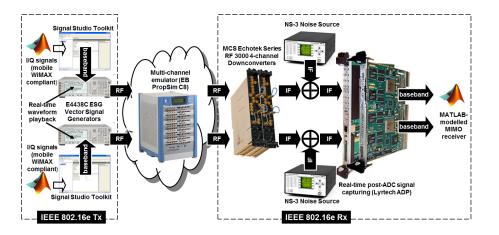

|                  |     | 4.4.5GEDOMIS' signal impairments4.4.6Utilization of GEDOMIS                            | 96<br>98     |  |

|------------------|-----|----------------------------------------------------------------------------------------|--------------|--|

|                  |     |                                                                                        | 50           |  |

| <b>5</b>         |     |                                                                                        | 103          |  |

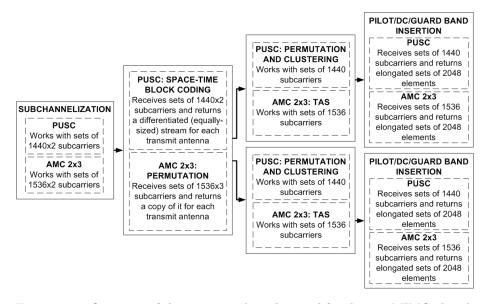

|                  | 5.1 | Considered system                                                                      |              |  |

|                  |     | 5.1.1 Basic description of the MIMO-OFDM technology                                    |              |  |

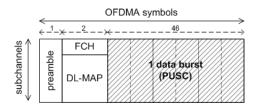

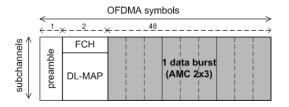

|                  |     | 5.1.2 Short introduction to the Mobile WiMAX PHY-layer                                 |              |  |

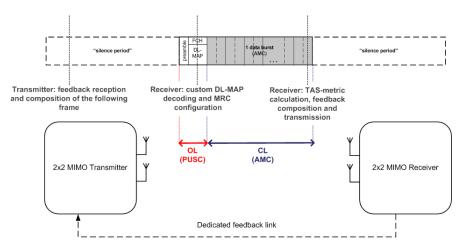

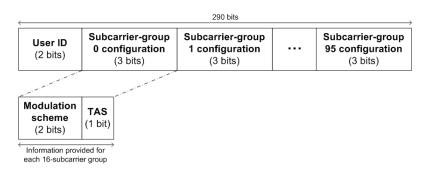

|                  | 50  | 5.1.3 System specifications and included features                                      |              |  |

|                  | 5.2 | Utilizing an incremental development                                                   |              |  |

|                  |     | 5.2.1 Single-antenna open-loop scheme                                                  |              |  |

|                  |     | 5.2.2 1x2 SIMO open-loop scheme                                                        |              |  |

|                  |     | 5.2.3 2x2 MIMO STBC-based system                                                       |              |  |

|                  | F 9 | 5.2.4 2x2 MIMO closed-loop scheme                                                      |              |  |

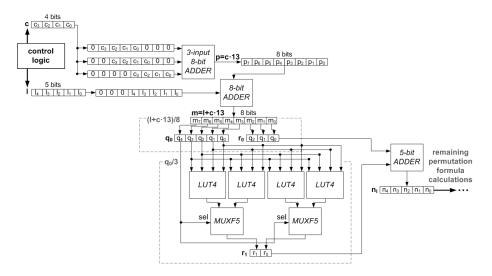

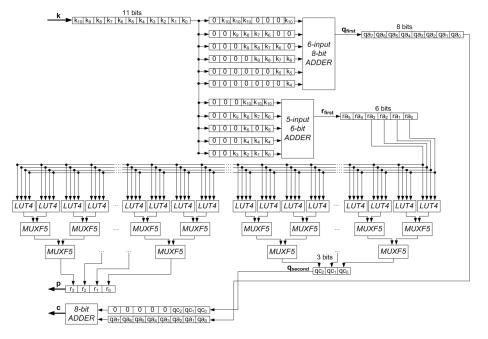

|                  | 5.3 | Innovating RTL design techniques                                                       |              |  |

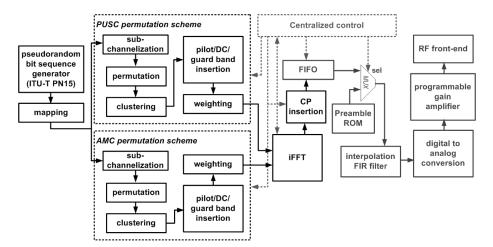

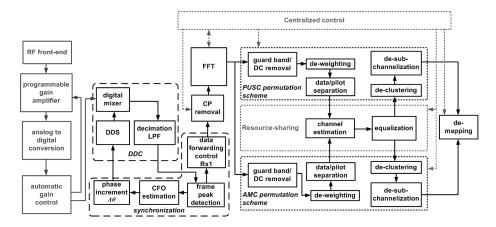

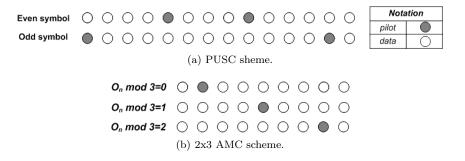

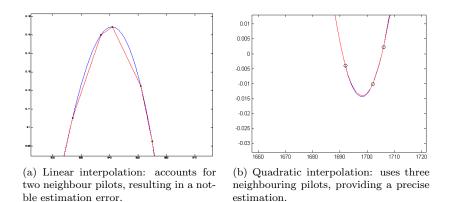

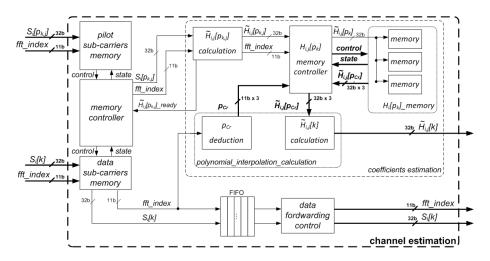

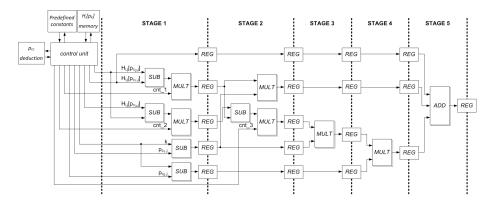

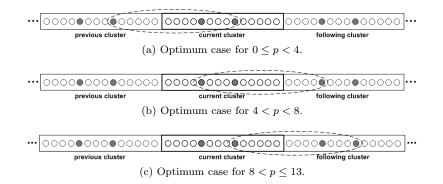

|                  |     | 5.3.1SynchronizationSynchronization5.3.2Channel estimation architectureSynchronization |              |  |

|                  |     | 5.3.3 Joint design of the STBC and MRC techniques                                      |              |  |

|                  |     |                                                                                        | $130 \\ 139$ |  |

|                  |     | 5.3.5 Implementing operations related to the WiMAX standard                            |              |  |

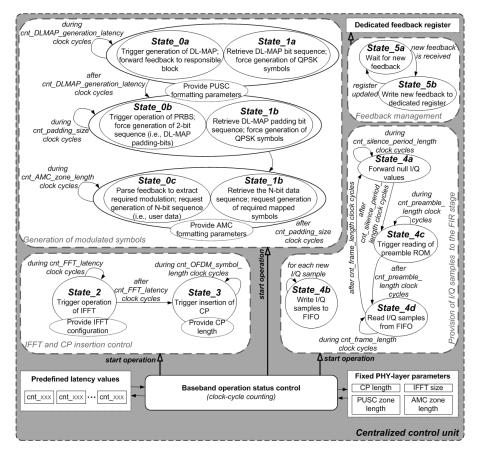

|                  |     | 5.3.6 Centralized control unit                                                         |              |  |

|                  | 5.4 | Integration and implementation using the GEDOMIS testbed                               |              |  |

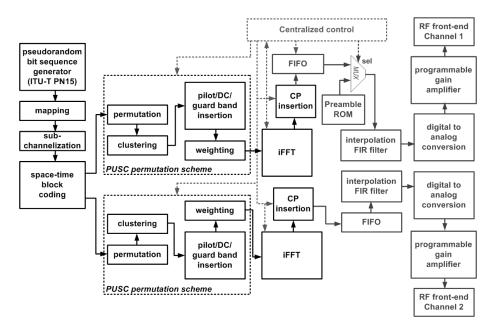

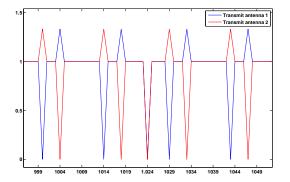

|                  | 0.4 | 5.4.1 Real-time MIMO signal transmission                                               |              |  |

|                  |     | 5.4.2 Real-time MIMO signal transmission                                               |              |  |

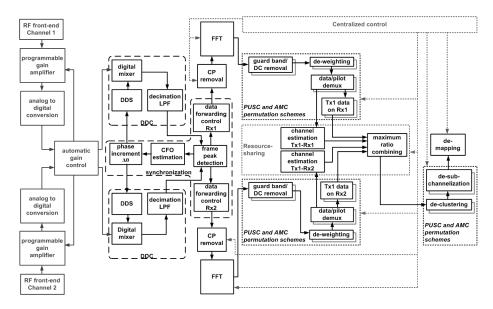

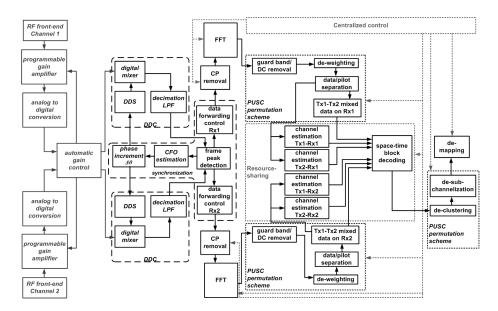

|                  |     | 5.4.3 Real-time MIMO signal reception                                                  |              |  |

|                  |     | 5.4.4 FPGA-based implementation of the presented systems                               |              |  |

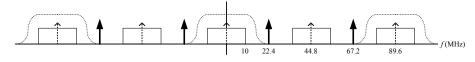

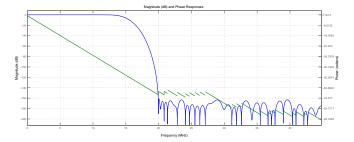

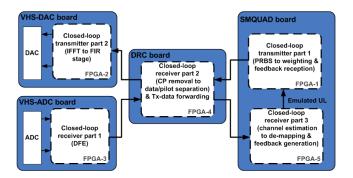

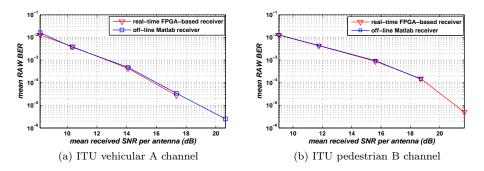

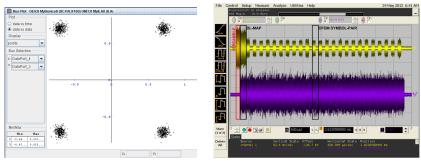

|                  | 5.5 | Experimental results                                                                   |              |  |

| 6                | TT  | Correct II                                                                             | 1 /7 1       |  |

| 0                | 6.1 | Case II<br>Considered system                                                           | 171          |  |

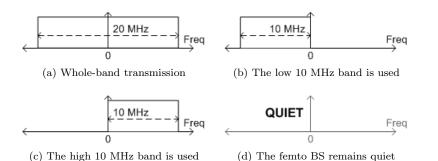

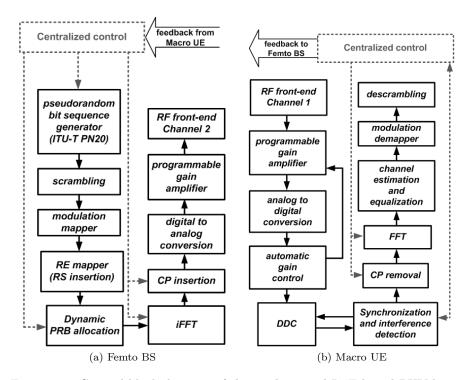

|                  | 0.1 | 6.1.1 Basic introduction to opportunistic frequency reuse                              |              |  |

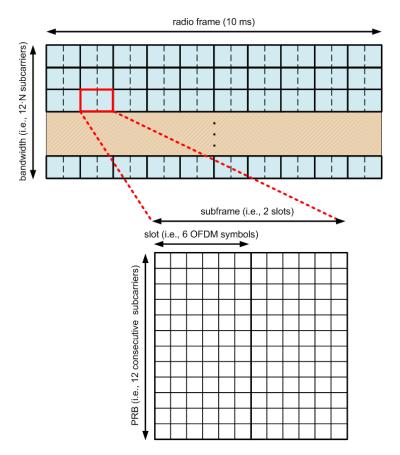

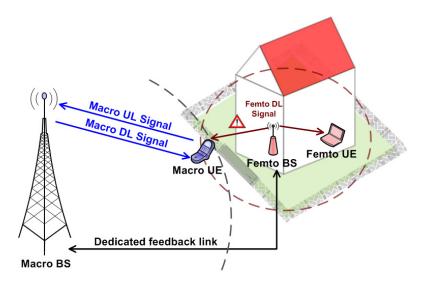

|                  |     | 6.1.2 Short introduction to the 3GPP LTE PHY-layer                                     |              |  |

|                  |     | 6.1.3 Considered scenario and PHY-layer specifications                                 |              |  |

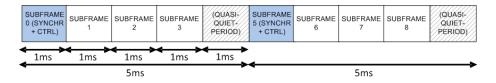

|                  |     | 6.1.4 Interference management scheme                                                   |              |  |

|                  | 6.2 | Utilizing an incremental development                                                   |              |  |

|                  | 0.2 | 6.2.1 Operation of the extended DFE                                                    |              |  |

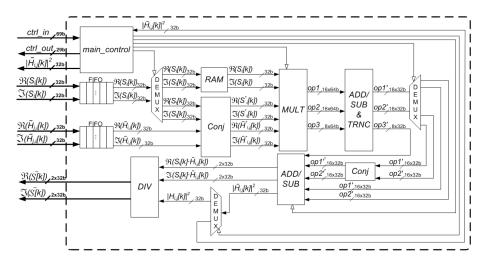

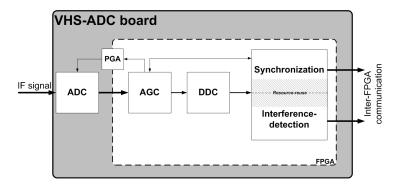

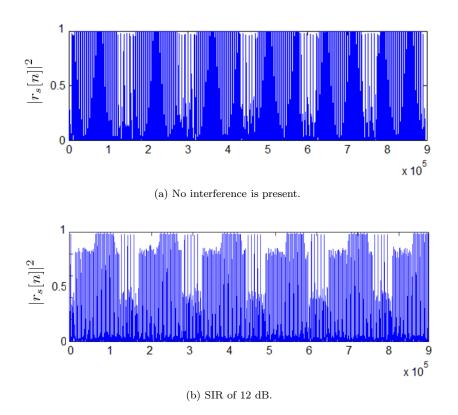

|                  | 6.3 | Efficient RTL design                                                                   |              |  |

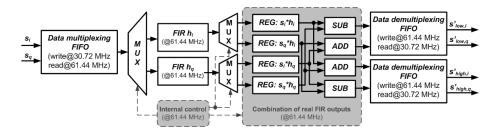

|                  | 0.0 | 6.3.1 Hardware-efficient digital filtering stage                                       |              |  |

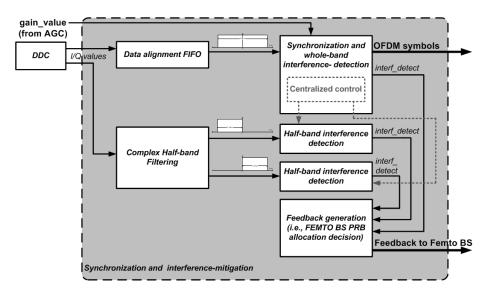

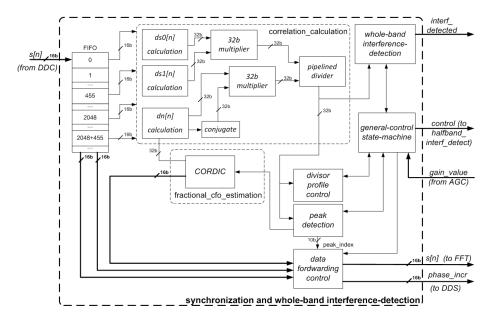

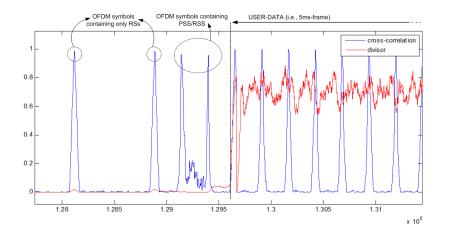

|                  |     | 6.3.2 Synchronization and interference-detection                                       |              |  |

|                  |     | 6.3.3 Centralized control unit                                                         |              |  |

|                  | 6.4 | Integration and implementation using the GEDOMIS testbed                               |              |  |

|                  |     | 6.4.1 Real-time channel and interference emulation                                     | 189          |  |

|                  |     | 6.4.2 FPGA-based implementation                                                        | 190          |  |

|                  | 6.5 | Experimental results                                                                   |              |  |

| 7                | Con | clusions and future work lines                                                         | 197          |  |

| •                | 7.1 |                                                                                        | 197          |  |

|                  | 7.2 | Future work lines                                                                      |              |  |

| Bibliography 201 |     |                                                                                        |              |  |

### Acronyms

- **3GPP** Third Generation Partnership Project

- ${\bf 4G} \ {\rm Fourth} \ {\rm Generation}$

- ADC Analog-to-Digital Converter

- **ADP** Advanced Development Platform

- AGC Automatic Gain Control

- **AI** Applied Instruments

- ${\bf ALU}\,$  Arithmetic Logical Unit

- AMC Adaptive Modulation and Coding

- **API** Application Programming Interface

- ASIC Application Specific Integrated Circuit

- AWGN Additive WGN

- ${\bf BER}\,$  Bit Error Rate

- **BICM** Bit Interleaved Coded Modulation

- ${\bf BS}\,$  Base Station

- ${\bf BW}$ BandWidth

- **BWA** Broadband Wireless Access

- **CAMTA** Argentine Conference on Micro-Nanoelectronics, Technology, and Applications

- **CBEA** Cell Broadband Engine Architecture

- **CCI** Co-Channel Interference

- **CFO** Carrier Frequency Offset

- ${\bf CIR}\,$  Carrier-to-Interference Ratio

- CMOS Complementary Metal-Oxide-Semiconductor

- ${\bf CoMP}\,$  Coordinated Multi-Point

- **CORDIC** Coordinate Rotation Digital Computer

- ${\bf COTS}$  Commercial-Off-The-Shelf

- ${\bf CP}\;\;{\rm Cyclic}\;{\rm Prefix}\;$

- $\mathbf{cPCI} \ \mathbf{compact} \ \mathbf{PCI}$

- **CPE** Customer Premises Equipment

- ${\bf CR}\,$  Cognitive Radio

- CS Compressed-Sensing

- **CSI** Channel State Information

- CTTC Centre Tecnològic de Telecomunicacions de Catalunya

- $\mathbf{EB}$  ElektroBit

- DAC Digital-to-Analog Converter

- DC Direct Current

- DDC Digital Down Converter

- **DDS** Direct Digital Synthesizer

- DFE Digital Front-End

- $\mathbf{DL}$ DownLink

- ${\bf DSP}$ Digital Signal Processing

- **EDA** Electronic Design Automation

- **EUSIPCO** European Signal Processing Conference

- ETH Eidgenössische Technische Hochschule

- **EVM** Error Vector Magnitude

- ${\bf FCH}\,$  Frame Control Header

- FDATool Filter Design and Analysis Tool

- FDD Frequency Division Multiplexing

- ${\bf FEC}\,$  Forward Error Correction

- FIFO First In First Out

- **FIR** Finite Impulse Response

- ${\bf FFT}$  Fast Fourier Transform

- FPGA Field Programmable Gate Array

- ${\bf FTW}\,$  Forschungszentrum Telekommunikation Wien

FUSC Full Usage of the Subchannels

GEDOMIS GEneric hardware DemOnstrator for MIMO Systems

GPGPU General-Purpose (computation on) GPU

GPP General Purpose Processor

GPU Graphics-Processing Unit

GTAS Grupo de Tratamiento Avanzado de Señal (UC research group)

**GTEC** Grupo de Tecnología Electrónica y Comunicaciones (UDC research group)

**GUI** Graphical User Interface

HDL Hardware Description Language

HetNet Heterogeneous Networks

${\bf HHI}$  Heinrich-Hertz-Institut

HIL Hardware-In-the-Loop

**HLPL** High-Level Programming Language

${\bf HLS}\,$  High-Level Synthesis

HSDPA High-Speed DL Packet Access

HW/SW HardWare/SoftWare

GBPS Giga-Byte Per Second

I/O Input/Output

$\mathbf{I}/\mathbf{Q}$  In-phase and Quadrature

**IC** Integrated Circuit

${\bf ICI}~{\rm Inter-Cell}~{\rm Interference}$

$\mathbf{ICIC} \ \ \mathbf{ICI} \ \ \mathbf{Coordination}$

**ICT** Information and Communication Technologies

**IDE** Integrated Development Environment

**IEEE** Institute of Electrical and Electronics Engineers

**IF** Intermediate Frequency

${\bf IFFT}~{\rm Inverse}~{\rm FFT}$

IMEC Interuniversitair Micro-Elektronica Centrum

**IMT** International Mobile Telecommunications

**IP** Intellectual Property

- **ISI** Inter-Symbol Interference

- ITU International Telecommunications Union

- $\mathbf{ITU}\text{-}\mathbf{R}$  ITU Radio Communication Sector

- **KPI** Key Performance Indicator

- LAN Local Area Network

- ${\bf LDPC}\,$  Low-Density Parity Check

- LNA Low-Noise Amplifier

- **LNICST** Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering

- LO Local Oscillator

- LST Layered Space-Time

- LT Linear Technology

- LTE Long Term Evolution

- LUT Look-Up-Table

- MAC Medium Access Control

- MASCOT Multiple-Access Space-Time Coding Testbed

- MCS Mercury Computer Systems

- ${\bf MG}\,$  Major Group

- MIMO Multiple Input Multiple Output

- MISO Multiple Input Single Output

- MLD Maximum-Likelihood Detector

- **MOBILIGHT** Mobile Lightweight Wireless Systems

- **MPI** Message Passing Interface

- MRC Maximum Ratio Combining

- **MSPS** Mega-Samples Per Second

- ${\bf MU}$  Multi-User

- MUBF MU BeamForming

- NCO Numerically Controlled Oscillator

- **NRE** Non Recurring Engineering

- **OFDM** Orthogonal Frequency Division Multiplexing

- **OFDMA** Orthogonal Frequency Division Multiple Access

| <b>OS</b> Operating System                           |

|------------------------------------------------------|

| <b>PA</b> Power Amplifier                            |

| ${\bf PAPR}$ Peak-to-Average Power Ratio             |

| <b>PAR</b> Place And Route                           |

| $\mathbf{PCI}$ Peripheral Component Interconnect     |

| PCIe PCI express                                     |

| ${\bf PGA}$ Programmable Gain Amplifier              |

| PHY PHYsical                                         |

| <b>PRB</b> Physical Resource Block                   |

| <b>PRBS</b> PseudoRandom Binary Sequence             |

| <b>PSS</b> Primary Synchronization Signal            |

| <b>PUSC</b> Partial Usage of Subchannels             |

| ${\bf QAM}$ Quadrature Amplitude Modulation          |

| <b>QoS</b> Quality of Service                        |

| ${\bf QPSK}$ Quadrature Phase-Shift Keying           |

| <b>RAM</b> Random Access Memory                      |

| $\mathbf{RF}$ Radio Frequency                        |

| <b>R&amp;S</b> Rohde & Schwarz                       |

| <b>RS</b> Reference Signal                           |

| <b>RTL</b> Register Transfer Level                   |

| <b>SDR</b> Software Defined Radio                    |

| <b>SDRAM</b> Synchronous Dynamic RAM                 |

| <b>SFDM</b> Space-Frequency Block Code               |

| <b>SIC</b> Successive Interference Cancellation      |

| ${\bf SINR}$ Signal-to-Interference-plus-Noise Ratio |

| <b>SIMO</b> Single Input Multiple Output             |

| <b>SIR</b> Signal-to-Interference Ratio              |

| 0                                                    |

| SISO Single Input Single Output                      |

| -                                                    |

**SNR** Signal-to-Noise Ratio

- ${\bf SoC}$ System-On-a-Chip

- SSS Secondary Synchronization Signal

- **STBC** Space-Time Block Coding

- ${\bf STBD}\,$  Space Time Block Decoding

- **STC** Space-Time Coding

- **STTC** Space-Time Trellis-Coding

- SVD Singular Value Decomposition

- ${\bf TAS}\,$  Transmit Antenna Selection

- ${\bf TDD}\;$  Time Division Duplex

- **TI** Texas Instruments

- **TridentCom** Testbeds and Research Infrastructure for the Development of Networks and Communities

- **TSC** Teoria del Senyal i Comunicacions (UPC department)

- ${\bf TU}\,$  Technischen Universität

- $\mathbf{UL}$  UpLink

- ${\bf UC}\,$ Universidad de Cantabria

- ${\bf UDC}\,$ Universidade da Coruña

- **UE** User Equipment

- **UPC** Universitat Politècnica de Catalunya

- **VHSIC** Very High Speed Integrated Circuit

- **VHDL** VHSIC HDL

- VLSI Very-Large-Scale Integration

- **VSA** Vector Signal Analyser

- ${\bf VSG}~{\rm Vector}~{\rm Signal}~{\rm Generator}$

- WARP Wireless Open-Access Research Platform

- WGN White Gaussian Noise

- WiMAX Worldwide Interoperability for Microwave Access

- WiMob Wireless and Mobile Computing, Networking and Communications

- WLAN Wireless LAN

- ${\bf WSN}$  Wireless Sensor Network

# Chapter 1

### Introduction

In recent years the world has experienced a dramatic evolution of wireless communications. This fast and continuous progression has been driven by the ambitious goal of providing ubiquitous communications services in every time more demanding operating conditions. A continuous increase of throughput and reliability, both for voice and data services, is expected in an environment featuring high mobility and a network composed by heterogeneous technologies. Novel solutions have been proposed by the academic community and the industry towards this end. In fact, the academic community has been covering a wide range of objectives from fundamental to applied research. Furthermore, the collaboration between both actors has been leading the generation of medium-to-long term solutions, aiming at setting the basis of future communication technologies. The target of the present thesis is the construction of solutions that will be employed in real-life applications in the mid-term.

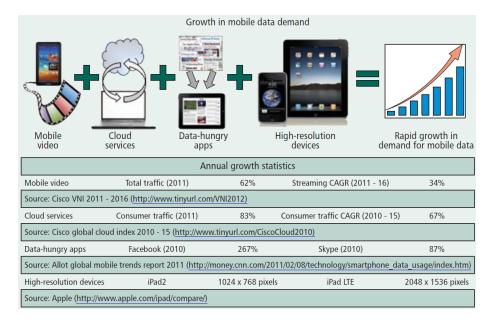

Mobile technology has entirely reshaped the telecommunications landscape, increasing the number of subscribers exponentially during the past decade. From the infrastructure point of view, mobile networks have suffered a drastic evolution in response to the ever increasing user requirements. Mobile operators have grown to dominate the market, offering services as comprehensive as those offered by their wireline counterparts. Furthermore, the utilization that the end-users are making of mobile phones and other mobile devices has also seen a significant change. The advanced mobile phones (e.g., smartphones) and other mobile devices have moved way beyond voice services, enabling complex datahungry applications (e.g., multimedia, video-calls, social networking, interactive multi-user applications) which have led to an unprecedented demand for high performance, high capacity and high bit-rate (see Figure 1.1).

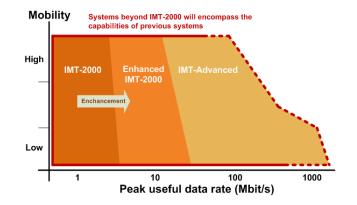

A key player in the future of mobile communications are the Broadband Wireless Access (BWA) technologies, which are meant to satisfy the advanced high data-rate and mobility requirements of the so-called 4G (fourth generation) and beyond mobile communications systems. The 4G requirements are detailed in the International Mobile Telecommunications Advanced (IMT-Advanced) specifications [ITU-R, 2003] defined by the International Telecommunications Union - Radio Communications Sector (ITU-R). The baseline data-rate for a 4G service is set at 100 Mbit/s for high mobility communication (i.e., speeds up to 500 km/h) and 1 Gbit/s for low mobility (i.e., up to 10 km/h) and stationary communication, as illustrated in Figure 1.2. Two indicative standard-

Figure 1.1: Relevant summary statistics on the annual growth of factors contributing to data explosion [1].

ization initiatives towards 4G wireless communication are the 3rd Generation Partnership Project (3GPP) Long Term Evolution (LTE), with its latest revision LTE-Advanced, and the Worldwide Interoperability for Microwave Access (WiMAX), through its evolved WiMAX-2 specifications (Institute of Electrical and Electronics Engineers - IEEE - 802.16.m) [2]. In spite of the ambitious requirements defined for 4G systems, future applications will continue impulsing the evolution of both mobile devices and service infrastructures, imposing demands that nowadays are only envisioned in a fundamental research context.

In addition, the different requirements imposed by applications which are developed in a constantly evolving wireless ecosystem, is promoting the coexistence of diverse wireless access technologies. This has given birth to the concept of Heterogeneous Networks (HetNet) posing serious design problems both at network and terminal level (e.g., the modern mobile devices are required to support multiple wireless access technologies).

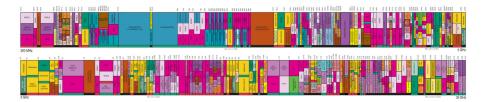

In an over-crowded Radio Frequency (RF) spectrum (see Figure 1.3), a determinant factor to cope with the continuously increasing demands of emerging wireless services is that of high spectral efficiency (i.e., high aggregated cell data rate per unit of spectrum). Among other measures, more efficient signal processing techniques, an improved Medium Access Control (MAC) and novel deployment concepts are needed for the the mobile cellular networks. For instance, an increased Base Station (BS) deployment combined with frequency reuse techniques should be implemented in HetNet scenarios. This actually constitutes a major topic investigated under the umbrella of Cognitive Radio (CR). Cognitive devices should be able to opportunistically utilize those RF spectrum bands which are not utilized by the primary communication (i.e., with high priority), without affecting their perceived service quality. A novel deployment scheme is that of small low-power cells coexisting with the evolved

Figure 1.2: Capabilities of IMT-Advanced [ITU-R, 2003].

Figure 1.3: United States radio frequency spectrum allocation (300 MHz to 30 GHz band) [NTIA, 2011].

cellular network. Such schemes are denoted as Femtocells (or jointly named as small cells, which encompass a more diverse size of cells) and are mainly aimed at covering the needs of short-range residential gateways, both addressing the indoor topology looses and opportunistically reusing the RF spectrum. However, in order to ensure a ubiquitous end-user experience, it is of paramount importance to guarantee a minimum Quality of Service (QoS).

In order to confront with the challenges encountered in this vast evolution, innovating algorithmic, design and implementation solutions are required at each communication layer (i.e., from network infrastructure to digital baseband design) separately, jointly and/or at system-level. Even if we constrain our view to the digital baseband design (which is the main focus of this thesis), there are still many levels of innovation required to pass from a high-level model-based description of the system and its embedded algorithms to their digital realization. In practical research terms, implementing the physical (PHY)-layer of modern mobile devices, including very complex signal processing, is of paramount importance to enable the real-world deployment of advanced wireless communication systems.

The PHY-layer of next generation wireless communication systems is due to support significantly augmented bandwidths (which implies a massive computational load at baseband), an increased number of users per cell and other flexible specifications that mostly affect the design and overall architecture of the baseband communications. Additionally, it is expected that the utilization of multiple antennas at both the transmitter and receiver sides, known as Multiple Input Multiple Output (MIMO), and interference mitigation techniques will have to be widely adopted to cope with the performance and reliability requirements of future mobile devices.

MIMO communication systems exploit spatial diversity to provide unprecedented capacity and throughput. On the other hand, Orthogonal Frequency Division Multiplexing (OFDM), with several data streams being transmitted in parallel, provides resilience against interference caused by multipath propagation. The merging of MIMO and OFDM offers a flexible signal processing substrate to implement the PHY-layer of various modern wireless communication systems. This is mainly due to the fact that this technology combination is able to provide increased channel capacity and robustness against multipath fading channels. Hence, many recent standardization efforts are using MIMO-OFDM as the basis of the proposed technologies (e.g., Wireless Local Area Network - WLAN, IEEE 802.11a/n/ac, LTE, WiMAX). Undoubtedly, accommodating high-performance prerequisites under fast channel fading implies challenging signal processing at baseband. The latter is scaled when considering a scenario with multiple competing users, where each user expects a minimum service quality (e.g., data-rate, Bit Error Rate - BER). Orthogonal Frequency Division Multiple Access (OFDMA) is augmenting the capacities of the MIMO-OFDM technology to serve various mobile subscribers at the same time. Moreover, a prominent scheme proposed to capitalize the benefits of diversity is the closedloop MIMO communications, where the receiver is providing information to the transmitter related to the current channel conditions by means of a dedicated feedback channel. In the transmitter, the Channel State Information (CSI) is exploited to adapt at run-time the transmission and, thus, take advantage of the capacities provided by MIMO-OFDM(A).

Another parameter of modern communication systems that every time acquires a more critical role, reducing operating costs [3] or the overall carbon footprint, is provided by optimizing the power consumption, which can also be achieved by means of adaptivity (e.g., accounting for the energetic cost and current channel conditions to select the most adequate MIMO scheme at every moment). Achieving both high performance and adaptivity augments in orders of magnitude the design complexity of MIMO-OFDM based systems. The most significant aspects in this sense are the number of antennas, the bandwidth and the implemented MIMO scheme. An indicative figure is given by the fact that the processing effort scales linearly with the bandwidth [4]. Currently, large bandwidths up to 20 MHz are considered in the pre-4G versions of both LTE and WiMAX (IEEE 802.16e standard, also denoted as mobile WiMAX). In actual or imminent wireless communications technology terms, bandwidths of up to 100 MHz are considered in order to enable true 4G LTE-Advanced systems.

Achieving the desirable performance in the PHY-layer requires to account for issues originated at a higher layer or at system-level. For instance, a strong limitation existing in dense BS deployments is posed by the presence of Inter-Cell Interference (ICI). Such in-band interference imposes significant constraints to the achievable performance. For this very reason, interference management techniques are considered a de-facto operational prerequisite for the deployment of 4G wireless access networks. Hence, interference management is being strongly considered in the current wireless communication standards, adapting and encapsulating novel PHY-layer techniques. While the leading wireless standards based on the MIMO-OFDM technology (e.g., LTE, WiMAX) can achieve improved spectral efficiency within one cell, ICI is still preventing them from

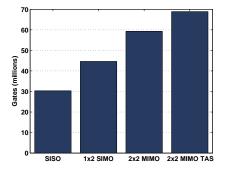

Figure 1.4: Augment of complexity, measured as equivalent gate-counts (Virtex-4 FPGA family), for different transceiver configurations based on results presented in Chapter 5.

coming close to the theoretical rates in multi-cell networks. For the particular case of small cells, many ICI-related innovative solutions are being proposed in the literature to efficiently enable the deployment of LTE-based Femtocells. Adaptive transmission plays a key role in the deployment of frequency reuse and interference management.

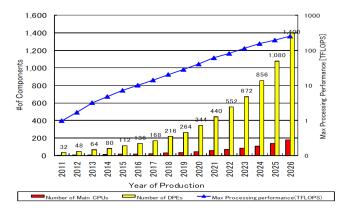

The projected exponential growth of wireless communication capacity (i.e., requiring every time for more signal bandwidth and spectral efficiency) caters for ground-breaking innovation not only at algorithmic level, but also new physical Integrated Circuit (IC) technologies, new implementation techniques and design methodologies. This is getting even more complex considering that high performance has to be every time more coupled with energy efficiency (i.e., the technology tendencies are to calculate the processing cost in terms of their bits per joule overhead). Fully exploiting the benefits of the previously introduced PHY-layer innovations, especially when they are combined, relies on the implementation of high-throughput receivers featuring a very high processing complexity at baseband (see Figure 1.4). The latter constitutes a fundamental digital design problem [Zhang, 2001]. As a consequence, the potential of the MIMO-OFDM based technology is still far from being fully exploited in actual implementations. Hence, the efficient implementation of advanced PHYlayer solutions has emerged as a major research topic [Burg, 2006, Edman, 2006, Eberle, 2006, Nilsson, 2007, Camera, 2008, Eberli, 2009, Wenk, 2010].

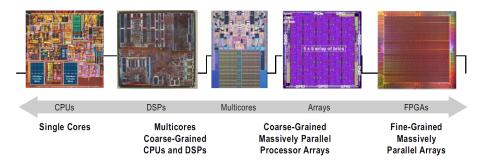

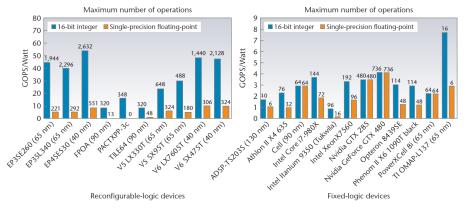

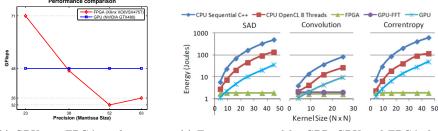

Addressing the bit-intensive requirements of high performance communication systems is traditionally questing the signal processing community throughout the historical trajectory of digital PHY-layer implementations. On top of that, the constant increase of computational complexity posed by the introduction of bit-intensive PHY-layer solutions is driving the need for massive and parallel computation. A clear trend towards the increased parallelism and heterogeneity is reflected in architectures where the processing elements are utilized to implement demanding Digital Signal Processing (DSP) arithmetic operations and transformations (i.e., PHY-layer of high-performance wireless communication systems), as shown in Figure 1.5. The amount of available options has, however, greatly complicated the selection of the most adequate technology for the digital realization of novel PHY-layer techniques. Mapping the PHY-layer

Figure 1.5: Recent trend of programmable and parallel technologies [5].

of different systems to this enormous design-space results in a widely varying performance and energy consumption, not solely when examining the target implementation technology, but also the different application domains and use cases.

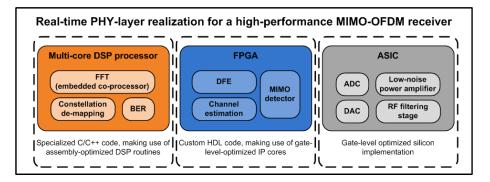

Likewise, the selected technology will have a great impact on the costs and time required to implement and validate the system. Hence, innovation is also required in the provision of optimized digital design, in terms of performance, utilized resources and energy consumption, accounting for the limitations of the selected technology. Over the last years, the most prominent technologies used in PHY-layer prototyping have been the DSP processors including multiple cores (usually called multi-cores), the cell processors, the Graphics-Processing Units (GPUs), the Field-Programmable Gate Arrays (FPGAs) and the Application Specific Integrated Circuits (ASICs). Given the large amount of available implementation technologies, the definition of the target application and a (set of) use case(s), results essential to narrow the explorable design-space. Traditionally, computer-based software simulations have constituted an extraordinary tool for the rapid validation and performance assessment of novel PHY-layer algorithms and systems. Nonetheless, the limitations encountered (i.e., assumptions and simplifications are applied considering that the simulation environments feature limited capacity to reproduce dynamic behaviours), seem to indicate that computer-based simulations are just constituting the first step towards the long path required to provide a comprehensive evaluation of novel algorithms and systems for real-life applications. Additionally, as the complexity of the algorithms introduced in the PHY-layer increases, it is not only required additional computational capacity, but also a complex testing infrastructure to accompany the analysis closer to real-world scenarios (e.g., realistic channel conditions, real-time operation, constraints and impairments introduced by the final implementation technology). Hence, the development of prototypes has been a major vehicle to realistically validate and assess the performance of advanced wireless communication systems, diminishing the gap between fundamental research and real-world solutions [Haustein, 2006, Perels, 2007, Caban, 2009, Naya, 2010, Murphy, 2010, Duarte, 2012]. In such context, a robust yet flexible methodology is essential not only to minimize the required design and implementation time, but especially to enable an optimum digital realization and guarantee the quality of the system evaluation in close-to-real-world conditions.

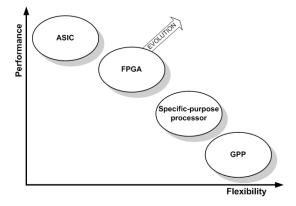

FPGAs are processing devices renown for their capacity to host custom

Figure 1.6: Performance vs. flexibility of different PHY-layer implementation technologies [8].

parallel digital processing systems and, thus, able to implement complex DSPintensive algorithms and advanced wireless communication systems. Modern FPGA devices have gone even further by integrating a number of different dedicated hard-wired Intellectual Property (IP) processing blocks within the fabric (Ethernet, Peripheral Component Interconnect express - PCIe - and Gigabit Input/Output - I/O - cores among others), while increasing dramatically the digital logic and DSP-specific building blocks and the embedded memory capacity. This gives them unprecedented parallel computing capacity from one side and flexibility from the other side (see Figure 1.6), when utilizing run-time partial reconfiguration techniques [6], or when using the on-chip hard-wired multi-core microprocessors [7], available in certain families, following by this way a hardware/software (HW/SW) co-design approach. Therefore, FPGAbased implementations are ideal to meet the needs posed by the development of realistic prototypes (i.e., cost, time, capacity and flexibility). As an example, when prototyping BWA systems, FPGAs are not only appropriate to satisfy the demanding PHY-layer processing requirements, but their flexibility is also very important if the constant evolution of the wireless communication standards is taken into account. Hence, modifications on the standards can be implemented with clearly smoother implications than when compared, for instance, with ASIC-based solutions (which are the preferred solution for large-scale fabrication).

This thesis is focusing on the PHY-layer and more concretely on the efficient realization of baseband signal processing algorithms, by employing advanced digital design techniques and by applying suitable optimizations at digital circuit level. The ultimate goal is to achieve performance improvements with agile usage of baseband processing resources. Such efficient design and FPGA-based implementation of advanced PHY-layer solutions forms the basis of those high-performance wireless communication systems that feature adaptive operation, which follows dynamically variable conditions. FPGAs have been selected because they satisfy a trade-off between performance and flexibility and provide the proof-of-concept environment where innovating Register Transfer Level (RTL)-design techniques can be validated realistically. Moreover, it is very important to underline that the innovative PHY-layer prototyping introduced herein is bound to real-life conditions, hardware specifications and constraints under realistic mobile channel propagation conditions.

The main contribution of this thesis, as it will be elaborated across the following chapters, is the provision of innovation in performance-efficient digital design, which is strongly tight to detailed design principles, procedures and a proposed incremental methodology, that jointly aim at efficiently designing, implementing and realistically verify advanced PHY-layer solutions. Moreover, although the scope of this thesis has been set on high-performance wireless communication systems featuring adaptivity, the provided contribution can be extrapolated to other communication systems with demanding DSP requirements (i.e., systems requiring wide bandwidth and dynamic range; e.g., MIMO channel emulation for power line communications or digital pre-distortion for wireless back-hauling links).

#### 1.1 Thesis overview

The contents of the thesis are organized as follows.

Chapter 2 covers the motivation of the thesis. The different technologies utilized in the modelling and implementation of the PHY-layer are discussed, whose target strictly falls within the realistic prototyping of high-performance wireless communication systems featuring adaptive behaviour. For this reason, a representative diagram of PHY-layer design, implementation and evaluation ecosystem is defined (i.e., the different levels encountered from high-level modelling to fabrication).

Chapter 3 reviews the related work, with the intention to provide a comprehensive taxonomy of relevant literature. The main contributions of the thesis are also detailed and located within the described landscape.

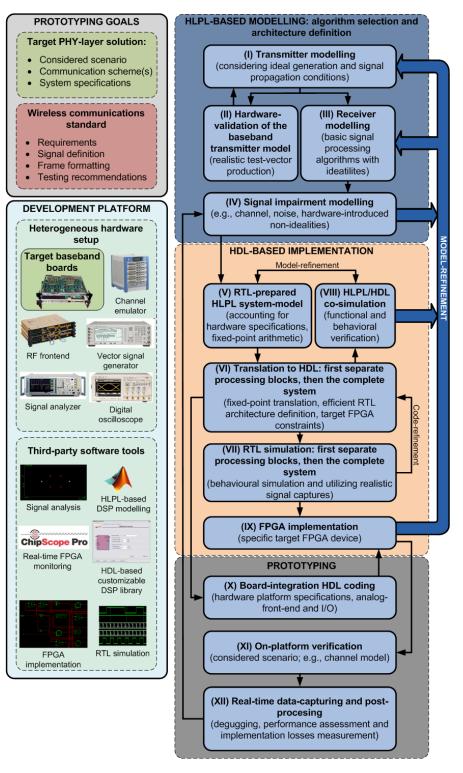

Chapter 4 proposes a design, implementation and verification methodology aimed at providing a performance-efficient implementation of bit-intensive wireless communication systems featuring adaptivity. The methodology covers all the required steps from the definition of the system requirements and high-level modelling to the comprehensive and realistic evaluation of the resulting prototype, using a heterogeneous hardware-setup with close to real life operating conditions. Moreover, it are discussed the multitude of challenges to which the system designer is deemed to face, in many different levels, when following the previously introduced methodology. The latter aims at providing system-level design principles which along with the design work flow constitute a complementary companion that helps to accomplish a successful performance-efficient applied research roadmap.

Chapters 5 and 6 provide two indicative use cases, focusing on the innovation provided in the digital realization of the PHY-layer of advanced wireless communication systems. The aim of those chapters is twofold. First, they serve as a proof-of-concept of the proposed design methodology. More importantly, those RTL design principles constituting a principal contribution of this thesis are fully illustrated therein.

Chapter 7 is closing the thesis by analysing the results and extracting useful conclusions, while pointing future work lines and extensions of the presented work.

#### Chapter 2

## The PHY-layer development ecosystem

Motivating the innovation in digital design

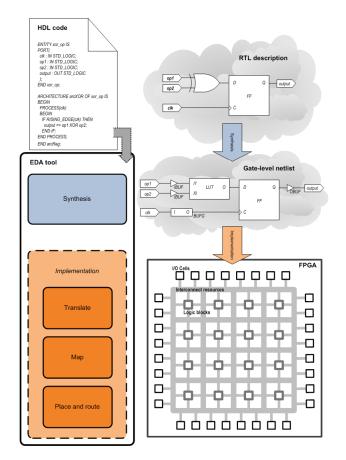

Empowering the constant evolution of the wireless communication systems requires inter-sectorial and cross-sectorial novel solutions. Yet, when strictly focusing on the PHY-layer, innovative solutions are needed at all different levels: theoretical conceptualization, modelling, design and implementation. The identification of these heterogeneous innovations is what this chapter intends to outline. The message that is conveyed is the fact that a long path lays across the proposal of a novel algorithm and its efficient digital realization.

#### 2.1 Introduction to the PHY-layer development ecosystem

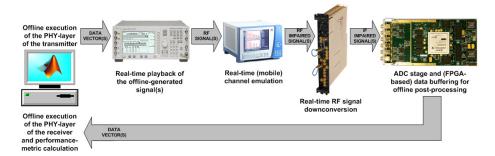

Figure 2.1 provides a graphical overview of the different approaches commonly utilized to design, implement and validate novel PHY-layer solutions. Evidently, the development-cycle time highly depends on the selected approach, that could serve different objectives: ranging from a rapid evaluation of known or novel concepts, to an extremely long development process when targeting a final-product. As the complexity of the proposed solutions augments (i.e., high-performance and adaptivity), more optimization is required for its digital implementation. Consequently, a more complex design, implementation and validation method is required. Furthermore, while the conceptual and behavioural modelling of PHYlayer algorithms related to wireless communication systems naturally starts by using High-Level Programming Languages (HLPLs) and a computer-based simulation, it is widely accepted within the experimentally-driven research community that the complete validation of innovating DSP algorithms is only achieved when the latter are implemented and tested using baseband and RF laboratory equipment that generates and processes signals, which are subject to real-life hardware constraints and impairments (i.e., including a physical or hardwareemulated signal propagation channel) [Caban et al., 2011].

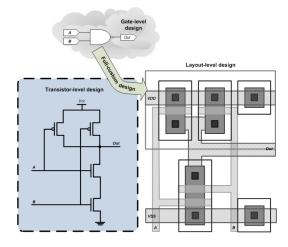

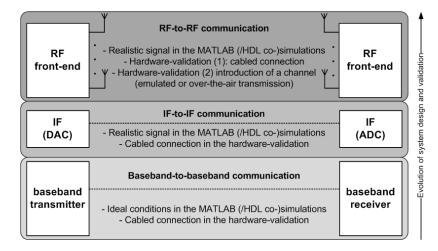

Figure 2.1: PHY-layer design, implementation and validation ecosystem.

# 2.1.1 Fundamental research founded on computer-based models and simulations

The innovative ideas impulsing the progression of wireless communications have their origins on fundamental research. In the case of the PHY-layer, the novel signal processing solutions are typically born as computationally demanding mathematical models, which in many cases require of unprecedented processing capacity. Consequently, the real-world conception of such solutions results prohibitive even when state-of-the-art technology is employed. Hence, in many cases a gap exists between fundamental and applied research. At the same time, the ability to verify the capacity gains of novel DSP algorithms and techniques, or the performance of new wireless communication standards, is one of the main research and development drivers of both academic and industrial entities. Therefore, fundamental research studies based on computer simulations, that describe in a high-level algorithms or entire systems, have been traditionally adopted as the principal method to rapidly estimate the achievable gains of the proposed solutions.

The capital features of software-based modelling (algorithmic or systemwide) indeed constitute the most adequate method to evaluate the proposed ideas at an early stage of technology-driven applied research. This is mainly due to the inherent facility provided by HLPLs to describe complex mathematical models, with numerous pre-verified software libraries and tools made available to the system designer. The utilization of the universally prominent C/C++ general purpose languages consists one of the most emblematic HLPL-based DSP modelling approaches. Some indicative open-source initiatives can be found in [AQU, SPU, DSP], whereas [IPP] provides a commercial General Purpose Processor (GPP)-based DSP library. Nonetheless, MATLAB<sup>®</sup> [MAT] probably constitutes the de-facto HLPL and mathematical modelling environment utilized by the signal processing research community. It is because MATLAB provides the means for rapid verification of signal processing algorithms and systems in a user-controlled cross-platform environment. Additionally, an ever-growing set of add-ons, open-source code and pre-compiled libraries facilitates the high-level design and modelling of complex systems. Within the most commonly utilized MATLAB extensions lies the Signal Processing Toolbox<sup>TM</sup> [SPT], providing an exhaustive collection of notable industry-standard DSP algorithms. The versatility of MATLAB has also made it one of the standard interfaces between computers and high-end testing, emulation and signal generation instruments.

The utilization of HLPL-based DSP libraries permits the researcher to concentrate on the conception of innovative PHY-layer solutions, as the complicated aspects related to its digital realization can be abstracted away. Another essential benefit of system modelling based on computer simulations is its relatively low development cost, both in temporal and economic terms, providing by this way an ideal environment for the rapid evaluation of complex solutions with inexpensive hardware equipment. Similarly, standard constructs of HLPLs can be utilized to describe the DSP model, not demanding the lengthy acquisition of expertise in the utilization of additional programming languages or tools aimed at constructing low-level hardware architectures (e.g., Hardware Description Languages - HDLs). All the previous advantages are substantially augmented when considering the flexibility provided by any software-based development (e.g., compilation time is short compared to low-level programming languages). The modelled solutions can be modified or extended without a notable change of the development cost. Moreover, complex and governable scenarios can be considered with a similar cost (e.g., large number of users and fully-controlled evaluation conditions, such as the channel model, the Signal-to-Noise Ratio -SNR - or the interference perceived by each mobile receiver). Likewise, the considered scenarios can also be easily modified or augmented.

The above provides a solid basis for computer-based algorithmic exploration or system-wide experimentation, constituting by this way an essential vehicle that enables fundamental research. At the same time the versatility of simulation-based high-level modelling environments is effectively used as an indispensable part of the applied research development cycle, that targets innovating prototypes of systems that are subject to real-life constraints. However, this particular use of HLPL-based mathematical modelling environments reveals a series of limitations which, generally speaking, are related to their finite capacity to deal with computational intensive data processing and other limitations on modelling or accounting for mixed signal effects and impairments. Hence when the numerical complexity of the PHY-layer algorithms increases, it is required to make assumptions and simplifications in the mathematical models, in an attempt to address the mismatch of the required computational capacity and simulation time. While the latter allows the analysis of the theoretical performance gains achievable by the proposed solutions, basic parameters that critically affect the operation and the physical realization of wireless communications are omitted in an idealized simulation environment. This may occasionally result in overoptimistic conclusions (e.g., in terms of performance, required processing architecture or estimated power consumption). A short description of some common assumptions and simplifications, and their impact on the realistic validation of PHY-layer algorithms and systems, follows:

- Unlimited resources: high-level software models do not usually account for the amount of baseband signal processing resources that will be required to physically implement the system under test, leading to an ideal validation scenario, where unlimited computational capacity is assumed. This additionally prevents a precise analysis and quantification of the achievable gains, since the DSP-computing architecture remains undefined. Furthermore, the computation latency of the required DSP calculations is also depending on the defined architecture. The lack of consideration of the previous aspects may affect the evaluation of algorithms, even when the digital realization of the system under test is not the principal target. Indicative examples are the analysis of performance or energetic gains, since they are both strongly related to the low-level DSP architecture and implementation technology (e.g., on-chip dedicated memory versus off-chip shared memory).

- Unlimited precision: HLPL-based models usually provide highly accurate double-precision numerical environments, leading to floating-point system models that neglect many of the constraints encountered in real-world implementations. In particular, the precision-loss introduced when translating a floating-point system model, built with a HLPL, to fixed-point logic, targeting a specific baseband processor technology, are often underestimated or completely ignored. As a result, the impact of some standard operating conditions or inherent functional features on the performance of an algorithm or an entire system may not be properly evaluated (e.g., noisy channel estimations), which in turn may lead to severe degradation of the global performance of the (wireless) communication system. Likewise, the target technology is limiting the maximum attainable precision (e.g., maximum bit-width provided by the Analog-to-Digital Converter ADC or Digital-to-Analog Converter DAC stages).

- Idealized channel conditions: it is quite common to assume a flat fading channel, with independent and identically distributed fading at each antenna, or simplified (quasi-)static channel models which are considered at simulation-time during the early stage of algorithm exploration. Furthermore, usually it is assumed perfect knowledge of the channel at both the transmitter and receiver sides. The mentioned environmental simplification and channel-knowledge idealization strongly impair the accurate assessment of the selected algorithms suitability and the confident analysis

of the computational complexity of a digital realization, which shall fulfil the performance requirements of the system under test. This is especially crucial in those scenarios that consider mobility and, thus, rapid variations of the channel propagation conditions. An illustrative case is the channel estimation at the receiver: channels featuring aggressive fading demand an increased arithmetic computation, often leading to a design-time trade-off between implementation complexity and performance. An accurate definition of this delicate trade-off requires an extensive algorithm selection phase, which is highly dependent on the considered scenario (e.g., channel model, SNR conditions).

- Ideal signal: it is not uncommon to encounter in the literature (see Chapter 3) algorithmic studies where the model's input signal or test vector is generated in the same simulation environment and, thus, failing to account for certain natural operating conditions, limitations and features of reallife hardware equipment that critically affect the received signal. In this context, it is often assumed the reception of perfectly synchronized signals, although for instance in OFDM-based systems, Fast Fourier Transform (FFT)-window misalignments have a direct impact on the performance of the receiver. Other potentially significant signal impairments, such as In-phase and Quadrature (I/Q) gain and phase imbalances, inaccuracy between the sampling clocks of the transmitter and receiver in respect to the ideal sampling frequency, Local Oscillator (LO) drifts, random phase noise due to LO instability and Carrier Frequency Offset (CFO), also tend to be neglected. This both affects the estimated performance and simplifies the implementation complexity: on the one hand, one of the key components with a critical impact on the performance of the baseband logic, the Digital Front-End (DFE - i.e., responsible for vital operations of the receiver, such as the symbol detection or the control of the power-gain applied at the ADC stage), is not taken into account. On the other hand, the RF front-end is also neglected, abstracting away the hardware non-idealities of real-world systems (e.g., attenuation suffered by RF components, additional noise originated by the RF equipment, antenna coupling, Direct Current - DC - levels).

- Control plane: real-world implementations are usually composed of specialized computing blocks working in parallel, that need to intercommunicate among them, and with other basic system resources (e.g., off-chip memories, buses), in a synchronized manner. Therefore, robust control units, managing the operation of the processing blocks, must be designed to ensure the correct operation of the system. Such control units tend to be complex entities, often requiring a non negligible amount of hardware resources and, likewise, of considerable design, implementation and verification time. This part is naturally not present in software simulations, thus omitting the implementation overhead of the control plane. The relevance of this issue is particularly important when the behaviour of the system needs to be dynamically adjusted, according to the response of external parameters. Hence, not only there will be the need to exchange control data between the transmitting and receiving entities, but it has to be delivered in a timely manner and with minimized overhead. If the

latter is not properly dimensioned, analysed and designed, it may heavily influence the expected gains introduced by an innovating PHY-layer algorithm.

Therefore, in many occasions what is missing in the evaluation cycle of innovating PHY-layer algorithms is the emulation of system-wide functional parameters that are subject to realistic physical conditions, inherent to the operation of real-life hardware devices, equipment and instrumentation, as well as realistic channel propagation and SNR conditions. Therefore, in order to assess in exact terms the performance of separate algorithms or the entire PHY-layer of a communication system, it is crucial that the simulation model under validation takes into account as many effects, system specifications and physical impairments as possible. The previous is an essential step to enable both the efficient implementation of novel solutions and a closer-to-reality analysis. Such a detailed model requires a substantially additional computational capacity, which is related to the complexity of the proposed PHY-layer solutions. This is especially true, when considering bit-intensive wireless communication systems, which by default feature elevated computation requirements that are due to the wide baseband bandwidth, the number of antennas, the considered communicationscheme and the time-varying DSP functions.

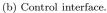

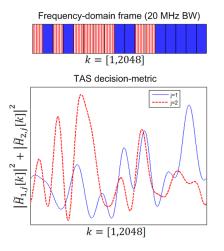

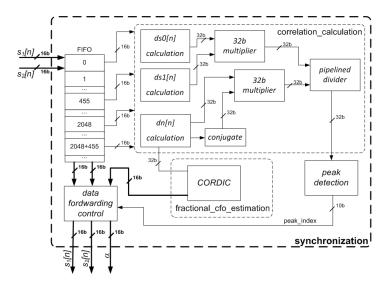

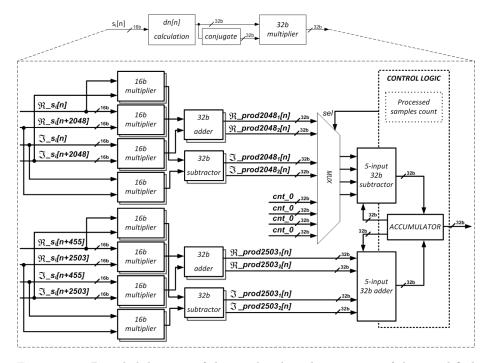

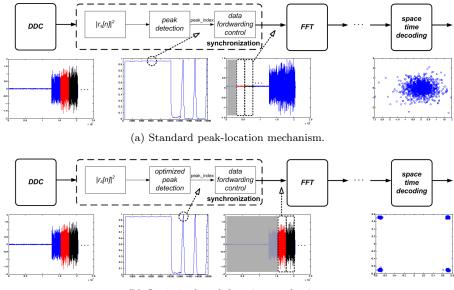

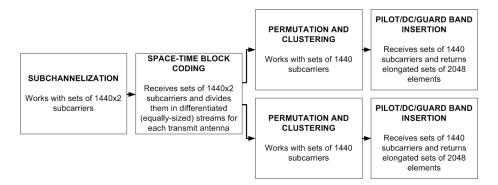

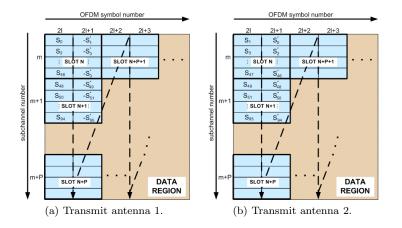

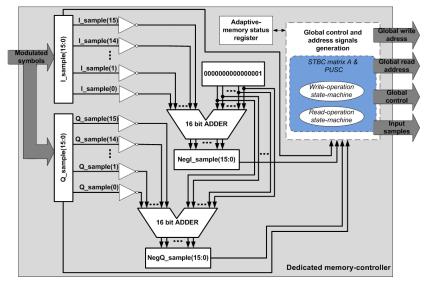

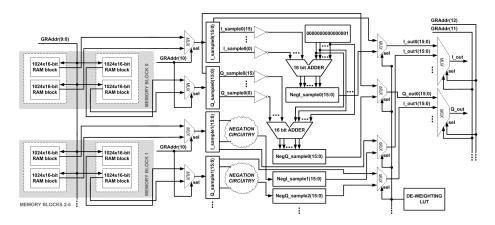

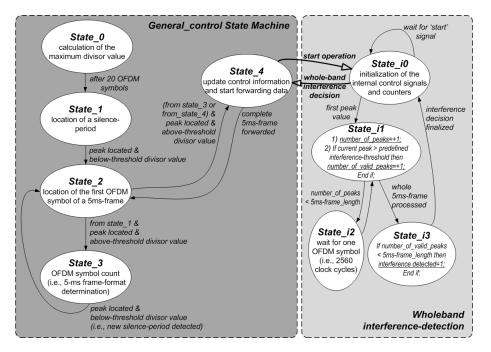

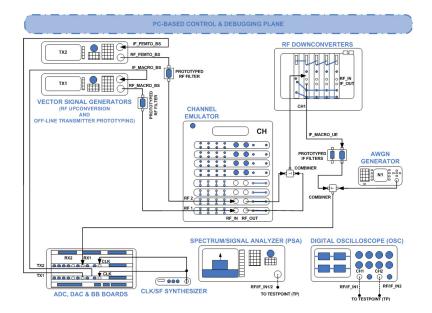

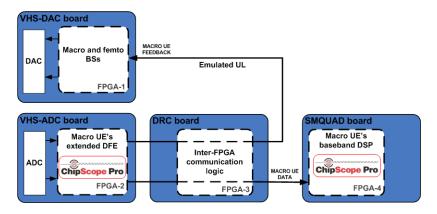

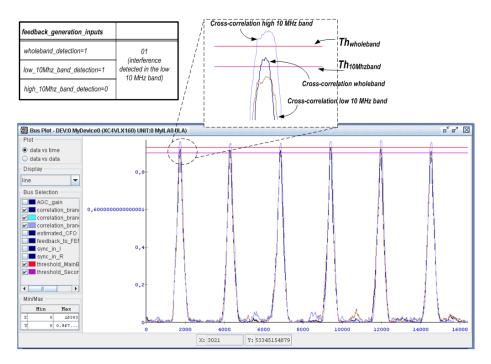

#### 2.1.2 Realistic PHY-layer modelling