**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

### Performance and Power Optimizations in Chip Multiprocessors for Throughput-Aware Computation

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Architecture Universitat Politècnica de Catalunya Barcelona, Spain

June 2013

## AUGUSTO J. VEGA

Thesis Advisors: Alex Ramírez Mateo Valero

Per Chiara

"Il tuo sorriso si espande

come una farfalla"

### Abstract

The so-called "power (or power density) wall" has caused core frequency (and single-thread performance) to slow down, giving rise to the era of multi-core/multi-thread processors. For example, the IBM POWER4 processor [97], released in 2001, incorporated two single-thread cores into the same chip. In 2010, IBM released the POWER7 processor [59] with eight 4-thread cores in the same chip, for a total capacity of 32 execution contexts. The ever increasing number of cores and threads gives rise to new opportunities and challenges for software and hardware architects. At software level, applications can benefit from the abundant number of execution contexts to boost throughput. But this challenges programmers to create highly-parallel applications and operating systems capable of scheduling them correctly. At hardware level, the increasing core and thread count puts pressure on the memory interface, because memory bandwidth grows at a slower pace phenomenon known as the "bandwidth (or memory) wall". In addition to memory bandwidth issues, chip power consumption rises due to manufacturers' difficulty to lower operating voltages sufficiently every processor generation. This thesis presents innovations to improve bandwidth and power consumption in chip multiprocessors (CMPs) for throughput-aware computation: a bandwidth-optimized last-level cache (LLC), a bandwidth-optimized vector register file, and a power/performance-aware thread placement heuristic.

In contrast to state-of-the-art LLC designs, our organization avoids data replication and, hence, does not require keeping data coherent. Instead, the address space is statically distributed all over the LLC (in a fine-grained interleaving fashion). The absence of data replication increases the cache

effective capacity, which results in better hit rates and higher bandwidth compared to a coherent LLC. We use double buffering to hide the extra access latency due to the lack of data replication.

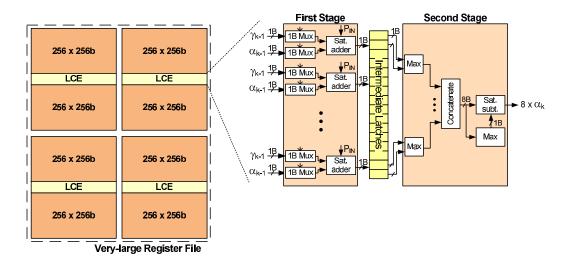

The proposed vector register file is composed of thousands of registers and organized as an aggregation of banks. We leverage such organization to attach small special-function *local computation elements* (LCEs) to each bank. This approach —referred to as the *processor-in-regfile* (PIR) strategy— overcomes the limited number of register file ports. Because each LCE is a SIMD computation element and all of them can proceed concurrently, the PIR strategy constitutes a highly-parallel super-wide-SIMD device (ideal for throughput-aware computation).

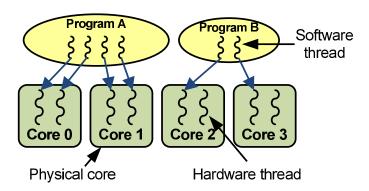

Finally, we present a heuristic to reduce chip power consumption by dynamically placing software (application) threads across hardware (physical) threads. The heuristic gathers chip-level power and performance information at runtime to infer characteristics of the applications being executed. For example, if an application's threads share data, the heuristic may decide to place them in fewer cores to favor inter-thread data sharing and communication. In such case, the number of active cores decreases, which is a good opportunity to switch off the unused cores to save power.

It is increasingly harder to find bulletproof (micro-)architectural solutions for the bandwidth and power scalability limitations in CMPs. Consequently, we think that architects should attack those problems from different flanks simultaneously, with complementary innovations. This thesis contributes with a battery of solutions to alleviate those problems in the context of throughput-aware computation: 1) proposing a bandwidth-optimized LLC; 2) proposing a bandwidth-optimized register file organization; and 3) proposing a simple technique to improve power-performance efficiency.

## Acknowledgments

There is a day that certainly changed my life. It was in 1990. I was ten years old when, one day at school, a teacher put in front of me a computer for the first time. It was a Commodore 64. It happened in a remote Argentinian village a long time ago. That day I will never forget.

After that first time, some people throughout my life helped me understand that, if working with computers was my dream, I had to do my best to pursue it. My parents, Miryam and Carlos, are the first ones in that "list". In the Spring Day of 1991 they got rid of a small motorcycle to buy me a Personal Computer XT. Seven years after I got my first computer, one day in 1998, they told me: "look, we have no wealth to bequeath you; but we can give you one thing: a university career." I then moved to Buenos Aires where I met Professor José Luis Hamkalo, a computer architecture researcher who opened me the doors of his lab for the first time. I then realized that I wanted to do processor architectures.

In 2007 I moved again, this time to cross the ocean. I started my Ph.D. at Universitat Politècnica de Catalunya, working as a Resident Student at the Barcelona Supercomputing Center. I want to especially thank Professors Alex Ramírez and Mateo Valero, my Ph.D. advisors, for giving me the opportunity to work with such a world-class group of researchers. Thanks!

I joined the IBM T.J. Watson Research Center in 2010, where I met the two most influential people in my professional life: Doctors Pradip Bose and Alper Buyuktosunoglu. With them, I discovered the *happiness* side of doing research, which is what really matters at the end of the day. With them, I finally became a researcher.

There is one special person around who my life revolves. Her name is

Chiara and she is my wife. Her support has been my source of strength since we met in Barcelona. And I hope I made sense to her life too. I dedicate this work to her.

I also want to thank Alex Rico and all the guys from BSC and UPC with whom I was fortunate to share unforgettable moments. Thanks to my sister too, María Inés, for those beautiful days of *mate y biscochitos* in Buenos Aires. You know how much I love you.

I could continue saying "thanks" to everyone who did their bit. To all of them, thanks for helping me to be a better person.

New York City Spring 2013 "Opportunity is missed by most people because it is dressed in overalls and looks like work."

Thomas A. Edison

## Contents

| 1        | Intr | oducti | ion                                              | 1 |

|----------|------|--------|--------------------------------------------------|---|

|          | 1.1  | Motiv  | ation                                            | 2 |

|          | 1.2  | Thesis | Statement                                        | 7 |

|          | 1.3  | Contr  | ibutions                                         | 7 |

|          |      | 1.3.1  | Bandwidth-Optimized Last-Level Cache             | 7 |

|          |      | 1.3.2  | Bandwidth-Optimized Register File                | 8 |

|          |      | 1.3.3  | Power Management Techniques for CMPs             | 8 |

|          | 1.4  | Summ   | ary and Concluding Remarks                       | 9 |

| <b>2</b> | Met  | hodol  | $_{ m ogy}$ 1                                    | 3 |

|          | 2.1  | Last-I | Level Cache Methodology                          | 3 |

|          |      | 2.1.1  | TaskSim                                          | 4 |

|          |      | 2.1.2  | CACTI                                            | 5 |

|          |      | 2.1.3  | Applications                                     | 7 |

|          | 2.2  | Regist | er File Methodology                              | 7 |

|          |      | 2.2.1  | In-Line Accelerator and Register File Model 1    | 8 |

|          |      | 2.2.2  | Performance Evaluation                           | 9 |

|          |      | 2.2.3  | Applications                                     | 0 |

|          |      | 2.2.4  | Area and Power Evaluation                        | 1 |

|          | 2.3  | Power  | Management Methodology                           | 1 |

|          |      | 2.3.1  | Experimental Platform                            | 1 |

|          |      | 2.3.2  | IBM Automated Measurement of Systems for Temper- |   |

|          |      |        | ature and Energy Reporting                       | 2 |

|          |      | 2.3.3  | POWER7 Performance Monitoring Unit 2             | 3 |

x CONTENTS

|   |     | 2.3.4 Applications                                                          | 24 |

|---|-----|-----------------------------------------------------------------------------|----|

| 3 | Las | z-Level Cache Design                                                        | 27 |

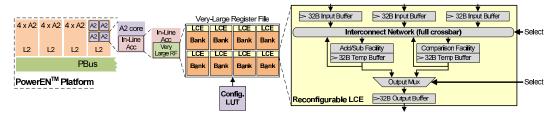

|   | 3.1 | Latency- vs. Bandwidth-Optimized Last-Level Caches                          | 28 |

|   | 3.2 | Last-level Cache Organization                                               | 32 |

|   |     | 3.2.1 Interleaving Granularity                                              | 34 |

|   |     | 3.2.2 Partitioned vs. With-Replication Scheme                               | 35 |

|   |     | 3.2.3 No-Write-Allocate Optimization                                        | 39 |

|   | 3.3 | Off-chip Memory Organization                                                | 39 |

|   | 3.4 | Summary and Concluding Remarks                                              | 41 |

| 4 | Reg | ister File Design                                                           | 43 |

|   | 4.1 | Wireless Base Stations                                                      | 45 |

|   | 4.2 | IBM PowerEN Processor                                                       | 46 |

|   | 4.3 | Area and Power Implications                                                 | 48 |

|   | 4.4 | Universal In-Line Accelerator                                               | 50 |

|   |     | 4.4.1 Programming Model                                                     | 51 |

|   |     | 4.4.2 Why Such a Large Register File?                                       | 52 |

|   |     | 4.4.3 Case Study: Fast Fourier Transform                                    | 53 |

|   | 4.5 | Processor-in-Regfile Strategy                                               | 54 |

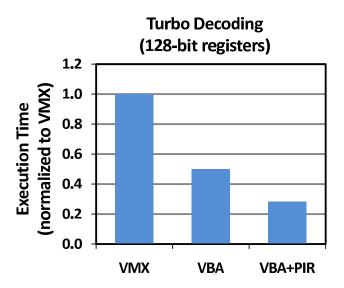

|   |     | 4.5.1 Case Study: Turbo Decoding                                            | 56 |

|   | 4.6 | Opportunities and Challenges                                                | 59 |

|   |     | $4.6.1  {\it Reconfigurable Processor-in-Regfile Architecture} \ . \ . \ .$ | 59 |

|   |     | 4.6.2 Challenges                                                            | 61 |

|   | 4.7 | Summary and Concluding Remarks                                              | 63 |

| 5 | Pov | ver Management                                                              | 65 |

|   | 5.1 | Thread Mapping and Thread Consolidation                                     | 70 |

|   | 5.2 | Thread Consolidation Efficiency (TCE)                                       | 72 |

|   | 5.3 | Thread Consolidation Opportunities and Value                                | 73 |

|   |     | 5.3.1 Fully Populated Scenarios                                             | 76 |

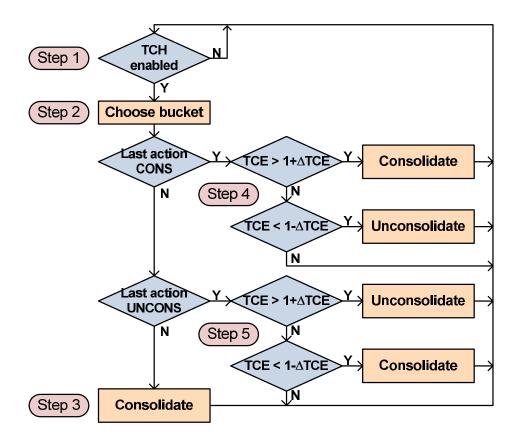

|   | 5.4 | Thread Consolidation Heuristic (TCH)                                        | 77 |

|   |     | 5.4.1 TCH Adjustment Knobs                                                  | 79 |

|   | 5.5 | TCH Evaluation                                                              | 81 |

| CONTENTS | xi |

|----------|----|

|          |    |

|   |      | 5.5.1 Analysis of Scenarios           |

|---|------|---------------------------------------|

|   | 5.6  | Per-Core Power Gating                 |

|   | 5.7  | Summary and Concluding Remarks        |

| 6 | Stat | te of the Art                         |

|   | 6.1  | Bandwidth-Optimized Last-Level Caches |

|   |      | 6.1.1 Commercial Products             |

|   |      | 6.1.2 Research Projects               |

|   | 6.2  | Throughput-Aware Register Files       |

|   |      | 6.2.1 Commercial Products             |

|   |      | 6.2.2 Research Projects               |

|   | 6.3  | Chip-Level Power Management           |

|   |      | 6.3.1 Commercial Products             |

|   |      | 6.3.2 Research Projects               |

|   | 6.4  | Summary and Concluding Remarks        |

| 7 | Pub  | olications 109                        |

|   | 7.1  | Last-Level Cache Design               |

|   | 7.2  | Register File Design                  |

|   | 7.3  | Power Management                      |

|   | 7.4  | Methodology and Tools                 |

|   | 7.5  | Other Publications                    |

| 8 | Con  | aclusions 113                         |

|   | 8.1  | Bandwidth-Optimized Last-Level Cache  |

|   | 8.2  | Bandwidth-Optimized Register File     |

|   | 8.3  | Power Management Techniques for CMPs  |

xii CONTENTS

# List of Figures

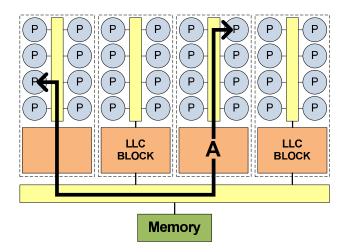

| 1.1 | Illustrative 32-core CMP, with the proposed LLC organization.         |    |

|-----|-----------------------------------------------------------------------|----|

|     | Eight cores per cluster share a local LLC block, and can access       |    |

|     | remote blocks (double buffering hides the extra latency). Data        |    |

|     | is not replicated in the LLC                                          | 4  |

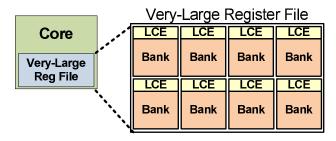

| 1.2 | Proposed very-large register file, in this case with eight banks      |    |

|     | and one LCE per bank. Each LCE provides SIMD computa-                 |    |

|     | tion support to its attached bank                                     | 5  |

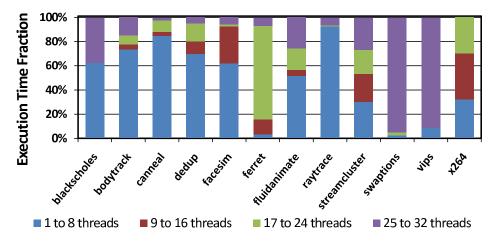

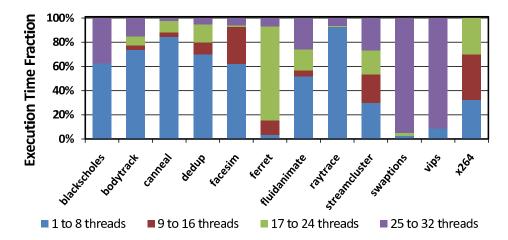

| 1.3 | Software thread count histogram for twelve multi-threaded             |    |

|     | PARSEC applications. Applications are executed with 32 soft-          |    |

|     | ware threads to fully populate the underlying POWER7 pro-             |    |

|     | cessor. Even in that case, applications are not able to exploit       |    |

|     | all the available hardware threads                                    | 6  |

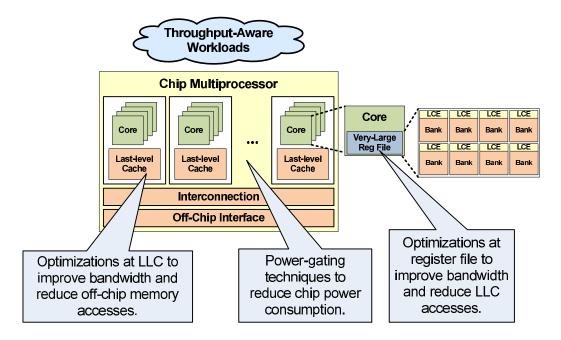

| 1.4 | Overview of the optimizations considered in this thesis               | 9  |

| 2.1 | Illustrative CMP architecture simulated in TaskSim. In this           |    |

|     | example, processing elements are clustered in groups of eight.        |    |

|     | Each processing element includes a CPU (core), a local mem-           |    |

|     | ory and a DMA engine. There is a LLC block per cluster, and           |    |

|     | all clusters are interconnected through a global network. A           |    |

|     | set of memory controllers are also modeled                            | 15 |

| 2.2 | Micro-architecture model of the in-line accelerator (source: [28]) 19 |    |

| 2.3 | Experimental system for the evaluation of the proposed thread         |    |

|     | consolidation heuristic (TCH)                                         | 23 |

|     |                                                                       |    |

| 3.1  | Illustrative 32-core CMP, with the proposed LLC organization.  In this particular example, eight cores per cluster share a local                                                                                                                                                                                              |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | LLC block. Because data is not replicated in the LLC, cores can also access remote blocks                                                                                                                                                                                                                                     | 28 |

| 3.2  | Evaluated DMA-based CMP architecture (LLC is not shown for sake of simplicity)                                                                                                                                                                                                                                                | 29 |

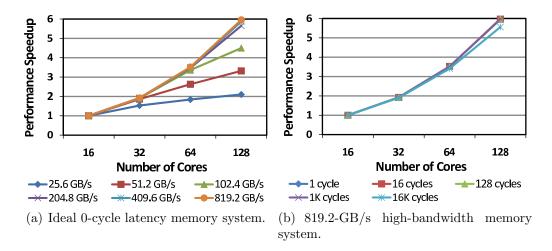

| 3.3  | Performance impact as a function of the number of cores in a DMA-based CMP. Due to the huge amount of parallelism in the applications, memory access latency can be hidden, and data bandwidth becomes the limiting factor. Results are averaged for all considered kernels. Performance is measured as total execution time. | 31 |

| 3.4  | Evaluated last-level cache alternatives                                                                                                                                                                                                                                                                                       | 32 |

| 3.5  | Evaluated last-level cache alternatives                                                                                                                                                                                                                                                                                       | 33 |

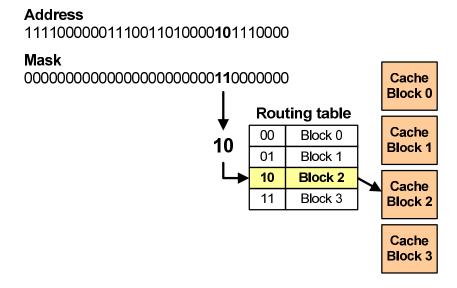

| 3.6  | Example of the mechanism employed in our LLC to map a particular memory address into a LLC block                                                                                                                                                                                                                              | 34 |

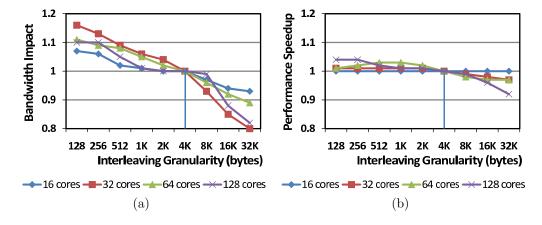

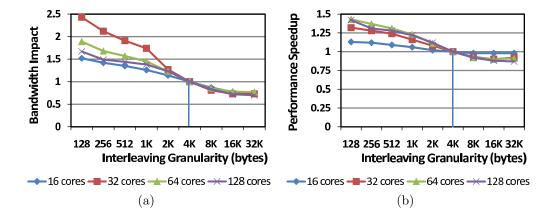

| 3.7  | Impact on (a) bandwidth and (b) performance of last-level cache interleaving granularity. Results are normalized to the 4-KB interleaving case. Performance is measured as total execution time.                                                                                                                              | 35 |

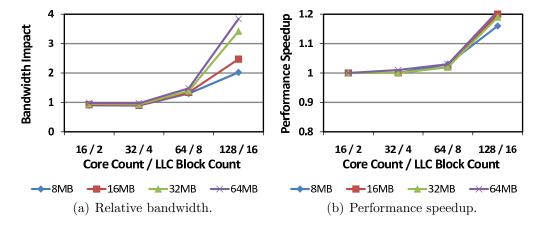

| 3.8  | Partitioned LLC vs. an organization with data replication.  For a particular number of workers (each point in X-axis), results are with respect to the organization with data replication.  Performance is measured as total execution time                                                                                   | 36 |

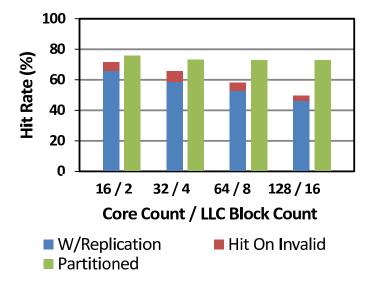

| 3.9  | Hit rate as a function of the number of cores, averaged for all considered kernels. Results correspond to a LLC with data replication and data coherence ("W/Replication") and the proposed partitioned LLC ("Partitioned")                                                                                                   | 37 |

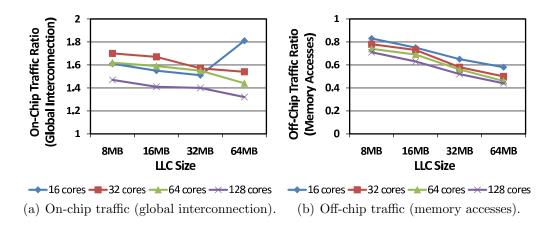

| 3.10 | Partitioned LLC vs. an organization with data replication.  For a particular LLC size (each point in X-axis), results are with respect to the organization with data replication                                                                                                                                              | 38 |

LIST OF FIGURES xv

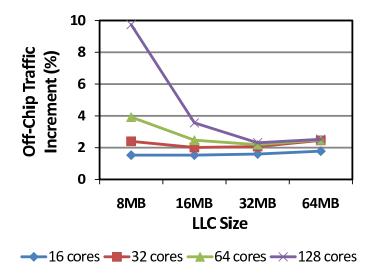

| 3.11 | Increment in the number of off-chip accesses when write allocation is enabled. For a particular LLC size (each point in X-axis), results are with respect to the organization with write-allocation disabled                                                                                                                                                                                                                                                                                                              | 40      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.12 | Impact on (a) bandwidth and (b) performance of memory interleaving granularity. Results are normalized to the 4-KB interleaving case. A 64-MB LLC with 128-byte interleaving is                                                                                                                                                                                                                                                                                                                                           |         |

|      | considered. Performance is measured as total execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41      |

| 4.1  | IBM PowerEN processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47      |

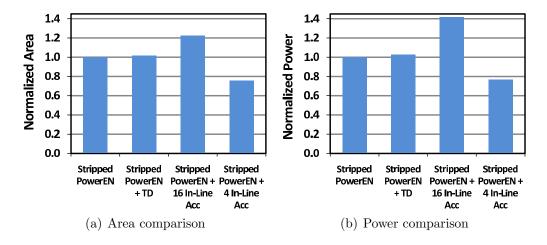

| 4.2  | Normalized area and power comparison for four particular configurations: a PowerEN without bus-attached accelerators ("Stripped PowerEN"), a stripped PowerEN with a bus-attached Turbo Decoding accelerator ("Stripped PowerEN + TD"), a stripped PowerEN with 16 in-line universal accelerators ("Stripped PowerEN + 16 In-Line Acc") and a stripped PowerEN with 4 in-line universal accelerators to target pico and femto base stations ("Stripped PowerEN + 4 In-Line Acc")                                          | d<br>49 |

| 4.3  | Organization of the 8-bank register file with 8 embedded LCEs.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55      |

| 4.4  | 8-bank 4-LCE register file organization for Turbo Decoding. Each LCE decodes the sub-blocks stored in its attached banks. The LCE is organized in a two-stage two-cycle pipeline, with an intermediate latch-based buffer between stages. The use of the two stages is multiplexed in time to hide the latency. Each "1B Mux" selects a 1-byte $\alpha$ or $\gamma$ value from one of the 32-byte input registers. The output of the second stage is a set of eight 1-byte $\alpha$ values corresponding to time step $k$ | 57      |

| 4.5  | Normalized execution time to decode a 6144-bit codeword in six iterations. "VMX" is a scenario with a 32-entry vector register file, "VBA" incorporates a 2048-entry VSRF and in "VBA+PIR", four LCEs are embedded into the VSRF. In all the cases, 256-bit vector registers are considered                                                                                                                                                                                                                               | 58      |

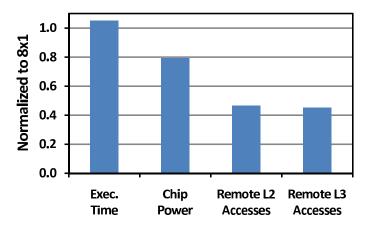

| <ul> <li>5.1 Allocation of six software threads (four belonging to program "A" and two to program "B") across eight hardware threads, in a 4-core 2-way SMT CMP. From a program standpoint, hardware threads are "seen" as eight logical cores. In most cases, the operating system maps software threads into hardware threads and cores</li> <li>5.2 Dedup application with eight software threads executed in POWER7. In one configuration, each software thread is pinned</li> </ul> | 61 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |

| to a different core ("8x1": eight cores with one software thread each), while in other configuration two software threads are pinned per core ("4x2": four cores with two software threads each). Figure presents execution time, chip power consumption and accesses to remote cores' caches. The results are                                                                                                                                                                           | 68 |

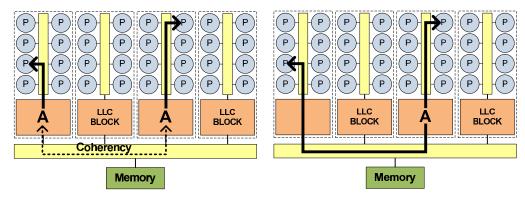

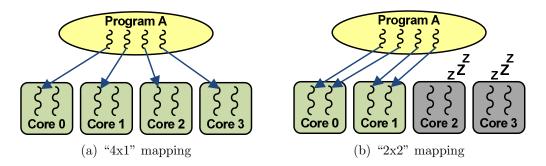

| 5.3 Placement of four software threads belonging to a multi-threaded application across four 2-way SMT cores. In 5.3(a), each software thread is assigned to a different core ("4x1" mapping).In 5.3(b), two software threads are assigned per core after consolidation. Unused cores can be leveraged to either save power or boost throughput                                                                                                                                          | 71 |

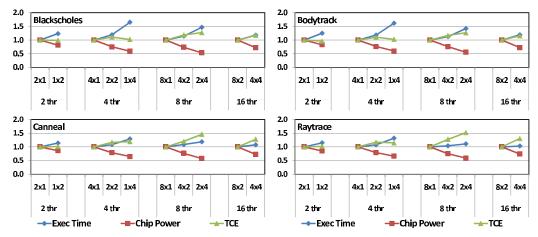

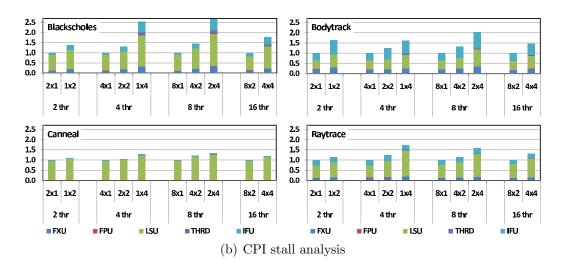

| 5.4 Static mapping analysis for four multi-threaded PARSEC applications on POWER7. Each application is executed with 2, 4, 8 and 16 software threads. For each software thread count, all possible mappings are considered. In each group, the results are normalized to the first configuration                                                                                                                                                                                         | 75 |

| 5.5 Software thread count histogram for twelve multi-threaded PARSEC applications. Applications are executed with 32 software threads to fully populate the underlying POWER7 processor. Even in that case, applications are not able to exploit all the available hardware threads                                                                                                                                                                                                      | 77 |

LIST OF FIGURES xvii

| 5.6  | Thread consolidation heuristic (TCH)                                 | 78 |

|------|----------------------------------------------------------------------|----|

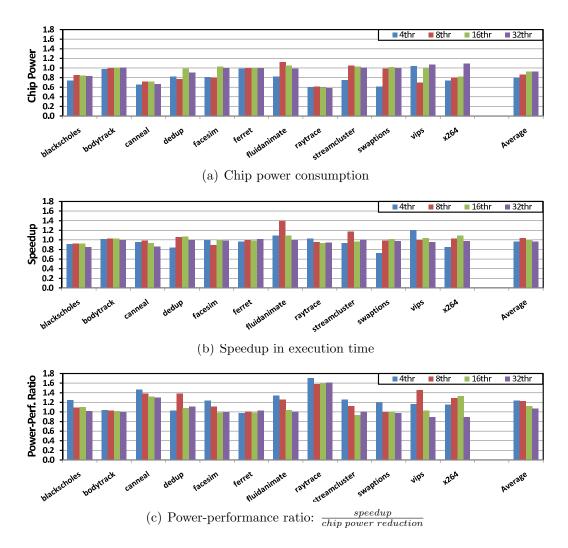

| 5.7  | TCH vs. the default Linux scheduler in an IBM BladeCen-              |    |

|      | ter PS701 system, in terms of chip power consumption (Fig-           |    |

|      | ure 5.7(a)) and performance (Figure 5.7(b)). Figure 5.7(c)           |    |

|      | presents the power-performance ratio: values larger than one         |    |

|      | mean better power-performance efficiency. The results corre-         |    |

|      | spond to all PARSEC applications executed with 4, 8, 16 and          |    |

|      | 32 software threads                                                  | 82 |

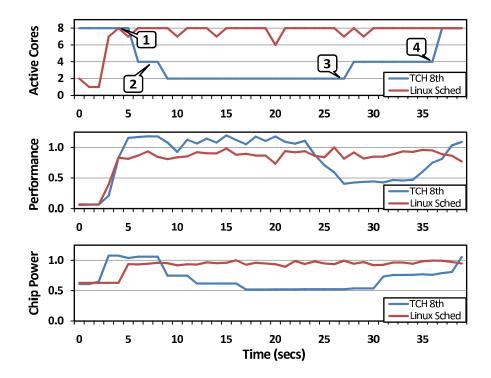

| 5.8  | Number of active cores (top), performance (middle) and chip          |    |

|      | power consumption (bottom) when X264 is executed under               |    |

|      | both TCH and Linux scheduler supervision. Performance and            |    |

|      | chip power curves are normalized to the maximum value in             |    |

|      | the Linux scheduler case                                             | 86 |

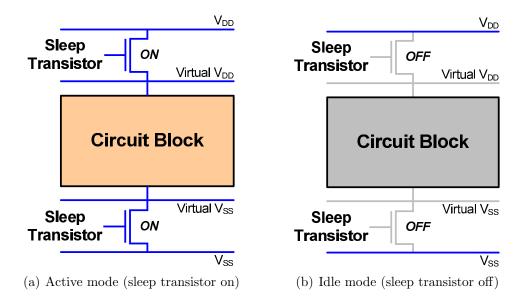

| 5.9  | Power gating operation. In Figure 5.9(a), header and footer          |    |

|      | sleep transistors are $on$ and, therefore, the circuit block is ac-  |    |

|      | tive. In Figure $5.9(b)$ , sleep transistors are off and the circuit |    |

|      | block is power gated                                                 | 87 |

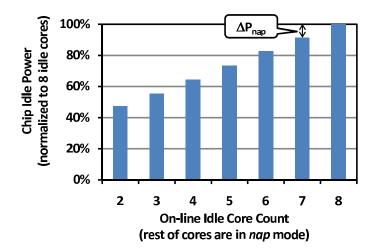

| 5.10 | POWER7 chip power consumption for different numbers of               |    |

|      | on-line idle cores, normalized to the eight on-line cores case.      |    |

|      | Off-line cores remain in $nap$ idle state, which deactivates in-     |    |

|      | struction fetch and execution and turns off all clocks to the        |    |

|      | execution engines in the core, but it still keeps L2 and L3          |    |

|      | caches coherent $[35]$                                               | 89 |

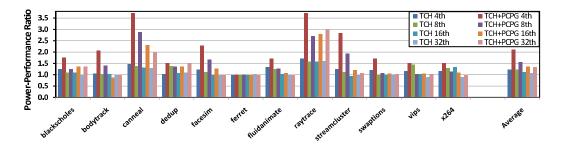

| 5.11 | TCH+PCPG vs. the default Linux scheduler in an IBM Blade-            |    |

|      | Center PS701 system, in terms of power-performance efficiency        |    |

|      | (values larger than one mean that chip power reduction is            |    |

|      | larger than performance degradation). The results correspond         |    |

|      | to all PARSEC applications executed with $4,8,16$ and $32$ soft-     |    |

|      | ware threads. Per-core-chiplet power reduction and PCPG              |    |

|      | latency are based on estimations                                     | 90 |

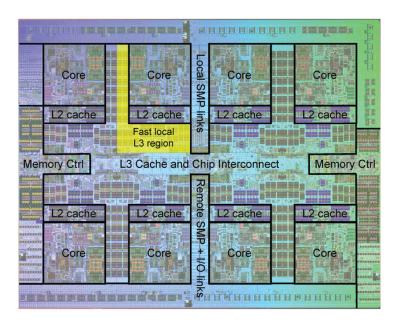

| 6.1  | IBM POWER7 die photo (source: [92])                                  | 94 |

|      | ± \ L 1/                                                             |    |

## List of Tables

| 2.1 | Simulated architectural parameters                          | 16  |

|-----|-------------------------------------------------------------|-----|

| 2.2 | CACTI input parameters used to estimate LLC block access    |     |

|     | latency.                                                    | 17  |

| 2.3 | Simulated benchmarks                                        | 18  |

| 2.4 | Simulated A2 core architectural parameters                  | 20  |

| 2.5 | POWER7 performance events measured by the proposed heuris-  |     |

|     | tic                                                         | 24  |

| 2.6 | Adopted PARSEC benchmarks (source: [12])                    | 25  |

| 4.1 | Required logic for radix-8 FFT and Turbo Decoding compu-    |     |

|     | tation at LCE level                                         | 61  |

| 5.1 | Selected TCH configuration parameters and ranges explored   | 80  |

| 6.1 | Comparison between POWER7 LLC, Xeon LLC and the or-         |     |

|     | ganization presented in this thesis                         | 95  |

| 6.2 | A comparative summary of a register file with embedded SIMD |     |

|     | support and a GPU streaming multiprocessor                  | 101 |

## Chapter 1

### Introduction

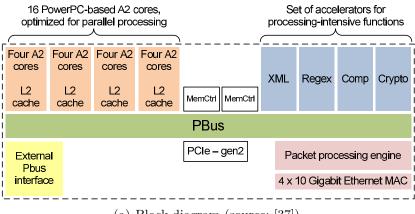

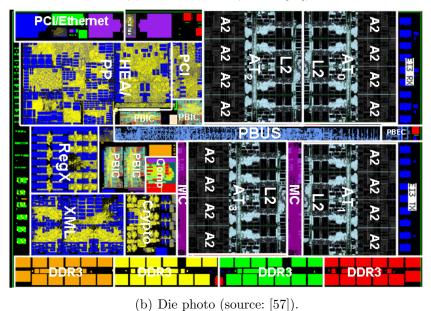

The well-known limits to transistor miniaturization gave rise to a variety of multi-threaded and multi-core processors. Since early 2000s, the number of threads in a core and the number of cores in a chip have been growing steadily as an answer to the concerns about Moore's Law sustainability. This trend crosses different design domains, from general-purpose processors, to graphics processing units (GPUs), to hybrid processors. In the general-purpose computation domain, the IBM POWER7 processor [59, 104] incorporates eight cores in the same chip, each one with four hardware threads. Intel's Xeon E5 processor family [49], based on the Sandy Bridge-EN and Sandy Bridge-EP architecture, has up to six cores, two threads each. In the GPUdomain, we can mention the NVIDIA GeForce GTX 580 GPU [74] (based on the Fermi micro-architecture [76]), with 512 CUDA cores in the same chip. More recently, NVIDIA has introduced the Tesla K-series GPU accelerator family based on the NVIDIA Kepler architecture [77] with up to 2688 CUDA cores. In the hybrid computation domain—i.e., designs combining general-purpose cores, with GPUs and/or other types of accelerators—, AMD released in 2011 the Llano [16] variant of the Fusion accelerated processor unit (APU) [4]. Llano integrates four x86 cores and a Radeon-based GPU into the same chip. The IBM PowerEN processor [17, 37, 57] is composed of 16 PowerPC-based cores, four threads each, plus six hardware accelerators. We also have to mention the IBM Cell/B.E. processor [58] with eight Synergistic Processing Elements (SPEs) attached to a POWER-based processor, intended for multimedia and vector processing applications.

There are two ways to exploit the growing number of execution contexts (i.e., physical threads and cores) in current chip multiprocessors (CMPs): an application can be parallelized using a parallel programming models (e.g. POSIX threads [20], OpenMP [22] or CUDA [75], among others), or multiple non-parallelizable applications can be executed at the same time, one per thread or per core. Throughout this thesis, we refer to the former model as multi-threaded execution, and to the latter as multi-programmed execution. Also, whenever we refer to physical threads at core level, we mean Simultaneous Multi-Threading (SMT) [103].

Regardless of the parallel execution model, threads and/or programs share CMP's resources, which poses new architectural challenges. This dissertation tackles two of those challenges, which we consider key in the context of throughput-aware computation:

- Memory bandwidth how to efficiently share the available memory bandwidth between physical threads and cores in the chip.

- Power consumption how to manage the chip power budget in order to achieve power-proportional computation [8].

In this thesis, we employ the term *throughput-aware computation* to refer to scenarios with abundant parallelism, either in the form of multiple threads or multiple single-threaded applications running at the same time.

#### 1.1 Motivation

In the last years, new designs were introduced in the growing domain of chip multiprocessors (CMPs). We provided examples of such designs in the previous section, categorized as: general-purpose computation (IBM POWER7, Intel Xeon E5), graphical computation (NVIDIA's Fermi and Kepler-based GPUs) and hybrid computation (AMD Llano, IBM PowerEN, IBM Cell/B.E.). The number of execution contexts (threads and cores) in CMPs has been

steadily growing to mimic Moore's Law. Today, we can find designs with tens or hundreds of execution contexts: e.g. 32 threads in IBM POWER7 (grouped in eight 4-way SMT cores) or 512 threads in NVIDIA GeForce GTX 580. This enables unprecedented levels of parallelism, which is ideal for throughput-aware computation [40, 73]. Examples of throughput-aware applications are: real-time computer graphics and video processing, signal processing, medical-image analysis, molecular dynamics, astrophysical simulation, and gene sequencing [40]. The most important characteristic of these applications is that they can be decomposed into data blocks for massively parallel processing.

The memory system in throughput-aware designs can be organized based on two models: hardware-managed coherent caches and software-managed streaming memory [64]. In the latter case, the processor usually incorporates per-core local memories and transfers data to and from those memories using direct memory accesses (DMAs). DMA transfers overlap computation to hide latency—technique known as double buffering [23, 89]. The double buffering technique requires large-enough local (scratchpad) memories to keep both, the data being processed and the data being prefetched from the memory system to be processed next. As an example, each Synergistic Processing Element (SPE) in the Cell/B.E. architecture [58] has a 256-KB local memory. A SPE-level DMA engine transfers data between this memory and main memory using high-bandwidth DMAs.

The double buffering technique is an effective way to tolerate high memory latencies. But the increment in the number of cores in current CMPs moved the problem from the *latency* side to the *bandwidth* side. It is not enough anymore to feed a core with data quickly. It is also mandatory to feed many cores. The memory bandwidth became the key limiter for performance scalability. For example, with only eight SPEs, the Cell/B.E. already had to resort to a high bandwidth Rambus XDR memory system to deliver 25.6 GB/s [58]. The POWER7, with eight 4-way SMT cores, incorporates two four-channel DDR3 memory controllers, delivering up to 100 GB/s [92]. The NVIDIA GeForce GTX 580 GPU feeds its 512 threads with a 192.4 GB/s DDR5 memory system [74].

The underlying problem about memory bandwidth is that it grows much slower than the number of cores. Bandwidth scalability is mainly limited by chip pin count and power consumption. Adopting large on-chip memories and caches can reduce memory pressure due to temporal reuse of data. However, off-chip memory pressure is heavily exacerbated by the increasing number of cores and threads [42], particularly true for highly parallel applications, to the point where *just* large caches are not the solution anymore. Based on this motivation, we focus on two key parts of the memory system: the last-level cache and the register file.

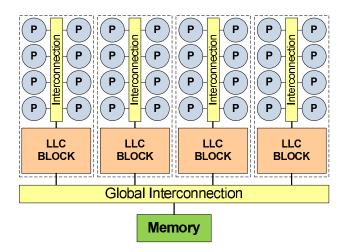

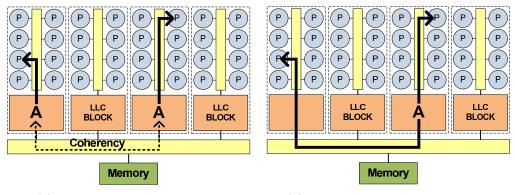

In the last-level cache (LLC), we leverage the benefits of the software-managed streaming memory model with DMA transfers. The main idea is to avoid data replication (and coherence requirements) in the LLC. Instead, cores are allowed to access remote cores' caches. Figure 1.1 shows an illustrative CMP with 32 cores grouped in four clusters. Cores in each cluster share a local LLC block, and can also access other clusters' LLCs. With this strategy, each core "sees" a much larger LLC, which is beneficial for bandwidth. We use double buffering to hide the extra latency to access remote blocks. The LLC organization proposed in this thesis is presented in Chapter 3.

Figure 1.1: Illustrative 32-core CMP, with the proposed LLC organization. Eight cores per cluster share a local LLC block, and can access remote blocks (double buffering hides the extra latency). Data is not replicated in the LLC.

5

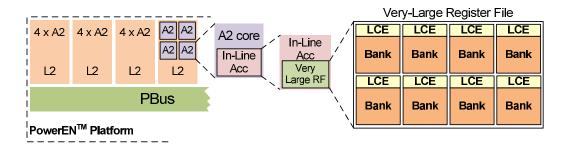

To further reduce the pressure on the memory system, we adopt a very-large vector register file. The goal is to keep data as much as possible in the register file to reduce accesses to the cache hierarchy. The register file considered in this thesis, which has thousands of vector registers, is presented by Derby et al. in [29] in the context of an in-line accelerator. In this thesis, we implement such organization with multiple banks, which provides a twofold benefit: it keeps wire propagation delay under control, and allows to exploit local computation in each bank. As explained in Chapter 4, this processing capability at register file level is implemented with embedded, small Single Instruction, Multiple Data (SIMD) local computation elements (LCEs) attached to each bank. Figure 1.2 shows an 8-bank register file with one LCE per bank.

Figure 1.2: Proposed very-large register file, in this case with eight banks and one LCE per bank. Each LCE provides SIMD computation support to its attached bank.

In addition to memory bandwidth, chip power consumption is the other key obstacle to CMP performance scalability. The "power wall" issue is so critical that has given rise to a new research field in microprocessor architectures: to minimize transistor under-utilization (dark silicon) [33]. The underlying problem about dark silicon is that the available energy/power budget in today's CMPs prevents having 100% of the chip powered on all the time. For example, at 22nm, 21% of a chip must be powered off due to power consumption constraints [33]. Therefore, it is crucial to understand what parts of the chip can be powered off during execution, in order to reduce energy/power consumption, with minimal performance impact. Even on highly-parallel applications, it is possible to identify computation phases

in which not all chip resources are exercised. Figure 1.3 presents the software thread count frequency for twelve PARSEC multi-threaded applications [12] executed with 32 software threads and *native* inputs on an IBM POWER7 processor. As can be observed, multi-threaded applications spend significant time with fewer threads than the specified thread count (just Swaptions and Vips execute with 32 threads most of the time). In such scenarios, we may decide to power off unused resources (e.g. cores) whenever possible to save energy and power. In this thesis we propose and evaluate a thread consolidation heuristic (TCH) which optimizes processor power-performance efficiency based on applications characteristics. TCH —which is implemented as a simple closed-loop control algorithm at operating system level—gets runtime chip-level power and performance information to infer characteristics of the applications being executed. Based on this information, the heuristic decides how to distribute software (application-level) threads across hardware (physical) threads and cores in a CMP to optimize power-performance efficiency. We describe the implementation details of this heuristic in Chapter 5.

Figure 1.3: Software thread count histogram for twelve multi-threaded PAR-SEC applications. Applications are executed with 32 software threads to fully populate the underlying POWER7 processor. Even in that case, applications are not able to exploit all the available hardware threads.

#### 1.2 Thesis Statement

Performance scalability of current CMPs is mainly constrained by memory bandwidth and chip power consumption.

Memory systems (including register files, caches, interconnections and memory controllers) are optimized for latency, which is supported by data replication and coherence. We argue that adopting latency-optimized memory systems in the domain of throughput-aware computation requires a thorough analysis. Throughput-aware computation is mostly bandwidth bound, instead of latency bound.

Chip power consumption is the other key factor that limits the amount of logic that can turned on in a modern CMP. We argue that power management techniques have to be incorporated into the chip and/or system software (e.g. operating system kernel). The goal is to attain power-proportional computation, by power gating unused chip components (e.g. functional units, cores, memory controllers, etc.).

The main goal of this dissertation is to improve CMP performance scalability in the context of throughput-aware computation, by tackling the memory bandwidth and power consumption issues. This goal is achieved with new bandwidth-optimized last-level cache and register file organizations, and a heuristic for chip power reduction.

#### 1.3 Contributions

In this thesis we evaluate optimizations to improve performance and power consumption of CMPs under throughput-aware workloads. We next summarize the main contributions of this thesis (an overview is shown in Figure 1.4).

#### 1.3.1 Bandwidth-Optimized Last-Level Cache

A re-design of the last-level cache (LLC) targeting throughput-aware computation. We present a bandwidth-optimized LLC organization that is suitable for throughput-aware computation on CMPs. Its most important character-

istics are the following:

- We avoid data replication to improve effective capacity. Since data is not replicated in the cache, there is no need to deal with coherence issues.

- We statically distribute the address space across cache blocks in a finegrained interleaving fashion.

The benefit of our LLC organization is twofold: its larger effective capacity delivers higher bandwidth (more data is kept in the LLC, which results in fewer off-chip memory accesses), and the fine-grained address space interleaving allows multiple transfers to proceed in parallel. These benefits come at the expense of locality, due to data being spread all over the available storage. While this trade-off is harmful for latency-aware computation, it is beneficial for throughput-aware workloads.

#### 1.3.2 Bandwidth-Optimized Register File

A very-large register file that significantly cuts down the number of memory accesses. It is conceived as an aggregation of banks to keep wire propagation delay under control. Such organization unveils an additional optimization opportunity: SIMD computation support embedded into the register file. This processor-in-regfile (PIR) strategy is implemented as small special-function local computation elements (LCEs) attached to each bank. This approach overcomes the limited number of register file ports. Each LCE is a SIMD computation element, and all of them can proceed concurrently. Therefore, the PIR strategy constitutes a highly-parallel super-wide-SIMD approach, ideal for throughput-aware computation.

#### 1.3.3 Power Management Techniques for CMPs

A heuristic that improves power-performance efficiency in CMPs by dynamically placing parallel applications across physical threads and cores. The heuristic —which is implemented as a simple closed-loop control algorithm

at operating system level— gets runtime chip-level power and performance information to infer characteristics of the applications being executed. For example, if an application's threads share data, the heuristic may decide to place them in fewer cores (at higher SMT level) to favor inter-thread data sharing and communication. In such case, the number of active cores decreases, which is a good opportunity to switch off the unused cores to save power.

Figure 1.4: Overview of the optimizations considered in this thesis.

#### 1.4 Summary and Concluding Remarks

This thesis evaluates optimizations to improve memory bandwidth and chip power consumption in the context of CMPs for throughput-aware computation.

Throughput-aware applications differ from traditional latency-aware applications in that they can be decomposed into data blocks for massively parallel processing. This abundant amount of parallelism increases the mem-

ory bandwidth pressure. Consequently, the adoption of caches optimized for latency in the domain of throughput-aware computation has to be done thoroughly: in throughput-aware scenarios, the memory system has to be designed to tackle the "bandwidth wall" instead of the "latency wall". The bandwidth wall, and its implications on CMP performance scalability, motivates us to propose a last-level cache (LLC) and a register file organizations aimed for throughput-aware computation.

The proposed LLC is composed of a set of independent blocks but neither multiple copies nor block migration between them is allowed. Instead, data is statically interleaved across LLC blocks in a fine-grained fashion. This approach delivers more bandwidth at the expense of higher access latency—we use double buffering to hide this extra latency.

The proposed register file is a very large storage with thousands of registers, conceived as an aggregation of banks. We attach a small SIMD local computation elements (LCEs) to each bank. This processor-in-regfile (PIR) strategy overcomes the limited number of register file ports: all the LCEs can proceed concurrently, reading/writing registers from/to its attached register file bank. The PIR strategy and the large register file capacity (tens of kilobytes) enable a novel computation model, suitable for throughput-aware domains: substantial performance gains can be obtained by loading relatively large blocks of data into the register file (e.g. a cache-line at a time), operating on the entire block of data, keeping intermediate results in the register file, and storing the final results to memory a cache-line at a time. The proposed register file organization provides further advantage when the produced result is used as the input to another function, a common scenario in throughput-aware computation. For instance, in graphics processing, a JPEG compressor applies a chain of functions to the input image. With the proposed register file organization, the entire image (or a large part of it) resides in the register file while the LCEs apply the different functions in situ.

In addition to the bandwidth-optimized LLC and register file, we also propose a heuristic that optimizes CMP power-performance efficiency. The heuristic —which is implemented as a simple closed-loop control algorithm

at operating system level— gets runtime chip-level power and performance information to decide which is the most efficient way to distribute software threads across hardware threads and cores. The goal is to place software threads in as few cores as possible to reduce power consumption on unused cores, with minimal performance impact.

In conjunction, the techniques presented in this thesis (either for bandwidth and power optimization) are intended to alleviate CMP performance scalability limitations in the context of throughput-aware computation.

## Chapter 2

## Methodology

This chapter describes the tools and methodology adopted throughout the development of this thesis. This includes analytical models, simulators, real hardware platforms, applications and other resources. As it was explained in Chapter 1, this thesis focuses on architectural innovations at three different CMP components: the last-level cache (LLC), the register file and core-level power gating —the presentation of the methodology is organized following that same structure.

#### 2.1 Last-Level Cache Methodology

We model the LLC organizations as part of TaskSim, a trace-driven cycle-accurate CMP simulator [83, 84]. The author of this thesis was part of the Heterogeneous Computer Architecture group at Barcelona Supercomputing Center, the team that developed TaskSim. We present TaskSim in Section 2.1.1.

We use CACTI to estimate the access latency of the LLCs modeled in TaskSim. CACTI is a model for cache access time, area and power developed by HP Labs [102]. We present CACTI in Section 2.1.2.

We adopt a set of parallel scientific kernels to generate the traces to use in TaskSim. We present the details of these applications and the trace generation process in Section 2.1.3.

#### 2.1.1 TaskSim

TaskSim is a trace-driven cycle-accurate modular simulator [83, 84] which targets large-scale multi-core architectures. TaskSim's most important characteristic is its ability to accurately model large-scale CMPs: tens or hundreds of cores, interconnections, complete cache hierarchy and memory system. This ability relies on the use of a task-level abstraction for the internal simulation of cores. This means that TaskSim does not capture intra-core micro-architectural behavior. The rest of the components (interconnections, cache hierarchy and memory controllers) are realistically modeled at cycle level. The lack of micro-architectural core details in the model is irrelevant to accurately evaluate the LLCs, while it also provides fast simulation.

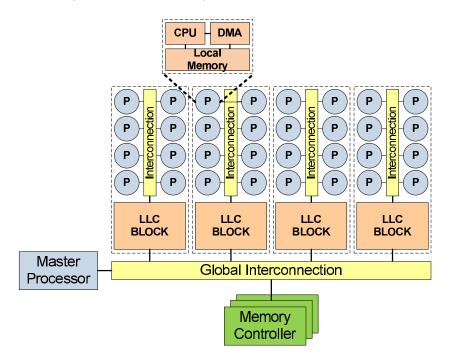

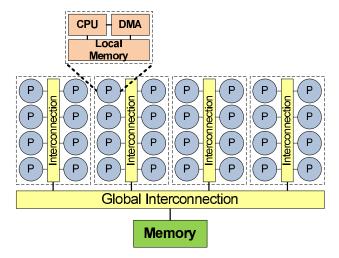

Figure 2.1 presents a high-level diagram of the CMP components that can be modeled using TaskSim. The simulator implements the different components as *modules* which are interconnected through *ports*. Our case study, shown in Figure 2.1, is a Cell/B.E.-like architecture with 32 processing elements (workers), each one composed of a CPU (core), a local memory and a DMA engine. Processing elements group together in clusters and share a local LLC block. A global network interconnects clusters and a set of memory controllers. In addition, a master processor is responsible for assigning tasks to processing elements, which resembles the master-worker execution model in the IBM Cell/B.E. processor [58]. We leverage TaskSim modularity to model a variety of configurations, with different numbers of processing elements and LLC blocks.

Table 2.1 summarizes the main architectural parameters adopted for the LLC evaluation of Chapter 3. The number of processing elements simulated are 16, 32, 64 and 128 in clusters of eight (i.e. 2, 4, 8 and 16 clusters, respectively). The LLC is partitioned in one block per cluster and modeled as embedded DRAM (eDRAM) [5, 55, 56]. The LLC sizes simulated are 8, 16, 32 and 64 MB. The access to LLC data is based on two schemes: *interleaved* and *non-interleaved*. The former does not replicate data in the LLC —instead, the address space is interleaved across blocks. The latter corresponds to a traditional coherence-based organization where data can be replicated across

LLC blocks. Chapter 3 presents the evaluation of these two LLC schemes. We model global and in-cluster interconnections as 8-byte/cycle full-crossbar networks, and the memory interface as four 25.6-GB/s memory controllers (for a 102.4-GB/s total bandwidth).

Figure 2.1: Illustrative CMP architecture simulated in TaskSim. In this example, processing elements are clustered in groups of eight. Each processing element includes a CPU (core), a local memory and a DMA engine. There is a LLC block per cluster, and all clusters are interconnected through a global network. A set of memory controllers are also modeled.

#### 2.1.2 CACTI

CACTI is a tool capable of finding optimal cache configurations in terms of access time, along with its power and area characteristics [102]. In this thesis, we adopt CACTI version 5.3 to determine the access latency corresponding to the different LLC configurations evaluated. Table 2.2 summarizes some of the most relevant CACTI input parameters chosen. Because we are interested in the access latency of one LLC block, the cache size parameter corresponds to

| Component        | Configuration                                     |

|------------------|---------------------------------------------------|

| Processing       | 16, 32, 64 and 128 processing elements (eight per |

| elements         | cluster)                                          |

|                  | Core frequency: 3.2 GHz                           |

|                  | Local memory size: 256 KB (one local memory       |

|                  | per core)                                         |

|                  | DMA engine: up to 16 concurrent DMAs, 128-        |

|                  | byte DMA packages                                 |

| Last-level cache | 4-way set associative, 45nm eDRAM, 128-byte       |

|                  | lines                                             |

|                  | Size: 8, 16, 32 and 64 MB                         |

|                  | Blocks: 2, 4, 8 and 16 (one LLC block per clus-   |

|                  | ter)                                              |

|                  | Ports: 2 read/write ports per LLC block           |

|                  | Data placement policies: interleaved and with     |

|                  | replication                                       |

|                  | MSHR: 64 entries each (one independent MSHR       |

|                  | per LLC block)                                    |

| Interconnections | 8 bytes/cycle bandwidth, full-crossbar network    |

| Memory system    | 4 memory controllers at 25.6 GB/s each            |

|                  | (102.4 GB/s total)                                |

Table 2.1: Simulated architectural parameters.

the size of the block and not the entire LLC. This size varies as a consequence of the difference LLC sizes and number of blocks explored, which are listed in Table 2.1. A LLC block is composed of one or more physical banks. In this thesis we assume a physical bank size of 512 KB. Therefore, the number of banks depends on the LLC block size. The smallest LLC block size simulated is 512 KB, which is implemented with just one physical bank. The largest LLC block size is 32 MB, which is implemented with 64 banks. To model eDRAM-based LLCs, the data and tag array cell type adopted is logic process based DRAM (LP-DRAM) [101].

| Parameter                              | Value           |

|----------------------------------------|-----------------|

| Cache sizes (LLC block sizes)          | 512 KB to 32 MB |

| Line size                              | 128 bytes       |

| Associativity                          | 4               |

| Banks                                  | 1 to 64         |

| Technology Node                        | 45 nm           |

| Read/Write Ports                       | 2               |

| RAM cell/transistor type in data array | LP-DRAM         |

| RAM cell/transistor type in tag array  | LP-DRAM         |

| Interconnect projection type           | Conservative    |

Table 2.2: CACTI input parameters used to estimate LLC block access latency.

### 2.1.3 Applications

In TaskSim, the master and worker CPU modules are fed with traces of scientific applications written using a task-based programming model. The traces are sequences of tasks that the master processor schedules on worker processors. The LLC evaluation presented in Chapter 3 is performed using six parallel scientific kernels: Check-LU, Cholesky, FFT-3D, K-means, K-NN and MatMul. These benchmarks were written in the Cell/B.E. variant of the StarSs [9] programming model. The traces collected from these benchmarks contain the information about the required computation time for different phases in the processors as well as the inter-processor communications through DMA transfers. Table 2.3 shows a summary of the main characteristics of each benchmark: number of tasks, average task run time, memory footprint, and estimated bandwidth required per task. The bandwidth estimate is obtained from the average task data size and run time.

## 2.2 Register File Methodology

Due to TaskSim's lack of support for core-level micro-architecture modeling, we have to resort to other tools to study the proposed register file. This part of the thesis is conducted at the IBM T.J. Watson Research Laborato-

| Kernel   | Number   | Average task          | Problem | Estimated BW            |

|----------|----------|-----------------------|---------|-------------------------|

|          | of tasks | run time              | size    | per task                |

| Check-LU | 54814    | $45.7~\mu \mathrm{s}$ | 256 MB  | 1.11 GB/s               |

| Cholesky | 357760   | $28.0 \ \mu s$        | 512 MB  | $1.68~\mathrm{GB/s}$    |

| FFT-3D   | 32768    | $13.9 \ \mu s$        | 128 MB  | $3.27~\mathrm{GB/s}$    |

| K-means  | 335872   | $30.7 \ \mu s$        | 195 MB  | $1.56 \; \mathrm{GB/s}$ |

| K-NN     | 800768   | $7.9 \ \mu s$         | 36 MB   | $0.49~\mathrm{GB/s}$    |

| MatMul   | 262144   | $25.8~\mu\mathrm{s}$  | 192 MB  | $1.42~\mathrm{GB/s}$    |

Table 2.3: Simulated benchmarks.

ries, during the internship that the author carries out in the Reliability- and Power-Aware Microarchitectures group. Due to confidentiality restrictions, configuration values and results corresponding to this study are normalized. Still, these disclosure-related issues do not affect the value of the study nor depreciate the importance of the conclusions presented in this thesis.

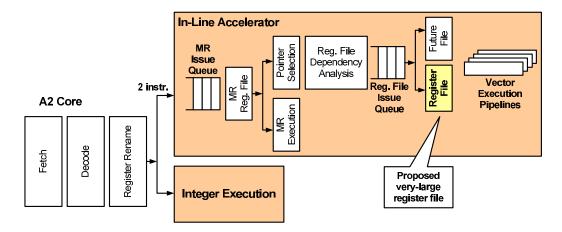

### 2.2.1 In-Line Accelerator and Register File Model

As we explain in Chapter 4, the very-large vector register file proposed in this thesis is studied in the context of an in-line accelerator for the IBM PowerEN processor [17, 37, 57]. Figure 2.2 presents an architectural outline of such in-line accelerator and its interaction with the A2 processor, the PowerEN's constituent core.

Execution in the accelerator proceeds in two stages. First, the map registers (MRs) are accessed to determine which registers will be read or written. MRs constitute a mechanism for indirect access to the register file using operand-associated mappings [29], because 5-bit operands are not enough to index 2048 registers. Vector execution then proceeds in the second stage. The fetch engine can enqueue two instructions per cycle into the MR issue queue inside the accelerator. After issuing and reading their input MRs, map management instructions are executed immediately. Other instructions proceed through the select pointers stage, which determines the actual registers read/written, based on the pointers in the MR values read from the register file. Dependency analysis then determines which prior instructions, if any,

each vector instruction depends on. Instructions are then enqueued a second time to wait for vector register dependencies and an appropriate execution pipeline. Once instructions issue, they read their input values and execute. Register renaming is impractical for registers in the very-large register file because the 2048 architected registers would require a highly-ported rename table with 2048 entries. Instead, the in-line accelerator employs a future file. The future file holds vector register values until the producer commits. After commit, future file entries are spilled to the register file, which holds only committed architected state. Instructions determine the future file entry of prior in-flight instructions that produce needed input values. After issue, instructions read their inputs from the future file, the bypass network or the register file as needed.

Figure 2.2: Micro-architecture model of the in-line accelerator (source: [28])

#### 2.2.2 Performance Evaluation

To study the performance of the proposed register file in the context of an A2 processor, we use an IBM-internal trace-driven cycle-accurate simulator. This tool models the most important A2 core micro-architectural details, as well as first level instruction and data caches, and second level cache. The simulator is augmented to incorporate the in-line accelerator, of which the very-large register file is a constituent part.

We use the simulator to evaluate the register file performance for a single A2 core. Table 2.4 summarizes the main architectural parameters adopted for this study. Although the original A2 design is 4-way SMT, in this thesis we model a single-threaded core because so are the studied applications. Among the core execution pipelines, the in-line accelerator is a VMX-like 32-byte-wide SIMD unit. The register file, which is part of the accelerator, consists of 2048 32-byte vector registers together with an indirection mechanism for addressing them dynamically. We discuss the register file features in Chapter 4. In our model, we adopt perfect (i.e. "infinite") L1 and L2 caches. Due to its large capacity, the register file is able to keep input and output data from beginning to end of the computation. Therefore, L1 and L2 caches do not influence the evaluation.

| Component       | Configuration                                                 |

|-----------------|---------------------------------------------------------------|

| A2-like core    | Single-threaded <sup>†</sup> , 64-bit PowerPC-based architec- |

|                 | ture (†original A2 processor is 4-way SMT)                    |

|                 | Core frequency: 2.3 GHz                                       |

|                 | Issue width: 2                                                |

|                 | Execution mode: out-of-order                                  |

|                 | <b>Execution units:</b> branch unit, two fixed-point          |

|                 | units, load/store unit and in-line accelerator                |

| Cache hierarchy | Perfect L1 and L2 caches                                      |

| In-line         | 32-byte-wide SIMD unit with fixed-point and                   |

| accelerator     | single-precision floating-point arithmetic support            |

|                 | Execution mode: in-order                                      |

|                 | Register file: 2048 256-bit vector registers (64              |

|                 | KB total), eight 8-KB banks, 4RD/1WR ports                    |

|                 | per bank                                                      |

Table 2.4: Simulated A2 core architectural parameters.

## 2.2.3 Applications

The benefits of the proposed register file are evaluated in the context of applications for wireless base stations. We select two classes of algorithms of particular importance for base stations, namely FFT and Turbo Decoding,

because they are the most heavily used and perhaps the most significant consumers of processor cycles.

The adopted FFT implementation is based on Pease's method [93], which is explicitly optimized for parallel computation. The evaluated FFT sizes are 512, 1024 and 2048 complex points, with 16 bits each for the real and imaginary parts.

The Turbo Decoding algorithm incorporates two constituent decoders, interleaver, and de-interleaver in a feedback loop, with the decoders implementing the BCJR algorithm [7]. The input to the decoder is a bit stream (codeword) with two parity bits per each data bit (1/3 rate encoding). We evaluated a 6144-element codeword because this is the maximum length specified by the 3GPP Long Term Evolution (LTE) wireless standard [1].

#### 2.2.4 Area and Power Evaluation

Register file area and power consumption are analytically estimated based on information about PowerEN 45nm SOI-CMOS technology and register file cell type [31, 57].

## 2.3 Power Management Methodology

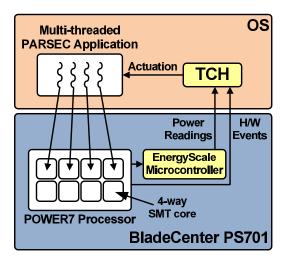

In this part of the thesis we study the power implications of running multithreaded workloads on cores with varying SMT levels. This evaluation is done in the context of a real platform (an IBM BladeCenter PS701 system), which is explained in Section 2.3.1. We use multi-threaded applications from the PARSEC 2.1 benchmark suite [12], which are presented in Section 2.3.4.

## 2.3.1 Experimental Platform

The set-up system used for the experiments is an IBM BladeCenter PS701 machine. The system has one IBM POWER7 processor running at 3.0 GHz and 32 GB of DDR3 SDRAM running at 800 MHz. The POWER7 chip multi-processor [59] is composed of eight processor cores, each one capable

of four-way SMT operation. The eight cores can provide 32 concurrently executing threads. Each core has access to a private 256-KB L2 cache and to a local 4-MB L3 region. Eight L3 regions constitute a 32-MB on-chip L3 cache (local L3 regions provide low-latency access to the cores). In addition to its private L2 and local L3 caches, a core can also obtain data from other cores' L2 and L3 caches [92].

The platform runs RHEL 5.7 OS with Linux kernel version 3.0.1. Each PARSEC benchmark is executed as a single running workload to analyze its performance and power characteristics. During each run, we explicitly define the correspondence between software and hardware threads using the taskset command, which is a Linux tool to set processes' CPU affinity [91].

Our experimental system consists of an IBM BladeCenter PS701 system (Figure 2.3), where the proposed thread consolidation heuristic (TCH) executes and actuates at OS level. TCH obtains chip-level power measurements using the IBM Automated Measurement of Systems for Temperature and Energy Reporting software [35, 63]. The software connects to the EnergyScale microcontroller to download real-time power readings of the POWER7 processor under evaluation. In addition, TCH obtains hardware events information from processor counters available in the POWER7 chip [32, 69], which are discussed in Section 2.3.3. With all this information, TCH can make decisions and perform actuations (i.e. to consolidate or unconsolidate threads) at runtime.

Whenever TCH decides to consolidate threads, cores that are left unused are switched to *nap* idle state to reduce power consumption. The nap mode in POWER7 deactivates instruction fetch and execution and turns off all clocks to the execution engines in the core, but it still keeps L2 and L3 caches coherent [35, 36].

## 2.3.2 IBM Automated Measurement of Systems for Temperature and Energy Reporting

The IBM BladeCenter PS701 system used in our experiments incorporates firmware which runs on a dedicated microcontroller to provide energy man-

Figure 2.3: Experimental system for the evaluation of the proposed thread consolidation heuristic (TCH).

agement support [35, 63]. This subsystem, which is known as the EnergyScale firmware and microcontroller, senses the system at runtime providing a mechanism to control it based on user directives. The heuristic presented in this thesis leverages this energy management capability to collect chip power consumption information at runtime. The EnergyScale microcontroller is accessed through an interface known as the IBM Automated Measurement of Systems for Temperature and Energy Reporting software.

## 2.3.3 POWER7 Performance Monitoring Unit

The POWER7 processor incorporates a built-in performance monitoring unit (PMU) which makes possible to measure runtime performance through a set of six thread-level performance monitoring counters [32, 69]. POWER7 PMU provides an extensive list of more than 500 performance events that can be measured in the chip, such as cache miss rates, unit utilization, thread balance, hazard conditions, translation related misses, stall analysis, instruction mix, cache behavior and memory latency, among others. The six available counters can be programmed to "count" different event combinations. In this thesis, we make use of just three events, which are listed in Table 2.5. The heuristic presented in this thesis employs events PM\_RUN\_INST\_CMPL and

PM\_RUN\_CYC to characterize performance as instructions per cycle (IPC), and event PM\_L1\_DCACHE\_RELOAD\_VALID to detect execution phase transitions.

| Event                     | Description                                      |

|---------------------------|--------------------------------------------------|

| PM_RUN_INST_CMPL          | Number of instructions completed, gated by       |

|                           | the run latch.                                   |

| PM_RUN_CYC                | Processor cycles gated by the run latch. Op-     |

|                           | erating systems use the run latch to indicate    |

|                           | when they are doing useful work. The run latch   |

|                           | is typically cleared in the OS idle loop. Gating |

|                           | by the run latch filters out the idle loop.      |

| PM_L1_DCACHE_RELOAD_VALID | The L1 data cache has been reloaded for de-      |

|                           | mand loads, reported once per cache line.        |

Table 2.5: POWER7 performance events measured by the proposed heuristic.

### 2.3.4 Applications

We adopt the PARSEC 2.1 benchmark suite [12] to study the use of the optimum combination of core-wise SMT level and number of active cores as a knob to achieve a desired power-performance efficiency. PARSEC applications include a representative set of shared-memory parallel programs for chip-multiprocessors. Parallelism is supported by either POSIX threads (pthreads) [20], OpenMP [22] or Intel Threading Building Blocks (TBB) [50]. In this thesis, we adopt the POSIX threads version. Table 2.6 presents a description of the applications used in our experiments (we exclude frequine due to its lack of support for POSIX threads). All the executions are done using native input sets — the largest ones provided in PARSEC and which resemble real program inputs most closely.

| Program       | Domain             | Description                              |

|---------------|--------------------|------------------------------------------|

| blackscholes  | Financial          | Option pricing kernel that uses the      |

|               |                    | Black-Scholes partial differential equa- |

|               |                    | tion                                     |

| bodytrack     | Computer Vision    | Tracking of a person's body              |

| canneal       | Engineering        | Simulated cache-aware annealing ker-     |

|               |                    | nel which optimizes the routing cost of  |

|               |                    | a chip design                            |

| dedup         | Enterprise Storage | Next-generation compression kernel       |

|               |                    | which employs data deduplication         |

| facesim       | Animation          | Simulation of the motions of a human     |

|               |                    | face for animation purposes              |

| ferret        | Similarity Search  | Content similarity search server         |

| fluidanimate  | Animation          | Fluid dynamics simulation for anima-     |

|               |                    | tion purposes                            |

| raytrace      | Rendering          | Real-time raytracing                     |

| streamcluster | Data Mining        | On-line clustering                       |

| swaptions     | Financial Analysis | Pricing of a portfolio of swaptions with |

|               |                    | the Heath-Jarrow-Morton framework        |

| vips          | Media Processing   | Image processing application             |

| x264          | Media Processing   | H.264 video encoding application         |

Table 2.6: Adopted PARSEC benchmarks (source: [12]).

# Chapter 3

# Last-Level Cache Design

This chapter presents a last-level cache (LLC) organization conscientiously designed for throughput-aware computation in chip multiprocessors (CMPs). As shown in Figure 3.1, the proposed LLC is divided into multiple independent blocks. Cores are grouped in clusters, and each cluster contains a LLC block connected to its local network. The most important characteristic of the LLC is the lack of data replication. Instead, the address space is interleaved in a fine-grained fashion across blocks. In this way, effective capacity of the LLC is significantly improved, which boosts memory bandwidth. In addition, since data is not replicated in the cache, there is no need to deal with data coherence.

The key insight of our proposal is that a fine-grain partitioning of the address space enables higher bandwidth, since multiple transfers can proceed in parallel, at the expense of locality, due to data being spread all over the available storage. While this trade-off is harmful for latency-aware architectures, it is beneficial for throughput-aware computation in CMPs.

In this chapter, we compare our proposal against a memory system optimized for latency. Both alternatives are evaluated on a throughput-aware CMP with a master-worker execution model and support for DMA transfers. The architecture is composed of processing elements (cores) grouped in clusters interconnected through a global network.

Figure 3.1: Illustrative 32-core CMP, with the proposed LLC organization. In this particular example, eight cores per cluster share a local LLC block. Because data is not replicated in the LLC, cores can also access remote blocks.

## 3.1 Latency- vs. Bandwidth-Optimized Last-Level Caches