# Avalanche Ruggedness of Local Charge Balance Power Super Junction Transistors

Thesis dissertation presented to obtain the qualification of Doctor of Philosophy from the Electronic Engineering Department of Universitat Autònoma de Barcelona (UAB)

by Ana Villamor Baliarda

Supervised by:

David Flores Gual

Peter Moens

Jaume Roig Guitart

Barcelona, July 2013

| Dr. David Flores Gual, Dr. Peter Mathesis dissertation entitled "Avalan Super Junction transistors" is presented to be presented for lecture and | nche Ruggedness of Local C<br>ented by Ana Villamor Baliar<br>tat Autònoma de Barcelona. | Charge balance power da to obtain the PhD in |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|

| Cerdanyola del Vallès, May 2013                                                                                                                  |                                                                                          |                                              |

| David Flores Gual                                                                                                                                | Peter Moens                                                                              | Jaume Roig Guitart                           |

#### **Abstract**

The main objective of the thesis is the reliability increase of high voltage (600 V) power MOSFETS based in the Super Junction concept when they are submitted to the most extreme conditions in DC/DC converters and Factor Power Correction circuits and the intrinsic body diode has to handle a big amount of energy in a very short period of time. The research has been carried out in the framework of a collaboration between Institut de Microelectrònica de Barcelona (IMB-CNM-CSIC) and ON Semiconductor (Oudenaarde, Bèlgica).

The process technology of the new Super Junction power MOSFET transistors designed in ON Semiconductor (named UltiMOS) has been optimized with the aim of robustness enhancement, which has to be totally independent of the charge balance in the device. The transistors are destined to 400 V line applications that require a voltage capability above 600 V and a minimal on-state resistance to operate at high frequency. The thesis starts with an introduction to the state of the art of Super Junction transistors, including a description of the different process technologies used in the commercial counterparts. Afterwards, the most relevant electrical and technological parameters are introduced and linked to the electrical characterization of the UltiMOS transistor.

The research is centered in the study of the physics involved in the failure mechanisms combining TCAD simulations and experimental measurements, from where it is concluded that a technological solution to increase the energy capability of UltiMOS transistors is needed, with a wide CB manufacturability window. Different devices derived from the UltiMOS structure (conventional UMOS transistor, SJ Diodes and SJ Bipolar transistors) were fabricated in the ON Semiconductor's Clean Room and tested under the same avalanche conditions as UltiMOS transistors. All the results derived from complementary techniques (*Unclamped Inductive Switching, Emission Microscopy, Thermal Infrared Thermography, Transmission Line Pulse, Transient Interferometric Mapping*, etc.) lead to the same conclusion: the current is focalized at a certain region of the UltiMOS transistor, enhancing the activation of the parasitic bipolar transistor. Two approaches are proposed to increase the energy capability of UltiMOS transistors and, once its efficiency has been demonstrated, they have been included on the process technology of the device designed to go into production.

### Acknowledgements

As a prelude to this thesis dissertation, I would like to express all my gratitude to the people which have contributed to the work here reported or to the PhD in general.

First of all I am very honoured that Prof. Josef Lutz (University of Chemitz, Germany), Dr. Frédéric Morancho (LASS, France) and Prof. Ettore Napoli (University of Naples, Italy), had accepted being members of the PhD jury of this research work, as well as the substitute members, Dr. Salvador Hidalgo (IMB-CNM-CSIC, Spain) and Dr. Jordi Suñé (UAB, Spain). Thanks also to Dr. P. Vanmeerbeek and Dr. A. Irace to accept being members of the European Doctorate Mention.

Thanks also to Prof. Emilio Lora Tamayo and Carles Cané to allow me to use the IMB-CNM-CSIC facilities, and to the Ministerio de Economia y Competitividad for the FPI scholarship (BES-2009-014385). I am very grateful for the two additional scholarships that supported my research in the ON Semiconductor facilities. Special thanks to Prof. J. Millán (IMB-CNM-CSIC) and Dr. Marnix Tack (On Semiconductor) to let me join their R&D respective teams during my PhD research.

Secondly, I would like to express my deep gratitude to Dr. David Flores, who trusted in my capabilities from the very first moment. He gave me a great view of the process technology, he showed me always a different point of view that the one I acquire during my stages in ON Semiconductor, what helped enormously to the development of the investigation. Moreover, he gave me the physics basics that were required, which I love so much... Many thanks also for all the effort that allowed me to be in Belgium for my stages in ON Semiconductor. I have learned in all senses with your advices. And many thanks for all the patience you had with me!

I am also very grateful to Dr. Peter Moens, who encouraged and motivated me during all my research. I will always remember how he introduced me into the "company world", giving my first presentations, writing reports and rushing for deadlines. He made me lose my fear and I grew professionally. Many thanks also to take care of all the practical arrangements during my stages in ON Semiconductor.

Thanks also to Dr. Jaume Roig Guitart for the scientific discussions during the thesis work.

I also want to express my gratitude to the people of University of Naples (Dr. A. Irace, Dr. M. Riccio and Dr. G. Brelio) and from University of Vienna (Dr. D. Pogany and Dr. S. Bychikhin) for the nice discussions during the collaboration work we had. Thanks to X. Jordà for its help on the Reverse Recovery measurements.

Thanks to my colleagues in CNM for the lunch times, laughs, biers, discussions, coffees... Abel, Dr. Jesús, Pablesito, Matthieu, Alessandra, Javi, Lluís, Arnau, Andrés, Miki, and all the senior members of the Power Group. A thesis is a very exhausting work and I think that our group environment was just perfect. I also want to present my gratitude for everything to our ex-office-mate Dr. Aurore Constant. And I do not want to forget to mention the ETSE boys, especially Jordi and Vikas: lunches, study time, travels and a lot of laughs.

Thanks also to my colleagues in ON Semiconductor for the patience on my first presentations, to introduce me to the company environment (measurements, data location, new programs, etc), to the sport activities after work, the meals outside the company, and to the nice environment that is created in the group...Filip B., Piet, Chin Foong, Joris, Hocine, Johan, Peter L., Marleen, Sylvie, and a long etc.

To the Catalan-Belgian community that made me feel like home during the rainy Sundays in Gent with nice lunch+siesta times. We were like a family:) Go angels!

And also to my precious nenes: Lorena, Evelyn, Anna, Eva and Cris (and relatives). I appreciate all the time we spend together and I hope we can do it even if we are old ladies with a lot of child running and shouting during our dinner times.

To Teresa, Cele, Alex, Ester, and to the rest of my family, I want to thank all the patience, persistence and all the love that they always gave me. I could not have got so far without all of you.

Finally, many thanks to my Thomas. You are the best. Je t'aime mon amour.

# **Table of Contents**

| Abstractv                                                   |

|-------------------------------------------------------------|

| Acknowledgements                                            |

| List of symbols and acronyms xii                            |

|                                                             |

| CHAPTER 11                                                  |

| 1.1. Motivation                                             |

| 1.2. Framework and thesis outline4                          |

| 1.3. References 6                                           |

|                                                             |

| CHAPTER 2: Introduction                                     |

| 2.1. Fundamentals of Power MOSFETs                          |

| 2.2. Enhancing the vertical Power MOSFET: SJ Concept        |

| 2.3. Different SJ-MOSFET structures                         |

| 2.4 Main requirements of the SJ MOSFET transistors          |

| 2.5 References                                              |

|                                                             |

| CHAPTER 3: UltiMOS structure2                               |

| 3.1. UltiMOS target                                         |

| 3.2. Device description                                     |

| 3.2.1. Active Area                                          |

| 3.2.1.1. Electrical behaviour and role of different regions |

| 3.2.1.2. Impact of the main technological parameters        |

| 3.2.2. Edge termination                                     |

| 3.2.2.1. Electrical behaviour                               |

| 3.2.2.2. Impact of the main technological parameters                              | . 38  |

|-----------------------------------------------------------------------------------|-------|

| 3.3. Experimental techniques to determine CB condition                            | .41   |

| 3.3.1. Negative gate voltage effect on the UltiMOS transistors                    | . 42  |

| 3.3.2. Depletion behaviour and $C_{ds}$ - $V_{ds}$ / $C_{gd}$ - $V_{ds}$ curves   | . 45  |

| 3.4. UltiMOS transistor performance                                               | . 53  |

| 3.4.1. Conduction and Switching Losses                                            | . 53  |

| 3.4.2. Robustness                                                                 | . 56  |

| 3.5. References                                                                   | . 60  |

|                                                                                   |       |

| CHAPTER 4: Edge Termination study                                                 | . 63  |

| 4.1. Introduction                                                                 | . 63  |

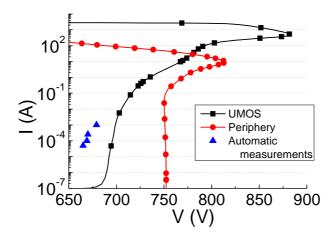

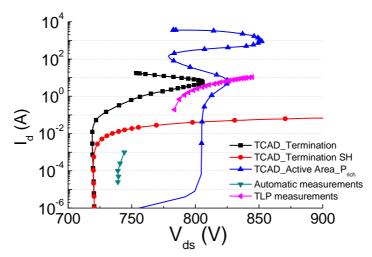

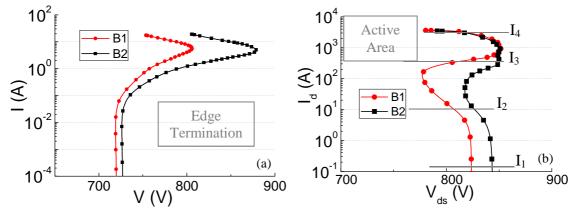

| 4.2. Breakdown location: Active area or Edge Termination                          | . 65  |

| 4.3. Failures in the Edge Termination                                             | . 68  |

| 4.4. How to avoid early failures in the edge termination: postpone the NDR branch | . 70  |

| 4.5. UltiMOS after edge termination optimization                                  | . 75  |

| 4.6. Conclusions                                                                  | . 80  |

| 4.7. References                                                                   | . 81  |

|                                                                                   |       |

| CHAPTER 5: Active Area study                                                      | .83   |

| 5.1. Introduction                                                                 | . 83  |

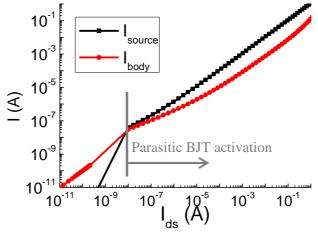

| 5.2. Parasitic Bipolar Transistor activation                                      | . 84  |

| 5.3. Basic structures analysis                                                    | . 86  |

| 5.3.1. Trench MOSFET (UMOS)                                                       | . 87  |

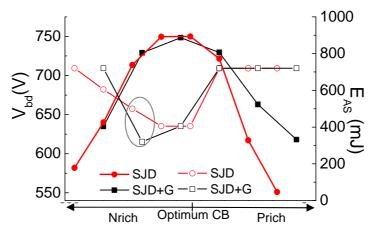

| 5.3.2. SJ Diode                                                                   | . 91  |

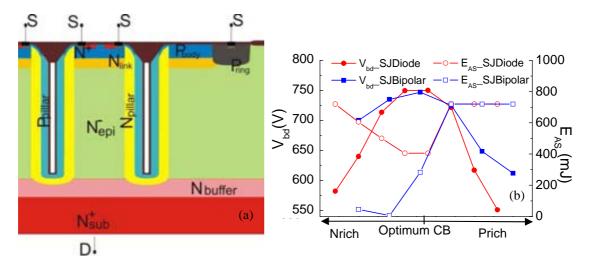

| 5.3.3. SJ Bipolar transistor                                                      | . 97  |

| 5.4. Parasitic bipolar gain on UltiMOS transistors                                | . 100 |

| 5.5. UltiMOS transistor behaviour                                                 | . 104 |

| 5.6. Summary and conclusions                                                      | . 109 |

| 5.7. References                                                                       |

|---------------------------------------------------------------------------------------|

| CHAPTER 6: Robustness enhancement of UltiMOS113                                       |

| 6.1. Introduction                                                                     |

| 6.2. Interaction between Active Area and Edge Termination                             |

| 6.3. Proposals to enhance the robustness of UltiMOS transistors                       |

| 6.3.1. Proposals in literature to enhance the robustness of SJ MOSFET transistors 119 |

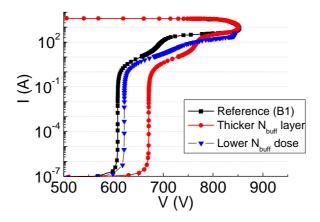

| 6.3.2. N <sub>buff</sub> layer optimized for the Active Area and Edge Termination     |

| 6.3.2.1. Simulation and experimental results                                          |

| 6.3.2.2. Optimized N <sub>buff</sub> layer                                            |

| 6.3.3. Forcing a PDR branch in the Active Area                                        |

| 6.3.3.1. Simulation results                                                           |

| 6.3.3.2. Technological variations                                                     |

| 6.3.3.2. Optimized P <sub>connection</sub> implant                                    |

| 6.4. New N <sub>buff</sub> layer and new P <sub>connection</sub> implant together     |

| 6.5. Conclusions                                                                      |

| 6.6. References                                                                       |

|                                                                                       |

| CHAPTER 7145                                                                          |

| 7.1. General conclusions                                                              |

| 7.2. Future work                                                                      |

| 7.2. Publication list                                                                 |

| Appendix A: Technology requirements and building blocks151                            |

| Appendix B: Experimental techniques and TCAD simulations                              |

## **List of Symbols and Acronyms**

#### **Symbols**

$\mu_n$  Permeability of the silicon

A Area

$AAV_{bd}$  Active area breakdown voltage

$A_N$  P<sub>connection</sub> implant angle

C Capacitance

$C_{ds}$  Drain-Source capacitance  $C_{gd}$  Drain-Gate capacitance  $C_{gs}$  Gate-Source capacitance

$C_{iss}$  Input capacitance  $C_{oss}$  Output capacitance

$C_{rr}$  Reverse transfer capacitance

d Depletion width

$D_N$  P<sub>connection</sub> implant dose

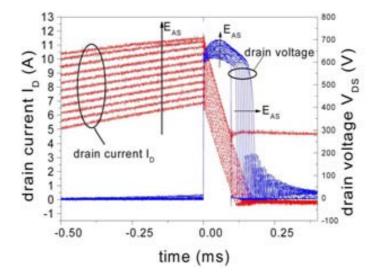

$E_{AR}$  Energy under repetitive avalanche UIS test  $E_{AS}$  Energy under single avalanche UIS test

$E_C$  Critical electric field

$E_F$  Electric field

$E_N$  P<sub>connection</sub> implant energy  $E_{off}$  Energy dissipated at turn-off  $E_{on}$  Energy dissipated at turn-on  $\mathcal{E}_S$  Permittivity of the silicon

*f* Frequency

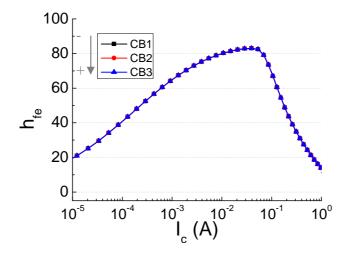

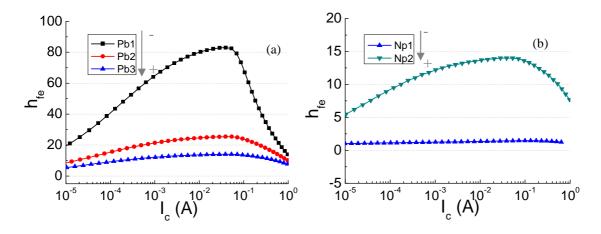

$h_{fe}$  Gain

$I_{AS}$  Failure current under single avalanche UIS test

$I_{body}$  or  $I_b$  Body current  $I_c$  Collector current  $I_d$  Drain current  $I_g$  Gate current

*I<sub>RRM</sub>* Reverse recovery maximum current

$I_{snap}$  Snapback current  $I_{source}$  Source current L Inductance value l Depletion extension

*n-BAL or NB* N<sub>buff</sub> layer dose

$N_{conc}$  Doping concentration of the N-type pillar

$N_D$  Donor concentration  $n_i$  Intrinsic carrier density

$Opt \pm \#$  Different CB condition notation

p Cell pitch

$P_{conc}$  Doping concentration of the P-type pillar

$Q_g$  Gate charge

$Q_{gd}$  Gate-Drain charge  $Q_{gs}$  Gate -source charge  $Q_{rr}$  Reverse recovery charge

$R_g$  Gate resistance  $R_{on}$  On-resistance

$SR_{on}$  Specific on-resistance

t1 Fall time during reverse recovery test t2 Rise time during reverse recovery test

T-BAL or NT N<sub>buff</sub> layer thickness  $T_{in}$  Intrinsic temperature

$T_{max}$  Maximum temperature in the device

$T_{rr}$  Reverse recovery time

$TV_{bd}$  Termination breakdown voltage

$V_{bd}$  Voltage capability /breakdown voltage

$V_{bi}$  Built-in potential

$V_{ce}$  Emitter collector voltage

$V_{dd}$  Drain voltage

$V_{ds}$  Drain-source voltage

$V_{gs}$  Gate voltage  $V_{in}$  Input voltage  $V_{out}$  Output voltage  $V_{pinch}$  Pinch-off voltage  $V_{TH}$  Threshold voltage

W Perimeter

$W_b$  Spacing between rings  $W_N$  Width of N-type column  $W_P$  Width of P-type column

$W_r$  Width of the rings

#### Acronyms

BJT Bipolar transistor

BPSG Borophosphosilicate

CB Charge Balance

CIBH Controlled injection of backside holes

CMP Chemical Mechanical Polishing

DIBET Department of Biomedical, Electronics, and Telecommunications

Engineering from University of Naples Federico II

DRIE Deep Reactive Ion Etching

DUT Device under test

EMMI Emission microscopy ESD Electrostatic discharge

FA Failure analysis

FCS Fairchild

FOM Figure of Merit

FOX Field Oxide

GaN Gallium Nitride

GR Ground ring

IPA or IFX Infineon

IT Information Technology

JFET Junction field effect transistor

KUL University of Leuven

ME/MI Multi-epitaxy/Multi-implant

MOSFET Metal Oxide Semiconductor Field Effect Transistor

$\begin{array}{ll} NDR & Negative \ differential \ resistance \\ N_{rich} & Negative \ Charge \ Balance \ condition \end{array}$

PDR Positive differential resistance PFC Power Factor Correlation

P<sub>rich</sub> Positive Charge Balance condition

SCM Scanning Capacitance Microscopy

SEM Scanning Electron Microscope

SH Self-heating Si Silicon

SiC Silicon Carbide

SIMS Scanning ion mass spectometer

SJ Super Junction ST or STF ST semiconductor

STUBA Slovenská Technická Univerzita V Bratislave

TCAD Technology Computer Aided Design

TEOS Tetraethylorthosilicate

TIM Transient Interferometric measurement

TLP Transmission line pulse

TUV Vienna University of Technology UIS Unclamped Inductive Switching

VDMOS Vertical Diffused Metal Oxide Semiconductor

# CHAPTER I

#### 1.1. Motivation

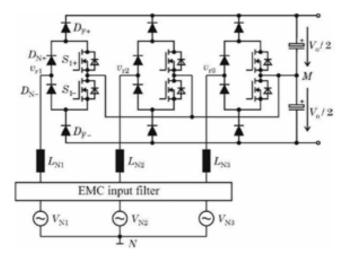

New application fields such as power electronics in aircrafts<sup>1</sup> are very restrictive in terms of efficiency, compactness, weight and losses. Indeed, active pulse width modulation (PWM) rectifiers (see Fig.1.1) with minimized total harmonic distortion of the input current and high power factor have to be designed for future electric power control. Advanced architectures for three-phase/level rectifiers have a reduced power semiconductor stress, allowing the use of high-efficiency power MOSFETs with a voltage capability in the 600 V range.

Fig.1.1. Typical application for 600 V power MOSFETs: active three-phase/level PWM  $\underline{\text{rectifier}}$ . Adapted from  $^1$ .

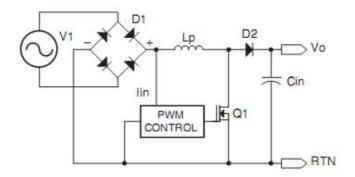

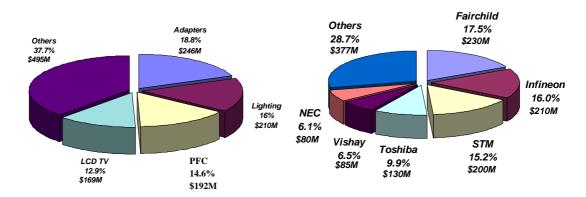

Today, the 600 V power MOSFET market is dominated by switching power mode supplies (SMPS) and LCD-TV applications, although power factor correction<sup>2</sup> (PFC, see Fig.1.2) and lighting applications also require high-efficiency power semiconductor switches<sup>3</sup>. The market distribution for 600 V power MOSFETs is shown in Fig.1.2-(a).

Fig.1.2. Typical application for 600 V power MOSFETs: PFC Boost pre-regulator. Adapted from<sup>2</sup>.

A high performing – high voltage power MOSFET requires very low conduction and transient losses. Conduction losses are basically driven by the specific on-state resistance ( $sR_{on}$ ) value but transient losses are determined by several electrical parameters which mainly depend on the transistor architecture and the process technology. Moreover, transient losses are dominant in high frequency applications where the parasitic capacitances of the power MOSFET have to be minimised. In some particular applications, the performance of the body diode of the power MOSFET transistor is crucial.

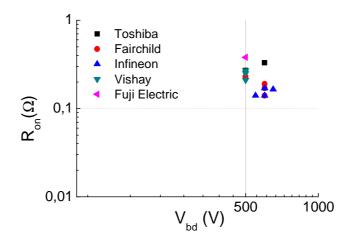

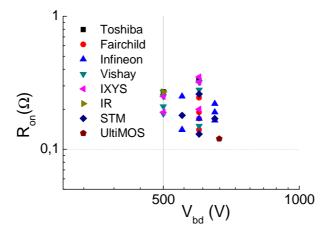

In the late 1990s, a new device concept was introduced to decrease the  $sR_{on}$  value of power MOSFETs without degrading the voltage capability: the Super Junction (SJ) architecture with charge balance in the drift region. The drastic  $sR_{on}$  reduction to the 10-30 m $\Omega$ ·cm<sup>2</sup> range when the SJ concept is implemented favoured the development of different techniques for the fabrication of 600 V power MOSFETs (multi epitaxial growth and deep trench etch). Today, different manufacturers as Infineon, Fairchild, STMicroelectronics, Toshiba and Vishay are already power SJ MOSFET suppliers, with a great success in the market (see Fig.1.2-(b)). Although the performance of the first generations of power SJ MOSFETs are much superior than those of the conventional VDMOS counterparts, there is still a long way to go in the optimisation of their performance and robustness.

Fig.1.2. Market distribution from the point of view of (a) application or (b) manufacturer for high-efficiency 600 V power SJ MOSFETs.

New base materials are emerging to fabricate power electronic devices, such as Gallium Nitride (GaN) or Silicon Carbide (SiC). Although SiC JFETs, SiC Schottky Diodes and GaN HEMTs have been proven to be far superior than Si SJ power MOSFETs in several electrical parameters, it is still not clear what chances are offered by SiC and GaN technologies to address the global needs of power switches better and/or cheaper. Last generation of SJ MOSFETs have reached an  $sR_{on}$  value in the range of  $10 \text{ m}\Omega\cdot\text{cm}^2$  but the  $sR_{on}$  values of SiC and GaN prototypes are one order of magnitude lower and will be further reduced in the next decade. Calculations made on SJ MOSFETs with a cell pitch of 2  $\mu$ m predict a minimum  $sR_{on}$  of 1  $m\Omega\cdot\text{cm}^2$  by introducing doping variation along the SJ columns.

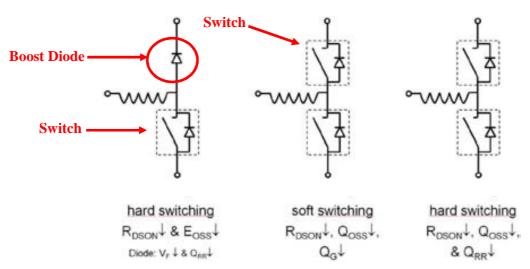

The energy stored in the output capacitance ( $E_{oss}$ ) is crucial to determine the losses in hard switching applications. Power SJ MOSFETs exhibits  $E_{oss}$  values even lower than those of the SiC JFETs but GaN switches will sure be far better. Charge stored in the output capacitance ( $Q_{oss}$ ) limits the maximum frequency, specially in resonant applications.  $Q_{oss}$  can hardly be improved in SJ MOSFETs but it will be reduced by a factor of 5 in SiC and GaN.

Fig.1.3. Typical switching applications and basic requirements for the switch and the boost diode. Adapted from <sup>4</sup>.

Three topologies are usually implemented in switching applications using a power MOSFET and a boost power diode, each one with specific requirements on the conduction and transient performance, as shown in Fig.1.3<sup>4</sup>. SJ MOSFETs with very low  $E_{oss}$  values are suitable for the hard switching topology with the boost diode implemented with a SiC Schottky. The topologies where two switches are used will sure be implemented with SiC and GaN switches in the future since SJ MOSFETs cannot compete in terms of very low  $Q_{oss}$ .

Although SiC and GaN are very promising technologies due to their good performance, they still have a long way to be able to fill the whole semiconductor market since they are competing with the Silicon, which is a mature and very good established base material. Nevertheless, serious improvements have to be done in power

SJ MOSFETs in terms of high frequency operation, where the risk of ringing oscillations in the gate electrode is not accepted, and robustness performance. The enhancement of the power SJ MOSFETs robustness performance is mandatory in applications where voltage spikes coming from the mains can occur due to the instability of the infrastructures. Indeed, hard switching conditions, such as Unclamped Inductive Switching (UIS) can also easily destroy the power semiconductor device when the energy stored in an inductor is directly dumped to the body diode. Today, power SJ MOSFETs are much more robust than SiC and GaN switches but the continuous reduction of the  $sR_{on}$  value leads to smaller chip size with the subsequent increased risk of thermal destruction due to current crowding in avalanche conditions.

Voltage spikes can go to 1/3 over the operating voltage. Due to the complex architecture of power SJ MOSFETs from the manufacturing point of view, small technological variations during the wafer processing can eventually lead to failures when the switch operates in hard switching conditions. In this sense, the research reported in this document is focussed on the robustness enhancement of the ON Semiconductor 600 V power SJ MOSFET based on the deep trench technology, known as UltiMOS.

#### 1.2. Framework and Thesis Outline

The robustness enhancement of the UltiMOS transistor, which is the final goal of this PhD, has been done in the framework of the collaboration between Instituto de Microelectrónica de Barcelona (IMB-CNM-CSIC) and ON Semiconductor (Oudenaarde, Belgium). The set-up of the UltiMOS process technology started with the initial test masks used to define the correct technological parameters for the different fabrication steps as etch of layers, epitaxial growths, implantations, diffusion times, etc. The  $sR_{on}$  value had to be low and independent of technological variations, and this is achieved by an accurate control of the process technology.

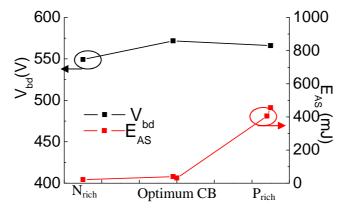

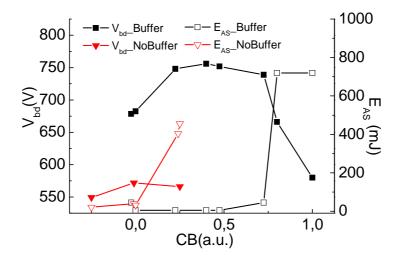

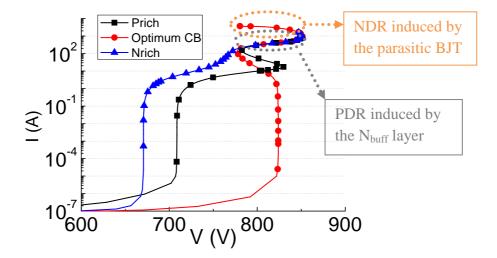

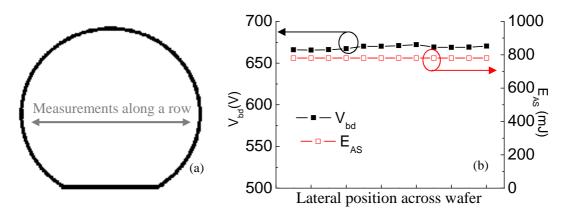

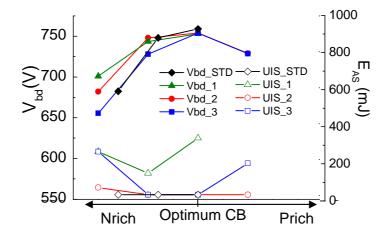

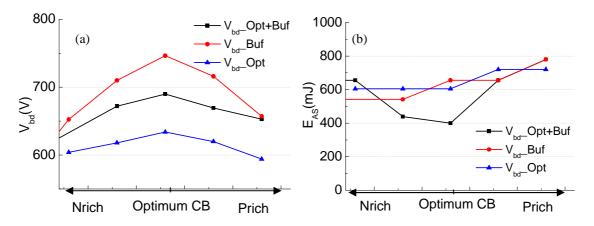

Afterwards, the layout was optimized to enhance the most relevant electrical parameters, but this first optimization steps are not subject of study on this document. The edge termination layout was also optimized before starting the PhD research when the device was process stable but not yet reliable due to the low current capability performance. The most relevant electrical parameters under study are the voltage and energy capabilities since the  $R_{on}$  and  $V_{TH}$  targets were already accomplished. Therefore, mainly the off-state performance is analysed. Nevertheless, the optimisation of  $V_{bd}$  and  $E_{AS}$  has also impacted the conduction performance with the necessary re-optimisation work.

The thesis document is structured in 6 chapters and 2 appendices:

- Chapter 1 describes the motivation, framework and outline of the performed research.

- The basic SJ MOSFET theory is reported in Chapter 2 where the development of the different SJ architectures and their main requirements are described. A final comparison of the electrical performance of the commercially available power SJ MOSFETs is provided.

- Solid state concepts and tools needed to follow the investigation presented in

this thesis are explained in Chapter 3. The chapter is split into Active area and

Edge Termination regions to better study their electrical performance and to

determine the impact of the technological parameters on each region. Two ways

to determine the CB on the UltiMOS transistor are also presented, although it

could be used on other SJ MOSFET architectures.

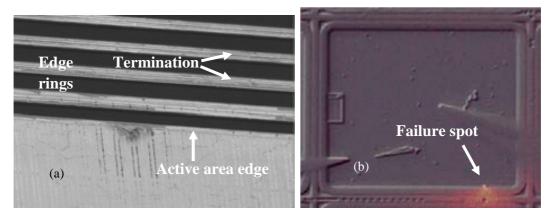

- The improvement of the edge termination robustness is studied in Chapter 4. It concludes with the analysis of the active area electrical performance when the edge termination is already optimized.

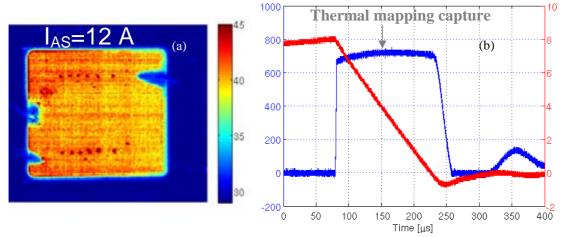

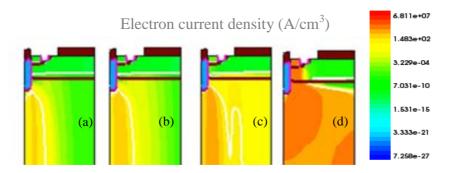

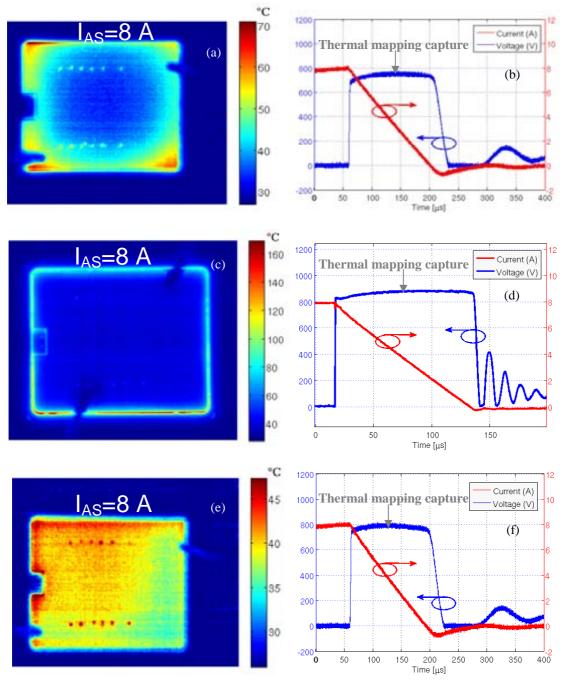

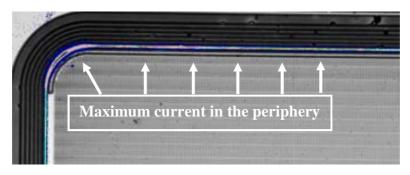

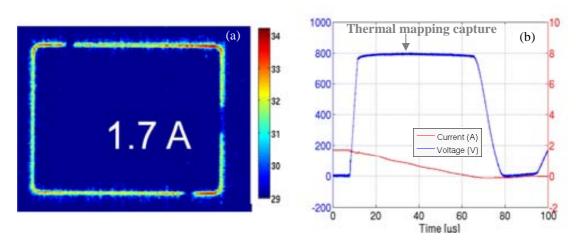

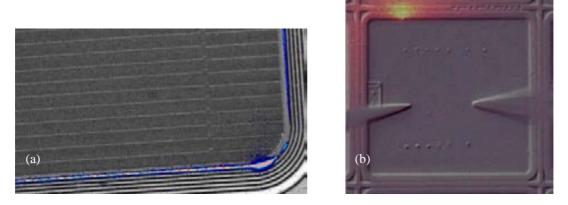

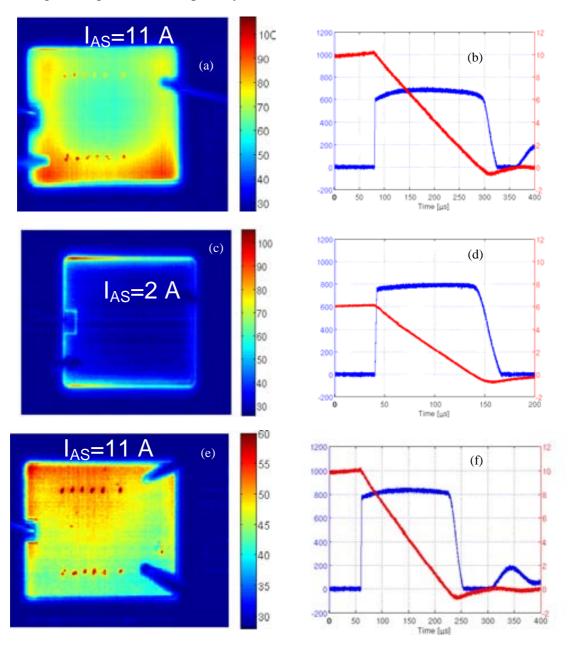

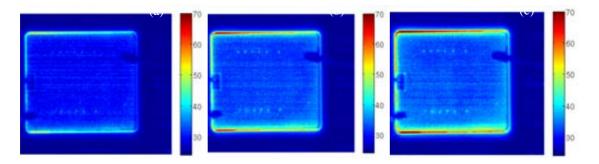

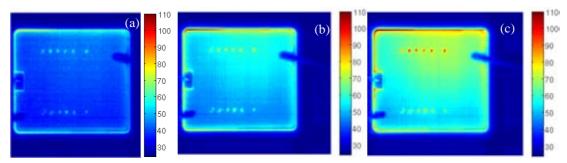

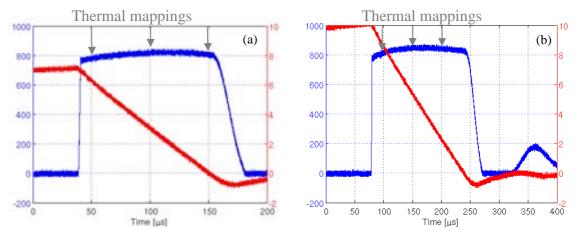

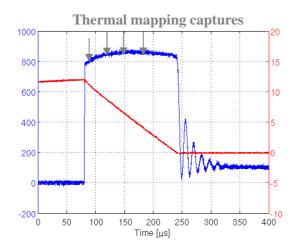

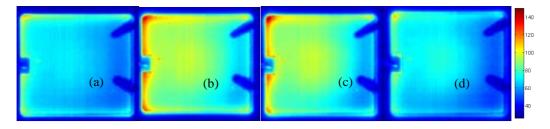

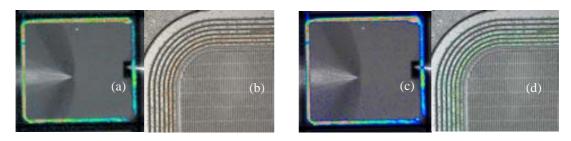

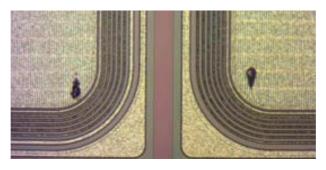

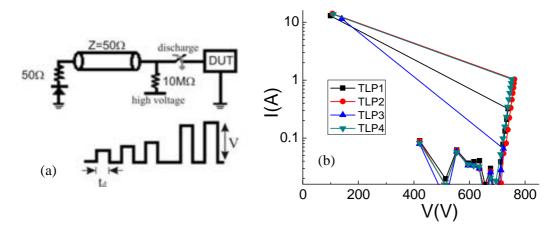

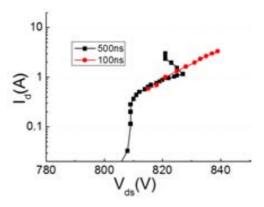

- The ruggedness of the active area is reported in Chapter 5. Different power structures derived from the UltiMOS transistor are simulated and fabricated to understand the failure mechanisms with the aid of the experimental techniques described in Appendix B (EMMI, Thermal Mapping, TIM, TLP, etc.).

- Different approaches implemented in commercial SJ MOSFET devices to improve its robustness of are reported in Chapter 6. Afterwards, two approaches to improve the robustness of UltiMOS transistors under the UIS test are presented. The energy capability improvement is accomplished in both proposed cases.

- The conclusions of this thesis are finally drawn in Chapter 7 together with the recommendations for future work.

- The UltiMOS process technology is detailed in Appendix A.

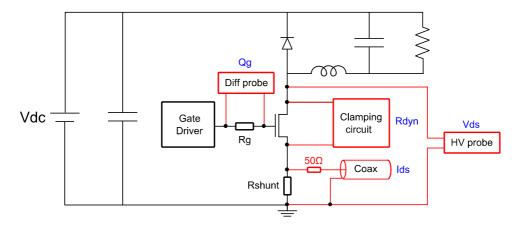

- Experimental techniques used in the performed research are reported in Appendix B, including the test set-up. ON Semiconductor cannot perform all the necessary tests at the Oudenaarde site. Therefore, a brief description on where each type of measurement was performed is provided.

#### 1.3. References

<sup>&</sup>lt;sup>1</sup> M. Hartmann, H. Ertl, J. W. Kolar, "On the trade-off between Input Current Quality and Efficiency of High Switching Frequency PWM Rectifiers", ITPE vol. 27, No. 7, pp. 3137-3149 (2012).

<sup>&</sup>lt;sup>2</sup> Fairchild, Application Note 42047: "Power Factor Correction (PFC) basics". (2004).

<sup>&</sup>lt;sup>3</sup> J. Lutz, H. Schlangenotto, U. Scheuermann, R. De Doncker. "Semiconductor Power Devices: Physics Characteristics", Reliability. Springer (2011).

<sup>&</sup>lt;sup>4</sup> M. Treu, E. Vecino, M Pippan, O. Häberlen, G. Curatola, G. Deboy, M. Kutschak, U. Kirchner, "*The role of silicon, silicon carbide and gallium nitride in power electronics*", Proc. IEDM '12, pp. 147-150 (2012).

# **CHAPTER 2**

# Introduction

In this chapter the fundamentals of Power MOSFET are introduced. One of the most important parameters to optimize for the design of these devices is the  $V_{bd}$ - $R_{on}$  trade-off. The principal applications of these devices are discussed in this section. A new concept is introduced: the Super Junction. The relation  $V_{bd}$ - $R_{on}$  can be highly improved, breaking the so-called Silicon Limit.

#### 2.1. Fundamentals of Power MOSFETs

The power MOSFET (*metal-oxide-semiconductor field-effect transistor*) was developed in the 1970s to overcome the intrinsic limitations of power bipolar transistors (BJT), inherent to the current control process. Thus the necessary base current to maintain the BJT in the on-state leads to an inefficient energy operation at high frequency. In fact, the bipolar nature of power BJTs limits their switching speed. Power MOSFETs are majority carrier devices with positive temperature coefficient and high switching speed, even at high temperatures in contrast with the power BJT, where electrons and holes need to be removed during the turn-off process<sup>1</sup>. In addition, power MOSFETs have a more linear characteristics and better temperature stability with enhanced performance in linear applications and less complex feedback circuitry. Finally, the leakage current of power MOSFETs is extremely low (nA) and no conduction threshold is present, eliminating electrical noise in sensitive AC switching applications. These devices found applications in power electronic circuits operating at low voltages (<150 V).

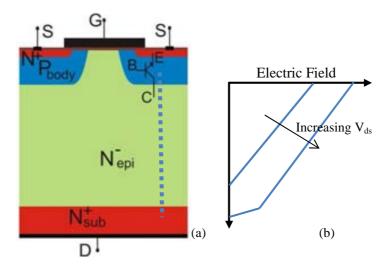

The vertical power MOSFET, known as VDMOS (*Vertical Double Diffused MOS*) transistor, is implemented as n-channel device due to the higher electron mobility. The charge modulation in the N-type inversion layer created at the Silicon surface is achieved with a metal plate (gate electrode, *G*) located above the P-type body region (P<sub>body</sub> in the VDMOS cross section plotted in Fig.2.1-(a)) and insulated by the gate oxide from the active Silicon area and by an interlevel oxide from the source electrode. The

source (S) and drain (D) electrodes of the power VDMOS transistor are connected to high doped N-type regions to obtain a good ohmic contact while a low doped N-type epitaxial region ( $N_{epi}^-$ ), grown on the  $N^+$  substrate ( $N_{sub}^+$ ), is necessary to reach the desired blocking voltage capability ( $V_{bd}$ ). The  $P_{body}$  region is also contacted to the source electrode in the third dimension to avoid the eventual activation of the inherent parasitic NPN bipolar structure<sup>2</sup>. When a gate voltage higher than the threshold voltage ( $V_{TH}$ ) is applied, an inversion channel is created at the top of the  $P_{body}$  region and electrons can flow from source to drain, provided a positive drain bias is applied. The power MOSFET structure includes a body diode with the cathode connected to the drain contact and the anode to the source contact. This diode can be used as a freewheeling diode or can be driven in avalanche during operation.

Fig.2.1. (a) Cross section of a conventional power VDMOS structure and (b) schematic electric field cut in the same structure as increasing the positive drain bias.

The doping and thickness of the  $N_{epi}^-$  layer are determined by the  $V_{bd}$  value since in the off-state (G grounded) the depleted region is mainly spread into this layer. As a consequence, the  $N_{epi}^-$  layer properties are responsible for the vertical electric field profile and avalanche process. A high  $V_{bd}$  value can only be achieved if the doping concentration and the thickness of the  $N_{epi}^-$  layer are increased, sustaining more drain voltage before reaching the critical electric field ( $E_C$ ) at the  $P_{body}/N_{epi}^-$  junction<sup>1</sup>. If the depleted region reaches the  $N_{sub}^+$  a reach-through breakdown will happen with a trapezoidal electric field shape.

The main concern when a device is chosen for a certain application is the losses that will be introduced in the circuit by the device: the conduction losses (ruled by the on-resistance,  $(R_{on})$ ) and the switching losses (mainly depending on the capacitive behaviour of the device). The  $R_{on}$  value is the added contribution of the channel resistance, the resistance of the accumulated layer under the gate electrode, the JFET resistance between adjacent cells and the epitaxial resistance<sup>3</sup>. The substrate and the package resistances contribution to the total  $R_{on}$  is very low and are not taken into account. The resistance of the  $N_{epi}$  layer is the most important contribution in the case of high voltage transistors (approximately 95% in 600 V Power MOSFETs) due to the

necessary thick and low doped N<sup>-</sup><sub>epi</sub> layer to reach high  $V_{bd}$  values. The relation between two relevant parameters is usually described by a figure of merit (FOM)<sup>4</sup>. The most important FOM that has to be improved in a power VDMOS transistor is the reduction of the specific on-state resistance ( $sR_{on}$ ) defined as the product of the  $R_{on}$  and the active area of the device (A). Another important FOM for the design of a power VDMOS transistor is the  $sR_{on}$ - $V_{bd}$  trade-off described by Eq.1 (ideal  $R_{on}$ ) where  $\varepsilon_s$  and  $\mu_n$  are the permittivity the permeability of the silicon, respectively, and Ec is the critical electric field<sup>4</sup>. The  $R_{on}$  value increases with the  $V_{bd}$  value since a thicker and less doped N<sup>-</sup><sub>epi</sub> layer is needed. The  $sR_{on}$ - $V_{bd}$  trade-off has to be optimised with the aid of 2D TCAD simulations in real power VDMOS transistors, taking into account the process technology.

$$R_{on-ideal} = \frac{4V_{bd}^2}{\varepsilon_s \mu_n E_C^3} \tag{Eq.1}$$

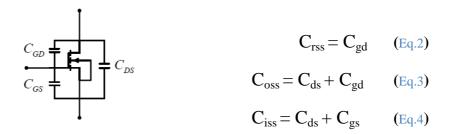

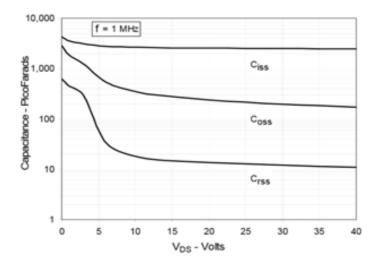

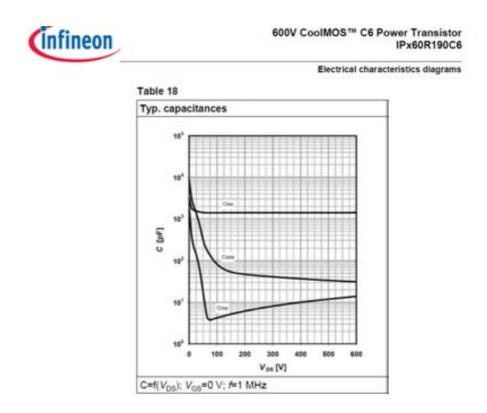

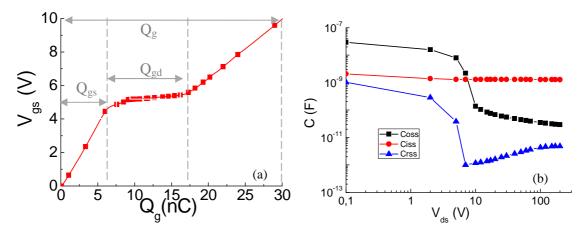

The switching losses on a Power MOSFET depend on the inherent capacitances since they work as energy storage centres. The  $C_{gd}$ ,  $C_{gs}$  and  $C_{ds}$ , are the gate-to-drain, gate-to-source and drain-to-source capacitances, respectively (see Fig.2.2). However, in the commercial datasheets the capacitances are labelled as input ( $C_{iss}$ ), reverse transfer  $(C_{rss})$  and output  $(C_{oss})$  capacitances, according to Eq.2, Eq.3 and Eq.4, respectively.  $C_{oss}$ for a 600 V VDMOS can be approximated to  $C_{ds}$  since the  $C_{gd}$  value can be neglected when compared to  $C_{ds}$ .  $C_{gd}$  can be divided in two parts: the capacitance related with the overlap between the polysilicon gate and the silicon drift region under the gate, and the capacitance associated to the depletion region under the gate coming from the P<sub>body</sub>/N<sub>drift</sub> junction.  $C_{gs}$  is the capacitance derived from the overlap between the gate electrode and the source and channel regions. This capacitance mainly depends on the geometry of the device. Finally,  $C_{ds}$  is the capacitance associated with the  $P_{body}/N_{epi}$  diode<sup>1</sup>. Typical values of the intrinsic capacitances of a 600 V-20 A VDMOS transistor with  $R_{on}$ =0.55  $\Omega$  are provided in Fig.2.3.  $C_{oss}$  gradually decreases with the applied drain voltage<sup>1,5</sup> and the  $C_{rss}$  curve exhibits a similar behaviour than  $C_{oss}$ , but at lower capacitance values. It is worth to say that a minimised  $C_{rss}$  value leads to a faster depletion and a higher switching speed. Finally,  $C_{iss}$  is almost constant with the drain voltage.

Fig.2.2. MOSFET capacitance equivalent circuit

Fig.2.3. Typical capacitive behaviour of a power VDMOS transistor (IXFH14N60P, from Infineon).

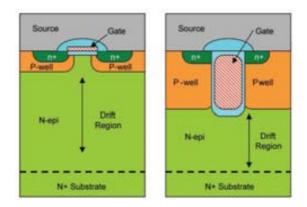

The  $Q_g$  accounts for the gate charge that needs to be removed during the turn-on process of a power MOSFET, and it depends on the total gate width.  $Q_g$  determines the gate peak current ( $I_g$ ) and the drive loss<sup>6</sup>. As expected, the lower the  $Q_g$  value, the faster the charges are removed, leading to a lower switching time. Therefore, an optimised  $R_{on}$ - $Q_g$  trade-off is crucial for the conduction and switching losses. The gate architecture is also a key point for the optimisation of the power MOSFET performance. The original planar gate was substituted by advanced trench gate designs in the 1990's, in almost all the commercial power VDMOS transistors due to the strong increase of the integration density and the current capability<sup>7</sup>. The  $sR_{on}$  can be reduced when a Trench MOS (UMOS) is used because the channel density is larger if a smaller cell pitch is used<sup>4</sup>. However, the large trench wall area leads to an increase of the  $Q_g$  value, typically twice of the corresponding planar gate value with the subsequent reduction of the operating frequency<sup>4</sup>. Cross sections of power VDMOS and UMOS transistors are plotted in Fig.2.4, respectively.

Fig.2.4. Cross sections of power transistors. (a) VDMOS with planar gate and (b) UMOS with trench gate.

The real  $V_{bd}$  value of a power VDMOS is lower than that of its basic cell due to the high electric field peaks at edge of the active area where the curvature of the  $P_{body}/N_{epi}$  junction is not self-protected, leading to the crowding of the potential lines.

Therefore, the implementation of a robust and area-efficient edge termination is crucial to achieve reliable operation in the field. The edge termination is basically used to smooth the electric field from the end of the active area to the edge of the device, avoiding a premature breakdown in the curvature of the  $P_{body}$  diffusion. There are two ways to implement an efficient edge termination for power VDMOS and UMOS transistors: floating guard rings or metal field plates, depending on the desired voltage capability. The metal field plate is typically used in low voltage power MOSFETs ( $V_{bd}$ <50 V) while the floating guard rings are used for medium and high voltage power MOSFETs. A Field Oxide (FOX) growth is required in both cases to protect the Silicon surface from high electric field peaks at the metal corners. The floating guard rings are implemented by implanting several P-type rings, whereas the metal field plate consists on the enlargement of the source metal over the FOX<sup>4</sup>. An edge termination combining floating guard rings and a metal field plate is also feasible.

The main FOMs for a 30V VDMOS and UMOS transistors are presented on Table 2.1 (see definitions in Eq. 5-7)  $^7$ . Notice that in all cases, the performance of UMOS transistors is better than that of the VDMOS counterparts, since the  $R_{on}$  decrease is more relevant than the  $Q_g$  increase. Therefore, nowadays the power MOSFET market is dominated by the UMOS architectures even if its switching performance is slightly degraded.

| FOM | VDMOS (30V)                 |                       | UMOS                   | (30V)                 |

|-----|-----------------------------|-----------------------|------------------------|-----------------------|

|     | $V_{\rm gs} = 4.5 \ { m V}$ | $V_{gs}=10 \text{ V}$ | $V_{gs}=4.5 \text{ V}$ | $V_{gs}=10 \text{ V}$ |

| A   | 64000                       | 32000                 | 7085                   | 3720                  |

| В   | 30,9                        | 15,5                  | 15,6                   | 8,2                   |

| С   | 303                         | 152                   | 120                    | 63                    |

Table 2.1. Basic FOMs for a 30 V VDMOS and UMOS transistors.

$$FOM (A) = \frac{R_{on}}{C_{in}}$$

(Eq.5)

$$FOM(B) = R_{on} * C_{iss}$$

(Eq.6)

$$FOM(C) = R_{on} * Q_{gd}$$

(Eq.7)

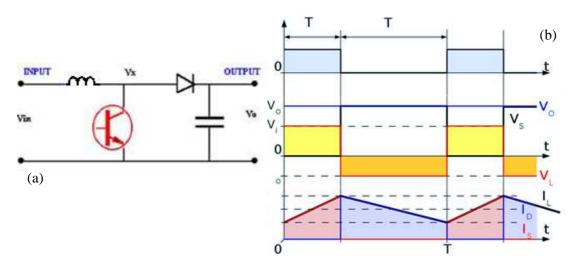

Power UMOS transistors are basically addressed to low voltage DC/DC converters<sup>2</sup> for telecommunication applications and switched mode power supplies (basically for the Power Factor Correction circuits<sup>8</sup>). Applications for medium voltage range (150 to 600 V), basically in the automotive industry, were implemented with power BJTs. However, the limited switching frequency of BJTs due to their bipolar nature and the need to increase the switching frequency of the systems, lead to the gradual replacement of the BJTs by power MOSFETs. As an example, a basic Boost Converter (step-up converter) is shown in Fig.2.5-(a), with a power MOSFET as a switch. A voltage pulse is applied to the gate of the MOSFET to control the duty cycle and output voltage. When a positive bias is applied to the gate, the MOSFET turns-on and

the power diode turns-off. On the opposite, when the gate is ramped down to ground the MOSFET turns-off and the power diode starts conducting. The inductor is charged when the MOSFET is in the on-state, as shown in the *I-V* curves plotted in Fig.2.5-(b), while the output voltage comes from the capacitance. Once the MOSFET is turned-off the output voltage comes from the inductor, whereas the capacitor is charged. The switching frequency has to be high enough to be sure that the inductor is not completely discharged at the end of each period with the subsequent output voltage fluctuations. Typical  $V_{in}$  and  $V_{out}$  values in automotive applications are 90 and 400 V, respectively, what means that the MOSFET has to sustain at least 400 V in the off-state. Therefore, when the power MOSFET is turned-off, its intrinsic diode has to handle 400 V. Unexpected transients can appear in real converter application, as device snappy switching behaviour, voltage spikes, static discharge, and oscillations<sup>9</sup>, which will make  $V_x$  be greater than 400 V (even 1/3 higher). These transients are voltage or current changes in a short period of time (100 ns range)<sup>10</sup>. Although these transients do not occur in every switching cycle during normal circuit operation, as a protection, the MOSFET has to properly operate in the off-state (when it behaves as a diode).

Fig.2.5. (a) Basic schematic circuit of a Boost converter. (b) I-V curves for the Boost converter.

# 2.2. Enhancing the vertical Power MOSFET: SJ Concept

As already stated, the most important contribution to the  $sR_{on}$  value in a power 600 V VDMOS transistor comes from the  $N_{epi}$  layer and the series resistance of this layer increases with the  $V_{bd}$  due to the necessary reduction of the doping concentration. In this sense, the only possible way to integrate power MOSFETs combining a high voltage capability (> 600 V) and a competitive on-state resistance is using a new device concept to break the so-called "Silicon Limit" of conventional architectures, which is proportional to  $R_{on}\alpha V_{bd}^{2.5 \, 11}$ . Focused on the improvement of the  $sR_{on}$ - $V_{bd}$  trade-off, the Super Junction (SJ) concept was introduced in the late 1990s<sup>12,13</sup>. The key point is to replace the  $N_{epi}$  layer by alternating thin columns of opposite doping, as shown on the

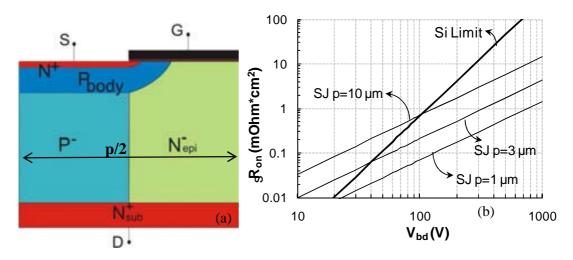

schematic cross-section drawn in Fig.2.6-(a). When the drain bias is applied, a depletion layer is simultaneously created under the gate electrode ( $P_{body}/N_{epi}$  junction) and in the vertical junction formed by the P/N columns in the drift region, in such a way that a 2D charge coupling that improves the electric field distribution is feasible<sup>4</sup>. As a consequence, the  $N_{epi}$  doping level can be increased and the final  $R_{on}$  value is significantly lower than that of the conventional power VDMOS counterpart, breaking the "Silicon Limit" as shown on the  $sR_{on}$ - $V_{bd}$  FOM reported on Fig.2.6-(b). This graph is based on the drift region of a SJ power MOSFET as the one drawn in Fig.2.6-(a) with identical N and P pillars width.

Fig.2.6. (a) Cross section of a basic SJ structure (half-cell). (b)  $V_{bd}$ -s $R_{on}$  FOM for SJ power MOSFETs for different cell pitch (p).

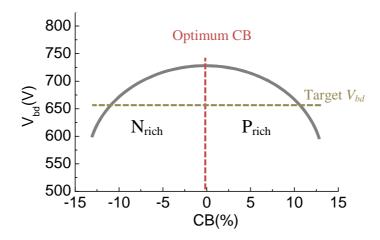

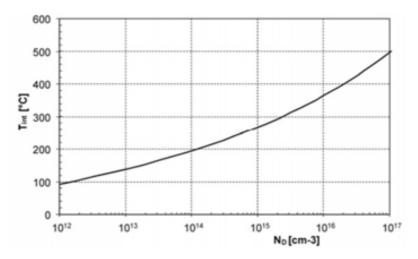

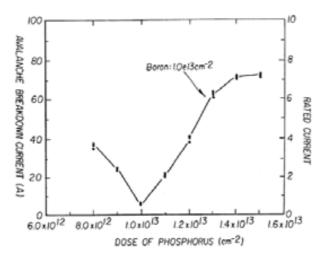

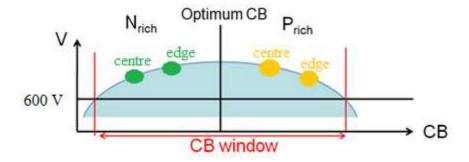

The electric field in the Silicon volume of SJ devices is determined by the net charge in both columns (P and N). The ratio between the charges in each column is defined as the Charge Balance (CB) and it is normally given as a percentage (see Eq.8, being  $N_{conc}$  the Phosphorous concentration in the N column and  $P_{conc}$  the Boron concentration in the P column). When the net charge is perfectly compensated between the columns (Optimum CB condition) a rectangular vertical electric field distribution is achieved in the P/N columns junction, leading to the highest  $V_{bd}$  value. The  $V_{bd}$  value of the SJ structure strongly depends on the net charge balance, as shown in Fig.2.7. Positive or negative CB conditions leads to the bending of the equipotential lines and to the creation of an electric field peak at bottom or top of the SJ structure, respectively with the subsequent reduction of the  $V_{bd}$  value. The fast  $V_{bd}$  decrease with a small variation of the CB condition leads a CB margin for the process sensitivity in the range of 10%. In this thesis, positive and negative CB conditions account for  $P_{rich}$  and  $N_{rich}$  SJ structures, respectively. A more detailed study on the electrical behaviour of devices with different CB conditions is reported on Chapter 3.

$$CB = \frac{P_{conc} - N_{conc}}{N_{conc}} \qquad (\%)$$

(Eq.8)

Fig.2.7. Schema of the  $V_{bd}$  dependence on the CB condition.

Going back to the FOM reported in Fig.2.6-(b), notice that the  $sR_{on}$ - $V_{bd}$  trade-off decreases with the p value. The  $sR_{on}$  is reduced since the width of the pillars decreases with the p value and the doping concentration is increased to maintain the desired voltage capability<sup>1</sup>. The  $V_{bd}$  value is not degraded since the doping concentration of both pillars can be increased. Therefore, if the p reduction is feasible from the lithography point of view, a better  $sR_{on}$ - $V_{bd}$  trade-off can be achieved. The new ideal  $sR_{on}$ - $V_{bd}$  trade-off in the SJ structures is described by Eq.9, where  $W_N$  and  $W_P$  are the widths of N and P columns, respectively, and  $E_C$  is the critical electric field<sup>4</sup>. The improvement of the  $R_{on}$  value is basically due to the modified depletion process as a consequence of the P column implementation, leading to an almost rectangular equipotential distribution in the basic cell of the SJ structure<sup>4</sup>.

$$R_{on-idealSJ} = \frac{V_{bd}}{\varepsilon_S \mu_n E_C^2} \left( \frac{W_N + W_P}{2} \right)$$

(Eq. 9)

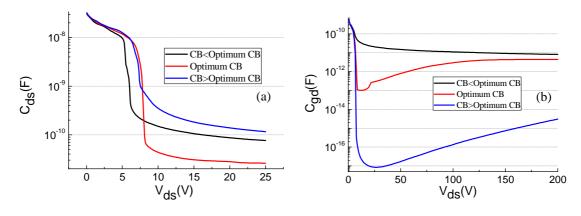

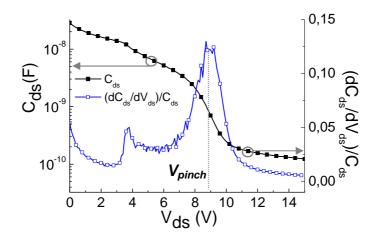

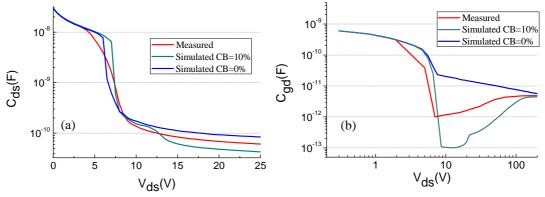

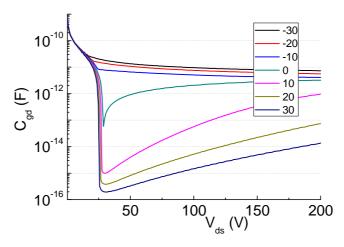

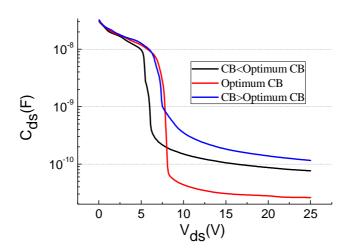

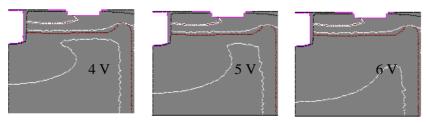

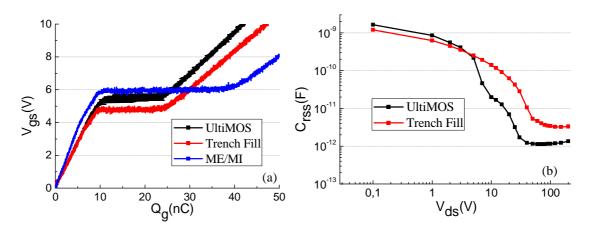

It was described that the  $C_{oss}$  and  $C_{rss}$  values decrease with the drain voltage in the case of a power VDMOS transistor. However, the full depletion of the SJ pillars is typically achieved at low voltage values (less than 100 V), leading to a sharp decrease on the capacitance values at low voltage and to a significant improvement of the switching frequency in comparison with the power VDMOS counterpart <sup>14</sup>. The  $Q_g$  is also reduced when using a SJ MOSFET instead of a UMOS transistor. A more detailed study on the capacitive behaviour of SJ MOSFETs for different CB conditions is reported on section 3.3.2.

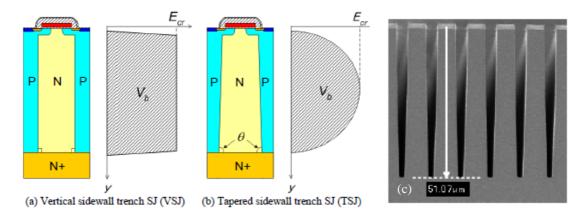

#### 2.3. Different SJ-MOSFET structures

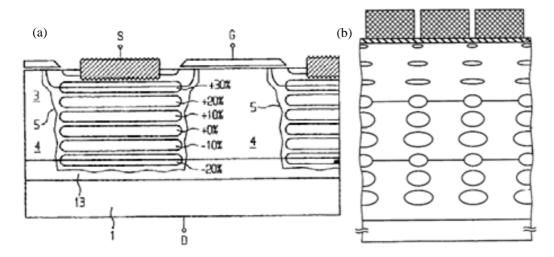

The idea of this section is to give a brief description of the different technologies used to implement power SJ transistors. The first commercial power MOSFET implemented with the Super Junction concept was called the CoolMOS<sup>TM</sup> (by Infineon)<sup>15</sup>. The technological integration of a CoolMOS<sup>TM</sup> transistor requires the

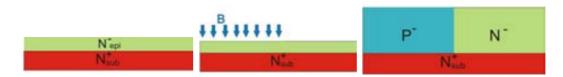

repeated iteration (5-6 times) of the growth of several microns of N doped epitaxial layer followed by the subsequent Boron masked implantation (Fig.2.8), known as multi-epitaxy/multi-implant (ME/MI) technology. The exact number of iterations depends on the desired final column depth which will set the  $V_{bd}$  value. It has to be considered that the first Boron implant is submitted to the thermal budget of the 5-6 epitaxial growths. Opposite, the last Boron implant is just submitted to one drive-in process. As a consequence, different mask windows are mandatory to implement straight vertical pillars at the end of all the ME/MI steps. This is a Global CB approach, meaning that the whole silicon active area contributes in the charge balance when the structure is reversed biased.

Fig.2.8. Basic schema of the ME/MI technology for the integration of a CoolMOS<sup>TM</sup> transistor: (a)  $N_{epi}$  growth, (b) Boron implant and (c) final structure after 5 iterations.

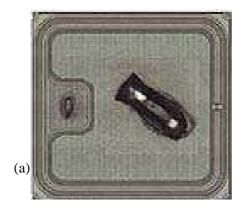

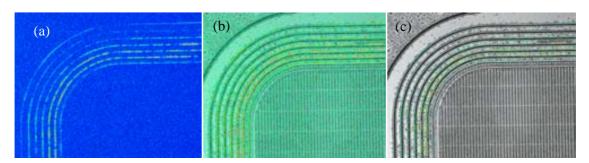

The area of power devices has to be minimized in order to increase the number of devices per wafer in a production line. There are different ways to reduce the device area, as implementing a trench gate or increasing the doping concentration of the pillars to make them thinner<sup>16</sup>. However, the cell pitch in the case of the ME/MI structure is limited by the multiepitaxial growth process. When Boron implants are diffused at high temperature during the epi growth steps, it is necessary to have a minimum pitch to ensure the correct fabrication of the separated deep P columns. The cell pitch could be reduced if a lower thermal budget is used. Therefore, less Boron would laterally diffuse but the number of subsequent epitaxial growths would increase to reach identical column depth and so the cost of each CoolMOS<sup>TM</sup> transistor. The edge termination of the CoolMOS<sup>TM</sup> transistor is also implemented with alternating P and N-type columns, thicker and more spaced than those of the active area, using the same mask sequence. In this way, the electric field will decrease smoothly in the edge termination region. The last Boron implant is skipped and a Field Plate is used to enhance the field distribution on the edge termination<sup>17</sup>. A top view of the CoolMOS<sup>TM</sup> SPP02N80C3 transistor is shown on Fig.2.9-(a) 18, with the gate located at the left side and the remaining metal of the source wire in the middle of the active area. Two P-type pillars are shown in the image obtained with the Scanning Capacitance Microscopy (SCM) technique (Fig.2.9-(b) 18). The waved shape of the pillar walls gives evidence about how the pillars are formed: six epitaxial layers are grown with the Boron implant after each growth step.

Fig.2.9. (a) Top view and (b) SCM image of the ME/MI technology for the integration of the CoolMOS $^{\text{TM}}$  SPP02N80C3 MOSFET. Adapted from  $^{18}$ .

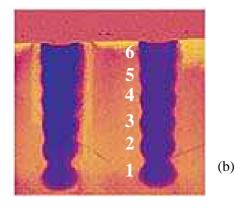

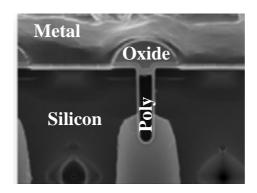

Another approach to implement a Global CB MOSFET is based on deep trenches etched on a high doped N-type substrate and filled with a selectively grown P-type epitaxial layer<sup>19,20,21</sup> (Toshiba, Fuji Electric, Fairchild and Toyota). The resulting SJ power MOSFET exhibits a lower *sR<sub>on</sub>* value since the N-type pillar is thinner than that of the CoolMOS<sup>TM</sup> counterpart implemented with the ME/MI technique. The main drawback of the filled deep trench approach is the eventual creation of a void in the middle of the P-type trench during the epitaxial growth when the trench becomes closed before the complete fill. This effect can be observed on the SEM images corresponding to the DTMOS-4 transistor (Toshiba) captured on Fig.2.10<sup>19</sup>. These devices use a trench gate architecture that contributes to the reduction of the gate charge and the switching losses. The trench gate is shown in Fig.2.11, located in between the P-type pillars, labelled as Poly. The N-type substrate can be seen at the bottom of the trench gate.

Fig.2.10. (a) Basic schema of the trench fill technology and (b) SEM cross section of the DTMOS-4 transistor (Toshiba). Adapted from  $^{19}$ .

Fig.2.11. SEM cross section showing the trench gate and the top of the pillars for the DTMOS-4 transistor (Toshiba). Adapted from <sup>19</sup>.

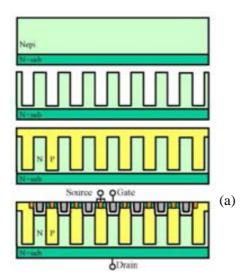

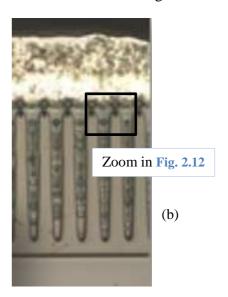

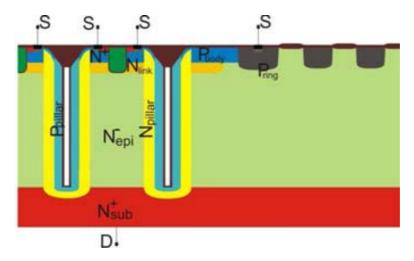

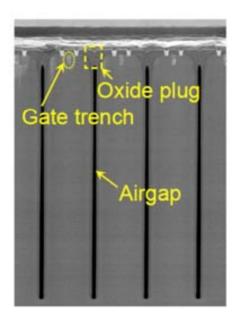

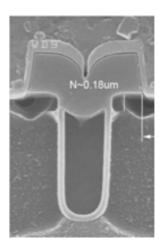

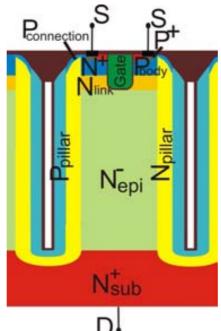

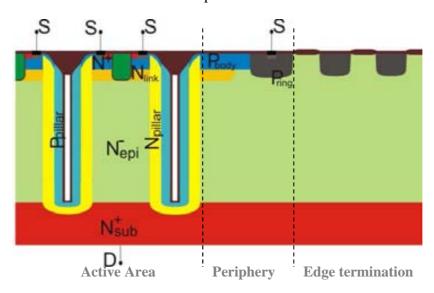

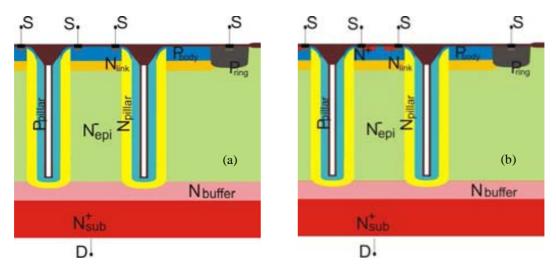

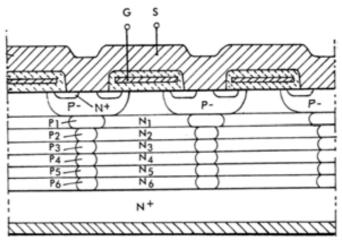

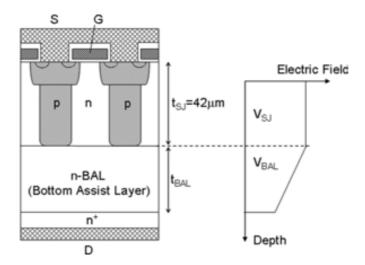

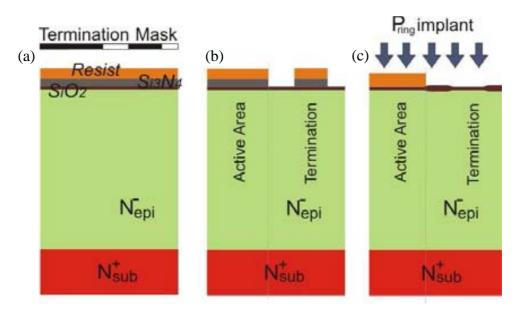

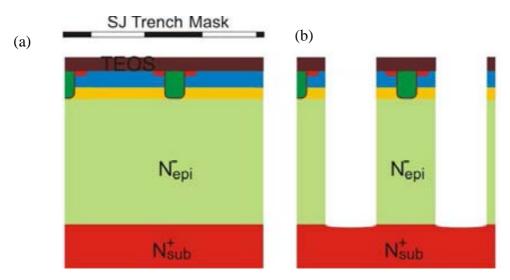

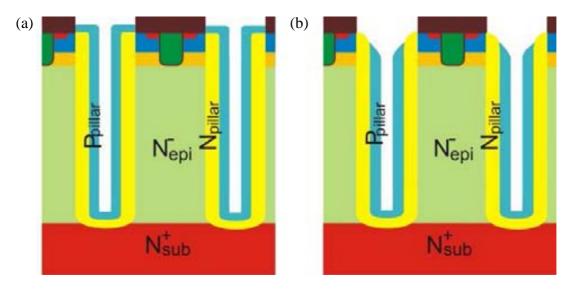

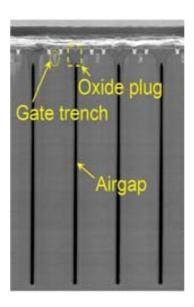

A novel possibility to apply the SJ concept to high voltage MOS transistors is known as Local CB, meaning that just a region of the structure contributes to the charge coupling in the silicon volume. The UltiMOS transistor (ON Semiconductor) is a vertical Local CB device: the first one was presented 10 years ago<sup>21</sup>, but it is not reported that it ever went in production. The UltiMOS structure is implemented by etching deep trenches in a lowly doped N-type substrate with the subsequent filling of the trench with a high doped N and P-type epitaxial layers <sup>22,23</sup> (see Fig.2.12) and the final sealing of the trenches with an oxide plug. Given that the N<sub>epi</sub> layer basically works as a mechanical support, the cell pitch can be reduced if compared with the previous Global CB approach, since only the width of the gate trench needs to be ensured between adjacent deep trenches, leading to a reduction of the on-state resistance. The SEM image of the UltiMOS active area (see Fig.2.13) shows the gate trench at the top of the structure and the void in the middle of the SJ trenches with the oxide plug on top. The edge termination of the UltiMOS transistor is implemented with the conventional floating guard rings technique, in contrast with the Global CB SJ power MOSFETs where this technique cannot be used due to the high doping concentration of the epitaxial layer<sup>4</sup>.

Fig.2.12. Cross section of the UltiMOS structure.

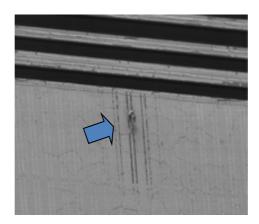

Fig.2.13. SEM image of an UltiMOS transistor. (a) Complete vision of the vertical pillars and (b) zoom in the gate region. Adapted from  $^{23}$ .

## 2.4. Main requirements of the SJ MOSFET transistors

This thesis is dedicated to the study of the 20 A SJ power MOSFET transistors with a voltage capability in the range of 600 V. Nowadays, there are several companies that have launched their SJ MOSFET into the market. An exhaustive optimisation task has to be performed in every new power device before becoming a commercial product to be sure that the electrical performances in the state-of-the-art and superior to the competitors in some of the most relevant parameters. Moreover, new power devices have to be competitive on cost and energy efficient in circuit operation. There are several standard tests to quantitatively compare power MOSFETs when making a choice for a certain application. As introduced, the SJ power MOSFET transistors are basically designed to be used in applications such as switched mode power supply synchronous rectifiers where the internal body diode can be activated when the device turns off<sup>24</sup>. Different parameters have to be optimized in a power transistor to accomplish with the market requirements:

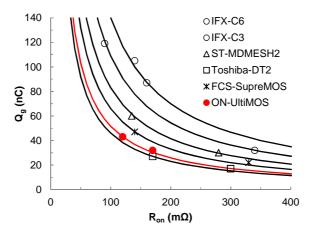

• An optimum  $R_{on}$ - $V_{bd}$  trade-off minimizes the conduction losses. The  $R_{on}$  of a SJ power MOSFET has to be in the range of 150-250 m $\Omega$  to be commercially competitive in the 600 V, 20 A market. The  $R_{on}$ - $V_{bd}$  values for different commercial power MOSFETs are plotted in Fig.2.14.

Fig.2.14.  $V_{bd}$ - $R_{on}$  FOM for commercial SJ power MOSFETs.

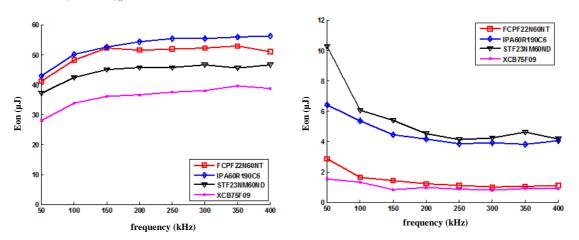

• The  $C_{rr}$  and the  $C_{oss}$  capacitances have a strong impact on the switching time, thus they need to be minimized. The  $Q_g$  value ( $Q_{gs}+Q_{gd}$ ) determines the gate drive loss and it is extremely dependant on the gate voltage<sup>6</sup>. In high-frequency applications (higher than the standard 100-300 kHz) a low FOM  $sR_{on}\cdot Q_g$  is required to obtain a high performance transistor<sup>25</sup>. On the other hand,  $C_{oss}$  is ruled by the  $C_{ds}$  capacitance as already explained, which basically depends on the device architecture. Competitive capacitive values for four commercial 600 V and 20 A SJ power MOSFETs are detailed in Table 2.2. The voltages at which the measurements are performed are defined in Table 2.3. However, Infineon's counterpart is rated for  $I_d$ =25-30 A (IPB60R125CP), where the chip area might be increased, leading to a lower  $R_{on}$  value. The package for all the devices is the TO-220FP. Notice that the Toshiba counterpart has the lower  $R_{on}\cdot Q_g$  value. Thus, from the point of view of reducing the swithing losses, this device should be selected.

|                                 | Toshiba<br><i>TK20E60U</i> | STMicroelectronics<br>STP26NM60N | Infineon<br>IPB60R125CP | Fairchild <i>FCP20N60</i> |

|---------------------------------|----------------------------|----------------------------------|-------------------------|---------------------------|

| $R_{on}\left(\Omega\right)$     | 0.165                      | 0.135                            | 0.125                   | 0.15                      |

| $Q_g$ (nC)                      | 27                         | 60                               | 53                      | 75                        |

| $Q_{gs}$ (nC)                   | 16                         | 8.5                              | 12                      | 13.5                      |

| $Q_{gd}$ (nC)                   | 11                         | 30                               | 18                      | 36                        |

| $R_{on} \cdot Q_g (m\Omega nC)$ | 4455                       | 8100                             | 6625                    | 11250                     |

| $C_{iss}$ (pF)                  | 1470                       | 1800                             | 2500                    | 2370                      |

| Coss (pF)                       | 3500                       | 115                              | 120                     | 1280                      |

| $C_{rss}$ (pF)                  | 150                        | 1.1                              | -                       | 95                        |

Table 2.2.  $R_{on}$ , Capacitive and charge values for commercial SJ MOSFET.

| Measurement voltage | Toshiba<br><i>TK20E60U</i> | STMicroelectronics<br>STP26NM60N | Infineon <i>IPB60R125CP</i> | Fairchild <i>FCP20N60</i> |

|---------------------|----------------------------|----------------------------------|-----------------------------|---------------------------|

| Q                   | 400 V                      | 480 V                            | 350 V                       | 480 V                     |

| С                   | 10 V                       | 50 V                             | 100V                        | 25 V                      |

Table 2.3.  $V_{ds}$  at which the capacitance (C) and charge values (Q) listed in Table 2.2 are measured.

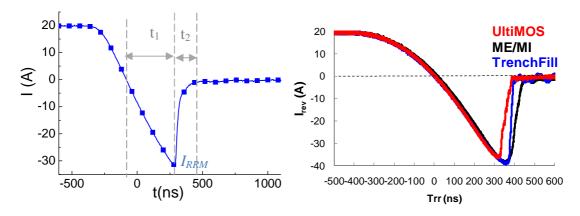

• The Reverse Recovery characteristics of the internal diode determine the reverse recovery time ( $T_{rr}$ ) value, quantifying the time to remove the charge during turn-off and **how fast the device can be switched off under extreme conditions** (see Appendix B). Therefore, the  $T_{rr}$  needs to be as short as possible since no positive bias can be applied to the gate until the diode is completely turned off, thus limiting the device operating frequency. The reverse recovery charge ( $Q_{rr}$ ) to be removed during the diode turn-off has to be also minimized to decrease the switching time. However, the turn-off behaviour of the intrinsic diode of all the SJ power MOSFETs is relatively poor when compared with an optimized equivalent power diode. Since the recovery of the SJ diode has a very steep di/dt, the occurrence of high frequency and high amplitude recovery oscillations during transients is more possible  $^{24}$ . The comparison of the  $T_{rr}$  and  $Q_{rr}$  values for commercial SJ power MOSFETs is provided in Table 2.4. From the point of view of recovering after a high voltage peak, the more robust device is the STMicroelectronics counterpart.

|                       | Toshiba<br><i>TK20E60U</i> | STMicroelectronics<br>STP26NM60N | Infineon<br>IPB60R125CP  | Fairchild <i>FCP20N60</i> |

|-----------------------|----------------------------|----------------------------------|--------------------------|---------------------------|

| $T_{rr}(\mathbf{ns})$ | 450                        | 370                              | 430                      | 530                       |

| $Q_{rr}(\mu C)$       | 8.1                        | 5.8                              | 9                        | 10.5                      |

| Test<br>Set-up        | 20 A,<br>di/dt=100μA/μs    | 20 A,<br>di/dt=100μA/μs          | 400 V,<br>di/dt=100μA/μs | 20 A,<br>di/dt=100μA/μs   |

Table 2.4.  $T_{rr}$ ,  $Q_{rr}$  and measurement conditions for different commercial SJ power MOSFETs.

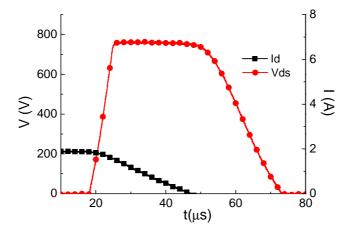

• The UIS test evaluates the energy capability when an inductor is discharged through the internal body diode of a power MOSFET. The body diode is forced to handle a high voltage during a certain periode of time, which is translated in a lot of power dissipation requirements. Normal values of commercial SJ power MOSFET transistors are in the range of 340-600 mJ for a given area (from commercial datasheets). Values for different commercial components are detailed in Table 2.5. Notice that the Toshiba counterpart is measured with a fixed inductance value whereas all the other are performed at a fixed current level, sweeping the inductance. For further details on these tests, see Appendix B. Notice that, even the Toshiba counterpart would be selected for the swithing characteristics, the  $E_{AS}$  value is quite low.

|                       | Toshiba<br>TK20E60U         | STMicroelectronics<br>STP26NM60N | Infineon<br>IPB60R125CP     | Fairchild <i>FCP20N60</i>     |

|-----------------------|-----------------------------|----------------------------------|-----------------------------|-------------------------------|

| $E_{AS}(\mathbf{mJ})$ | 114                         | 610                              | 636                         | 690                           |

| Test<br>set-up        | $L=0.63$ mH, $R_g=25\Omega$ | $V_{dd}$ =50V, $I_d$ =6 A        | $V_{dd}$ =50V, $I_d$ =5.2 A | $V_{dd}$ =50V,<br>$I_d$ =10 A |

Table 2.5.  $E_{AS}$  and measurement conditions for different commercial SJ power MOSFETs.

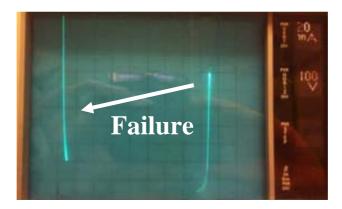

UIS and Reverse Recovery tests are performed under extreme conditions and the device under test is usually driven to failure. In this sense, both tests provide relevant information about the device robustness. However, just the UIS test is used in commercial datasheets to give the amount of energy that the device can handle while the Reverse recovery is used to quantify the time to recover when the device is submitted to hard switching conditions.

Concluding, the main commercial SJ power MOSFETs have been presented. The selection of a particular device is strongly dependent on the requirements of each application (switching speed, robustness, internal diode behaviour).

## 2.5. References

<sup>&</sup>lt;sup>1</sup> B. J. Baliga, "Modern Power Devices", John Wiley & Sons, 2nd edition (1987).

<sup>&</sup>lt;sup>2</sup> J. Lutz, H. Schlangenotto, U. Scheuermann, R. De Doncker. "Semiconductor Power Devices: Physics Characteristics", Reliability. Springer (2011).

<sup>&</sup>lt;sup>3</sup> J. Fernández, S. Hidalgo, J. Paredes, F. Berta, J. Rebollo, J. Millán, F. Serra-Mestres, "An ON-resistance closed form for VDMOS devices", EDL, vol. 10, No. 5 (1989).

<sup>&</sup>lt;sup>4</sup> B.J.Baliga, "Advanced Power MOSFET concepts", Ed. Springer, ISBN 978-1-4419-5916-4 (2010).

<sup>&</sup>lt;sup>5</sup> A.Villamor, I. Cortés, D.Flores, J.Roig, F.Bogman, P.Vanmeerbeek, P. Moens, "*Capacitive behavior in Super Junction trench MOSFET devices*", Proc. CDE, pp. 1-4 (2011).

<sup>&</sup>lt;sup>6</sup> Application note, Renesas Electronics, Rev. 2.00, 2004.08.

<sup>&</sup>lt;sup>7</sup> B. Jayant Baliga, "Trends in Power Semiconductor Devices", ITED, vol. 43, No. 10, pp. 1717-1731 (1996).

ON Semiconductor: *Power Factor Correction Handbook*. Retrieved from http://www.onsemi.com/pub\_link/Collateral/HBD853-D.pdf. (2007).

<sup>&</sup>lt;sup>9</sup> "Causes and effects of transient voltages", STEDI-POWER website (http://www.tvss.net/).

<sup>&</sup>lt;sup>10</sup> R.D. Winters, "Power supply voltage transient: Analysis and protection", Presented at the Proc. of Powercon III, Power conversion conference (1976).

- P. Kondekar, HS. Oh, "Analysis of the Breakdown Voltage, the On-Resistance, and the Charge Imbalance of a Super-Junction Power MOSFET", Journal of the Korean Physical Society, vol. 44, no. 6, pp. 1565-1570 (2004).

- <sup>12</sup> T. Fujihira, "Theory of semiconductor superjunction devices", Jpn. J. Apl. Phys., vol.36, pp. 6254-6262 (1997).

- G. Deboy, M. Marz, J-P. Stengl. H. Sack, J. Tihanyi and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon", IEDM, pp. 683-685 (1998).

- <sup>14</sup> O.Alatise, N-A. Adotei, P. Mawby, "Super-Junction Trench MOSFET for improved energy conversion efficiency", Proc. ISGT Europe (Manchester), pp.1-5 (2011).

- <sup>15</sup> L.Lorenz, G. Deboy, A. Knapp and M. März, "COOLMOS a new milestone in high voltage Power MOS", Proc. EPE'99 Conf. (1999).

- <sup>16</sup> W. Saito, I. Omura, S. Aida, S. Koduki, M. Izmisawa, H. Yoshioka, H. Okumura, M. Yamaguchi, T. Ogura, "A 15.5 mΩcm2- 680V superjunction MOSFET reduced on-resistance by lateral pitch narrowing", Proc. ISPSD'06, pp. 300 (2006).

- <sup>17</sup> Zhijun Qu, "Termination structure for superjunction device", Patent No. US 20030011046 A1, IR Corp., 16 Jan (2003).

- http://micromagazine.fabtech.org/archive/06/04/chipworks.html.

- <sup>19</sup>http://www.i-micronews.com/reports/Toshiba-TK31E60W-4thgen-DTMOS-600V-Super-Junction-MOSFET/12/355/.

- <sup>20</sup> S. Iwamoto, K. Takahashi, H. Kuribayashi, S. Wakimoto, K. Mochizuki, H. Nakazawa, "Above 500V class Superjunction MOSFETs fabricated by deep trench etching and epitaxial growth", Proc. ISPSD'05, pp. 31-34 (2005).

- <sup>21</sup> S. Yamamuchi, T. Shibata, S. Nogami, T. Yamaoka, Y. Hattori, H. Yamaguchi, "200 V Super Junction MOSFET fabricated by high aspect ratio trench filling", Proc. ISPSD'06, pp. 1-4 (2006).

- <sup>22</sup> G. Loechelt, P. Zdebel, G. Grivna, "Semiconductor device having deep trench charge compensation regions and method", United States Patent No. US7.176.524 B2, Feb. 13 (2007).

- <sup>23</sup> P. Moens, F. Bogman, H. Ziad, H. De Vleeschouwer, J. Baele, m. tack, G. loechelt, G. Grivna, J. Parsey, Y. Wu, T. Quddus and P. Zdebel, "*UltiMOS: A Local Charge-Balanced Trench-Based 600v Super-Junction Device*", Proc. ISPSD'11, pp. 304-307 (2011).

- <sup>24</sup> M.T. Zhang, "Electrical, Thermal, and EMI designs of High –Density, Low-Profile Power Supplies", Thesis dissertation, (1998).

- <sup>25</sup> NXP Application Note: "Understanding Power MOSFET Data Sheet Parameters" (2013).

# **CHAPTER 3**

# **UltiMOS** structure

The main part of the experiments, measurements and simulations reported in this thesis have been performed on the power SJ UltiMOS structure. This chapter is basically conceived to have an insight in the device requirements based on the application which is designed for, the structure design, the electrical behaviour, and the available parameters to vary. The goal is to provide all the necessary information for a complete understanding of Chapters 4, 5 and 6. The technology process and the different used experimental techniques and simulation methods are detailed in Appendix A and B, respectively.

## 3.1. UltiMOS target

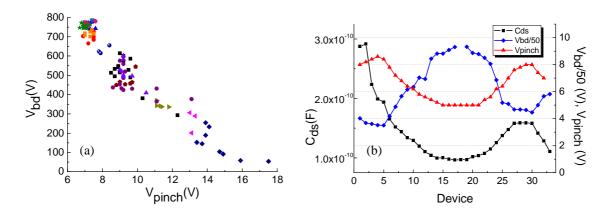

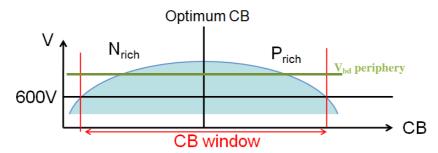

The UltiMOS structure is a SJ power MOSFET rated to 600 V applications, with a  $sR_{on}$  in the range of 20-25 m $\Omega$ cm<sup>2</sup> and a nominal current of 20 A<sup>1</sup>. As a rule of thumb, a power device designed for a certain voltage application range has to exhibit a higher voltage capability for a safe operation. In this sense, the target UltiMOS  $V_{bd}$  value is 650 V, although some measured devices and simulated structures during the investigation reach higher  $V_{bd}$  values, in the range of 750-800 V. The  $V_{bd}$  value is basically determined by the doping and the thickness of the SJ trenches<sup>2</sup>. A wide UltiMOS manufacturing window is needed to be able to go into the market and to ensure a high enough  $V_{bd}$  value to get the maximum yield (see schema on Fig.3.1). The 650 V needs to be still guaranteed even if the CB is varied, copping with the possible manufacturability variation. Therefore, different CB conditions are normally implemented for the different experiments performed during the UltiMOS optimization. Once the required  $sR_{on}$  value is reached, the  $N_{conc}$  is fixed in the fabrication process and the  $P_{conc}$  is modified to get the different CB conditions. The variation of the  $P_{conc}$  is not high enough to modify the  $sR_{on}$  value<sup>3</sup>. From the manufacturing point of view, there are different process steps that

need to be accurately defined to get the required results, as the SJ trench etch or the epitaxial growth (Appendix A).

Fig.3.1. A wide CB window has to be defined to have a manufacturable technological process.

## 3.2. Device description

The development of a new power device starts with the procuring of the main requirements, as the  $sR_{on}$  and the  $C_{rr}$  values. These basic parameters are optimised by a suitable choice of the active area design criteria with the help of TCAD simulations and clean room experiments. In this chapter the electrical behaviour of the UltiMOS transistor is explained and the technological requirements for the desired electrical performance are described. The function of the different layers and the critical parameters directly impacting the UltiMOS electrical performance (doping concentrations, junction depths, etc.) has to be studied. If an initial parametric analysis is performed, the tuning of the critical parameters during the UltiMOS optimization will be time efficient. The effect of the different parameters on the electrical UltiMOS performance is analysed separately for the active area and the edge termination due to the strong impact of the device periphery on its reliability in avalanche conditions.

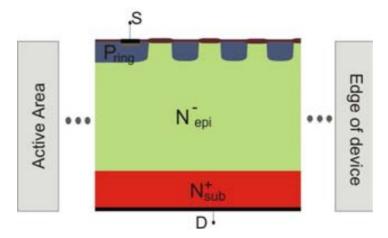

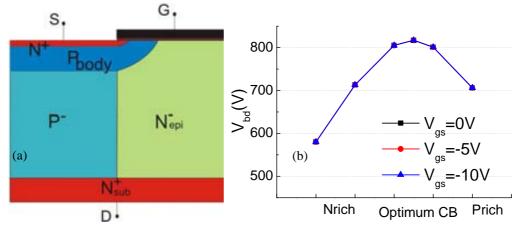

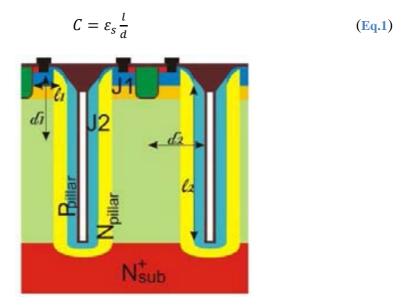

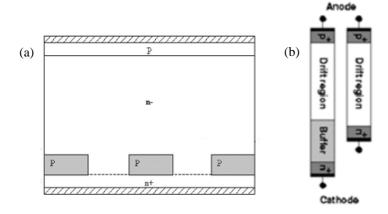

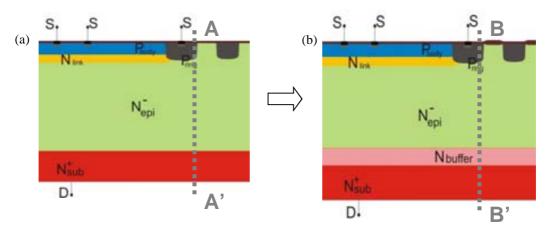

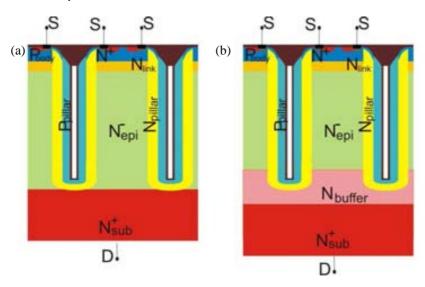

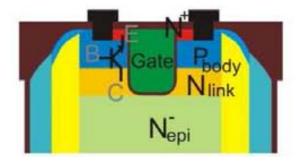

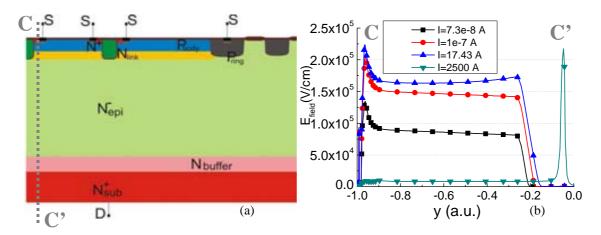

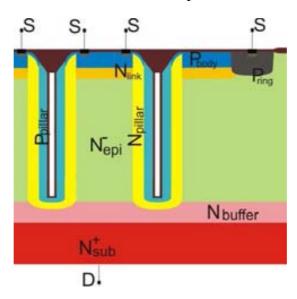

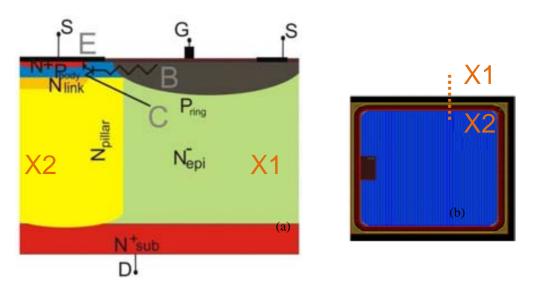

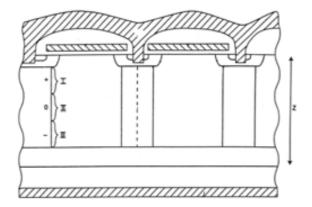

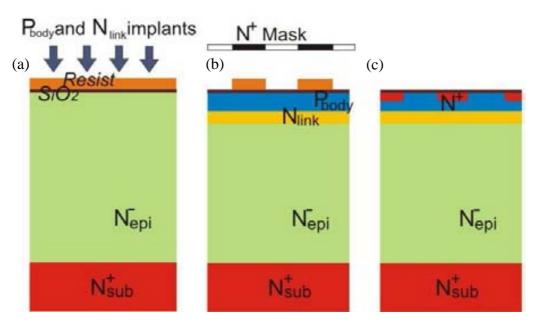

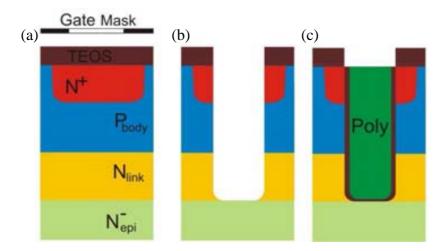

## 3.2.1. Active Area

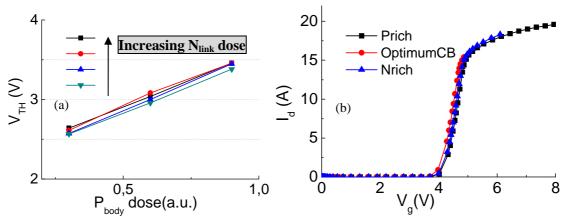

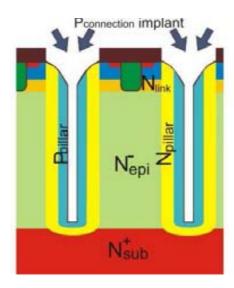

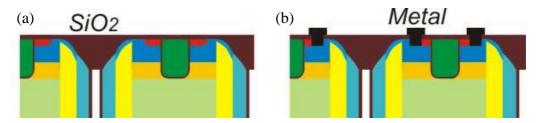

The UltiMOS active area consists on a thick  $N^-_{epi}$  layer, grown on the starting  $N^+$  substrate ( $N^+_{sub}$ ), where deep trenches are etched $^1$ . N and P-type epitaxial layers are grown on the sidewalls of the trenches ( $N_{pillar}$  and  $P_{pillar}$  layers). These trenches go into the  $N^+_{sub}$  layer, as shown in Fig.3.2, and are sealed with oxide, leaving a void in the middle. The regions directly contributing to the UltiMOS switching performance are implemented at the top of the structure: the  $N^+$ ,  $P_{body}$  and  $N_{link}$  diffusions and the gate trench. A P-type region is present at the top of the  $N_{pillar}$  to connect the  $P_{body}$  and the  $P_{pillar}$  regions to do not have a floating  $P_{pillar}$  that could introduce instabilities, parasitic diodes or BJT's activation, etc. The structure is homogeneous in depth from the bottom of the gate to the  $N^+_{sub}$  layer. The shallow  $N^+$  diffusion is placed at both sides of the gate trench top to minimise the on-state resistance and the consumed Silicon area at a given

current capability. The  $P_{body}$  layer is used to implement the MOSFET channel and mainly determines the  $V_{TH}$  value of the power transistor. Therefore, the channel length depends on the depth of the  $P_{body}$  diffusion. The source metal contacts the shallow  $N^+$  diffusion but also the  $P_{body}$  diffusion to do not leave this diffusion floating. The drain contact is placed at the bottom of the structure, on the  $N^+_{sub}$  layer. A detailed explanation of the whole technological process to achieve the described structure can be found in Appendix A.

Fig.3.2. Cross-section of UltiMOS active area.

## 3.2.1.1. Electrical behaviour and role of different regions

The main technological parameters are determined by the electrical requirements, and the device design needs to be done accordingly. For instance, the gate trench has to go into the  $N_{link}$  diffusion to avoid an increase on the  $sR_{on}$  and  $V_{TH}$  values. Moreover, the  $N_{link}$  needs also to be deep enough to do not counter dope the  $P_{body}$  region.

## • Threshold voltage (V<sub>TH</sub>)

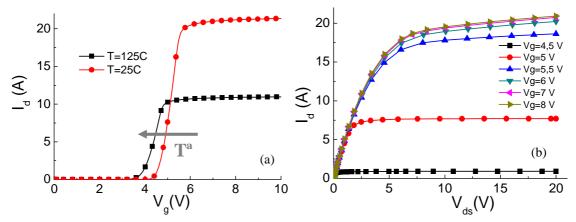

On Fig.3.3-(a) the simulated  $I_d$ - $V_g$  is plotted showing a  $V_{TH}$ =4.5 V, taken at  $I_d$ =250  $\mu$ A. It can be observed that when the device is switched on at high temperature, the  $I_d$  value in the on-state decreases a 50%, leading to a heavy increase of the  $sR_{on}$  value due to the decrease in mobility at high temperatures. On the other hand, when the temperature increases from 25 to 125 °C the  $V_{TH}$  decreases from 4.5 to 3.7 V, taken at  $I_d$ =250  $\mu$ A. Therefore, if the device is heated during its normal operation, it will not turn on provided the gate voltage is relatively high. On Fig.3.3-(b) the isothermal simulated  $I_d$ -

$V_{ds}$  characteristics for different  $V_g$  values are plotted. Note that when  $V_g$  is higher than 5 V the curves exhibit a slight current increase in the saturation mode.

Fig.3.3. Simulated UltiMOS (a)  $I_d$ - $V_g$  curves for different temperatures and (b)  $I_d$ - $V_{ds}$  curves for different  $V_g$  values.

## • Specific On-Resistance (\$R\_{on})

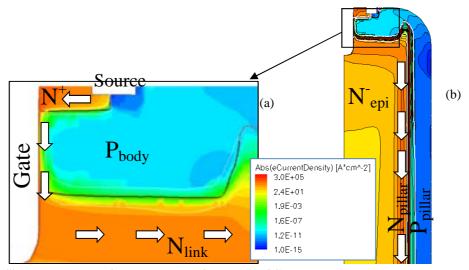

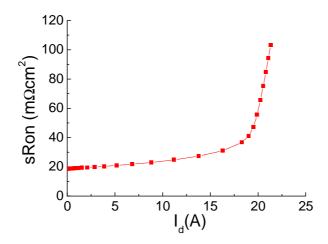

The N<sub>link</sub> diffusion is used to reduce the  $sR_{on}$  value: when the device is in the onstate, the current flows from the N<sup>+</sup> source through the channel created in the P<sub>body</sub> region, the N<sub>link</sub> diffusion and the N-type pillar to the drain contact (see Fig.3.4-(a) and (b)). The  $sR_{on}$  versus the  $I_d$  value is plotted in Fig.3.5. The  $sR_{on}$  value at 10 A is 22 m $\Omega$ ·cm<sup>2</sup>, taking into account the W of the device. Notice that the  $sR_{on}$  strongly increases when the current is in the range of 20 A (current saturation).

Fig.3.4. Simulated current flow at the top of the UltiMOS structure in the on-state when  $V_g$ =12 V and  $V_{ds}$ =20 V. (a) Zoom of the top part and (b) half-cell.

Fig.3.5. (a) Measured UltiMOS  $sR_{on}$ - $I_d$  curve at  $V_g$ =20 V.

## • Charge balance and voltage capability ( $V_{bd}$ )

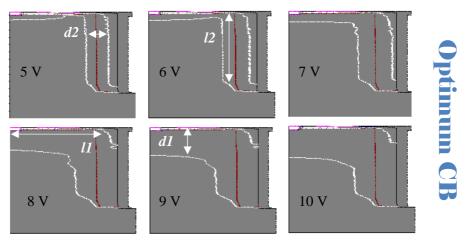

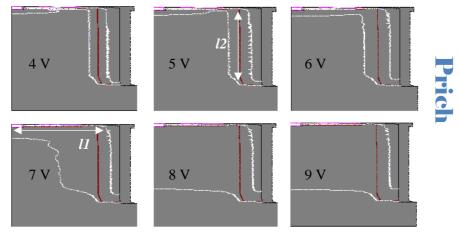

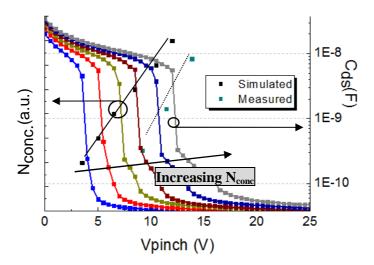

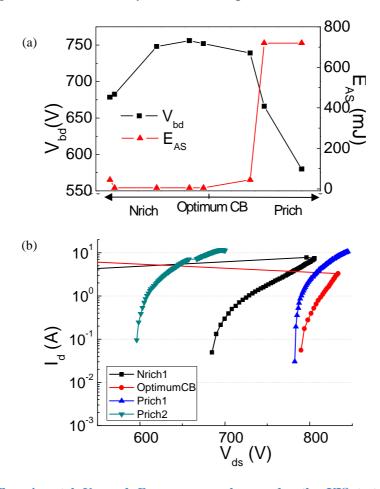

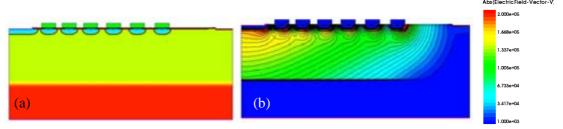

As introduced, the UltiMOS transistor is a Trench SJ power MOSFET structure, based on the Local CB approach where the two pillars (N-P) are the main contributors to the charge balance when the device is in the off-state. The  $N_{\rm epi}$  contribution on the CB is in the range of 3.3%, as derived from simulation results. This is translated as a 3.3% addition of majority carriers to the  $N_{\rm conc}$  for the CB calculation. The depletion behaviour of the structure depends on the CB condition, but all the structures become fully depleted at 15-20 V for any CB condition. The complete explanation of the depletion process at different CB conditions is detailed in section 3.3.2.

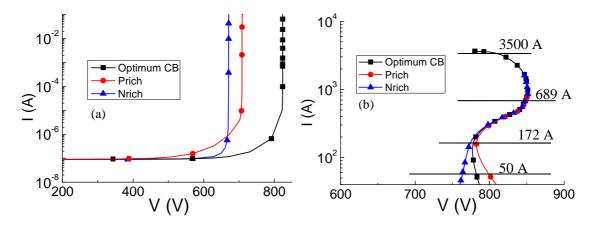

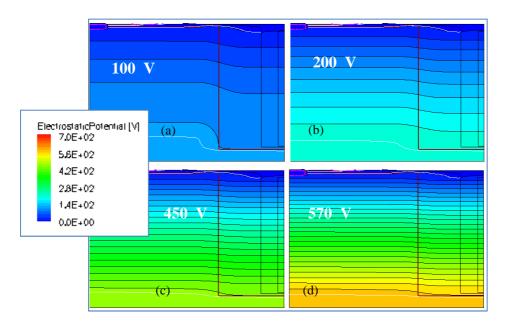

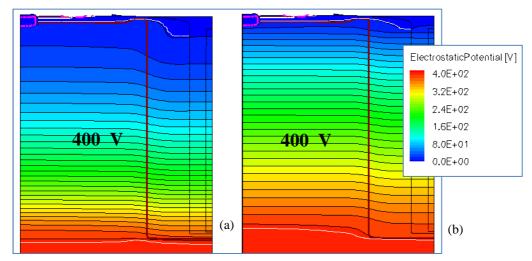

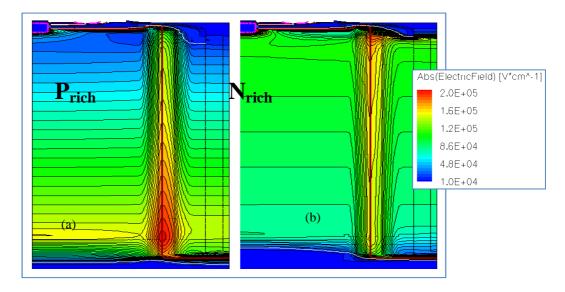

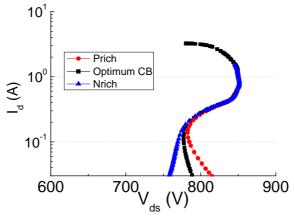

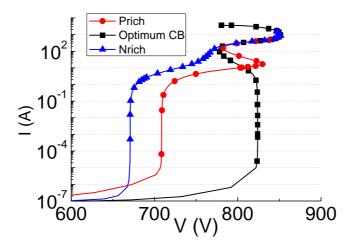

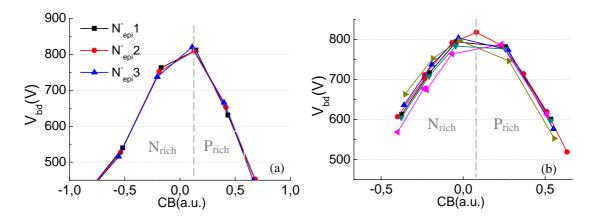

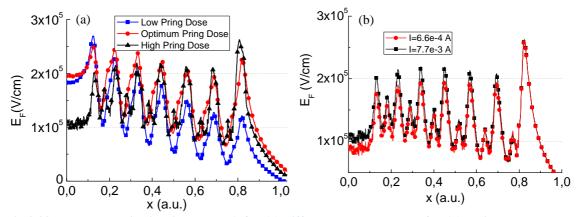

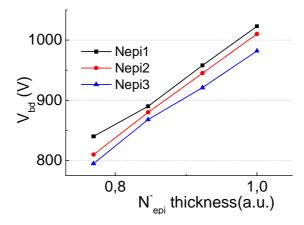

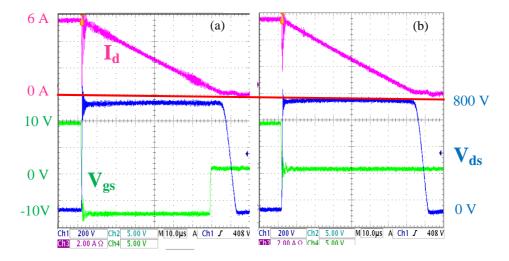

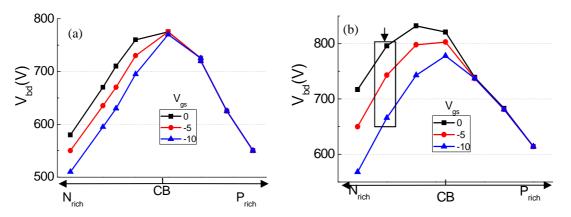

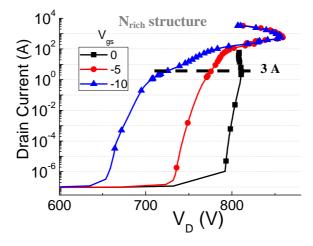

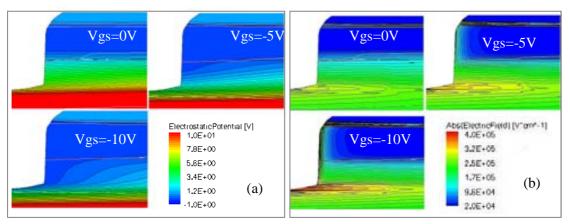

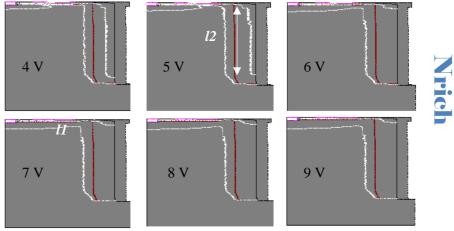

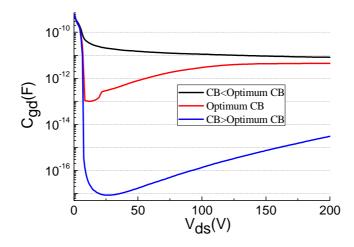

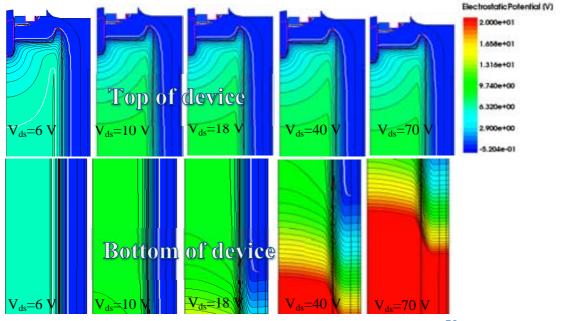

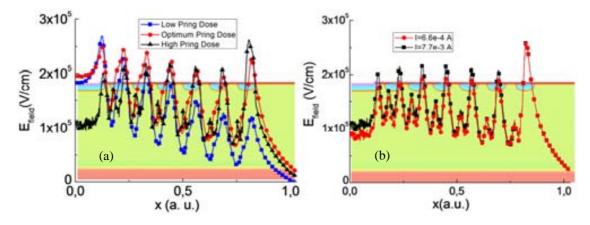

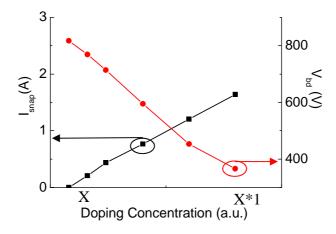

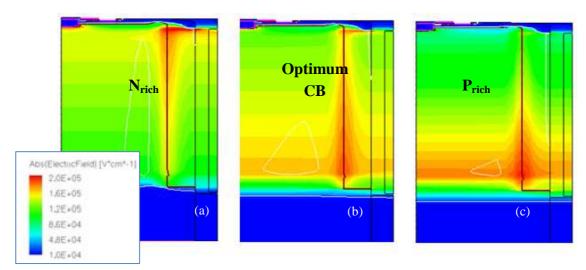

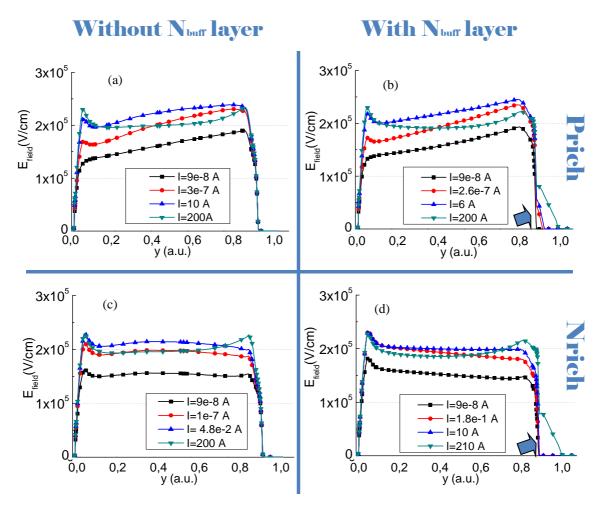

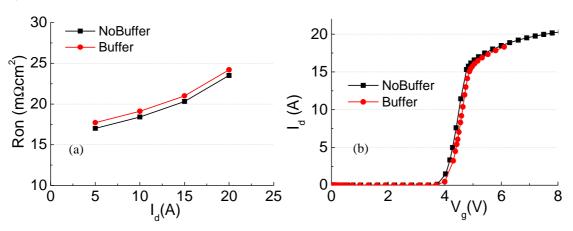

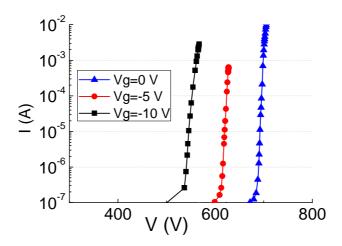

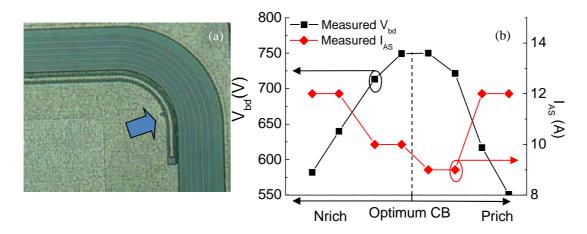

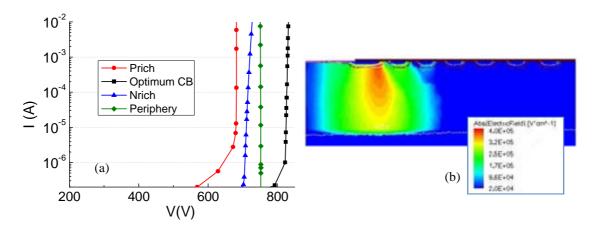

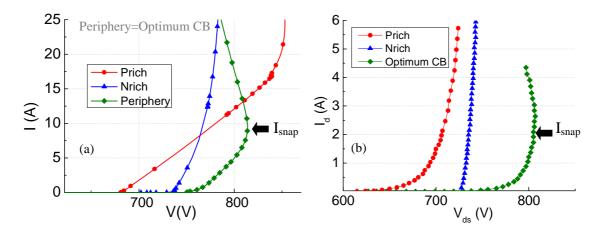

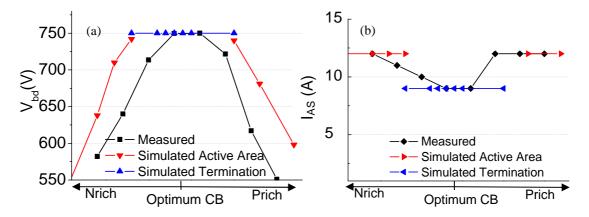

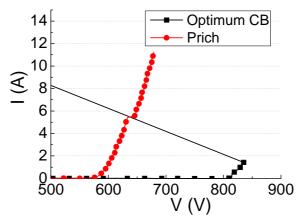

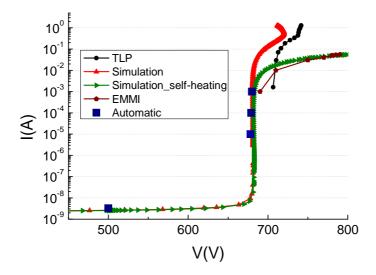

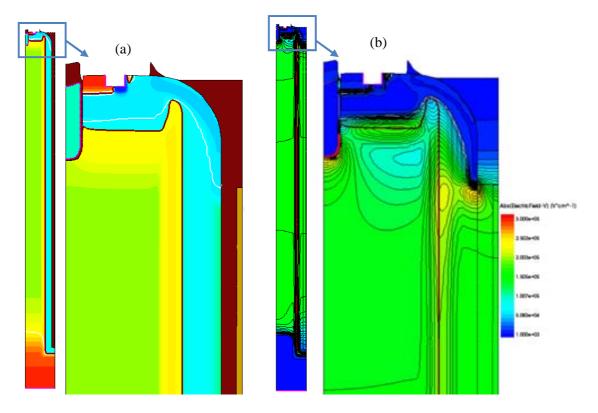

The  $V_{bd}$  value is one of the most important parameters on the UltiMOS design and it is very sensitive to small CB variations. Therefore, the  $V_{bd}$  value needs to be high enough to ensure a wide manufacturing window. The isothermal simulated  $I_d$ - $V_{ds}$  curves for different CB are plotted in Fig.3.6. The curves are scaled taking into account that the current is equally distributed in the whole active area. As expected, the  $V_{bd}$  value is maximum for the Optimum CB  $I_{d}$ - $V_{ds}$  curve, decreasing for both  $N_{rich}$  and  $P_{rich}$  cases (see Fig.3.6). The potential lines for different  $V_{ds}$  values are plotted in Fig.3.7. The vertical line where the potential distribution changes its shape is the interface between the N-P pillars. See that the lines tend to flatten when the  $V_{ds}$  increases. As inferred from Fig.3.8, the potential lines get closer at the top or at the bottom of the structure, for N<sub>rich</sub> or P<sub>rich</sub> devices, respectively. Accordingly, one can see in Fig.3.9 how the  $E_F$  peak has a different location depending on the CB condition: at the bottom of the SJ trench for the Prich and at the gate bottom/top of the SJ trench for the N<sub>rich</sub> case, following the potential lines crowding placement. This effect is typical for SJ structures, in exception of the  $E_F$  peak at the bottom of the gate, which is due to the trench gate architecture and the  $E_F$ crowding in that region<sup>4,5</sup>. The creation of an  $E_F$  peak at the gate bottom can be used to determine the CB condition, as detailed in section 3.3.1.

Fig.3.6. Isothermal simulated  $I_{d}$   $V_{ds}$  curves of the UltiMOS active area to determine the  $V_{bd}$  value for  $N_{rich}$ , Optimum CB and  $P_{rich}$  cases at (a) avalanche current level and (b) high current. The curves are scaled by the whole active area.

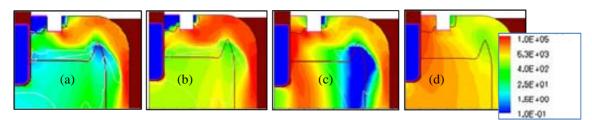

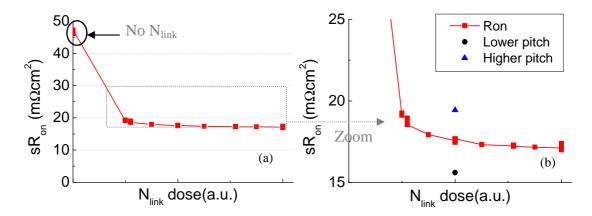

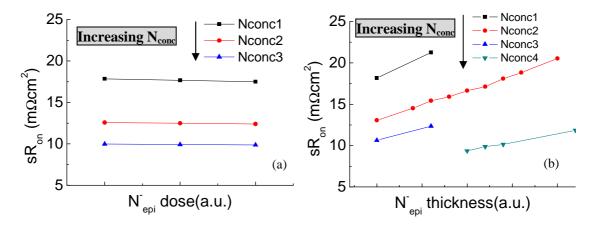

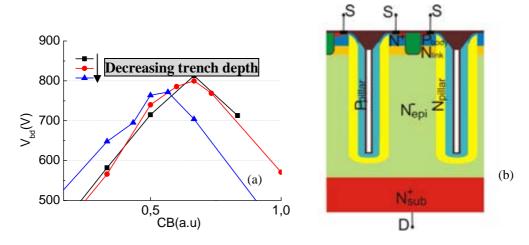

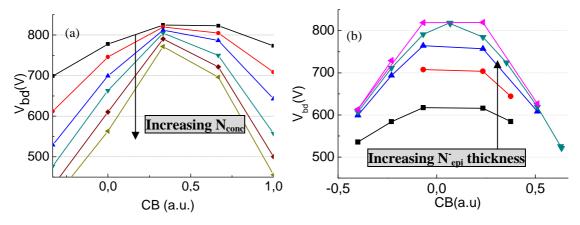

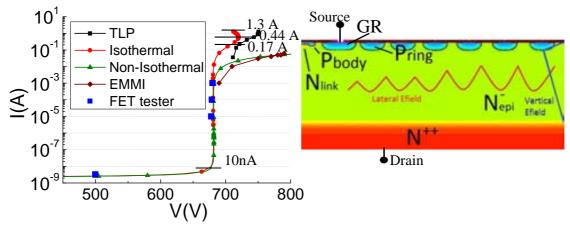

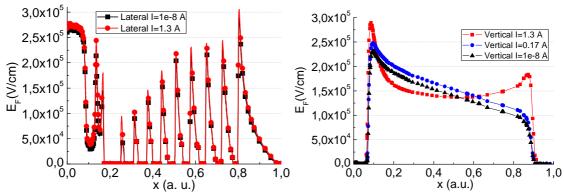

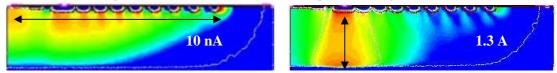

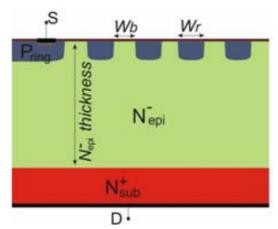

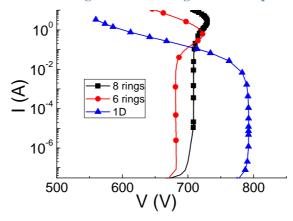

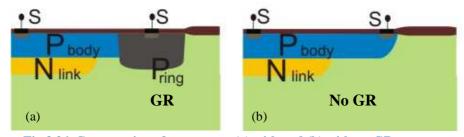

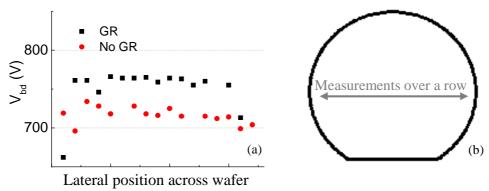

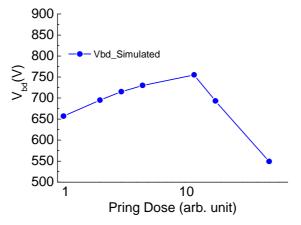

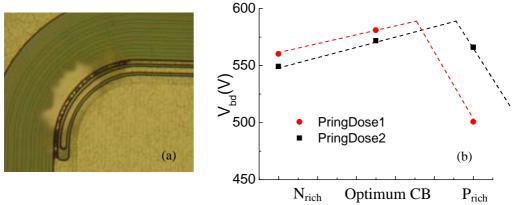

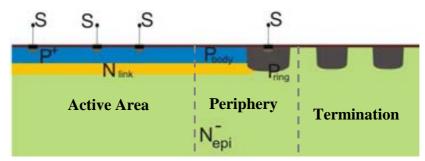

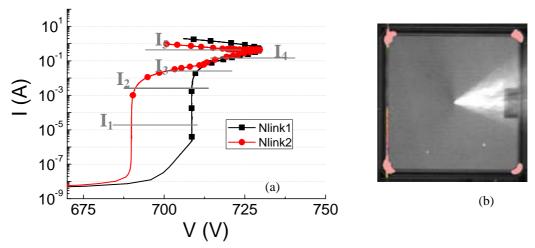

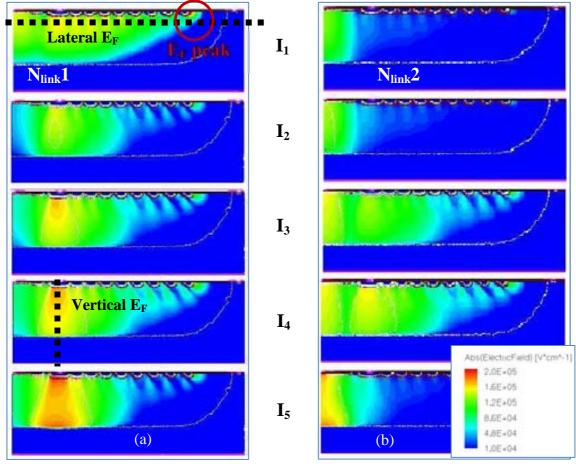

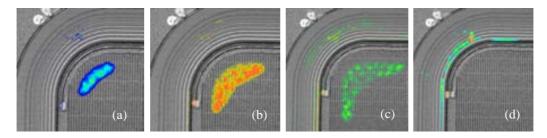

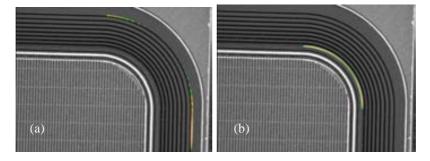

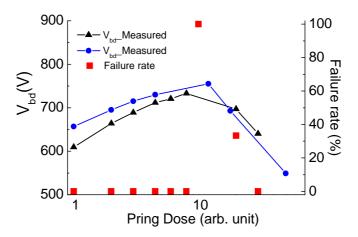

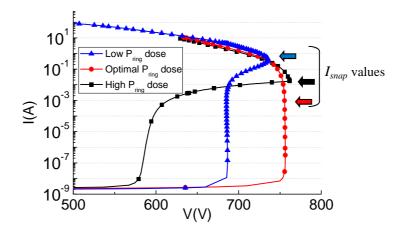

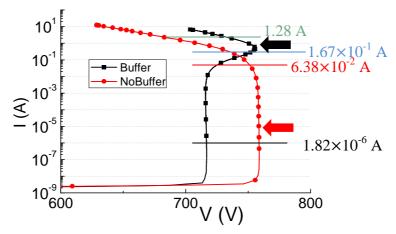

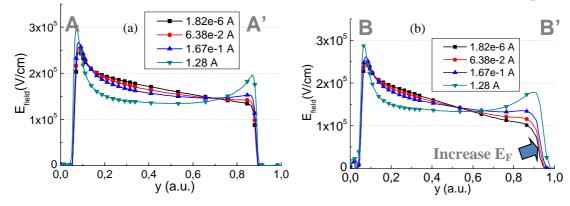

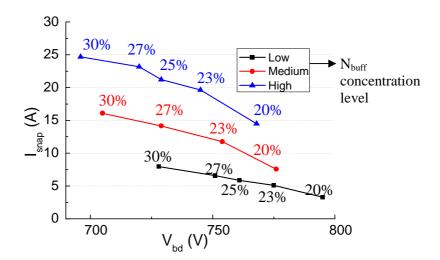

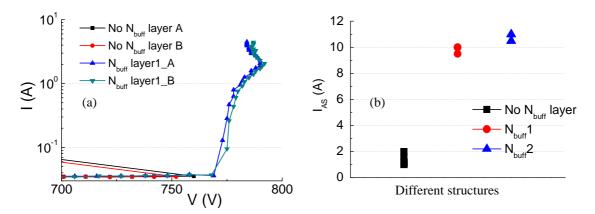

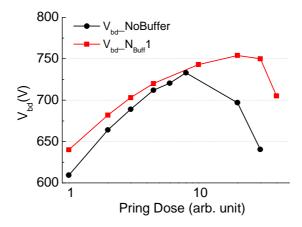

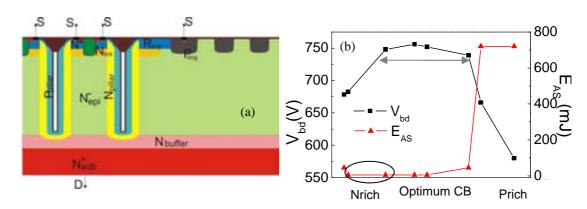

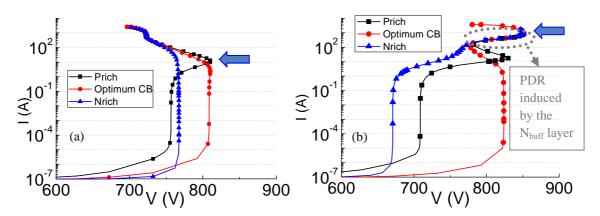

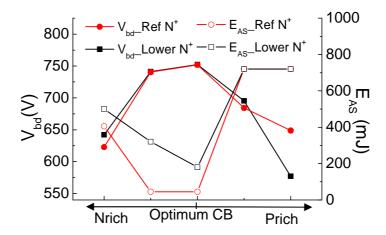

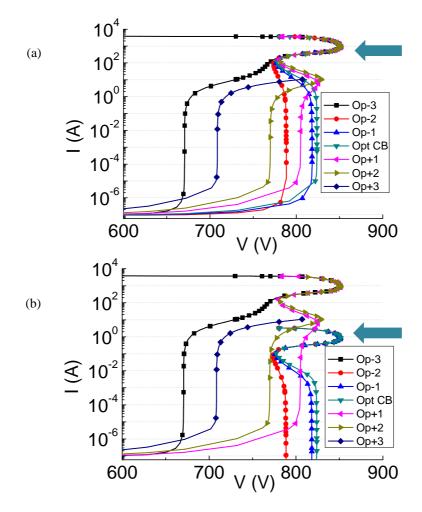

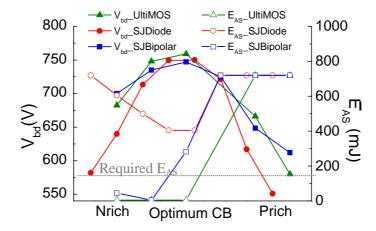

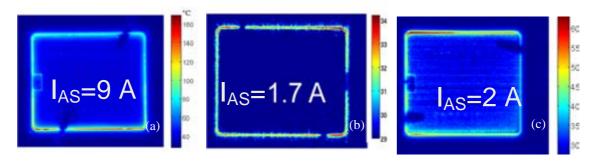

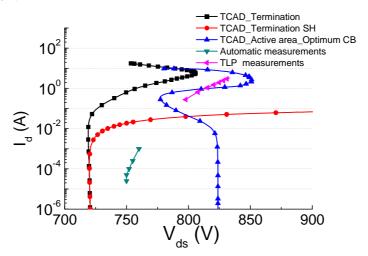

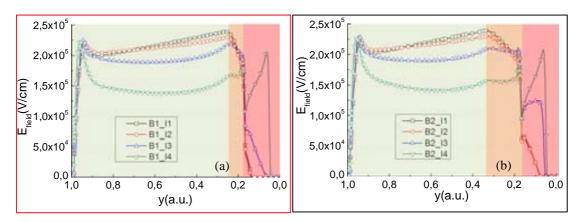

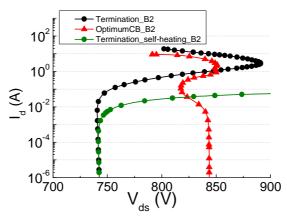

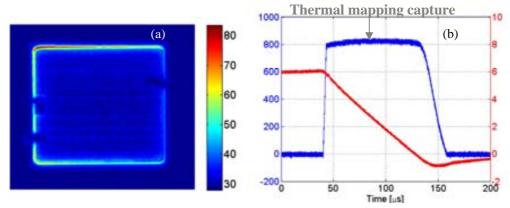

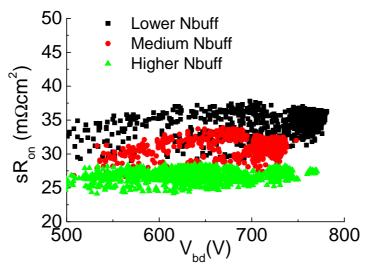

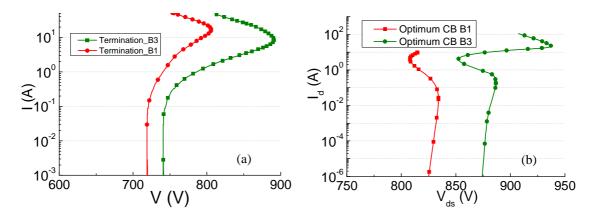

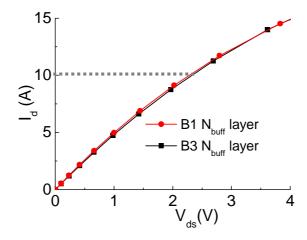

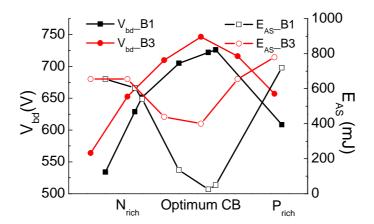

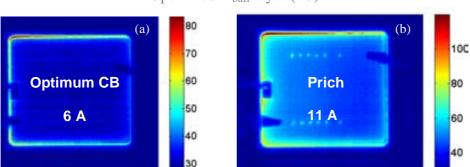

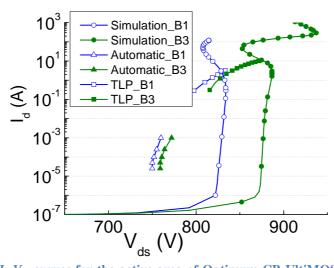

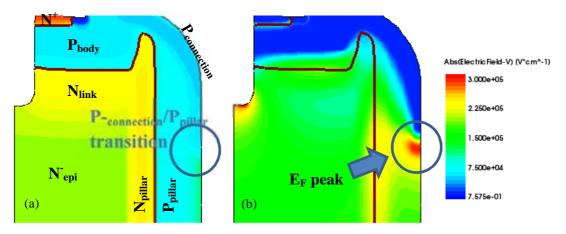

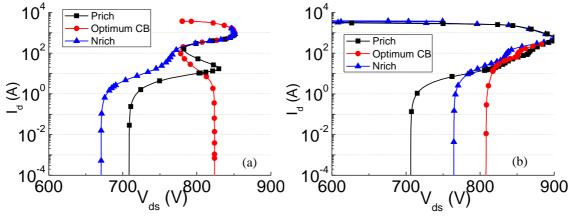

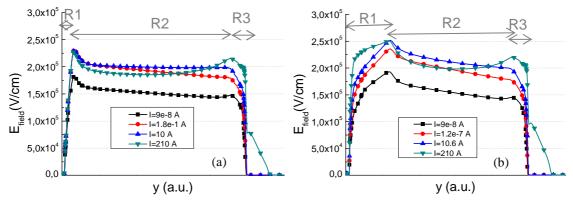

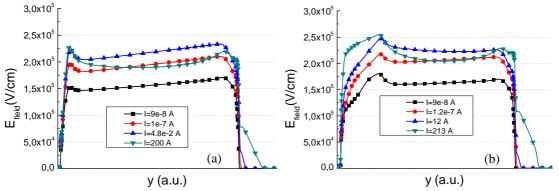

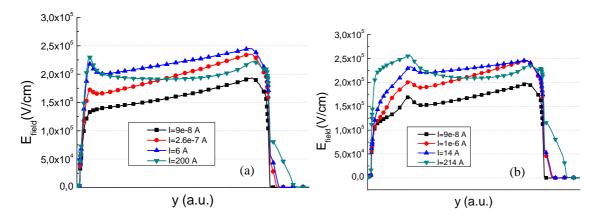

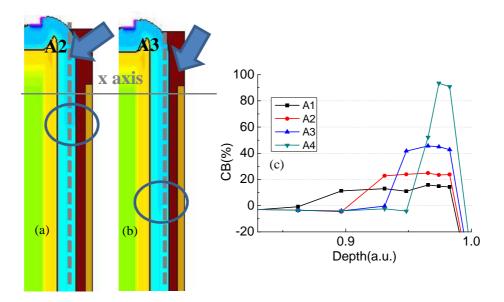

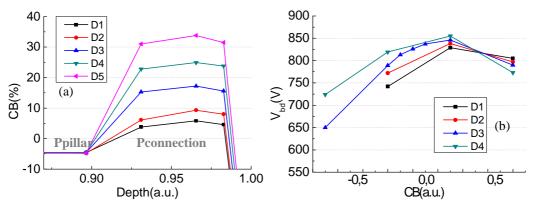

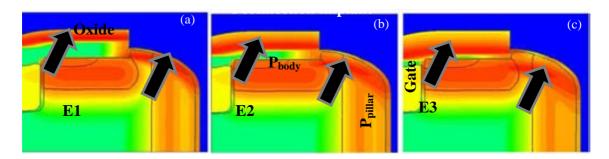

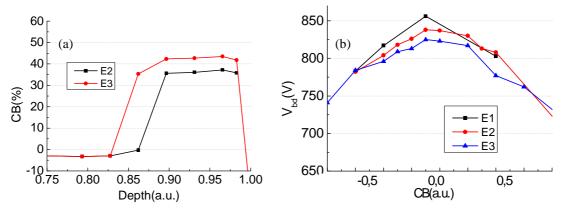

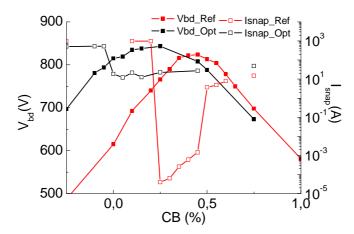

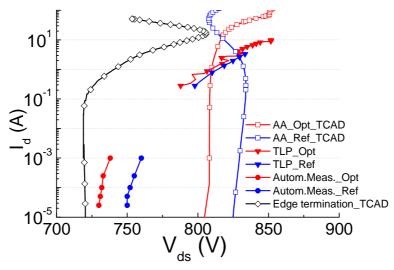

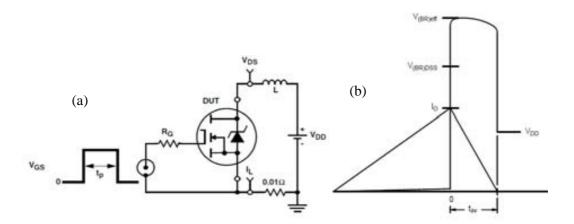

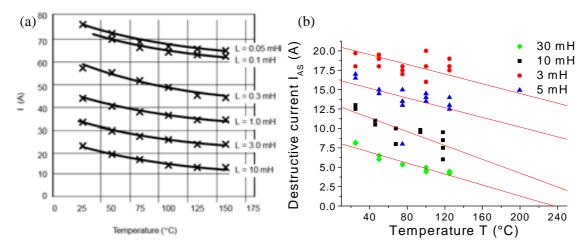

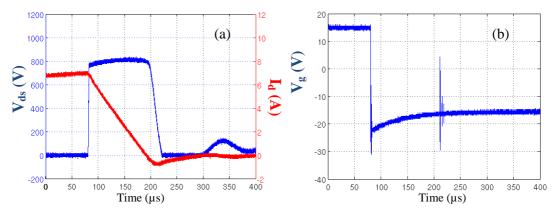

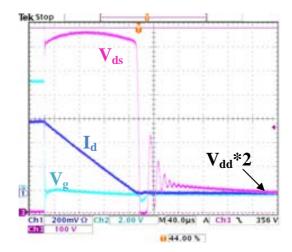

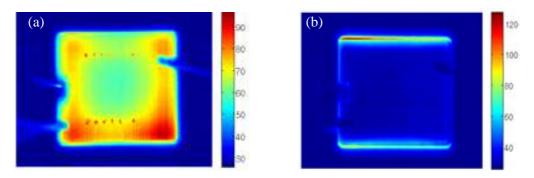

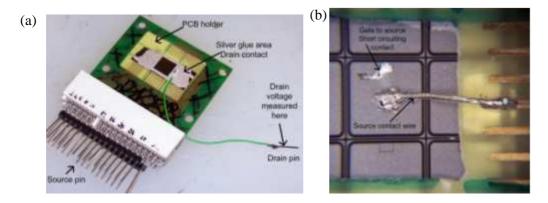

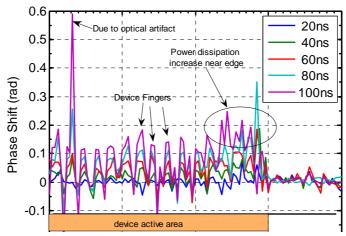

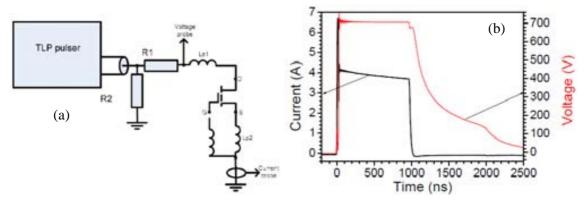

Fig.3.7. Snapshot of potential lines at (a) 100 V, (b) 200 V, (c) 450 V and (d) 570 V for an  $N_{rich}$  device. Correspondence with curves in Fig.3.6-(a).