# CPU ACCOUNTING IN MULTI-THREADED PROCESSORS

## José Carlos Ruiz Luque

(Carlos Luque)

Barcelona, 2014

A thesis submitted in fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Department of Computer Architecture Universitat Politècnica de Catalunya

# CPU ACCOUNTING IN MULTI-THREADED PROCESSORS

### José Carlos Ruiz Luque

(Carlos Luque)

Barcelona, 2014

Thesis director: Francisco J. Cazorla Almeida

Barcelona Supercomputing Center Spanish National Research Council Universitat Politècnica de Catalunya

Thesis co-directors: Miquel Moretó Planas

Universitat Politècnica de Catalunya Barcelona Supercomputing Center

Mateo Valero Cortés

Universitat Politècnica de Catalunya Barcelona Supercomputing Center

A thesis submitted in fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Department of Computer Architecture Universitat Politècnica de Catalunya

A mi hermano *Roberto* y mi madre *Dori*

## **Abstract**

In recent years, multi-threaded processors popularity has raised in industry in order to increase the system aggregated performance and per-application performance, overcoming the limitations imposed by the limited instruction-level parallelism, and by power and thermal constraints.

However, multi-threaded processors introduce complexities when accounting CPU (computation) capacity (CPU accounting), since the CPU capacity accounted to an application not only depends upon the time that the application is scheduled onto a CPU, but also on the amount of hardware resources it receives during that period. And given that in a multi-threaded processor hardware resources are dynamically shared between applications, the CPU capacity accounted to an application in these processors depends upon the workload in which it executes. This is inconvenient because the CPU accounting of the same application with the same input data set may be accounted significantly different depending upon the workload in which it executes. Deploying systems with accurate CPU accounting mechanisms is necessary to increase fairness among running applications. Moreover, it will allow users to be fairly charged on a shared data center, facilitating server consolidation in future systems.

This Thesis analyses the concepts of CPU capacity and CPU accounting for multi-threaded processors. This study demonstrates that current CPU accounting mechanisms are not as accurate as they should be in multi-threaded processors. For this reason, we present two novel CPU accounting mechanisms that improve the accuracy in measuring the CPU capacity for multi-threaded processors with low hardware overhead. We focus our attention on several current multi-threaded processors, including chip multiprocessors and simultaneous multithreading processors. Finally, we analyse the impact of shared resources in multi-threaded processors in operating system CPU scheduler and we propose several schedulers that improve the knowledge of shared hardware resources at the software level.

ii Abstract

# Acknowledgements

It is a great pleasure to find oneself at this stage of research life when the real adventure with science just begins, yet already with a clear taste of it. It is even a greater pleasure to be able to thank to all those that have contributed in some way to the completion of this Thesis.

In the first place, I would like to express my sincere gratitude to my advisor Francisco Javier Cazorla and my co-advisors Miquel Moretó and Mateo Valero for their dedication, encouragement and guidance throughout my Ph.D. adventure. Also, their criticism and encouragement has been a great inspiration for me. I have enjoyed every single discussion with them and I believe it will continue in the future. I will always be thankful for their valuable comments and remarkable patience. It has been an honour to be their Ph.D. student. Thanks to them I have learnt what *research* truly means!

I am also greatly indebted to Enriquez Fernández for his excellent guidance at the early stage of my career. He introduced me to the computer architecture. I would also like to thank my collaborators, Roberto Gioiosa, Alper Buyuktosunoglu and Alexandra Fedorova for great interactions and endless discussions.

Special thanks go to my colleagues from the group 'CAOS' in Barcelona Supercomputing Center for an overwhelming support and a great encouragement at the very last stage of this Thesis.

This work would not have been possible without the financial support of Barcelona Supercomputing Center, Universitat Politècnica de Catalunya, Generalitat de Catalunya and the Spanish Ministry of Education and Science.

Last but not least, I wish to thank my Family for their love, for patience, and for their understanding and gigantic encouragement through difficult moments. If it had not been them, this Thesis would not come into existence. iv Acknowledgements

# **Contents**

| Al | ostrac | et      |                                                               | i    |

|----|--------|---------|---------------------------------------------------------------|------|

| A  | cknov  | vledgem | nents                                                         | iii  |

| In | dex    |         |                                                               | viii |

| 1  | Intr   | oductio | n                                                             | 1    |

|    | 1.1    | Challe  | nges for Accurate CPU Accounting in Multi-Threaded Processors | 2    |

|    | 1.2    | Thesis  | Contributions                                                 | 6    |

|    |        | 1.2.1   | Concept of CPU Capacity and CPU Accounting for Multi-         |      |

|    |        |         | Threaded Processors                                           | 7    |

|    |        | 1.2.2   | CPU Accounting for Multi-Core Processors                      | 8    |

|    |        | 1.2.3   | CPU Accounting for CMP+SMT Processors                         | 8    |

|    |        | 1.2.4   | CPU Capacity-Aware Scheduling in Multi-Core Processors        | 9    |

|    | 1.3    | Thesis  | Structure                                                     | 10   |

| 2  | Plat   | form, T | ools, and Benchmarks                                          | 13   |

|    | 2.1    | Introd  | uction                                                        | 13   |

|    | 2.2    | MPsin   | n Simulator                                                   | 14   |

|    | 2.3    | Bench   | marks                                                         | 16   |

|    |        | 2.3.1   | Simulation Time Reduction                                     | 18   |

|    |        | 2.3.2   | Workload Selection                                            | 22   |

|    | 2.4    | Comp    | arison Metrics                                                | 22   |

| 3  | Con    | cept of | CPU Capacity and CPU Accounting for Multi-Threaded Pro-       |      |

|    | cess   | ors     |                                                               | 25   |

|    | 3.1    | Defini  | ng CPU Capacity                                               | 25   |

|    |        | 3.1.1   | Abstracting CPU Capacity in MT processor                      | 26   |

<u>vi</u> Contents

|   |     | 3.1.2          | CPU Capacity                                | 27 |

|---|-----|----------------|---------------------------------------------|----|

|   |     | 3.1.3          | Fair Share of CPU Capacity                  | 28 |

|   |     |                | 3.1.3.1 Putting It All Together             | 29 |

|   | 3.2 | Defini         | ng CPU Accounting                           | 30 |

|   | 3.3 | Summ           | ary                                         | 31 |

| 4 | CPU | J <b>Accou</b> | nting for Multi-Core Processors             | 33 |

|   | 4.1 | Introdu        | uction                                      | 33 |

|   | 4.2 | Backgr         | round                                       | 34 |

|   |     | 4.2.1          | The Classical Approach                      | 35 |

|   | 4.3 | InterTa        | ask Conflict-Aware Accounting               | 37 |

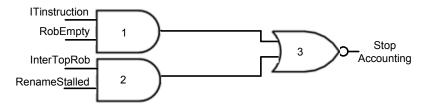

|   |     | 4.3.1          | Hardware Implementation                     | 38 |

|   |     | 4.3.2          | CPU Accounting in ITCA                      | 39 |

|   | 4.4 | Evalua         | ation Results                               | 41 |

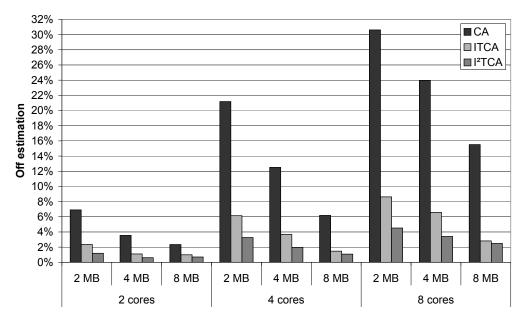

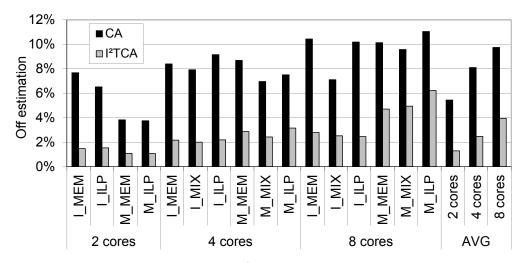

|   |     | 4.4.1          | Accuracy Results                            | 42 |

|   |     | 4.4.2          | Reducing the ATD's Overhead                 | 43 |

|   |     | 4.4.3          | Memory Bandwidth Sensitivity                | 45 |

|   |     | 4.4.4          | ITCA and Cache Partitioning Algorithms      | 45 |

|   | 4.5 | Improv         | ved ITCA Accounting                         | 48 |

|   | 4.6 | Even-S         | Share Accounting                            | 52 |

|   |     | 4.6.1          | Hardware requirements                       | 54 |

|   |     | 4.6.2          | Accuracy Results                            | 56 |

|   | 4.7 | Other (        | Considerations                              | 56 |

|   |     | 4.7.1          | Performance Counters                        | 56 |

|   |     |                | 4.7.1.1 Results                             | 57 |

|   |     | 4.7.2          | Other Proposals Providing Fairness          | 58 |

|   |     | 4.7.3          | Parallel Tasks                              | 59 |

|   | 4.8 | Summ           | ary                                         | 60 |

| 5 | CPU | J <b>Accou</b> | nting for CMP+SMT Processors                | 61 |

|   | 5.1 | Introdu        | uction                                      | 61 |

|   | 5.2 | Backg          | round                                       | 62 |

|   |     | 5.2.1          | Processor Utilization of Resources Register | 62 |

|   |     | 5.2.2          | Processor Utilization Recording Register    | 66 |

|   |     | 5.2.3          | Cycle Accounting Architecture               | 66 |

|   | 5.3 | Micro-         | -Isolation Based Time Accounting            | 68 |

|   |     |                |                                             |    |

Contents

|   |     | 5.3.1   | MIBTA for SMT Processors                           | 69  |

|---|-----|---------|----------------------------------------------------|-----|

|   |     |         | 5.3.1.1 Hardware Implementation                    | 71  |

|   |     | 5.3.2   | MIBTA for CMP processors                           | 72  |

|   |     | 5.3.3   | CPU Accounting in MIBTA                            | 74  |

|   | 5.4 | Evalua  | ation Results                                      | 74  |

|   |     | 5.4.1   | Sensitivity Analysis for Single-Core Architectures | 75  |

|   |     | 5.4.2   | MIBTA Storage Overhead                             | 78  |

|   |     | 5.4.3   | Shared Register File                               | 79  |

|   |     | 5.4.4   | MIBTA on CMP+SMT Architectures                     | 80  |

|   |     | 5.4.5   | Memory Bandwidth Sensitivity                       | 82  |

|   |     | 5.4.6   | Comparison with Other Accounting Mechanisms        | 83  |

|   | 5.5 | Other   | Considerations                                     | 85  |

|   |     | 5.5.1   | System-level Considerations                        | 85  |

|   |     | 5.5.2   | Virtualized Environments                           | 87  |

|   |     | 5.5.3   | Dynamic Voltage and Frequency Scaling              | 87  |

|   |     | 5.5.4   | Parallel Tasks                                     | 87  |

|   |     | 5.5.5   | Scalability                                        | 89  |

|   | 5.6 | Summ    | ary                                                | 89  |

| 6 | CPU | J Capac | city-Aware Scheduling in Multi-Core Processors     | 91  |

|   | 6.1 | Introd  | uction                                             | 91  |

|   | 6.2 | Backg   | round                                              | 93  |

|   |     | 6.2.1   | Completely Fair Scheduler                          | 93  |

|   |     | 6.2.2   | Functioning and Implementation Aspects of CFS      | 94  |

|   | 6.3 | Effecti | ive CPU Capacity Share in CMP Processors           | 96  |

|   | 6.4 | CPU (   | Capacity-Aware CFS                                 | 97  |

|   |     | 6.4.1   | Balanced CPU Capacity Scheduler (BCCS)             | 98  |

|   |     | 6.4.2   | Equal CPU Capacity Scheduler (ECCS)                | 100 |

|   |     | 6.4.3   | Integrating BCCS and ECCS in CFS                   | 101 |

|   | 6.5 | Evalua  | ation Results                                      | 101 |

|   |     | 6.5.1   | Experimental Setup                                 | 102 |

|   |     | 6.5.2   | CPU Capacity-based Schedulers Self-Evaluation      | 104 |

|   |     | 6.5.3   | Time-based vs. CPU Capacity-based Schedulers       | 106 |

|   |     | 6.5.4   | Scalability Analysis to Large Core Counts          | 108 |

|   |     | 0.0.    | Scalability Thatysis to Large Core Counts          |     |

|   |     | 6.5.5   | Case Studies                                       |     |

viii Contents

|    |             |               | 6.5.5.2 Different Priorities                           | 110 |

|----|-------------|---------------|--------------------------------------------------------|-----|

|    |             | 6.5.6         | Discussion                                             | 111 |

|    | 6.6         | Relate        | d Work                                                 | 112 |

|    | 6.7         | Summ          | ary                                                    | 114 |

| 7  | Con         | clusions      | S                                                      | 117 |

|    | 7.1         | Thesis        | Contributions                                          | 118 |

|    |             | 7.1.1         | Concept of CPU Capacity and CPU Accounting for Multi-  |     |

|    |             |               | Threaded Processors                                    | 118 |

|    |             | 7.1.2         | CPU Accounting for Multi-Core Processors               | 118 |

|    |             | 7.1.3         | CPU Accounting for CMP+SMT Processors                  | 119 |

|    |             | 7.1.4         | CPU Capacity-Aware Scheduling in Multi-Core Processors | 119 |

|    | 7.2         | Future        | Work                                                   | 120 |

|    | 7.3         | Public        | ations                                                 | 121 |

|    |             | 7.3.1         | Conferences                                            | 121 |

|    |             | 7.3.2         | Journals                                               | 122 |

|    |             | 7.3.3         | Posters                                                | 122 |

|    |             | 7.3.4         | Video                                                  | 123 |

| Bi | bliog       | raphy         |                                                        | 125 |

| Li | st of l     | Figures       |                                                        | 133 |

| Li | st of [     | <b>Fables</b> |                                                        | 137 |

| A  | Acronyms 13 |               |                                                        | 139 |

# Chapter 1

# Introduction

Over the last 20 years, the performance of Single-Threaded (ST) processors has increased due to two factors: *advances in the integrated circuit technology* and *microarchitectural techniques* such as deeper pipeline, dynamic scheduler, speculative execution through branch predictor, cache hierarchy and non-blocking caches. Advances in the integrated circuit technology have provided both faster and smaller transistors. Smaller transistors increase integration while faster transistors allow increasing clock rates, and hence, processors can run at higher clock rate, in other words, high frequency. Microarchitectural techniques allow exploiting Instruction-Level Parallelism (ILP) inherent in tasks<sup>1</sup>. Although microarchitectural techniques help improving performance, a large portion of this performance comes from advances in integrated circuits. On the whole, processors run instructions very fast due to high frequency and the number of instructions running concurrently is high due to microarchitectural techniques.

Due to power and thermal constraints [20] and the limited amounts of ILP inherent in tasks [66], new techniques have been developed to improve performance with low energy requirements. One such technique is Thread-Level Parallelism (TLP). Current processors implement at least one form of TLP, which allows executing several tasks onto the processor simultaneously.

TLP can be implemented across multiple chips. For instance, Symmetric MultiProcessing (SMP) consists of two or more processors that are connected to shared hardware resources such as main memory. TLP can also be implemented at the chip level. In this level, a wide variety of processors supports TLP. On one extreme of the spectrum, we find Simultaneous Multithreading (SMT) processors [52, 64], in which tasks share most of the processor resources. On the other end of the spectrum,

<sup>&</sup>lt;sup>1</sup>In this Thesis, we use the term task to refer to an application running in a computing system.

Chip MultiProcessors (CMP) [42] or multi-core processors, in which tasks share only some levels of the cache hierarchy and the memory bandwidth. In between, there are other TLP paradigms like Coarse-Grain MultiThreading (CGMT) [2, 62] or Fine-Grain MultiThreading (FGMT) [19, 57]. Each of these designs offers different benefits as they exploit TLP in different ways, which motivates processor vendors to combine different TLP paradigms in their latest processors. Some notorious examples are the Intel core i7 [51] and IBM POWER7 [56], which are CMP+SMT processors, and the ORACLE UltraSPARC T4 [43] that is CMP+FGMT. This trend in integrating different TLP paradigms will keep growing in importance according to the ITRS roadmap for the future years [24]. In this Thesis, we make use of the term Multi-Threaded (MT) processor to refer to a processor implementing any TLP paradigm or combination of TLP paradigms at chip level.

Both SMP systems and MT processors permit to execute several tasks simultaneously. In this way, the utilization of the hardware resources is improved because several tasks can use different parts of hardware resources, and hence, the system throughput is increased.

On the other hand, the communication latency in SMPs is higher than in MT processors because on-chip communications are faster than outside the chips used in SMPs. For instance, if two or more threads of a parallel task want to share data, the communication latency will be lower in a MT processor as data will be cached on-chip (in the cache hierarchy), and not in main memory as in a SMP. The SMP can have a cache hierarchy with a Last level Cache (LLC) shared among processors, but this LLC is outside the chip. Consequently, increased communication latencies are obtained on those systems.

Other benefits of MT processors are the design costs and power efficiency. The design costs are reduced because the design complexity of a MT processor is fairly less than a processor with a larger monolithic core. Due to the described benefits of MT processors, processor vendors prefer this microarchitecture to improve the processor performance with low energy requirements.

#### 1.1 Challenges for Accurate CPU Accounting in Multi-Threaded Processors

An Operating System (OS) is a software application that manages computer hardware resources and provides common services for computer systems. It also acts as an

interface between user and the computer hardware and supplies an environment within which user applications can do useful work [55]. Its major responsibility is to manage and ensure proper operation of the hardware resources. Moreover, an OS provides the user with an abstraction of the hardware resources. The user application perceives this abstraction as if it was using the complete hardware while, in fact, the OS shares hardware resources among the user applications. For example, several tasks demand service from the Central Processing Unit (CPU). Hardware resources can be shared *temporally* and *spatially*. Hardware resources are time shared between users when each task can make use of a resource for a limited amount of time (for example, the exclusive use of a CPU). Orthogonally, hardware resources can be shared spatially when each task makes use of a limited amount of resources, such as cache memory or I/O bandwidth.

In traditional, ST uniprocessor systems, the execution time of a task is influenced by the amount of hardware resources shared with the other running tasks. It is also affected by how long the task runs with other tasks. However, the time accounted to that task is roughly the same regardless of the workload<sup>2</sup> in which it is executed, in other words, regardless of how many tasks are sharing the hardware resources at any given time. We call this principle, the *Principle of Accounting*.

To illustrate this principle of accounting, we use an Unix-like system that differentiates the real execution time and the time a task actually is running onto a CPU. Commands such as time or top provide three values: *real*, *user* and *sys*. *Real* is the elapsed wall clock time between the invocation and termination of the task; *user* is the time spent by the task in the *user mode*; and *sys* is the time spent in the *kernel mode* on behalf of the task. In these systems, *sys+user* time is the execution time accounted to a task.

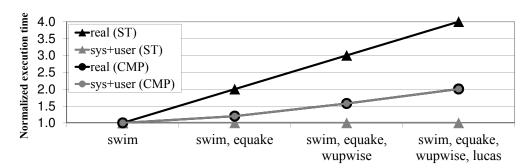

Figure 1.1 shows the total (*real*) and the accounted execution time (*sys+user*) of the 171.*swim* (or simply *swim*) SPEC CPU 2000 benchmark [60] when it runs in different workloads. In this figure, the time results are normalized to the real execution time of *swim* when it runs in isolation<sup>3</sup>, meaning that, once *swim* is scheduled on a CPU it does not share the CPU resources with any other task. For this experiment, we use an Intel Xeon Quad-Core processor at 2.5 GHz (though the general trends drawn from Figure 1 apply to other current MT processor). There are four cores in the chip,

<sup>&</sup>lt;sup>2</sup>In this Thesis, we use the term workload to refer to a set of tasks running onto a processor simultaneously.

<sup>&</sup>lt;sup>3</sup>In this Thesis, we use the term execution in *isolation* to refer to when a task runs alone onto a processor.

Figure 1.1: Total (*real*) and accounted (*sys+user*) time of *swim* in different workloads running on an Intel Xeon Quad-Core CPU

on which we run Linux 2.6.18. We move most of the OS activity to the first core, leaving the other cores as isolated as possible from *OS noise*. When *swim* runs alone in one of the isolated cores, it completes its execution in 117 seconds. However, when *swim* runs together with other tasks in the same core, its real execution time increases up to 4x due to context switches forced by the OS (black triangles in Figure 1.1). Nevertheless, *swim* is accounted roughly the same time (grey triangles), which is the time the task actually uses the CPU. Tasks may suffer some delay because of cache data eviction and the loss of TLB contents caused by a context switch, but this effect is small in this case. Hence, even if total execution time of *swim* increases depending upon the other tasks it is co-scheduled with, the time accounted to *swim* is always the same.

In ST uniprocessor systems, each running task uses 100% of the processor's resources and its progress can be generally measured in terms of the time spent running onto the CPU. We call this CPU accounting mechanism the *Classical Approach*. The classical approach has been proved to work well for ST uniprocessor and SMP systems, as the amount of hardware resources spatially shared is limited.

However, MT processors make more complex to measure CPU utilization because the progress of a task depends upon the activity of the other tasks running at the same time. Current CPU accounting mechanisms may lead to inaccuracy for the time accounted to each task. In order to show this inaccuracy, in a second experiment, we use all the cores in the Intel Xeon Quad-Core processor. We execute *swim* concurrently with other tasks, as shown by the x-axis in Figure 1.1. In this case, *swim* suffers no time sharing and *real* time is roughly the same as *sys+user* because the number of tasks that are running is equal or lower than the number of virtual CPUs (see Figure 3.1) in the system. In Figure 1.1, the grey circles show a variance up of to 2x in the

time *swim* is accounted for depending upon the workload in which it runs. This means that *a task running onto a MT processor may be accounted different CPU utilization depending upon the other tasks running on the same chip at the same time*. From the user point of view this is an undesirable situation, as the same task with the same input data set is accounted differently depending upon the tasks it is co-scheduled with.

In short, the principle of accounting is not guaranteed in MT processors due to the fact that the performance of a task depends on both the time the task runs onto the processor and the amount of resources it receives during that time. The latter is in general not under the control of the user or the OS. To make things worse, there is a non-linear relation between the percentage of resources assigned to a task and the slowdown it suffers with respect to running in isolation.

The inaccuracy measuring per-task CPU utilization may affect several key components of a computing system, such as performance monitoring tools, the CPU scheduler, or billing mechanisms in data centers:

- *Performance tools* generate statistics of various parameters of a task such as CPU utilization and I/O activities in order to know the behaviour of the task in a computing system. For example, in Unix-like systems the command *vm*-stat reports statistics regarding virtual memory, disks, and CPU activity. These tools may not properly account the CPU utilization of task in a MT processor and hence, the tools generate wrong profile of tasks. This is undesirable. For instance, in a queue system, a task may exceed the threshold for the particular queue where it runs because its execution time changes depending upon who are its co-runners.

- In modern time-sharing OSes, the *CPU scheduling algorithm* multiplexes the CPU time for different tasks in the system and maintains fairness between tasks. In this scenario, the task schedulers assume that the time a task is scheduled onto CPU is a good metric in order to measure the CPU utilization of each task in ST uniprocessor system. However, in MT processors, this metric is flawed because each task may make a different progress in different workloads. For this reason, even if the CPU scheduler can balance time among tasks in the system achieving fairness, the scheduling algorithms cannot guarantee that a task progresses according to its software-assigned priority.

- Selection of appropriate co-runners. Task interaction in hardware shared resources may negatively affect tasks, hurting performance and increasing energy

requirements. Per-task CPU accounting can help the OS scheduler or a runtimebased scheduler to decide which tasks must be run and when, thus increasing the total system performance.

• Billing in data centers. Data centers charge users for the use of their resources. The fact that CPU utilization in MT processors is not accurately measured, makes current billing systems unfair when several users are consolidated onto the same processor. Measuring the CPU utilization each task performs, would allow charging each user more fairly. Traditionally, data centers offer services of compute capacity and storage to execution and store of its customers' tasks and data. In order to charge compute capacity to a customer, the data center may utilize the CPU utilization as measurement of the CPU activity. The payment of these services depends upon the utilized resources such as used amount of memory, disk space, I/O and CPUs activity, etc. For example, Amazon Elastic Compute Cloud (Amazon EC2) [3] is a virtual computing environment that leverages Amazon's own infrastructure to provide computing capacity to external users. The user sets up an image with all the required applications, libraries and data, and uploads them to Amazon's facilities. After this preliminary step, the user instructs Amazon EC2 to start executing an instance bound to previously uploaded image. At this point, Amazon starts billing the user for the number of hours the instance executes, for data transfers (network usage) and for disk space usage. In conclusion, having accurate per-task CPU utilization will facilitate server consolidation, allowing an efficient usage of the servers and a fair charging to users.

#### 1.2 Thesis Contributions

This Thesis presents several proposals that effectively track the CPU capacity to account each task running onto MT processors. The contributions are divided into three groups. First, we formally define the CPU capacity and CPU accounting for MT processors. Second, at the hardware level, we propose two novel CPU accounting mechanisms that improve the accuracy in measuring the CPU accounting in MT processors. To start with, we study CPU accounting mechanisms for CMP processors. Next, CPU accounting mechanisms are studied for CMP+SMT processors, where each core supports SMT. Finally, at the software level, we study how the CPU scheduler should be adapted to take advantage of the proposed CPU accounting hardware mechanisms to

1.2. Thesis Contributions 7

increase system fairness. The following sections briefly summarize each one of the contributions.

#### 1.2.1 Concept of CPU Capacity and CPU Accounting for Multi-Threaded Processors

The first problem that is addressed in the Thesis is the definition of *CPU capacity* and *CPU accounting* for MT processors. Although these concepts are clearly defined in ST processors, they are vague in MT processors. For this reason, we provide two definitions of CPU capacity (*resource utilization* and *CPU progress*) and we also introduce the *fair share of CPU capacity* which represents the hardware resources that a task should get access when the task runs alone onto a MT processor. The fair share of CPU capacity can be defined with two different approaches: *full-share* and *even-share*.

In this Thesis, we focus on CPU capacity as CPU progress. The full-share approach assumes that a task running in isolation accesses all processor hardware resources during a given period of time. Consequently, the task execution progress of a task in a MT processor is equivalent to its execution progress when runs in isolation. Meanwhile, the even-share approach assumes that a task accesses even part of the processor resources. In our cases, even part of the processor resources is defined as 1/N of the processor resources, where N is the number of tasks supported by processors. In this way, the task execution progress of a task is equivalent to its execution progress when runs in isolation with an even part of the processor resources.

The *CPU accounting* is the process of measuring the CPU capacity utilized by task in a MT processor. In other words, the CPU accounting measures the CPU capacity of a task would have if the task run alone onto a MT processor. For instance, if a task A executes 5 milliseconds in a MT processor and the CPU accounting measures 4.5 milliseconds, it means that the task would run for 4.5 milliseconds if it is alone on the processor. The task progressed 90 percent of the time, and in the remaining time, the task was stalled due to interferences with other tasks. In contrast, in a ST processor, the task A would have progressed 100 percent of the time as it would run alone in the processor. We name *full-share accounting* when using CPU capacity based on CPU progress and full-share approach and *even-share accounting* when using CPU capacity based on CPU progress and even-share approach.

#### 1.2.2 CPU Accounting for Multi-Core Processors

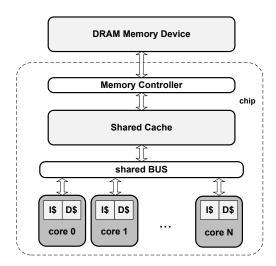

The second problem that we address in this Thesis is how the CPU accounting is obtained in CMP processors. CMP processors consist of simple processor cores and share only some levels of the cache hierarchy and the memory bandwidth (see Figure 2.1). We firstly focus on CMP processors because they have less shared hardware resource among tasks than SMT processors and we can easily identify the sources that generate inaccuracies when measuring CPU capacity in CMP processors with current CPU accounting mechanisms.

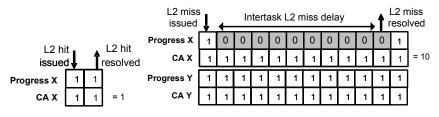

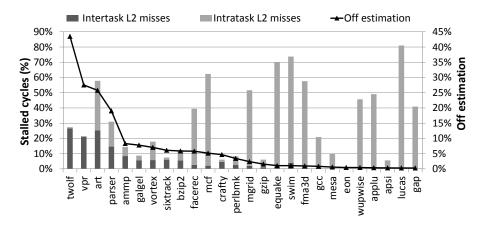

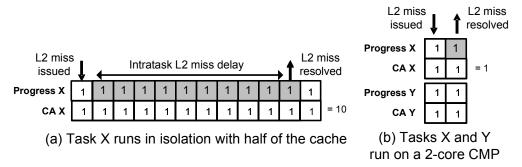

We propose a new CPU accounting mechanism for CMP processors, called *InterTask Conflict-Aware* (ITCA) accounting [33, 34]. The main goal of ITCA is to estimate accurately the CPU accounting to a task by keeping track of the interference in shared hardware resources, mainly in the on-chip shared cache. Moreover, we show that our understanding of the processor architecture in developing ITCA is correct by making a complete design space exploration of the possible combinations of hardware resource status indicator states. This exploration confirms that ITCA provides reasonably accurate results at moderate hardware cost. It also shows that with small changes we can implement an improved ITCA accounting mechanism, denoted I<sup>2</sup>TCA, that further improves the accuracy of ITCA.

In addition, we show that ITCA works well with cache partitioning algorithms and that both *full-share* and *even-share* accounting approaches can be used with our proposed mechanisms.

#### 1.2.3 CPU Accounting for CMP+SMT Processors

The third problem that is addressed in the Thesis is how the CPU capacity is measured in processors combining different TLP paradigms such as CMP+SMT processors. In these processors, more hardware resources are shared than CMP processors, since both on-core and off-core hardware resources are shared among running tasks. It is important to note that, in general, on-core shared resources in the SMT processor are more heavily shared than off-core resources shared among different cores.

ITCA does not adapt correctly to processors with multiple TLP paradigms because it cannot track interferences of shared on-core resources such as register files, issue queues, execution units, the reorder buffer, etc. In addition, the current CPU accounting mechanisms or combination of them either incurs an unaffordable hardware cost to track CPU capacity in processors with multiple TLP paradigms, or leads to inaccuracies in its measurement. Consequently, we introduce *Micro-Isolation Based*

1.2. Thesis Contributions 9

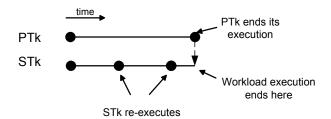

Time Accounting (MIBTA) [35], a new CPU accounting mechanism to compute CPU capacity in CMP+SMT processors. Instead of adding hardware support in *each* shared hardware resource to track tasks' slowdown, MIBTA makes use of a time sampling technique in which tasks run in isolation for short periods of time, with negligible effect on the system throughput and with high accuracy in CPU accounting of tasks. In particular, our CPU accounting mechanism combines the following two mechanisms:

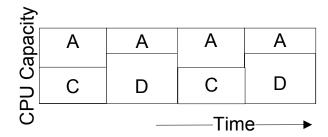

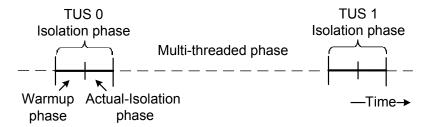

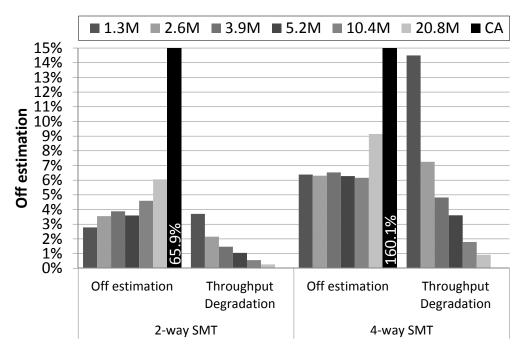

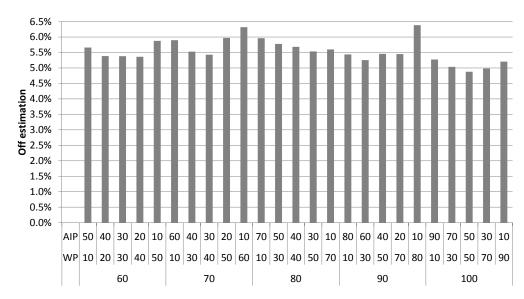

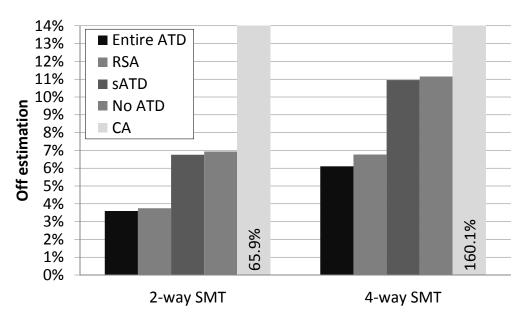

- At SMT level, where tracking how tasks interact in each core resource would introduce significant hardware overhead, our technique periodically runs each task in isolation to measure its CPU capacity. The execution of each task in a workload is divided into two phases that are executed in alternate fashion. In the first, isolation phase, all tasks but one are stopped so that the Instruction Per Cycle (IPC) in isolation of the task is measured. In a second, multi-threaded phase, all tasks run together. The ratio IPC<sub>MT</sub>/IPC<sub>isol</sub> times the total execution time gives the CPU accounting for each task. Since the number of available threads in each SMT processor is restricted (only 2-8 threads), this solution can be implemented with minimal performance degradation.

- At CMP level, our technique makes use of dedicated hardware monitoring support to track the interferences between tasks running in different cores. This hardware support is based on ITCA accounting mechanism [33, 34], which tracks the conflicts in the last level of cache, shared among all different cores, and estimates with high accuracy the CPU accounting in CMP processors. In addition, we propose a new monitoring hardware that significantly reduces the storage overhead of ITCA without affecting its high accuracy. The *Randomized Sampled Auxiliary tag directory*, denoted RSA, combines sampling techniques with randomized algorithms to predict inter-task misses to the entire LLC.

MIBTA combines both proposals to provide tight CPU accounting in CMP+SMT processors with reduced hardware overhead.

#### 1.2.4 CPU Capacity-Aware Scheduling in Multi-Core Processors

Finally, we address how the software can be adapted to the proposed CPU accounting mechanisms in this Thesis with the aim of improving fairness. We focus on the CPU scheduler, which is a key component of the OS and has a significant impact in the system throughput and fairness.

The CPU scheduler focuses on efficiently sharing CPU resources among tasks. In ST uniprocessors, the CPU resources are shared temporarily, in other words, they are time-shared. The CPU scheduler selects the task that should be run next, and for how long this task should use the CPU resources. Time-based schedulers assume that the progress of a task is measured in terms of the time spent onto a CPU. On the other hand, for MT processors, which dynamically share a large amount of processor resources, this assumption is invalid because the task's progress depends upon the activity of other tasks in the same processor as illustrated in Figure 1.1.

In this Thesis, we define a new concept of *effective CPU capacity share* for MT processors, which is aware of the amount of actual CPU capacity used by a task during its execution. Moreover, we propose two novel task schedulers, *Balanced CPU Capacity Scheduler* and *Equal CPU Capacity Scheduler*, that are aware of the CPU capacity received by each running task, and make use of this information to share the CPU more effectively.

#### 1.3 Thesis Structure

This Thesis is structured as follows:

- Chapter 2 focuses on explaining our experimental environment. This includes both the simulation tools and the benchmarks used in this Thesis.

- Chapter 3 defines the concepts of CPU Capacity and CPU Accounting for MT processors, identifying the main sources of inaccuracy in current CPU accounting mechanisms. Also, it introduces the fair share of CPU capacity which represents the hardware resources that a task should get access when the task runs alone onto a MT processor.

- Chapter 4 presents a novel CPU accounting mechanism, ITCA, for CMP processors that is aware of interference in shared hardware resources.

- Chapter 5 describes a novel CPU accounting mechanism for CMP+SMT processors, MIBTA, that extends the concepts of ITCA to SMT processors.

- Chapter 6 describes our concept of effective CPU capacity share for MT processor and proposes two OS CPU scheduling algorithms that are aware of the actual CPU capacity enjoyed by each scheduled task.

1.3. Thesis Structure

• Chapter 7 summarizes the main conclusions of this Thesis, presents our future work, and lists the relevant publications related to this Thesis.

# Chapter 2

# Platform, Tools, and Benchmarks

In this Chapter, we explain the tools and benchmarks we use to evaluate the current CPU accounting mechanisms and the CPU accounting mechanisms proposed in this Thesis.

#### 2.1 Introduction

Researchers in this field propose and test novel techniques that could be included in the actual processor designs. In order to evaluate new techniques, computer architecture researchers usually use both simulation tools and benchmark suites. The simulation tools are used at different levels of detail, form circuit to system level, depending on the particular target system are studied. The benchmarks suites are representative of current and future applications that will be executed by the designed processor.

In this Thesis, several microarchitecture proposals are evaluated in term of both performance and accuracy for different workloads and processor configurations. For this reason, cycle-level microarchitecture simulators are used to model in detail the architecture of the processor and estimate the performance of a benchmark with different configurations. This simulator can be execution driven or trace driven. Execution-driven simulators usually have higher accuracy, but are time-consuming. Trace-driven simulators are less accurate, but are faster. As a result, we decided to choose a trace-driven simulator in order to get a trade-off between speed and accuracy in our experiments.

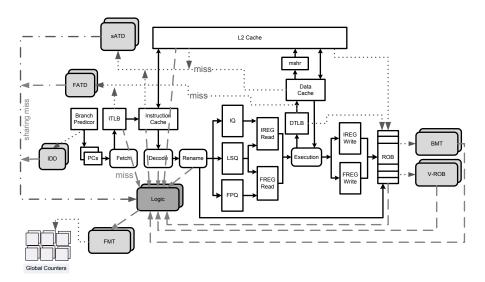

Figure 2.1: Modeled baseline microarchitecture

#### 2.2 MPsim Simulator

To evaluate the performance of the different mechanisms shown in this Thesis and calculate the IPC, we use MPSim [1] (Multiple Purpose Simulator). This simulation tool includes a trace driven SMT simulator derived from SMTsim [64]. MPsim supports CMP processors and SMT processors and simulates the impact of executing along wrong paths on the branch predictor and the Instruction Cache. Also, MPsim models an in-order processor and an out-of-order processor.

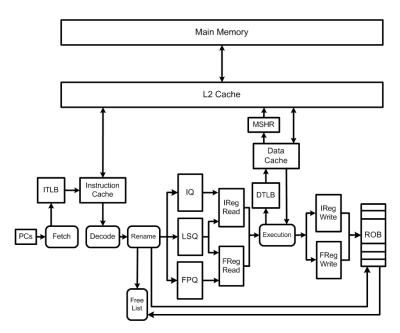

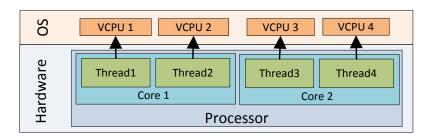

In this Thesis, we model both CMP and CMP+SMT processors. Figure 2.1 shows our baseline CMP microarchitecture which consists of two or more cores which are connected to a shared L1-L2 bus, a shared last level cache, a shared memory controller, and a shared memory bandwidth. In our baseline CMP+SMT, each core supports SMT in which most on-core hardware resources are shared among all tasks running in the core. In both processor microarchitectures, the modelled pipeline each core is out-of-order as shown in Figure 2.2.

The fetch logic fetches instructions from the instruction cache in program order. Next, instructions are decoded and renamed in order to track data dependences. When an instruction is renamed, it is allocated an entry in the issue queues (Integer queue (IQ), Floating point queue (FPQ), and load/store queue (LSQ)) until all its operands are ready. Each instruction also allocates one entry in the Re-Order Buffer (ROB) and a physical register, if required. ROB entries are assigned in program order. When

2.2. MPsim Simulator 15

Figure 2.2: Block diagram of pipeline of a core

an instruction has all its operands ready, it is issued<sup>1</sup>: it reads its operands, executes, writes its results, and finally commits.

The data and the instruction caches are accessed with physical addresses. The data cache uses write back as write hit policy and write allocate as write miss policy. Caches are tagged with the identifier of tasks so that tasks do not share data and/or instructions.

The instruction fetch policy has an important role in SMT core because it determines which of the available tasks can fetch instructions each cycles. In our baseline SMT core, the modelled instruction fetch policy is ICOUNT [30] policy. The configuration of ICOUNT policy is 1.N: up to N instructions can be fetched each cycle from a task.

The main shared resources in our baseline SMT core are the following. (1) The front-end bandwidth, which is assigned to tasks according to the instruction fetch policy. (2) The issue queues are shared between all tasks running on a core. (3) The issue bandwidth: we use is *first in first out* (oldest first) as issue policy. (4) The physical register files (Integer register file (IReg), and Floating point register file (FReg)) are

<sup>&</sup>lt;sup>1</sup> In this Thesis, the term dispatch indicates the action of moving instructions to the issue queues. The term issue is applied to the action of submitting instructions from the issue queues to the backend of the processor.

Figure 2.3: Pipeline stages in a core

common to all tasks. (5) Instruction and Data caches are shared between tasks. (6) Instruction and data Translation Lookaside Buffer (TLB) are also shared and tagged with task identifier, and (7) the ROB is shared among all tasks in a core.

The pipeline of our baseline core is composed of eight stages as shown in Figure 2.3. In our experiments, the decode stage takes up to four cycles and, in this way, the final number of stages in our pipeline is eleven.

#### 2.3 Benchmarks

In the experiments performed during this research, we used the SPEC CPU 2000 benchmark suite [60] to evaluate our proposals in Chapter 4, and the SPEC CPU 2006 benchmark suite [61] in remaining Chapters. These benchmark suites are released by the Standard Performance Evaluation Corp. (SPEC), and are a worldwide standard for measuring and comparing computer performance across different hardware platforms.

SPEC CPU 2000 and SPEC CPU 2006 comprise two suites of benchmarks: SPEC CPU INT 2000 and SPEC CPU INT 2006 for compute-intensive integer performance and SPEC CPU FP 2000 and SPEC CPU FP 2006 for compute-intensive floating point performance. These benchmarks are selected from existing applications, representing high performance computing applications that stress the microarchitecture of the processor. Benchmark source codes run in different platforms so that performance comparisons can be made between different systems.

In our case, we run all benchmarks on an Alpha machine: an AlphaServer DS25 with two processors Alpha 21264C running at 1 GHz with the operating system Tru64 5.1b. Each program is compiled with the -O2 -non\_shared options using DEC Alpha AXP-21264 C/C++ compiler and executed using the reference input set. Fortran programs are compiled with the DIGITAL Fortran 90/Fortran 77 compilers. We succeeded in compiling all the SPEC CPU 2000 benchmark suite and the SPEC CPU 2006 benchmark suite. We only had problems with the integer benchmark 483.xalancbmk from SPEC CPU 2006 since its execution produced a known stack overflow problem.

In Tables 2.1, 2.2, 2.3 and 2.4, we give a short description of each benchmark in

2.3. Benchmarks

Table 2.1: SPEC CPU INT 2000 benchmark description and simulation starting point (in millions of instructions) using the SimPoint methodology [54]

| Benchmark     | Description                        | Input         | Language | Fast    |

|---------------|------------------------------------|---------------|----------|---------|

| Deliciiliai K |                                    |               | Language | forward |

| 164.gzip      | Data compression utility           | graphic       | С        | 68.100  |

| 175.vpr       | FPGA circuit placement and routing | place         | C        | 2.100   |

| 176.gcc       | C compiler                         | 166.i         | C        | 14.000  |

| 181.mcf       | Minimum cost network flow solver   | inp.in        | C        | 43.500  |

| 186.crafty    | Chess program                      | crafty.in     | C        | 74.700  |

| 191.parser    | Natural language processing        | ref.in        | C        | 83.100  |

| 252.eon       | Ray tracing                        | cook          | C++      | 57.600  |

| 253.perlbmk   | Perl                               | splitmail.535 | C        | 45.300  |

| 254.gap       | Computational group theory         | ref.in        | C        | 79.800  |

| 255.vortex    | Object Oriented Database           | lendian1.raw  | C        | 58.200  |

| 256.bzip2     | Data compression utility           | inp.program   | C        | 13.500  |

| 300.twolf     | Place and route simulator          | ref           | C        | 324.300 |

these suites together with the language in which the source codes were written. In the case of integer benchmarks, all the applications are written in C or C++, while in the case of floating point benchmarks, some of them are written in Fortran, C, C++, or a combination of C and Fortran codes. For example, in 435.gromacs the only Fortran code is the inner loops (innerf.f) which typically account for more than 95% of the runtime.

Some benchmarks in the SPEC CPU 2006 suite are executed multiple times with different inputs for the reference test. We execute all benchmarks with the input sets suggested by Phansalkar et al. [46]. In this paper, the authors analyze all the reference input sets of each benchmark to find redundant input sets, and they choose the representative input set of the benchmarks that have multiple input sets. To obtain this representative input set, the authors find the input set that is the closest to the whole benchmark run (with all the input sets). In the SPEC CPU INT 2006 suite, the benchmarks with multiple input sets are 400.perlbench, 401.bzip2, 403.gcc, 445.gobmk, 456.hmmer, 464.h264.ref and 473.astar. In the SPEC CPU FP 2006 suite, they are 416.games and 450.soplex. For each benchmark, we list the most representative input set in Tables 2.5 and 2.6 for the all the integer and floating point benchmarks, respectively.

Table 2.2: SPEC CPU INT 2006 benchmark description

| Benchmark      | Description                                                                                                                                | Language |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 400.perlbench  | Devired from Perl V5.8.7                                                                                                                   | С        |

| 401.bzip2      | Julian Seward's bzip2 version 1.0.3, modified to do most work in memory, rather than doing I/O                                             | С        |

| 403.gcc        | Based on gcc Version 3.2, generates code for Opteron                                                                                       | C        |

| 429.mcf        | Vehicle scheduling. Uses a network simplex algorithm (which is                                                                             | C        |

|                | also used in commercial products) to schedule public transport                                                                             |          |

| 445.gobmk      | Plays the game of Go, a simply described but deeply complex game                                                                           | C        |

| 456.hmmer      | Protein sequence analysis using profile hidden Markov models                                                                               | C        |

| 458.sjeng      | A highly-ranked chess program that also plays several chess variants                                                                       | С        |

| 462.libquantum | Simulates a quantum computer, running Shor's polynomial-time factorization algorithm                                                       | С        |

| 464.h264ref    | A reference implementation of H.264/AVC, encodes a videostream using 2 parameter sets. The H.264/AVC standard is expected to replace MPEG2 | С        |

| 471.omnetpp    | Uses the OMNet++ discrete event simulator to model a large Ethernet campus network                                                         | C++      |

| 473.astar      | Pathfinding library for 2D maps, including the well known A* algorithm                                                                     | C++      |

| 483.xalancbmk  | Transforms XML documents to other docs using a modified Xalan-C++                                                                          | C++      |

#### 2.3.1 Simulation Time Reduction

The simulation of a whole benchmark takes a great amount of time which makes unaffordable to evaluate new techniques. To reduce simulation time, the most common approach is to select a smaller segment of every benchmark that is representative of the whole execution. Selecting these representative samples is an important issue [54, 67]. Random samples appear to be inadequate, while just choosing the beginning of a program could be incorrect due to initialization code. However, we know that a program execution consists of many different phases, where statistics such as cache or branch misses significantly change among them. Thus, representative segment (throughout this work we will call it *trace*) should represent major program phases. As a consequence, the traces allow reducing simulation time to analyse new techniques in this Thesis.

Another advantage of working with traces is that researches must only perform time consuming functional simulation of the whole application once, whereas they perform many times detailed timing simulations of the reduced trace. Therefore, the time of detailed simulation is significantly reduced. 2.3. Benchmarks

Table 2.3: SPEC CPU FP 2000 benchmark description and simulation starting point (in millions of instructions) using the SimPoint methodology [54]

| Benchmark    | Description                     | Input                 | Language  | Fast<br>forward |

|--------------|---------------------------------|-----------------------|-----------|-----------------|

| 168.wupwise  | Quantum chromodynamics          | wupwise.in            | Fortran77 | 263.100         |

| 171.swim     | Shallow water modeling          | swim.in               | Fortran77 | 47.100          |

| 172.mgrid    | Multi-grid solver in            | mgrid.in              | Fortran77 | 187.800         |

| C            | 3D potential field              |                       |           |                 |

| 173.applu    | Parabolic/elliptic              | applu.in              | Fortran77 | 10.200          |

| • •          | partial differential            |                       |           |                 |

|              | equations                       |                       |           |                 |

| 177.mesa     | 3D Graphics library             | frames100 + msea.in   | C         | 294.600         |

| 178.galgel   | Fluid dynamics: analysis        | galgel.in             | Fortran90 | 175.800         |

|              | of oscillatory instability      |                       |           |                 |

| 179.art      | Neural network simulation;      | -scanfile c756hel.in  | C         | 13.200          |

|              | adaptive resonance theory       | -trainfile1 a10.img   |           |                 |

|              |                                 | -trainfile2 hc.img    |           |                 |

|              |                                 | -stride 2 -startx 110 |           |                 |

|              |                                 | -starty 200 -endx 160 |           |                 |

|              |                                 | -endy 240 -objects 10 |           |                 |

| 183.equake   | Finite element simulation;      | inp.in                | C         | 27.000          |

|              | earthquake modeling             |                       |           |                 |

| 187.facerec  | Image processing                | facerec.in            | Fortran90 |                 |

| 188.ammp     | Computer vision:                | ammp.in               | C         | 13.200          |

|              | recognizes faces                |                       |           |                 |

| 189.lucas    | Computational chemistry         | lucas2.in             | Fortran90 | 30.000          |

| 191.fma3d    | Finite element crash simulation | fma3d.in              | Fortran90 | 10.500          |

| 200.sixtrack | Particle accelerator model      | sixtrack.in           | Fortran77 | 173.500         |

| 301.apsi     | Solves problems regarding       | apsi.in               | Fortran77 | 192.600         |

|              | temperature, wind, velocity     |                       |           |                 |

|              | and distribution of pollutants  |                       |           |                 |

This idea drives the *SimPoint* methodology [54]. Sherwood et al. [54] explain how to detect a program's phases by using the Basic Block Vector (BBV) which counts how many times each basic block appears. Two phases are considered the same if Mannheim's distance between their BBVs is small. At the beginning, the execution of the program is split into a set of *intervals* of fixed size (10 million instructions). Using clustering algorithms, such as *random linear projection* or *k-means*, the samples are joined. The first algorithm is used to reduce the dimension of the BBV and, in that way, accelerate the k-means algorithm. This last algorithm is run for values of k between 1 and M (M is the maximum number of phases to use) and the intervals are grouped into phases. Using the Bayesian Information Criterion (BIC), which measures the goodness of fit of a clustering within a dataset, the smallest value of k with

Table 2.4: SPEC CPU FP 2006 benchmark description

| Benchmark     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Language   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 410.bwaves    | Computes 3D transonic transient laminar viscous flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fortran    |

| 416.gamess    | Implements a wide range of quantum chemical computations. Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|               | case does self-consistent field calculations using several methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| 433.milc      | A gauge filed program: lattice gauge theory with dynamical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C          |

|               | quarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 434.zeusmp    | a computational fluid dynamics code developed at NCSA for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fortran    |

|               | simulation of astrophysical phenomena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

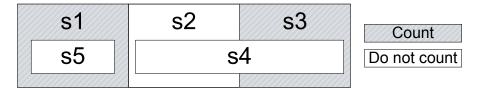

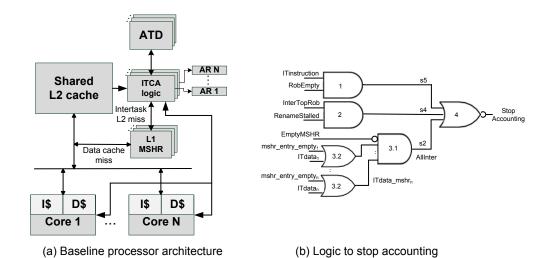

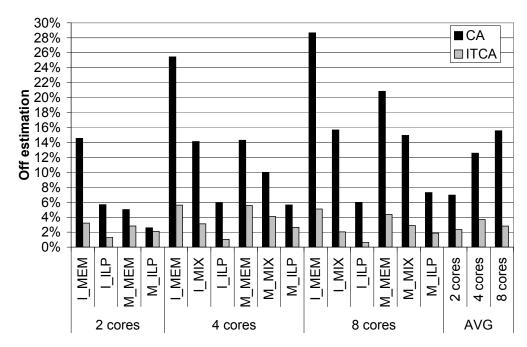

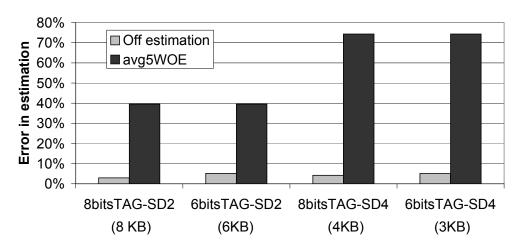

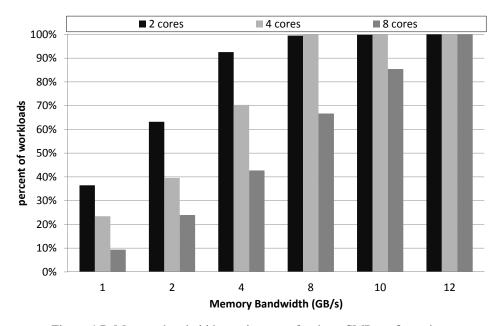

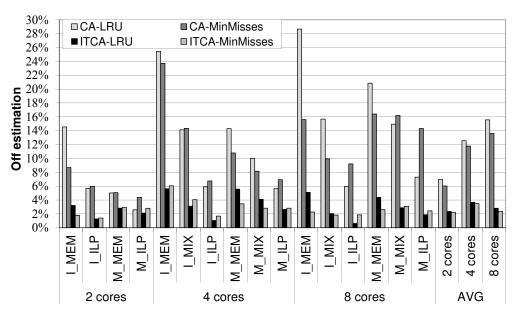

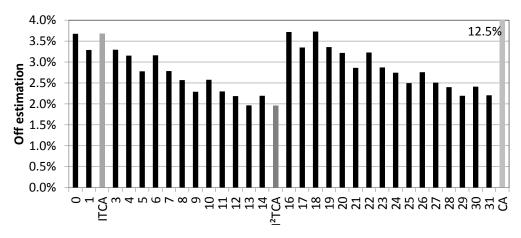

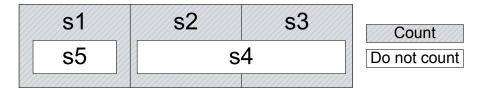

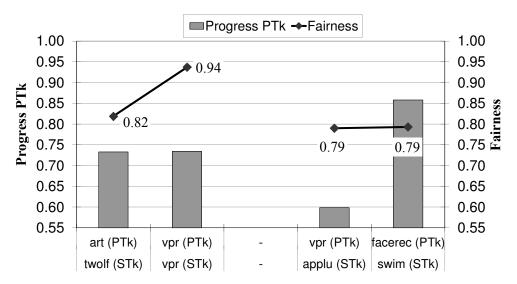

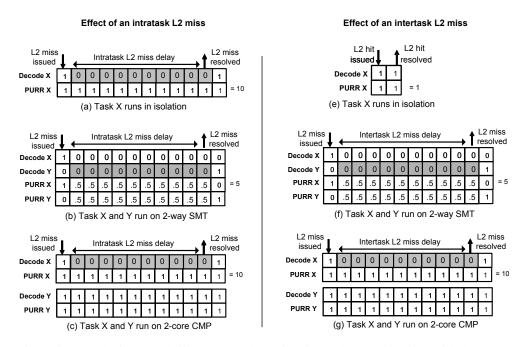

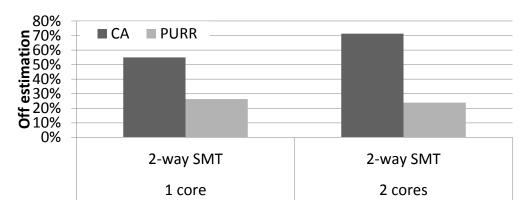

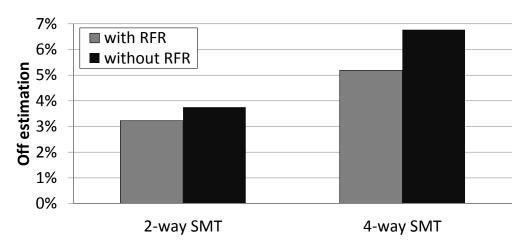

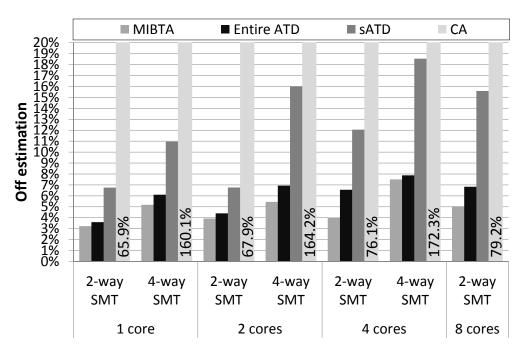

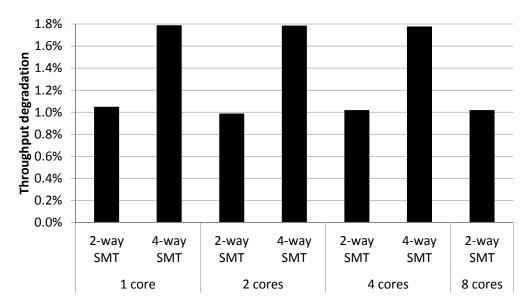

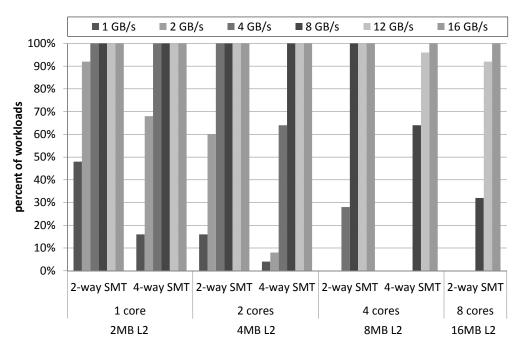

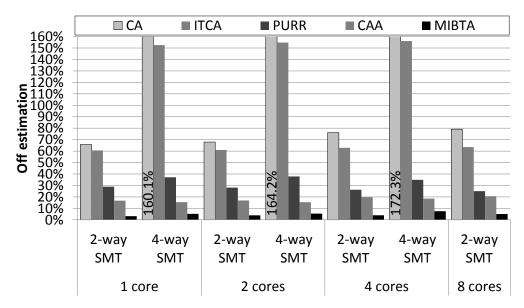

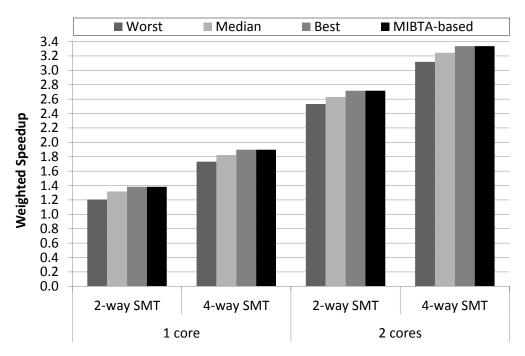

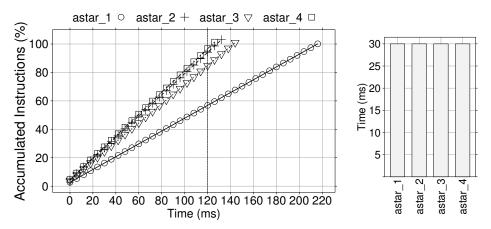

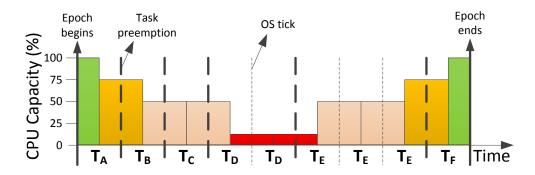

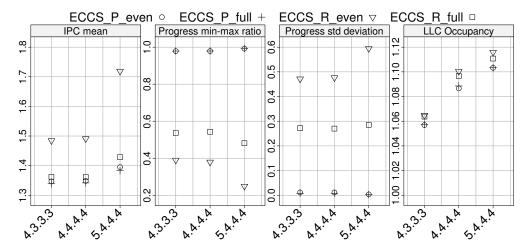

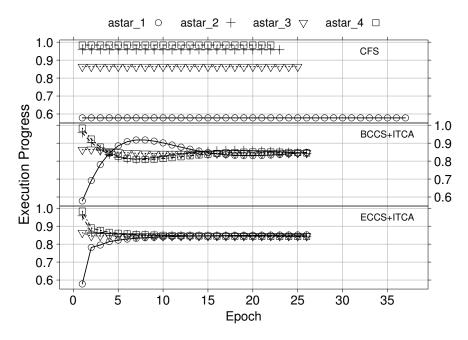

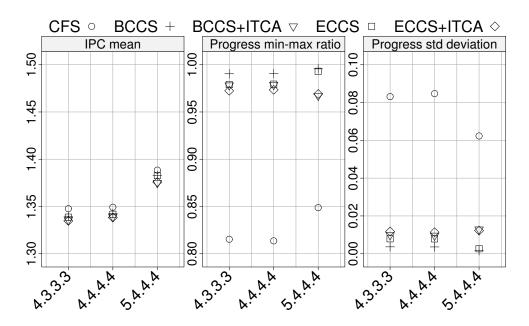

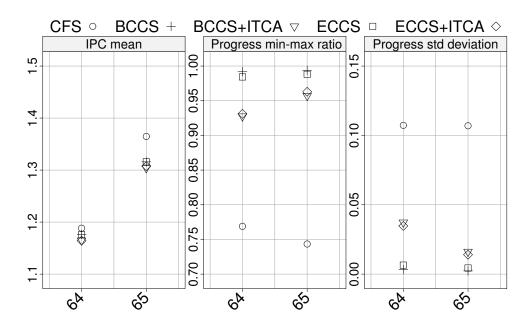

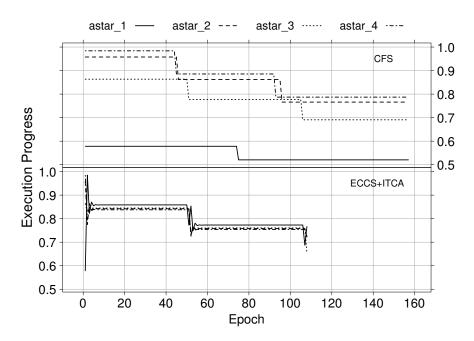

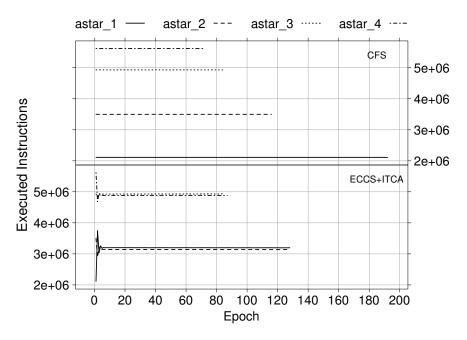

| 435.gromacs   | Molecular dynamics: simulate Newtonian equations of motion for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C, Fortran |