# Offloading Techniques to Improve Performance on MPI Applications in NoC-Based MPSoCs

| Ph.D. | Thesis | Dissert | tation |  |

|-------|--------|---------|--------|--|

|       |        |         |        |  |

|       |        |         |        |  |

|       |        |         |        |  |

Autor: Director:

Eduard Fernandez Alonso Jordi Carrabina i Bordoll

**Co-Director:**

Jaume Joven Murillo

Universitat Autònoma de Barcelona Abril 2014

| I certify that I have read this dissertation and |

|--------------------------------------------------|

| that, in my opinion, it is fully adequate in     |

| scope and quality as a dissertation for the      |

| degree of Doctor of Philosophy.                  |

|                                                  |

|                                                  |

|                                                  |

|                                                  |

| Dr. Jordi Carrabina I Bordoll                    |

|                                                  |

|                                                  |

Dr. Jaume Joven I Murillo

This work was carried out at Universitat Autònoma de Barcelona, and Recore Systems, Enschede, The Netherlands.

# **ABSTRACT**

Future embedded System-on-Chip (SoC) will probably be made up of tens or hundreds of heterogeneous Intellectual Properties (IP) cores, which will execute one parallel application or even several applications running in parallel. These systems could be possible due to the constant evolution in technology that follows the Moore's law, which will lead us to integrate more transistors on a single dice, or the same number of transistors in a smaller dice. In embedded MPSoC systems, NoCs can provide a flexible communication infrastructure, in which several components such as microprocessor cores, MCU, DSP, GPU, memories and other IP components can be interconnected.

In this thesis, firstly, we present a complete development process created for developing MPSoCs on reconfigurable clusters by complementing the current SoC development process with additional steps to support parallel programming and software optimization. This work explains systematically problems and solutions to achieve a FPGA-based MPSoC following our systematic flow and offering tools and techniques to develop parallel applications for such systems.

Additionally, we show several programming models for embedded MPSoCs and propose the adoption of MPI for such systems and show some implementations created in this thesis over shared and distributed memory architectures.

Finally, the focus will be set on the overhead produced by MPI library and on trying to find solutions to minimize this overhead and then be able to accelerate the execution of the application, offloading some parts of the software stack to the Network Interface Controller.

# **RESUM**

Probablement, el sistema-en-xip encastat futur estarà compost per desenes o centenars de nuclis de Propietat Intel·lectual heterogenis que executaran una aplicació paral·lela o fins i tot diverses aplicacions que funcionin en paral·lel. Aquests sistemes seran possible gràcies a l'evolució constant de la tecnologia que segueix la llei de Moore, que ens durà a integrar més transistors en un únic dau, o el mateix nombre de transistors en un dau més petit. En els sistemes MPSoC encastats, les xarxes intenrades (NoC) poden proporcionar una infraestructura de comunicació flexible, en què diversos components, com ara els nuclis microprocessadors, MCU, DSP, GPU, memòries i altres components IP, poden estar interconnectats.

En primer lloc, en aquesta tesi presentem un procés de desenvolupament complet creat per desenvolupar MPSoC en clústers reconfigurables tot complementant el procés de desenvolupament SoC actual amb passos addicionals per admetre la programació paral·lela i l'optimització del software. Aquest treball explica de manera sistemàtica els problemes i les solucions per aconseguir un MPSoC basat en FPGA seguint el nostre flux sistemàtic, i s'ofereixen eines i tècniques per desenvolupar aplicacions paral·leles per a aquests sistemes.

D'altra banda, descrivim diversos models de programació per a MPSoC encastats i proposem adoptar MPI per a aquests sistemes, i mostrem algunes implementacions creades en aquesta tesi amb arquitectures de memòria compartida i distribuïda. Finalment, ens centrem en la sobrecarrega de temps que produeix la llibreria MPI i intentarem trobar solucions per tal de minimitzar aquesta sobrecàrrega i, per tant, poder accelerar l'execució de l'aplicació, descarregant algunes parts del software stack al controlador d'interficie de la xarxa.

Time, what is time?

Time, so mortal concept, so human concept, so engineer concept. Without a clock the designer is lost, but the human is happy.

Time is life. When the clock strikes, a bit of your life moves away. Make it worth! Have a plan! Be one of the final five!

Some Peter Pan said once: "Life is a map, but it is quite confusing" Enjoy it then! Do not worry about the compass! Just be sure to do what you love to do and to be with who you want to be! ...And ignore those who want to make you waste your time.

Research.

# **ACKNOWLEDGEMENTS**

I do not want to end the work without thanking all the people who had a certain impact on the evolution of the thesis or my evolution while doing the thesis. I want to thank all of them, even if this impact was a totally fantastic idea or advise, or a complete deception that was useful for nothing and absolutely avoidable.

However, first of all, I want to thank my thesis directors. Jaume Joven, who already guided me when I was doing the final computer science degree's project, and Jordi Carrabina, who is at the same time my boss with who I have been working for so long.

I want to thank so many people from CAIAC/Cephis group... that it is impossible to mention them all in these lines. However, ALL of them deserve the opportunity to walk the same path that I walked to obtain their own PhD as I had.

I want to specially thank my lab mates. First of all, David Castells, from who I've learned plenty of things. I really appreciate that. And Albert Saa, who I share the love for board games with.

Some other lab mates are no more with us (we like to say that they are living a better life now), but I want to thank them, specially Chak Ma... man, you still have my umbrella!

Although we are not at the same lab, I want to thank deeply Eloi Ramon and Carme Martinez for sharing knowledge, articles, breakfast, lunch time, dinner, funny moments... and really sad moments. Thank you.

I want to thank also my Dutch friends. Gerard for being so kind and let me work in his company; Kim for his guide while I was working in The Netherlands and for appreciating the "art" created with the Xentiums; Simon-Thais for taking care of me when I had some "minor" health problems (I must hug you, man!); Inès for being absolutely lovely!, Lois for being always smiling and sharing with us the nice adventure of living at Enschede, and Jordy, John, Alejandro, Sébastien,... and the rest of the crew.

I cannot forget Jarkko. Thank you for helping us to feel like in our own country, for your attention, for being always in a good mood, for your friendship. Moltes gràcies per tot. Aquest missatge és especial per a tu: "setze jutges d'un jutjat mengen fetge d'un penjat".

I leave for the end my family and friends. I want to thank my parents, who gave me everything that made possible this PhD. I want to thank my little sister for being just like she is... thank you! I'm always learning from you. I'm so proud of you. I want to thank specially my cousin Sergi for SO many happy moments we have lived together... and I hope we'll share many more.

I want to thank my friends, Albert, Cris, Adam (I cannot forget him...his parents will kill me), Alex, the D&D group (Miki, Xavi, Fer, Iza, Pepo), the Vampire group (Montse, Laia, Jorge, Sergi, Mac, Xavi, Pepo again),... the list is too extensive.

Finally, I leave for the end my more deep-rooted thanks to my little family, Laia and Curial. Thank you for everything. YOU are my time, YOU are my passion, YOU are my life, I definitively could not have made it without you. I love you both.

# **TABLE OF CONTENTS**

| ABSTRACT                                                        | 5  |

|-----------------------------------------------------------------|----|

| RESUM                                                           | 6  |

| ACKNOWLEDGEMENTS                                                | 8  |

| TABLE OF CONTENTS                                               | 11 |

| LIST OF FIGURES                                                 | 14 |

| LIST OF TABLES                                                  | 18 |

| GLOSSARY                                                        | 19 |

| 1. Introduction                                                 |    |

| 1.1. Part 1– From computation to communication                  | 25 |

| 1.2. Part 2– Objective of this thesis                           | 33 |

| 2. MPSoCs: theoretical background                               | 36 |

| 2.1. Overview                                                   | 36 |

| 2.2. Parallelism                                                | 36 |

| 2.2.1. Characteristics                                          | 39 |

| 2.2.2. Laws                                                     | 41 |

| 2.2.3. Hardware Solutions                                       | 44 |

| 2.2.4. Theory of Architectures                                  | 47 |

| 2.2.5. Software Solutions / Levels of Parallelism               | 51 |

| 2.3. Theory of interconnection architectures                    | 52 |

| 2.3.1. NoC Components                                           | 54 |

| 2.3.2. Switching Method                                         | 56 |

| 2.3.3. Topology                                                 | 57 |

| 2.4. Parallel Programming Models                                | 58 |

| 2.4.1. Traditional Parallel Programming Models                  | 59 |

| 2.4.2. Programming Models for NoC-Based Systems                 | 60 |

| 2.4.3. Shared-Memory Programming Models for NoC-Based Systems   | 60 |

| 2.4.4. Message Passing Programming Models for NoC-Based Systems | 61 |

| 2.4.5. Other Parallel Programming Models Implementations  | 62  |

|-----------------------------------------------------------|-----|

| 3. Simulation Environment and MPSoC system implementation | 63  |

| 3.1. NoCMaker                                             | 63  |

| 3.2. MPSoC System                                         | 66  |

| 3.2.1. Related work                                       | 68  |

| 3.2.2. MPSoC System Example                               | 73  |

| 3.2.3. Building Blocks                                    | 73  |

| 3.2.3.1. Soft-Core Processor                              | 73  |

| 3.2.3.2. Floating Point Unit                              | 74  |

| 3.2.3.3. Network-on-Chip                                  | 74  |

| 3.2.4. Synthesis Results                                  | 77  |

| 3.2.5. Scalability Test                                   | 79  |

| 3.3. Conclusions                                          | 81  |

| 4. MPI Implementations                                    | 83  |

| 4.1. Overview                                             | 83  |

| 4.2. Shared Memory                                        | 88  |

| 4.2.1. STHORM                                             | 90  |

| 4.2.2. Recore System                                      | 97  |

| 4.2.3. Communication Mechanism                            | 100 |

| 4.3. Distributed memory                                   | 105 |

| 4.4. Conclusions                                          | 107 |

| 5. NoCS                                                   | 108 |

| 5.1. Delivery Protocol                                    | 108 |

| 5.1.1. Offloading Delivery Protocol                       | 111 |

| 5.1.2. Implementation and Results                         | 114 |

| 5.1.3. Summary                                            | 116 |

| 5.2. Bus Master                                           | 117 |

| 5.2.1. Implementation and Results                         | 123 |

| 5.2.1.1. Registers Bank             | 125 |

|-------------------------------------|-----|

| 5.2.1.2. System Bus Interface       | 127 |

| 5.2.1.3. Inner-NoC-router interface | 129 |

| 5.2.1.4. Results                    | 129 |

| 5.2.2. Summary                      | 131 |

| 5.3. Esyncop                        | 132 |

| 5.3.1. Implementation and Results   | 134 |

| 5.3.2. Summary                      | 139 |

| 6. Conclusions                      | 140 |

| 6.1. Open Research                  | 144 |

| REFERENCES                          | 147 |

| AUTHOR'S RELEVANT PUBLICATIONS      | 151 |

| CURRICULUM VITAE                    | 153 |

# **LIST OF FIGURES**

| Figure 1 Number of devices versus time. [11]                                                                                                                                                                       | . 23 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2 Hardware and software design gaps versus time . [11]                                                                                                                                                      | . 32 |

| Figure 3 Full methodology flow                                                                                                                                                                                     | . 34 |

| Figure 4 Thesis contribution graphical overview.                                                                                                                                                                   | . 35 |

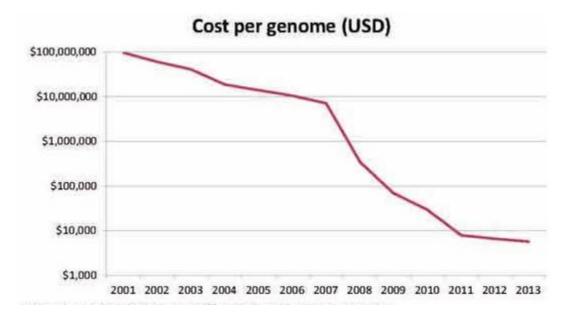

| Figure 5 Declining cost of human genome sequencing                                                                                                                                                                 | . 38 |

| Figure 6 Speedup on Amdah's law.                                                                                                                                                                                   | . 42 |

| Figure 7 Speedup on Gustafson's law.                                                                                                                                                                               | . 44 |

| Figure 8 Five stages deep pipeline example [93].                                                                                                                                                                   | . 45 |

| Figure 9 Breakdown of uses of supercomputer systems.                                                                                                                                                               | . 47 |

| Figure 10 Left) Homogeneous NORMA. Middle) Heterogeneous NORMA. Right) COMA.                                                                                                                                       |      |

| Figure 11 Interconnection systems a) Bus-based system approach b) Crossbar-based system approach.                                                                                                                  |      |

| Figure 12 IEEE Xplorer hits for different "network-on-chip" searches                                                                                                                                               | . 54 |

| Figure 13 NoC representation.                                                                                                                                                                                      | . 55 |

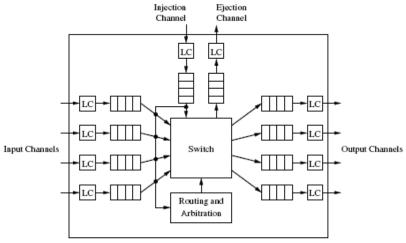

| Figure 14 Generic Router block diagram from DUATO[91] (LC = Link Controller)                                                                                                                                       | . 56 |

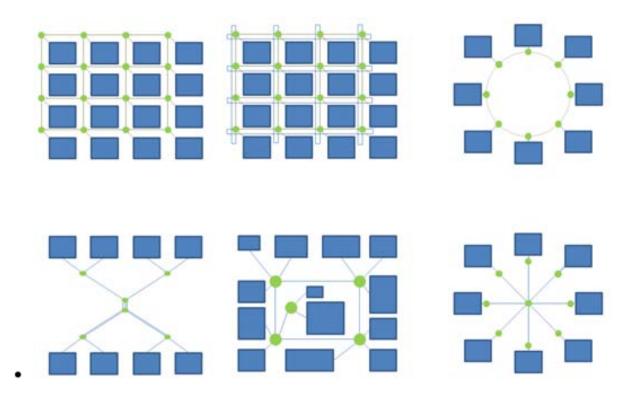

| <b>Figure 15</b> Some basic network topologies. a) Mesh (up-left), b) Torus (up-middle), Ring (up-right), d) Fat-tree (down-left), e) Custom (down-middle), and f) Star (down-right). All links are bidirectional. | 1-   |

| Figure 16 XML example of a NDSP                                                                                                                                                                                    | . 65 |

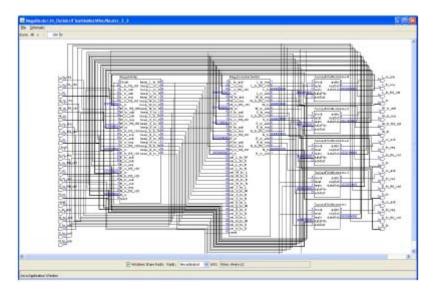

| Figure 17 RTL view from JHDL schematic view of a router                                                                                                                                                            | . 65 |

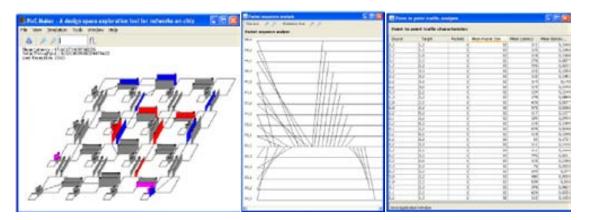

| Figure 18 Visualisation of traffic loaded on links during interactive simulation                                                                                                                                   | . 66 |

| Figure 19 Time diagram of messages.                                                                                                                                                                                | . 66 |

| Figure 20 Point to point traffic analysis example.                                                                                                                                                                 | . 66 |

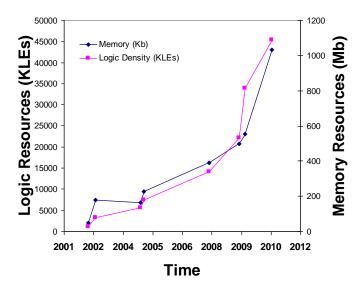

| Figure 21 Evolution of the capacity in logic and memory resources in FPGA devices the Altera Stratix family.                                                                                                       |      |

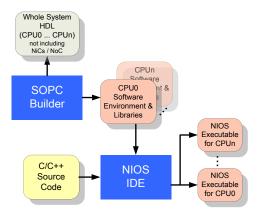

| Figure 22 Full methodology flow.                                                                                                                                                                 | 72    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>Figure 23 Left</b> ) MPSoC based on the 4x4 2-D Mesh NoC. <b>Right</b> ) Master & Slave node architecture                                                                                     |       |

| Figure 24 Left) Block diagram of the Network Interface. Right) Block diagram of Router                                                                                                           |       |

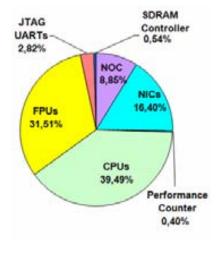

| Figure 25 Left) Resource utilization breakdown. Right) Synthesis Results                                                                                                                         | 78    |

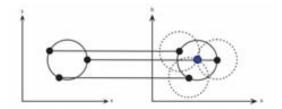

| <b>Figure 26</b> Hough Transform to detect circles where each point in geometric space (generates a circle in parameter space (right).                                                           |       |

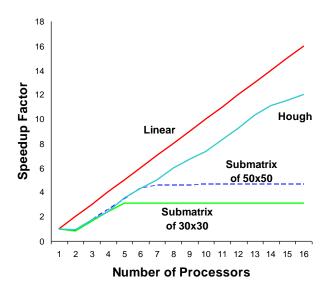

| Figure 27 Scalability                                                                                                                                                                            | 81    |

| Figure 28 Development process                                                                                                                                                                    | 84    |

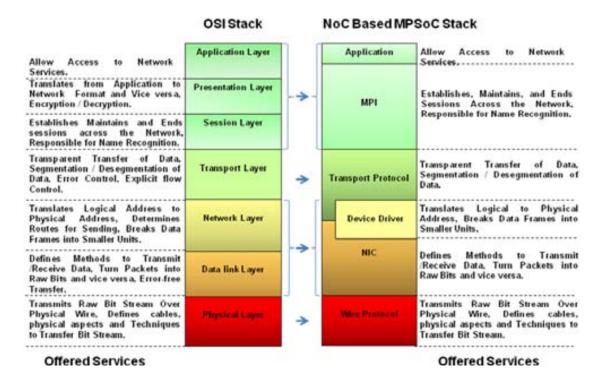

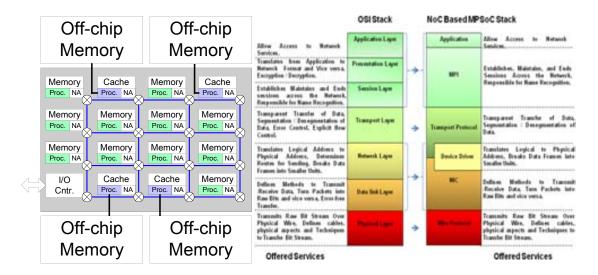

| Figure 29 Traditional OSI stack vs. MPSoC software stack                                                                                                                                         | 86    |

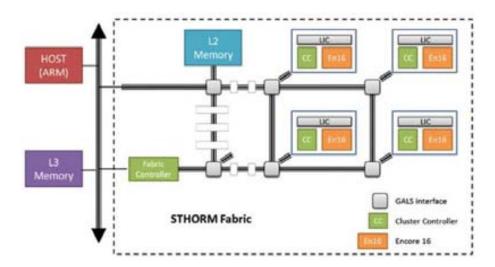

| Figure 30 STHORM architecture template [95][96]                                                                                                                                                  | 91    |

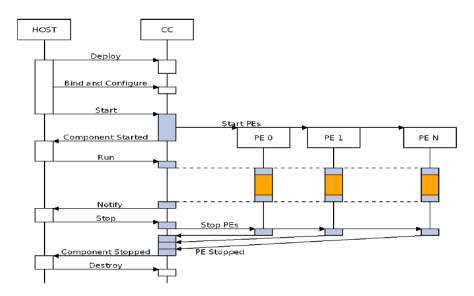

| Figure 31 Developed execution engine on top of the base runtime services and the HAL.                                                                                                            | 93    |

| Figure 32 MPI parallel code for Mandelbrot set calculation executed using STHOl platform.                                                                                                        |       |

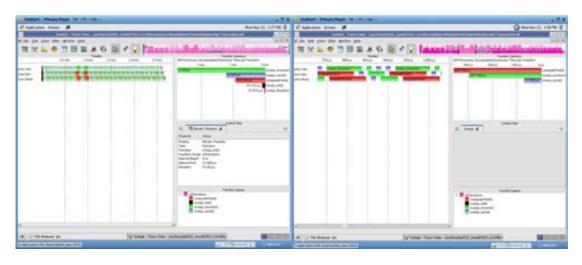

| <b>Figure 33</b> Visualisation of the traces obtained when performing Mandelbrot set calculation with 3 processors over STHORM platform. Right image zooms in a small section of the left image. |       |

| Figure 34 People counter application flow (serial version).                                                                                                                                      | 96    |

| Figure 35 Parallel version of 3D generation code.                                                                                                                                                | 96    |

| Figure 36 MPI Parallel code used on 3D generation code.                                                                                                                                          | 96    |

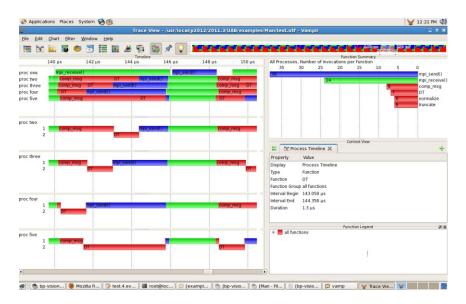

| Figure 37 Traces obtained when executing Ecomunicat's application of people cou                                                                                                                  |       |

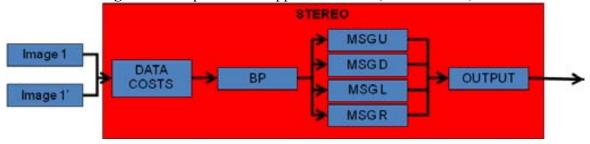

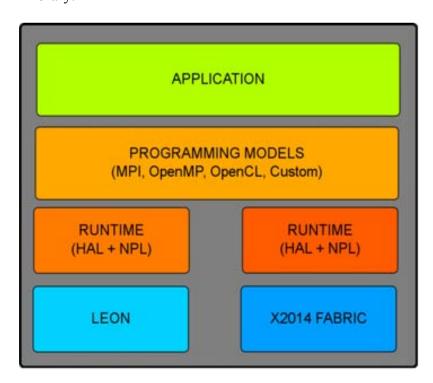

| Figure 38 Recore's Software stack diagram.                                                                                                                                                       | 98    |

| Figure 39 Recore's hardware mapping example from HAL library                                                                                                                                     | 99    |

| Figure 40 Recore's hardware assiciation example from HAL library                                                                                                                                 | 99    |

| Figure 41 Recore's MPI_Init process.                                                                                                                                                             | . 100 |

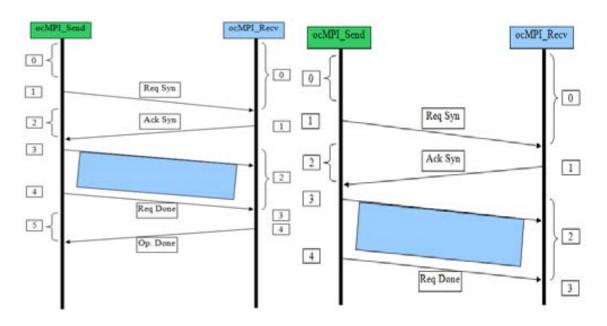

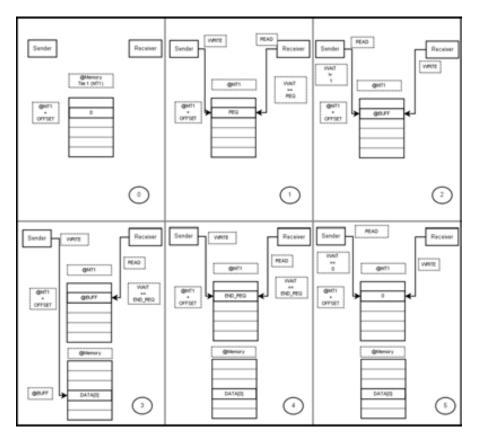

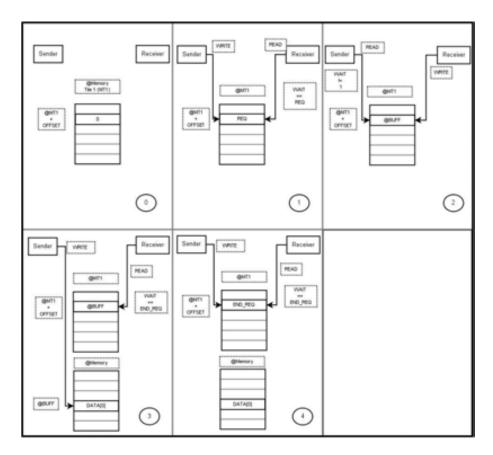

| Figure 42 Recore's MPI_SSend steps.                                                                                                                                                              | . 101 |

| Figure 43 Recore's MPI SRecv steps.                                                                                                                                                              | 101   |

| Figure 44 Recore's MPI_Send steps.                                                                                                                           | . 101 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 45 Recore's MPI_Recv steps.                                                                                                                           | . 101 |

| Figure 46 Left) Blocking Send/Recv rendezvous. Right) Synchronous Send/Recv rendezvous                                                                       |       |

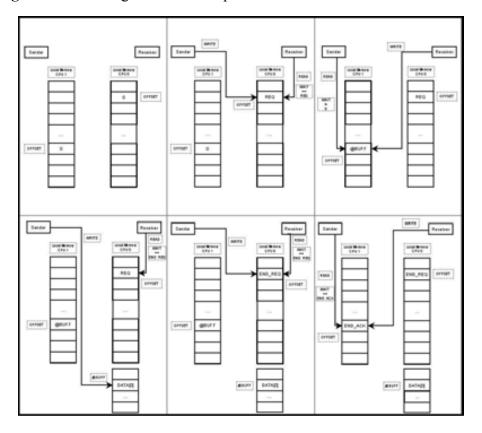

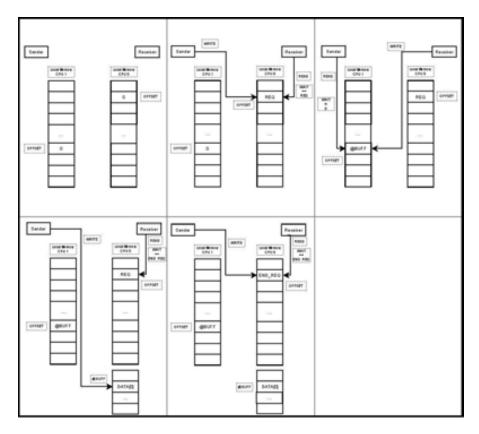

| Figure 47 Synchronous Send/Recv implementation with centralized memory                                                                                       | . 102 |

| Figure 48 Blocking Send/Recv implementation with centralized memories                                                                                        | . 103 |

| Figure 49 Synchronous Send/Recv implementation with distributed memory                                                                                       | . 103 |

| Figure 50 Blocking Send/Recv implementation with distributed memory.                                                                                         | . 104 |

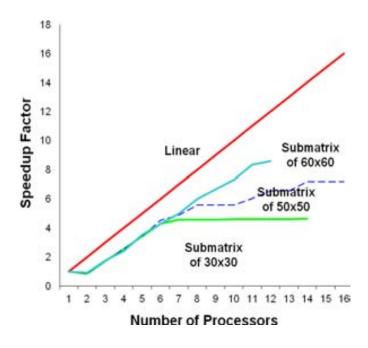

| Figure 51 Parallel MPI matrix multiplication execution over Recore's platform                                                                                | . 105 |

| Figure 52 Eager transmission protocol.                                                                                                                       | . 109 |

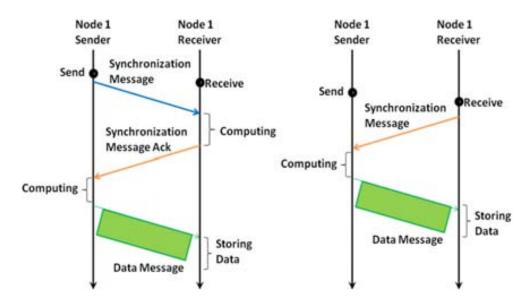

| Figure 53 Rendezvous transmission protocol. Left) Send initiates communication.  Right) Receive initiates communication.                                     | . 110 |

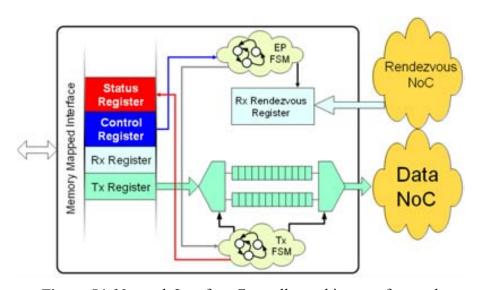

| Figure 54 Network Interface Controller architecture for <i>send</i> .                                                                                        | . 112 |

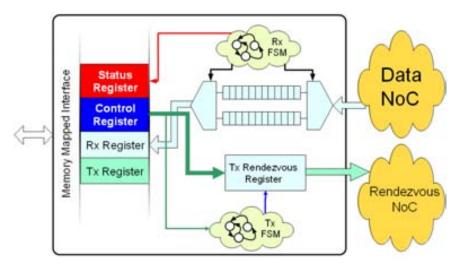

| Figure 55 Network Interface Controller architecture for <i>receive</i> .                                                                                     | . 113 |

| Figure 56 Software rendezvous scheme over NoC-based MPSoC.                                                                                                   | . 113 |

| Figure 57 Hardware rendezvous scheme over NoC-based MPSoC.                                                                                                   | . 114 |

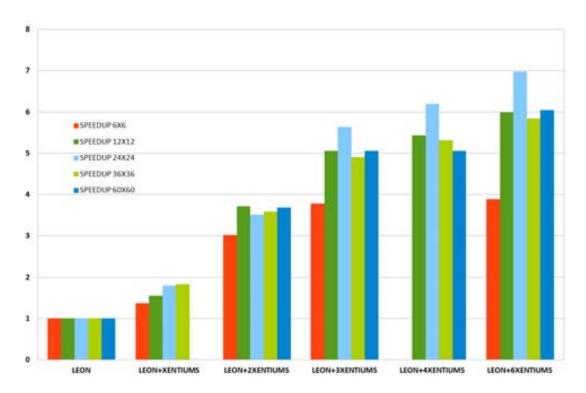

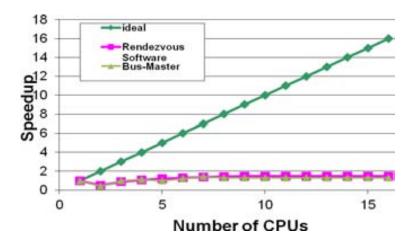

| <b>Figure 58</b> Scalability of Mandelbrot Set application for the original ocMPI implementation (pink) and for the version with Hardware Assisted Rendevouz | . 116 |

| Figure 59 Performance evolution through time processor versus memory                                                                                         | . 118 |

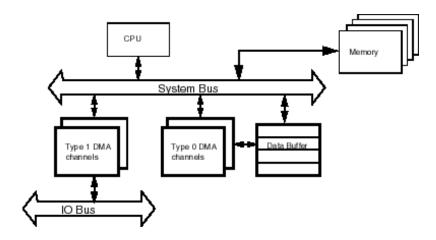

| Figure 60. Generic system with a DMA controller diagram block.                                                                                               | . 119 |

| Figure 61 Code example for perform_dma_operation function.                                                                                                   | . 120 |

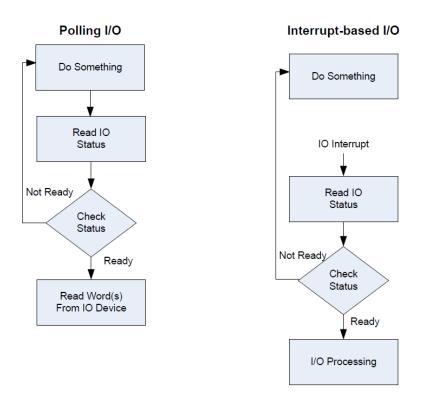

| Figure 62 DMA controller notification mechanisms.                                                                                                            | . 121 |

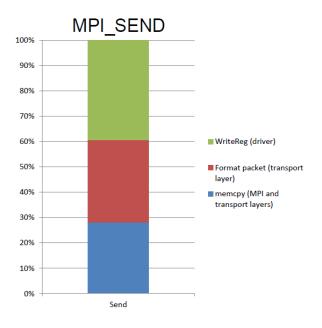

| <b>Figure 63</b> Breakdown of the MPI_SEND primitive (sending 1024 bytes of data)                                                                            | . 123 |

| Figure 64 Low level function from driver to perform a send for a Wormhole NoC.                                                                               | . 124 |

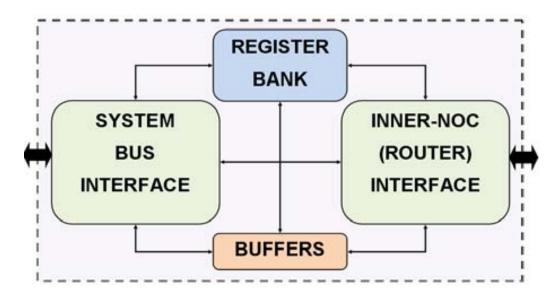

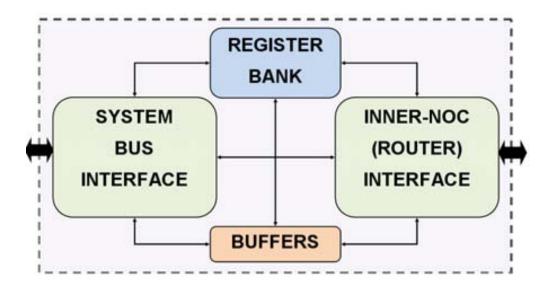

| Figure 65 Block diagram of the Bus Master NIC.                                                                                                               | . 125 |

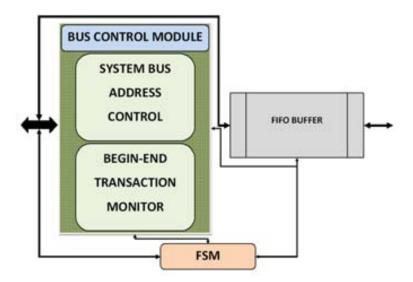

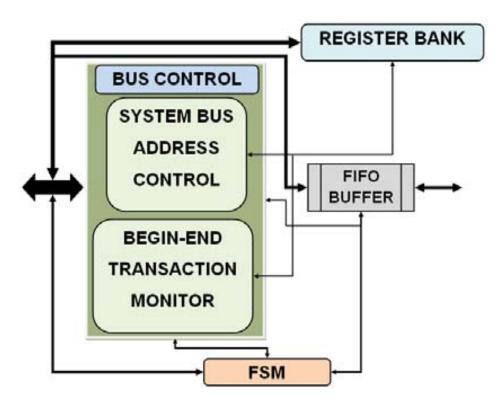

| Figure 66 Block diagram of the bus control module.                                                                                                           | . 127 |

| <b>Figure 67</b> Block diagram of the bus control module interacting with the register bar and NIC buffer.                                                   |       |

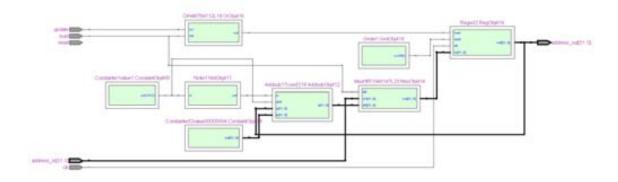

| Figure 68 Address control module RTL diagram from QUARTUSII.                                                                                                 | . 128 |

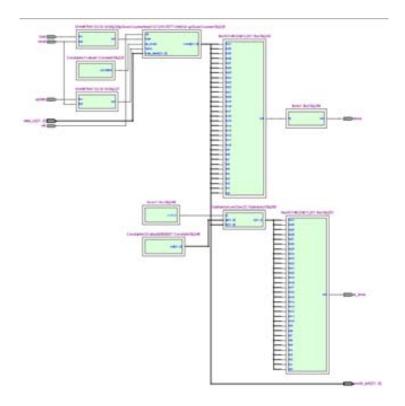

| Figure 69 Transaction monitor module RTL diagram from QUARTUSII                              | 129 |

|----------------------------------------------------------------------------------------------|-----|

| Figure 70 Matrix multiplication speedup results.                                             | 130 |

| Figure 71 Mandelbrot set computation speedup results for Bus-Master NIC                      | 131 |

| Figure 72 Simple "Hello world" MPI code example.                                             | 133 |

| Figure 73 ocMPI_Init code.                                                                   | 134 |

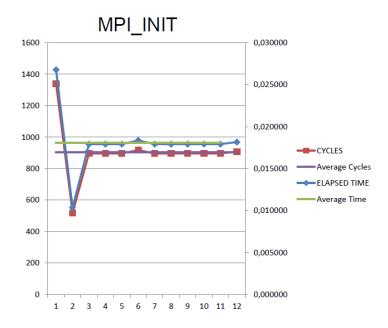

| Figure 74 Time required performing MPI_Init per processor node at 50 MHz                     | 135 |

| Figure 75 Generic NIC block diagram.                                                         | 136 |

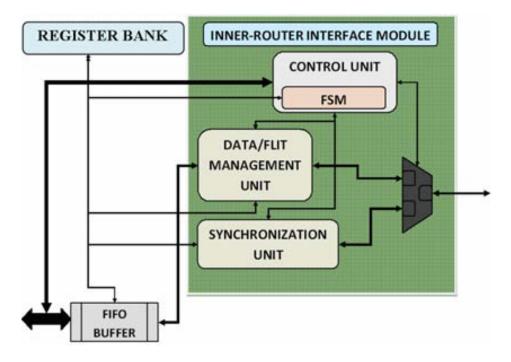

| Figure 76 Inner-router interface module block diagram.                                       | 136 |

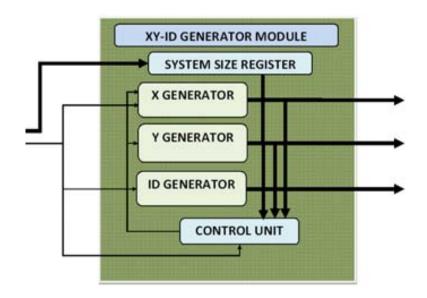

| Figure 77 Address(XY)-ID module block diagram.                                               | 137 |

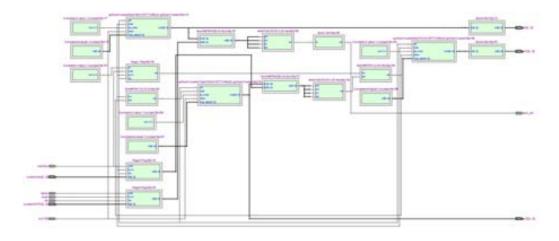

| Figure 78 Address(XY)-ID module RTL extract from QuartusII.                                  | 137 |

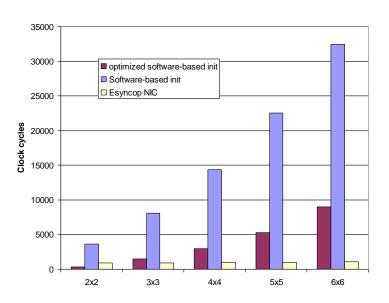

| Figure 79 MPI_init performance comparison results.                                           | 138 |

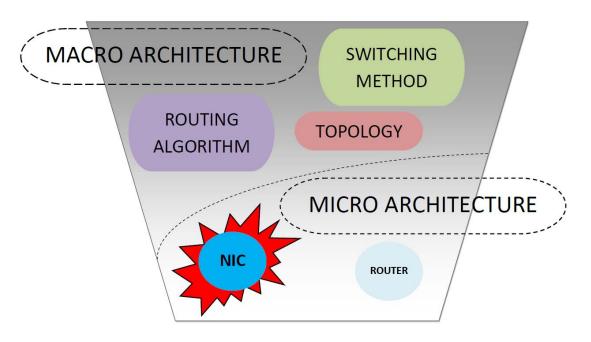

| Figure 80 Micro and macro architecture exploration done in the thesis                        | 140 |

| Figure 81 Left) MPSoC architecture Right) Software stack for MPSoC                           | 142 |

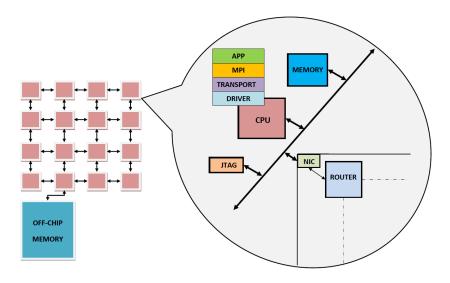

| Figure 82 NoC-based MPSoC diagram block.                                                     | 143 |

| <b>Figure 83</b> Space exploration on simulation tool connected to a real FPGA to cre MPSoC. |     |

# LIST OF TABLES

| Table 1 Left) Implemented ocMPI functions Right) Memory footprint of software         stack | . 86 |

|---------------------------------------------------------------------------------------------|------|

| Table 2 ocMPI compared with different MPI implementations for embedded systems              |      |

| Table 3 Minimal set of functions of ocMPI                                                   |      |

| Table 4 FPGA Synthesis Results NIC and NoC                                                  | 115  |

| Table 5 Comparison between the Bus Master NIC design versus the base-line NIC.              | 130  |

| <b>Table 6</b> Comparison between the Esyncop NIC design versus the base-line NIC           | 135  |

# **GLOSSARY**

**A-0** Arithmetic Language version 0

**ADL** Architecture Description Language

ALU Arithmetic Logic Unit

**ALUT** Adaptive Look-up table

**AMBA** Advanced Microcontroller Bus Architecture

**ANoC** Asynchronous NoC

**ANSI** American National Standards Institute

**API** Application Programming Interface

**APP** Application

**ASIC** Application Specific Integrated Circuit

ccNUMA cache coherence Non-Uniform Memory Access

**CFG** Control Flow Graph

**COMA** Cache Only Memory Access

**CPU** Central Processing Unit

**CUDA** Compute Unified Device Architecture

**DFG** Data Flow Graph

**DMA** Direct Memory Access

**DMAC** Direct Memory Access Controller

**DSP** Digital Signal Processor

**FFT** Fast Fourier Transfor

**FIFO** First In First Out

**FPGA** Field Programmable Gate Array

**FPU** Floating Point Unit

**GPR** General Purpose Register

**GPU** Graphics Processor Unit

**HAL** Hardware Abstraction Layer

**HDL** Hardware Description Language

**HPC** High-Performance Computing

**HW** Hardware

I/O Input/Ouput

IC Integrated Circuit

**ID** Identification

**IDE** Integrated Development Environment

**IEEE** Institute of Electrical and Electronics Engineers

**ILP** Instruction-Level Parallelism

**IP** Intellectual Properties

**ISA** Instruction Set Architecture

JTAG Join Test Action Group

**LAN** Local Area Network

**LCD** Liquid crystal display

LE Logic Element

MCU Microcontroller

MIMD Multiple-Instruction Multiple-Data

MISD Multiple-Instruction Single-Data

MM Matrix Multiplication

MOS Metal-Oxide-Semiconductor

MP Message Passing

MPI Message Passing Interface

MPSoC Multiprocessor System-on-Chip

**NA** Network Adapter

NI Network Interface

NIC Network Interface Controller

**NoC** Network-on-Chip

**NORMA** No Remote Memory Access

**NUMA** Non-Uniform Memory Access

ocMPI on-chip Message Passing Interface

**OCP** Open Core Protocol

**OCP-IP** Open Core Protocol-International Partnership

**OpenCL** Open Computing Language

**OpenMP** Open Multi-Processing

**OpenMPI** Open Message Passing Interface

**OSI** Open Systems Interconnection

**OTF** Open Trace Format

PC Personal computer

**PCB** Printed Circuit Board

PE Processor Element

**PIM** Processor-in-Memory

PIO Programmed Input/Output

**PPP** Parallel Programming Pattern

**QoS** Quality of services

**RAM** Random Access Memory

**RAMPSoC** Runtime Adaptive Multi-Processor System-on- Chip

RAMPSoC-MPI RAMPSoC-Message Passing Interface

RISC Reduced Instruction Set Computer

**RNI** Resource Network Interface

**ROM** Read-Only-Memory

SCC Single Chip Cloud

**SDK** Software Development Kit

**SDRAM** Synchronous Dynamic Random Access Memory

**SIMD** Single-Instruction Multiple-Data

**SiP** System-in-Package

SISD Single-Instruction Single-Data

**SoC** System-on-Chip

**SOPC** System on a Programmable Chip

**SRAM** Static Random Access Memory

**SW** Software

**TBB** Threading Building Blocks

**TLP** Thread-Level Parallelism

TX Transmission

**UART** Universal Asynchronous Receiver/Transmitter

UMA Uniform Memory Access

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# 1. Introduction

Ever since Lucy decided to start walking over her back legs, it is a human condition that each and every parent wishes the best for their descendents, wishes them to be more than themselves – more beautiful, more intelligent, more efficient. The same applies for engineers: they wish their little creatures to be "more", and our baby here is multiprocessors on-chip.

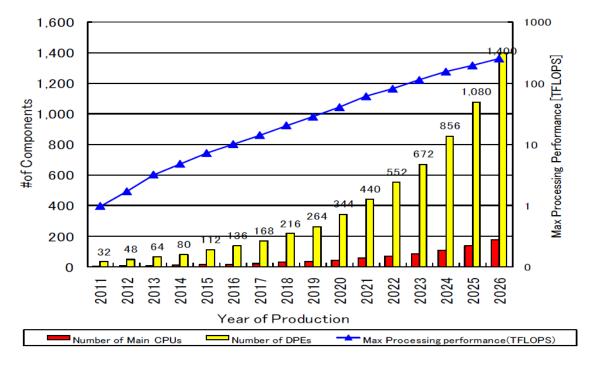

Due to the evolution of technology, future embedded System-on-Chip (SoC) processors will probably be made up of tens or hundreds of heterogeneous Intellectual Properties (IP) cores, which will execute one parallel application or even several applications running in parallel. Figure 1 shows the evolution (and prediction) of processor elements through time.

Figure 1 Number of devices versus time. [11]

Gordon Moore postulated in 1976 [1] that every 24 months approximately the number of transistors that can be integrated inside the same dice is multiplied by 2.

With such prediction, the genetic raw material is guaranteed to create every 24 months a new generation of powerful multiprocessors. But is this enough? Is it enough to face the challenges of upcoming applications?

We know now that the answer is NO: the mere evolution of technology is not enough, and it is not a sufficient condition to get better devices. Designers must adapt, find, change, and create new methodologies and electronic design automation tools to face the opportunities opened by technology. And yet, that is not enough. It is necessary to offer tools to the user to program such devices in an efficient way.

Across the last decade, system designers have been increasing their research efforts to develop an optimum interconnection system for multiprocessors devices.

This present thesis wants to contribute to the evolution of this world to achieve the goal of making our sons better.

The introduction is divided in two. The first part will talk a bout the history of the multiprocessor system-on-chip: when, how, and why of the network-on-chip concept. In the second part of the introduction, the highlight will be focused on the contributions of the thesis.

The rest of the thesis is divided into the following chapters:

- Chapter 2. General theory a bout MPSoCs a rehitectures and interconnection systems, and general theory of parallel programming models for MPSoCs.

- Chapter 3: Presentation of a simulation environment and the soft -core-NoC-Based MP SoC system im plementation used to support the of f-loading techniques shown in chapter 4.

- Chapter 3. Several MPI implementations developed in this thesis for NoC-based embedded systems using shared and parallel architectures.

- Chapter 4. Delivery protocol offloading design; Bus master of floading design; Synchronization operation offloading design.

- Chapter 5. Contributions and conclusions of the thesis.

# 1.1. Part 1- From computation to communication

Nowadays, the large computation capacity available to integrate in a single chip makes the complexity of mana gement of such r esources high, and, therefore, the focus of research is moved towards the communication system. In this part of the introduction, we are trying to give a brief in the evolution of embedded processors and computer architecture. First of all, we must say that there is plenty of literature talking about the history and evolution of computers, and it is not our intention to create a new reference document. However, as we mentioned above, we will give a brief summary using 60 milestones of the e volution throug h ti me of c omputers, e xtracted from [2][3][4][5][6][7][8][9][10]

### 1946: Eniac (Electronic Numerical Integrator and Computer) is born.

The first electronic "programmable" (general purpose) computer comes to life.

### 1948: Invention of the European transistor.

Herbert Mataré & Heinrich W elker independently create a germanium point-contact transistor in France.

### 1950: Assembly language for programming computers.

Low level programming language is introduced.

# 1952: First compiler for a programming language developed.

Grace Murray Hopper develops the first compiler for the A-0 (A rithmetic Language version 0) programming language.

### 1954: Silicon Transistors Offer Superior Operating Characteristics.

Morris Tanenbaum manufactures the first silicon transistor at Bell Labs, but Texas Instruments' engineers build and market the first commercial devices.

### 1957: First complete compiler developed.

IBM introduces the first complete compiler for FORTRAN.

### 1958: All semiconductor "Solid Circuit" is proved.

Jack Kilby produces a microcircuit with both active and passive components manufactured from a semiconductor material.

# 1959: Practical Monolithic Integrated Circuit Concept Patented.

Robert Noyce builds on Jean Hoerni's planar process to patent a monolithic integrated circuit structure that can be manufactured in high volume.

# 1961: Silicon Transistor Exceeds Germanium Speed.

Computer architect Seymour Cray funds development of the first silicon device to meet the performance demands of the world's fastest machine.

### 1963: Complementary MOS Circuit Configuration is invented.

Frank Wanlass invents the lowest power logic configuration but performance limitations impede early acceptance of today's dominant manufacturing technology.

### 1963: Institute of Electrical and Electronics Engineers.

IEEE is founded with the aim of advancing innovation and technological excellence for the benefit of humanity.

#### 1964: First Commercial MOS IC introduced.

General Microelectronics uses a Metal-Oxide-Semiconductor (MOS) process to pack more transistors on a chip than bipolar ICs and builds the first calculator chip set using technology.

### 1965: Semiconductor Read-Only-Memory Chips Appear.

Semiconductor read-only-memories (ROMs) offer high density and low cost per bit.

# 1965: "Moore's Law" Predicts the Future of Integrated Circuits.

Fairchild's Director of R & D predicts the rate of increase of transistor density on an integrated circuit and establishes a yardstick for technology progress. Gordon Moore's article, published in April 1965 Electronics Magazine, establishes Moore's Law.

### 1966: Computer Aided Design Tools Developed for ICs.

IBM engineers pioneer computer-aided electronic design automation tools for reducing errors and speeding design time.

# 1966: Flynn's Taxonomy presented.

Michael J. Flynn proposes a classification of computer architecture according to global control and data and control flows.

# 1970: Programmable logic array developed.

Texas Instruments developes PLA, programmable logic arrays based on IDM's readonly memory.

# 1972: Bell Laboratories introduce C programming Language.

C programming language is originally developed to run on DEC PDP-11 with UNIX operating system.

### 1972: Cray Research, Inc. founded.

Seymour Cray founds Cray Research in Chippewa Falls, USA.

## 1974: Scaling of IC Process Design Rules Quantified.

IBM researcher Robert Dennard's paper on process scaling on MOS memories accelerates a global race to shrink physical dimensions and manufacture ever more complex integrated circuits.

### 1974: Digital Watch is First System-On-Chip Integrated Circuit.

The Microma liquid crystal display (LCD) digital watch is the first product to integrate a complete electronic system onto a single silicon chip, called a System-On-Chip or SOC.

### 1975: Microsoft appears.

Bill Gates and Paul Allen deliver a BASIC compiler to MITS, who agrees to distribute it as Altair BASIC.

### 1975: First Cray supercomputer.

Cray Research Inc. introduces first Cray-1 supercomputer.

# 1979: Single Chip Digital Signal Processor Introduced.

Bell Labs' single-chip DSP-1 Digital Signal Processor device architecture is optimized for electronic switching systems.

### 1980: First hard disk drive for microcomputers.

Seagate Technology creates ST506 hard disk with 5megabytes of data storage capacity.

# 1981: VHDL (VHSIC Hardware Description Language).

VHDL is initially proposed to comment the behavior of ASICs.

# 1983: Altera appears.

Founding of Altera Corporation by Hartmann, Magranet, Newhagen, and Sansbury.

# 1984: First reprogrammable device.

Altera introduces the first reprogrammable logic device. Previous devices could only be programmed once.

# 1984: Xilinx appears.

Founding of Xilinx company in Silicon Valley by Freeman, Vonderschmitt, and V Barnett II.

### 1984: First FPGA device presented.

Xilinx designs the first FPGA device, called XC2000 series.

1985: Join Test Action Group formed.

JTAG is formed to develop a methodology to test IC.

1985: First commercial RISC processor.

Acorn Computer Group develops first commercial RISC processor.

1985: Intel 80386 appears.

Intel 80386, or simply 386, comes to reality as a 32-bit microprocessor with 275,000 transistors (however, the fully functional version of 386 is introduced in 1986).

1987: Borland releases the first version of Turbo C.

Turbo C gives a huge boost to the use of C in embedded applications.

1989: Intel 80486 appears.

Intel 486 appears with 1,200,000 transistors. It is a 32-bit x86-pippelined-design microprocessor, with 8192-byte of SRAM memory and two separated 32-bit buses (data and address).

1990: JTAG becomes standard.

IEEE accepts JTAG as the standard 1149.1-1990.

1993: PowerPC appears.

IBM, Apple, and Motorola introduce PowerPC architecture.

1994: Message Passing Interface library.

MPI first version is developed by a group of parallel computer vendors, programmers and scientists.

1995: Java is released.

Sun introduces Java programming language with the philosophy of letting programmers write just one code and be able to run it on any platform (Write Once, Run Anywhere).

1996: Windows Embedded CE released.

Microsoft releases the first version of Windows Embedded CE.

# 1996: Advanced Microcontroller Bus Architecture appears.

ARM releases AMBA bus, which becomes the first de facto commercial standard bus.

#### 1996: Virtual Socket Interface Alliance founded.

Several international companies from various segments of the SoC industry founded VSIA to enhance the productivity of the SoC design community.

### 1997: First Chip Multiprocessor architecture proposed.

By Hammond, Nayfeh and Olukotun from Standford University is presented including 8 cores.

# 1998: Open MultiProcessing language appears.

OpenMP is launched as an API for shared memory multiprocessing in C, C++ and Fortran.

#### 1999: GPU is released.

Graphics Processing Unit processor is introduced by NVIDIA into graphical cards.

### 2000: Daytona DSP architecture MPSoC published.

First multiprocessor system-on-chip containing four processing elements interconnected by a bus is presented.

### 2001: Open Core Protocol International Partnership created.

Sonics, Nokia, Texas Instruments, MIPS, and UMC launch OCP-IP to Standardize IP Core Socket Interface.

### 2001: OCP 1.0 Bus released.

OCP-IP launches the first OCP Bus specifications.

# 2001: Networks-on-Chip new SoC paradigm.

Several academic authors claim for adoption of NoC as interconnection paradigm for SoCs.

#### 2003: Will Networks-on-Chip Close the productivity gap?

Several problems related to busses appear as silicon technology continues advancing. Buses can efficiently connect up to 10 IP but do not scale to higher numbers.

# 2003: Arteris Company founded.

Arteris invents the industry's first commercial Network-on-Chip SoC interconnect IP solution.

### 2004: Tilera Company founded.

Tilera is founded as a manufacture of fables semiconductors and multicore embedded processor designs.

# 2005: First multicore commercial processors.

IBM, Intel, and AMD release their first multicore processors.

### 2005: CELL processor released.

IBM, Sony Computer Entertainment, and Toshiba Corporation release CELL multicore processor, which is part of PlayStation 3.

### 2007: Compute Unified Device Architecture SDK released.

NVIDIA introduces the initial CUDA SDK for Windows and Linux.

# 2007: Intel Polaris Processor.

Intel designs a multicore prototype with 80 cores called Polaris.

# 2008: Tilera TILE64 processor released.

Tilera Corporation launches TILE64 processor containing 64 programmable cores connected by a NoC.

# 2008: Intel's top processor i7 released.

Intel i7 general processor is released with 4 cores and 8 threads.

### 2008: VSI Alliance disappears

The VSI Alliance dissolved operations and transferred its ongoing work to other industry organizations

### 2010: Xilinx's Zynq FPGA families released.

Xilinx 7 FPGA families are launched with Zyng that has twin ARM Cortex-A9 cores.

### 2011: Altera releases QSYS system integration tool.

QSys is designed as the next generation SOPC builder tool.

# 2012: 22nm Manufacturing technology.

1.4 billion transistors into a single chip.

### 2014: To program multicore processors is still an uncompleted research.

As the number of transistors on a chip has been increasing through the IC history, processors have been progressing enhancing performance. Finally, this evolution allowed the creation of systems-on-chip where several IP components are integrated into a single dice. However, due also to evolution, busses showed scaling limitation when interconnecting several IP components on a SoC system. The solution appeared when the interconnection systems adopted the network-on-chip paradigm.

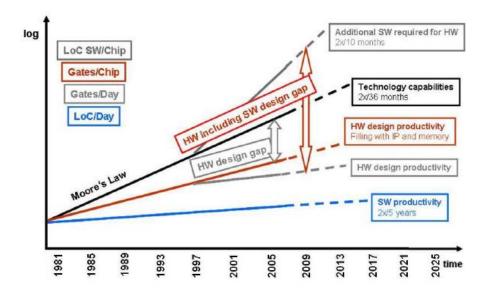

Over the last decade, academia and industry have been developing and enhancing networks-on-chip and trying to close the productivity gap (Figure 2).

**Figure 2** Hardware and software design gaps versus time <sup>1</sup>. [11]

<sup>&</sup>lt;sup>1</sup> Source: ITRS 2011

# 1.2. Part 2– Objective of this thesis

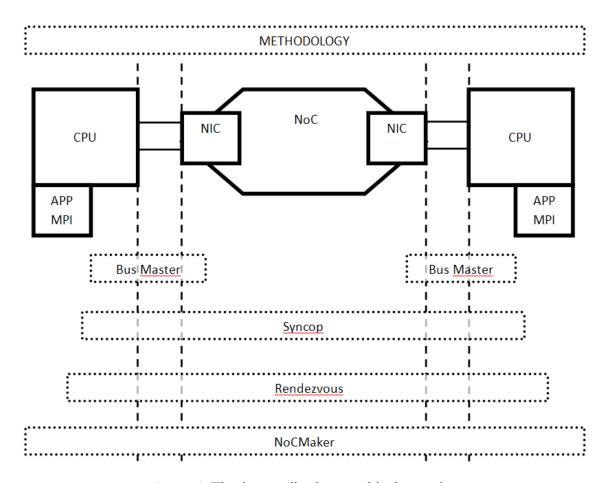

The research scope of this thesis is the concept of NoC-based MPSoC architecture in close relation with programming models for such multicore systems. In particular, the goal of this thesis focuses is to propose a message passing interface API over MPSoCs with NoCs interconnection system that uses shared or distributed memory architectures and, also, to provide techniques to improve performance of the participant processors of the system, by off-loading softwa re process to the network interface controller component.

Topics such as m emory architectures, n etwork interface controller design, programming model, and message passing interface are within the main scope of the thesis.

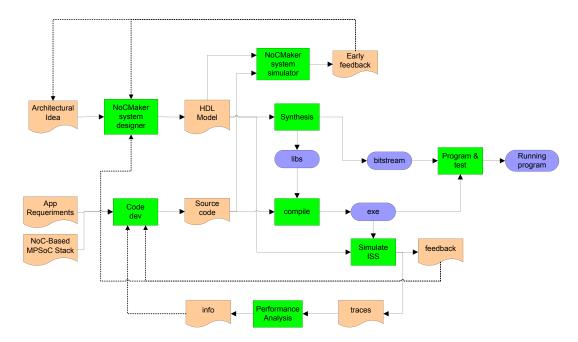

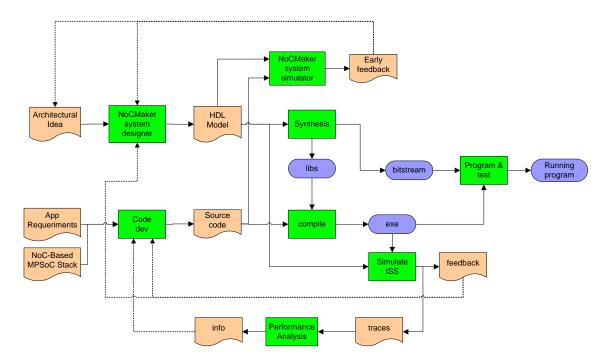

The general contribution of this thesis is to propose a general methodology to create MPSoC systems with n etworks-on-chip (Figure 3), to program such systems with a layered stack b ased on MP I-like AP I and techniques to improve the general performance of the system. The specific contributions aim to complete the existing methodologies to create, program and do performance analysis, and also, aim to help to improve the performance of the processors involved in the system by freeing them of doing some software process that will be of f-loaded to the NoC, particularly to the network interface controller.

The specific tasks where the research is focussed to reach those objectives are:

• Develop a methodology to create MP SoCs including: (i) MPSoCs design, (ii) software stack to program MPSoCs, and (iii) performance analysis.

- Contribute to the NoC simulator tool from UAB.

- Develop a MPI library for embedded systems including implementations on: (i) distributed memor y architecture s ystems (ocMPI), a nd (ii) shared memor y architecture systems (STHROM platform and Recore's Multicore systems).

- Study of MPI library overheads.

- Design of new NIC facilities: (i) Bus Master NIC, (ii) Syncop NIC, and (iii)

Rendez-vous NIC.

It must be pointed out that all contributions have been (completely or partially) implemented using FPGA platforms.

Figure 3 Full methodology flow

The contributions of the thesis are depicted in Figure 4, distributed according to their focus.

Figure 4 Thesis contribution graphical overview.

The work presented in this dissertation has been accomplished by the author of this thesis and several co-authors (academic and industrial researchers and engineers) together.

Finally, the complete list of papers on which this thesis is based on (with the full name of their co-authors) can be found in the appendix.

# 2. MPSoCs: theoretical background

# 2.1. Overview

To study MPSoCs is to talk about parallelism. So, we will start discussing a bit about parallelism before going deeper into MPSoCs systems. In this chapter, we will present a brief introduction on the current theoretical framework for parallelism.

# 2.2. Parallelism

Parallelism: Exploiting concurrency in a program with the goal of solving a problem in less time.

DR. Tim Mattson<sup>2</sup>

As this definition remarks, concurrency is crucial in parallelism and in parallel computing.

Concurrency: A property of a system in which multiple tasks that comprise the system remain active and make progress at the same time.

DR. Tim Mattson<sup>2</sup>

Concurrency is an old well-known term used in computer science theory. Carl Adam Petri was one of the first scientists to formalise and model concurrency with the Petri Nets. There are many other formalisms that model concurrency (actor model, the family model Process calculus, C-FSMs,...), but probably, Petri Nets is still the most famous model.

Nowadays, it is really common to find someone using a Smartphone with a dual-core or quad-core processor [12], or to buy a PC with 8 cores/threads [13], or even game consoles with 4 processor cores and 8 GPU cores [14]. It is obvious that parallelism and

\_\_\_

<sup>&</sup>lt;sup>2</sup> Principle engineer at Intel (Microprocessor Technology lab). [92]

parallel computing is the path to follow to create the upcoming devices and theoretical models. Parallelism has been used in several branches of technology and science, and the industrial requirements for solve complex problems make indispensable the use of parallelism.

Mankind is essentially social. We, humans, live in community, and it is in our nature to prone to parallelism to solve problems. It is unconceivable that one single person alone could construct highways or buildings, or design microchips. These human achievements are reached by a certain amount of people working together. These groups of people could have different qualities and skills, run different functions within the team, and so on.

In the computer science field, the solution of some problems turns again into parallelism. For some period of time, someone could wait for a new higher-performance-electronic-device to solve a certain problem. The continuous enhancing in technology made possible to increase the work clock frequency of transistors and, therefore, the new generations of electronic devices were faster and faster (in terms of clock frequency), and more dense in numbers of transistors.

Despite the benefits produced by this technological evolution, there was an important drawback: the increase in energy consumption and the need for power dissipation. As clock frequency rised, more switching from logic states were produced in the same amount of time and, therefore, energy consumption also raised. To compensate that, voltage supply has been decreasing for the core of the chips, down to the limit of the threshold voltage that cannot be lowered that much because the static energy consumption rises due to current at inverse biased PM junctions.

This is dynamic power consumption, which is still the major contribution to the chips (together with leakages) follows by the following formula:

$$P_{dynamic} = CV_{dd}^2 FA$$

where C depends on the wire,  $V_{DD}$  the supply voltage, F is the frequency, and A is the Activity (the amount of c hanges between 0 and 1 logic states per clock c ycle). Additionally, the static power has been growing which each new technology node [15].

Both dynamic and static power consumption have also another incidence on the performance of the system due to the increase of the temperature in the device. Higher transistor density  $\rightarrow$  More power density  $\rightarrow$  Temperature rises  $\rightarrow$  Performance lowers (speed decreases). Therefore, in many cases cooling is required. These issues could make the advances in technology shown in the Moore's law completely useless.

The exploit of parallelism helps to solve that sit uation, to c ontrol power consumption levels and power dissipation levels, while rises computing power. Figure 5 shows how parallelism helps in human challenges. In this case, the figure shows the evolution in time of the cost of human genome sequencing. It can be seen the falling in 2007 due to the use of parallel computers.

Figure 5 Declining cost of human genome sequencing <sup>3</sup>.

\_

<sup>&</sup>lt;sup>3</sup> Source: National human genome research institute.

We are going to show the characteristics and laws of parallelism, architectures of parallel computers, hardware and software solutions to achieve parallelism and the problems with communication systems.

#### 2.2.1. Characteristics

In this section, we identify the characteristics used to describe parallel systems. These characteristics can be classified in four groups that refer to: (i) the visibility of parallel resources or the concept of parallelism within the system, (ii) the variety of processing elements used to compose the parallel system, (iii) the granularity of parallelism provided by the system, and finally, (iv) who has the control of parallelism.

First group. Macroscopic vs. Microscopic.

This group deals with how parallelism is conceived.

The term microscopic relates to describing parallelism that is not necessarily visible.

To be more specific:

- Microscopic p arallelism refers to the use of p arallel hardware within a spe cific component. Some examples of microscopic parallelism are:

- o Parallel operations in an ALU.

- o Parallel access to general-purpose registers.

- o Parallel data transfer to/from physical memory.

- o Parallel transfer across an I/O interconnection system.

On the other hand, the term macroscopic relates to the concept of parallelism within the system as the leitm otiv for the system de sign. Some examples of macroscopic parallelism are:

• Duel-core (multi-core) Intel processors

#### NVIVDIA Graphic devices

#### Second group. Symmetric vs. Asymmetric.

This group deals with the main components with which the parallel system is built. It can be also referred as homogeneous and heterogeneous.

The term symmetric (or homogeneous) means that the main processors of the system are all the same. Some examples of symmetric parallel systems are:

- Duel-core (multi-core) Intel processors.

- NVIVDIA Graphic devices.

On the other hand, the term asymmetric (or he terogeneous) means that there is (some) variety within the processors found in the system.

#### Third group. Fine-grain vs. Coarse-grain.

This group deals with at which level parallelism is achieved. The term fine-grain (or small-grain) means that parallelism is a chieved at (single) data or (single) instruction level (where non-dependent data can be processed in parallel). Some examples of fine-grain level are:

- Matrix multiplication using row and column method.

- Computing single pixels.

On the other hand, in the coarse-grain (or large-grain) level parallelism is achieved at entire routines levels (programs or large portions of data). Some examples of coarse-grain level are:

- Computing FFTs

- Computing frames

#### Fourth group. Implicit vs. Explicit.

This group deals with who is in charge to control parallelism. In implicit parallelism the control of parallelism is assumed by the programmer.

On the other hand, explicit parallelism (or transparent) does not require a programmer to take the control of parallelism.

#### 2.2.2. Laws

So far, to parallelize an application appears as the magical solution to avoid all the problems related with computational time spent to solve a problem, energy consumption expended by the parallel system to solve a problem, and so on.

However, to achieve a useful parallelism is tricky. According to John Harper<sup>4</sup>:

"Building multiprocessor systems that scale while correctly synchronizing the use of shared resources is very tricky, whence the principle: with careful design and attention to detail, an N-processor system can be made to perform nearly as well as a single-processor system. (Not nearly N times better, nearly as good in total performance as you were getting from a single processor). You have to be very good — and have the right problem with the right decomposability — to do better than this."

In a more formal way, Gene Amdahl [1] expresses his point of view in 1967 using the following formula:

$$SpeedUp = \frac{(St + Pt)}{(St + \frac{Pt}{N})}$$

where St means the time spent in serial computation by a serial processor, Pt the time spent by a serial processor in the parts of the program that can be processed in

\_

<sup>4</sup> http://www.john-a-harper.com/john-harper-resume-20110901.pdf

parallel, so therefore St + Pt is the total time used computing, and N is the number of processors.

In other words, the Amdahl's law says that the max imum speed up that c and e achieved by any process is limited to the weakest link part of this process. Usually, any process can be divided in two parts:

- Serial sections, always present.

- Parallel code, not always present.

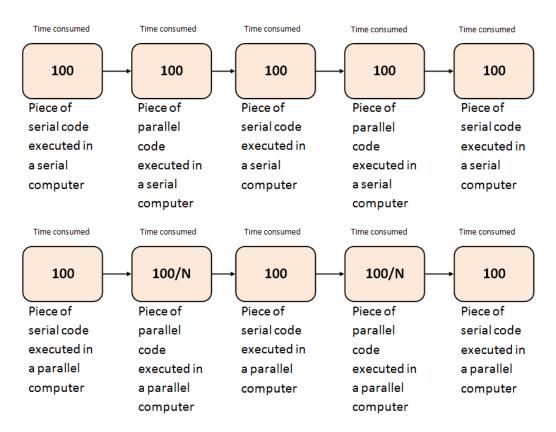

Therefore, the speedup of a process using multiple processors in parallel computing is limited by the time needed for serial sections (weakest part in a parallel process) of the process. For example, if we pay attention to Figure 6 we can see that a certain application can be divided in 5 computing modules and each of them consumes 100 unit times to be executed.

Figure 6 Speedup on Amdah's law.

When executed in a serial computer, the total time spent by the application is 500 time units. However, this application has two modules that can be executed in parallel Therefore, the time required by these two modules when executed in a parallel system is 100 time units divided by the number of processors used to compute those modules. At the extreme, using an enormous amount of processors, the time required by these two modules can be considered 0 (since 100 divided by N will be some value close to 0). In this case, the total time spent by the application will be 300 time unit versus 500 time units used by the serial system. That means a speedup of 1,66 using so many processors, just saved the 40% of the time.

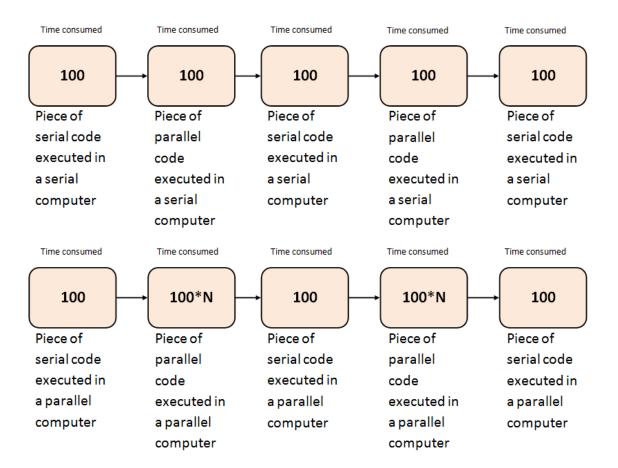

In 1988, at Sandia National Laboratories, John L. Gustafson et al. [21] presented their research involving massively-parallel processing to fight scepticism regarding the viability of massive parallel systems due to the Amdahl's law. Therefore, Gustafson stated the law known as Gustafson's Law, which states that increasing the number of processors gives linear speed up. More processors allow larger dataset size.

For example, using the same previous case, where a certain application, in a serial computer, uses 100 time units to compute a certain amount of data in serial and parallel pieces of code, Figure 7.

When the application is performed in a parallel computer, in the pieces of code that can be parallel, it can be run using more data information and therefore, if in the parallel part 10 threads of dataset are used, the speed up achieved is over 2,17 (Speedup = (500\*10)/(100\*3 + 100\*10\*2).

So the difference with Amdahl's law is that Gustafson proposed fixed time and increased work load. Therefore, serial parts of the program have a diminishing effect in reducing the overall speedup in a parallel environment.

Figure 7 Speedup on Gustafson's law.

His tests revealed that, as processors grow, the problem size is scaled and this scaling results in a substantial increase in the parallel parts of the program as compared to the serial parts. In other words, Amdahl fixed work and Gustafson fixed work per processor.

#### 2.2.3. Hardware Solutions

How parallelism is achieved or supported in hardware? In previous sections we have described the characteristics and laws of parallelism, how we can distinguish and, classify parallelism, but the question now is: how is all of this supported in hardware? What is beneath the surface?

While the clock frequency of the CPU was rising, the instruction throughput per second was also incising. So, the main technique to increase performance was clock frequency scaling. However, there are other techniques to increase the performance of the processor, for instance parallelism that does not increase power consumption in the same way that clock scaling.

When talking about single processors, parallelism is a chieved using pipeline. The pipeline technique allows the execution of several instructions simultaneously. This is achieved by dividing instructions in steps or stages that are processed sequentially one to next in a pipe-like shape. The first step enters first, following by the second stage of the instruction, and leaves first, followed by the second stage, and so on.

This technique does not execute a single instruction in parallel; however it allows to execute several instructions at the same time and to increase the instruction throughput Figure 8. The refore, the instruction throughput is defined as the frequency of the instructions leaving the pipeline.

|         |    |    |    |    | Current<br>Instruction |    |    |    |    |

|---------|----|----|----|----|------------------------|----|----|----|----|

| Cycle 1 | IF | ID | EX | MA | WB                     |    |    |    |    |

| Cycle 2 |    | IF | ID | EX | MA                     | WB |    |    |    |

| Cycle 3 |    |    | IF | ID | EX                     | MA | WB |    |    |

| Cycle 4 |    |    |    | IF | ID                     | EX | MA | WB |    |

| Cycle 5 |    |    |    |    | IF                     | ID | EX | MA | WB |

|         |    |    |    |    |                        |    |    |    |    |

Figure 8 Five stages deep pipeline example [93].

The pipeline technique imposes some restrictions to be used properly. Since any stage can be processed at the same time with any other stage, the time required to process any stage is determined by the time required to process the slowest pipe stage. When the processor has a balanced pipeline stages then, the time per instruction on the processor follows the formula:  $TPI = (Ti_{NP})/(N)$

Where TPI is the time per instruction,  $Ti_{NP}$  Time per instruction on the non-pipelined machine, and N is the Number of pipe stages.

The speedup that can be obtained from the use of the pipeline technique is equal to the number of pipe stages, but only if the stages are perfectly balanced. The balancing of the pipe is a duty of the pipe designer. Usually, the stages are not perfectly balanced, since the pipeline introduces some overhead.

Pipelining is the parallelism technique used for mono-processor. But there are other ways to support parallelism in hardware.

The most common way to implement a parallel system is to create a multi-processor system. Since clock frequency scaling is not anymore a viable solution (due to the fact that we are reaching the physical limits), the focus has been moved to scale the number of cores available per processor.

There a re three main types of multi-processors ystems based on their memory architecture: (i)—shared-memory, (ii)—distributed-memory, and (iii)—hybrid shared-distributed-memory. We define multi-core systems when the number of processor cores is less than 16. When there are more than 16 then we used the term many-core system. Some examples of many-core systems are the NVIDIA GPUs, or the research platform from ST Microelectronics STHORM. Later on this document, we will go deep on many-core systems details.

The last way of parallelism in hardware is the multi-computers systems (or clusters). Cluster systems have long been used in scientific computing, where large problem sizes could not be solved on a sing le processor. In the 70s, the first supercomputer was introduced by Seymour Cray. The first Cray-1 supercomputer system was installed at Los Alamos National Lab for 8.8 million dollars, and achieved 160 me gaflops and had 8 mega byte main memory [22]. In 2011, C ray installed the Jaguar's upercomputer

supported 200 cabinets of Cray XT5 blades, and each cabinet can be hold 24 Cray XK6 blades. That is 307200 CPU cores with 16 petaflops. Multi-computer systems can be created by interconnecting through a large network (LAN, internet) a large number of full computers, such a PCs, laptops, workstations, and so on. This can be called as grid computer. Examples of multi-computer systems are the Condor platform from UAB for instance.

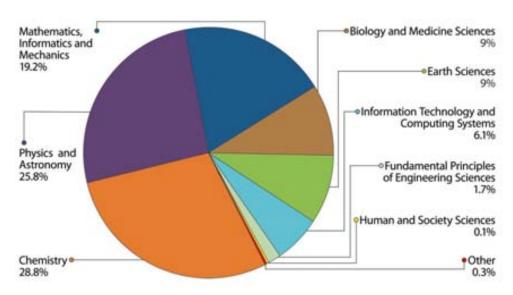

Supercomputers have been essential in cryptography tasks. Figure 9 shows the breakdown of uses of supercomputers systems.

Figure 9 Breakdown of uses of supercomputer systems<sup>5</sup>.

## 2.2.4. Theory of Architectures

In this section, we enumerate the different options of available architectures, and following the classifications on the theory, we select the suitable one for our MPSoCs.

Following Flynn's taxonomy [23][24], computer systems may be classified according to global control, and data and control flows. In practice, Flynn's taxonomy distinguishes between four categories:

\_

<sup>&</sup>lt;sup>5</sup> Source: Moscow University Supercomputing Center. http://hpc.msu.ru/?q=node/77

- Single-Instruction Single-Data (SISD). When a serial computer does not exploits any kind of parallelism. A single control unit fetches a single instruction from memory.

The most e vident e xamples of this category a rethe classical single-processor machines used as a PC like the desktop computers. It must be said that n owadays PC systems have multiple processors.

- Multiple-Instruction Single-Data (MISD). When a computer system exploits a single data flow in several instruction flows. This category is used in fault tolerant systems.

- Single-Instruction Mul tiple-Data (S IMD). When a computer exploits several data flows in a single instruction flow, to process parallel operations. GPUs are an evident example of this category.

- Multiple-Instruction Multiple-Data (MIMD). When a computer exploits several data flows in several instruction flows. Multiple processors executing in parallel different instructions using different data.

We select MIMD because it has multiple processing elements with separate data and instruction access to data and program data memory (shared or distributed). In MIMD each processing element can execute its own program; therefore, it is a more flexible architecture than SIMD, with only one program memory, and MISD, with one common access to a single global data memory. SISD is not even considered here since there is not a multi-processor.

Nearly all general-purpose parallel computers follow the MIMD model. However, according to the memory organization and to the different point of view from which it can be seen (physical or the programmer's), MIMD may be further classified. From the programmer's point of view, we must distinguish two cases: distributed address space or shared address space. It needs to be clarified that this classification does not match necessarily physical classification.

From the physical point of view, a memory may be classified as a shared memory or distributed memory, even though there are hybrid organizations that can provide, for instance, a virtual shared memory on a physical distributed memory.

In shared memory organization, processing elements can operate independently while sharing the same memory resources, which becomes the source of several problems. Shared memory architectures may be mainly divided into two classes based upon the memory access time: Uniform Memory Access (UMA) and Non-Uniform Memory Access (NUMA).

In UMA architectures, using an indirect network to access the external memory imposes a uniform latency to access the memory, which could be a counterproductive requirement in a large MPSoC since some processors will be much closer to external memory than others will and, consequently, performance will drop.

NUMA architectures mitigate this scalability problem presented in UMA architectures. In NUMA (ccNUMA when cache coherence is used) architectures, not all processors have equal access time to all memories. However, ccNUMA ultimately suffers the bottlenecks imposed by cache coherence protocols as indicated by Heinrich et al in [25].

Despite the fact that data sharing between processor elements is faster in shared memory architectures than in distributed memory, the lack of scalability between memory and processor elements is the primary disadvantage of such architectures.

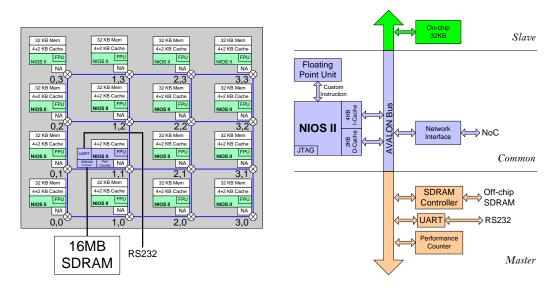

For this reason, we choose distributed memory architectures for our system. These architectures could be a viable way to overcome the limits that cache coherency imposes in terms of performance and in additional hardware support, becoming scalable architectures [26].

In distributed architectures, each core is a complete computer system, where no processor is allowed to access the memory module of another processor; hence, these systems can be called No Remote Memory Access (NORMA) architectures.

However, since the chip pinout is limited and external memory is mandatory for MPSoCs, not every core will be able to access the external memory.

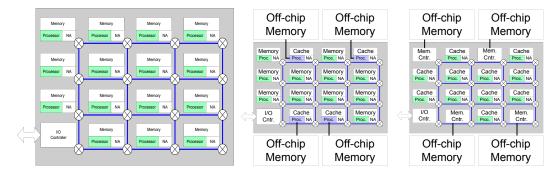

Consequently, homogeneous NORMA, as depicted in Figure 10 (left), will be only feasible for a very limited set of applications with low memory demand.

Two particular architectures are promising alternatives: COMA (Cache Only Memory Access) and heterogeneous NORMA. In COMA architectures, Figure 10 (right), processors have only cache and the rest of the memory is accessed through special I/O hardware. It might seem strange that we consider COMA to be a distributed memory architecture, but the reason is that interconnect is not necessary tailored to memory transactions. The main problem with this architecture is the need for additional hardware to control the input and output to the off-chip memory.

In heterogeneous NORMA, Figure 10 (middle), only a few processors would access the external memory. These processors have some cache memories and control the other processors of the system, which would access only their local memory. Therefore, distributed architectures solve the problems of scalability existing in shared memory architectures [25][26].

All this considered, for our MPSoC system we select the distributed heterogeneous NORMA architecture, which provides us flexibility – since each core can execute its own program flow– scalability, and does not require any special hardware, as in COMA architectures.

Figure 10 Left) Homogeneous NORMA. Middle) Heterogeneous NORMA. Right) COMA.

#### 2.2.5. Software Solutions / Levels of Parallelism

From the software point of view, the parallelism can be classified on two different levels of parallelism:

- ILP. I nstruction-level parallelism. When se veral instructions from the same instruction stream are executed in parallel.

- TLP. Thread level parallelism. When several threads from the same application are executed in parallel.

Multithreading attempts to push the utilization of functional units further by sharing functional units between more than one thread. Each thread has its own copy of the PC, register files, GPR, and so on

Thread switching time needs to be optimized. Virtual memory supports the sharing of memory resources. Two basic methodologies,

- Fine-grained multithreading:

- o Threads interleaved on an instruction by instruction basis

- Stalled threads are ignored.

- o Advantage,

- Smoothes out any stall cycles.

- Disadvantage,

- Increases the latency of any single thread.

- Course-grained multithreading:

- Only switches between thread execution on a 'costly' stall (e.g. a cache miss)

- o Advantage,

- Prioritizes the throughput of a specific thread.

- Simpler to control!

- o Disadvantage,

- Each thread switch encounters a startup overhead (empty pipe).

- Overall throughput and individual thread latency both poor

- Not used in commercial CPUs

# 2.3. Theory of interconnection architectures

All this considered, for our MPSoC system we select the distributed heterogeneous NORMA architecture, which provides us flexibility – since each core can execute its own program flow – scalability, and does not require any special hardware, as in COMA architectures.

Future e mbedded S ystem-on-Chip (SoC) will probably be made up of tens or hundreds of he terogeneous Intellectual P roperties (IP) cores, which will execute one parallel application or e ven se veral applications running in parallel. These s ystems could be possible due to the constant evolution in technology that follows the Moore's law, which will lead us to integrate more transistors on a single die, or the same number of transistors in a smaller die.

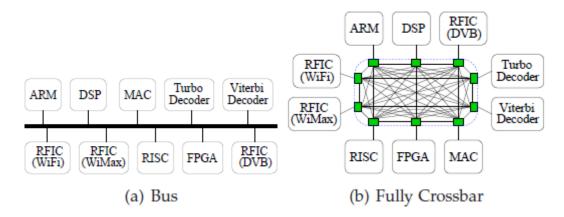

For such S oCs, Ne twork-on-Chip (NoC) architectures are the solution for the scalability pr oblem. T raditional on -bus c ommunication-based solutions, **Figure 11**a,

pose serious problems related to the integration of several IP cores. As the number of components connected to the bus raises, the bus system will produce a performance bottleneck problem [16] appears in the bus system.

**Figure 11** Interconnection systems a) Bus-based system approach b) Crossbar-based system approach.

An alternative for on-bus communication solution is to substitute the bus connection by a fully crossbar system, Figure 11b, but as the number of participating components rises, the complexity of the wires could be dominant over the logical parts.

Finally, NoC-based interconnection system was presented as the solution to these problems. The NoC [16][17][18][19][20] entails a unified solution to the On-Chip communication and the possibility to do scalable systems at supportable levels of power consumption. In embedded MPSoC systems, NoCs can provide a flexible communication infrastructure, in which several components such as microprocessor cores, MCU, DSP, GPU, memories, and other IP components can be interconnected. NoCs have been extensively discussed in several regular publications and special issues, from journals to conferences and workshops, and also, the NoC topic has inspired symposiums like ACM/IEEE International Symposium on Network-on-Chip.

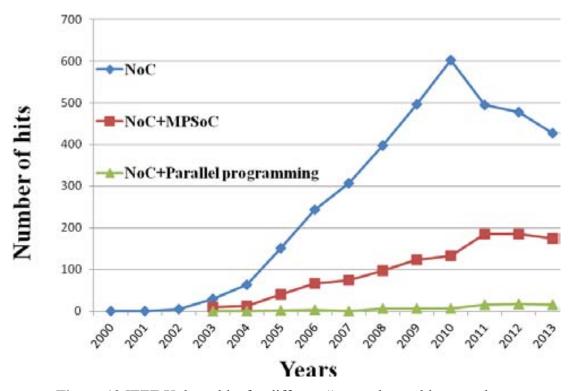

Figure 12 shows the evolution of the interest the NoC topic has raised in the last decade in terms of hits when "network-on-chip" is searched in the IEEE Xplore digital

library [27]. 0 also shows the evolution of a nother two topi cs combined with NoCs: multiprocessor systems based on ne twork-on-chip interconnection system publications have be en increasing it s popularity year by year, whereas the other topic, parallel programming model for such systems, seems not to be increasing its popularity among the academia, despite the interests shown by the industry in such topic.

Figure 12 IEEE Xplorer hits for different "network-on-chip" searches

# 2.3.1. NoC Components

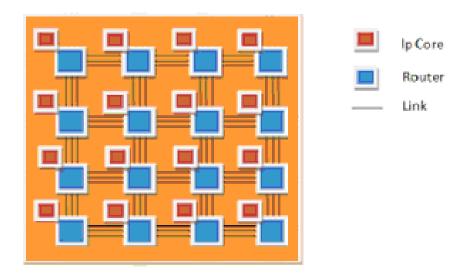

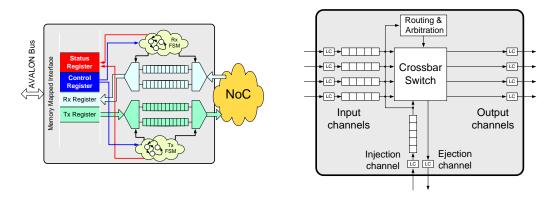

Basically there are just three main components on a NoC-based system (Figure 13):

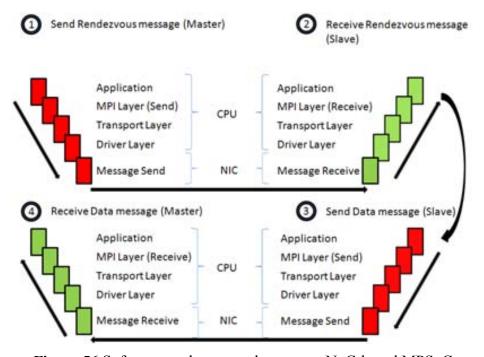

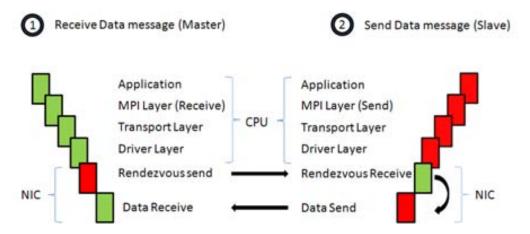

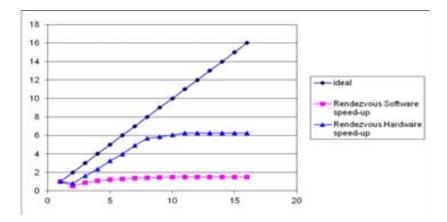

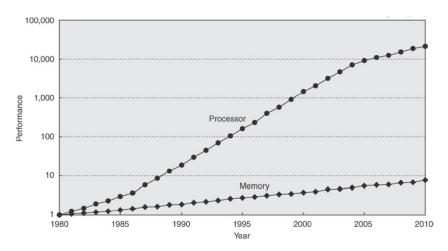

**Figure 13** NoC representation.