**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# A Novel Access Pattern-based Multi-core Memory Architecture

# Author: Tassadaq Hussain

Advisors:

Dr. Oscar Palomar, Dr. Adrian Cristal, Dr. Osman S. Ünsal, Prof. Eduard Ayguadé and Prof. Mateo Valero

Submitted to the Departament d'Arquitectura de Computadors in Partial Fulfillment of the Requirements for

Doctor of Philosophy (PhD)

Barcelona - December 2014

To my father Aman Ullah Cheema, my sweet mother Iffat Tanveer, my lovely wife Amna Hussain and my charming little kid Umar Hussain

## Acknowledgements

- \* All praises are due to Allah and may He send His salutations on our Master and Messenger of Allah Muhammad (P.B.U.H) and his brethren among the Prophets and Messengers and on their families and companions and whoever followed them in righteousness until the Day of Judgment.

- \* This work was not possible to complete without the help of my advisors. My cordial gratitude goes to my supervisors: Prof. Mateo Valero, Prof. Eduard Ayguadé, Dr. Adrian Cristal, Dr. Osman S. Ünsal and Dr. Oscar Palomar. I can never forget their outstanding manners, genius way of thinking and benevolence towards me. Because of their fruitful and everlasting efforts I feel very confident in myself in the field of science and technology. I often drew the inspiration from their incessant novel ideas. I consider myself fortunate to have the honor of being a Ph.D. student under their supervision. Dr. Oscar Palomar is the one who was absorbing and tolerating my strange ideas and helping me extraordinarily to bring them into good and meaningful shape before that these are presented to our seniors and as well at various research platforms. He has been conducting regular meetings throughout the years. I always found him ready to spare time for the research discussions.

- \* I would like to express my gratitude to Dr Miquel Pericas and Prof. Nacho Navarro. They helped me a lot to push this work ahead in the right direction. Later, my research group was changed but my learning with them helped me a lot to effectively pursue later studies.

\* The acknowledgements will remain incomplete if I do not quote the organizations and the projects who financially supported this thesis. These include Barcelona Supercomputing Center (BSC), Technical University of Catalonia (UPC), The Ministry of Science and Innovation of Spain (Project: Computaciòn de Altas Prestaciones V, TIN2007-60625), The European Union Framework Program-7 (Project: Scalable Computer Architecture, IST-2006-27648), the HiPEAC-2 Network of Excellence (FP7/ICT 217068), the European Commission in the context of the SARC Project #27648 (FP6), the European Research Council under the European Unions 7th FP (FP/2007-2013) / ERC GA n. 321253, the Spanish Government (TIN2012-34557), and the Unal Center of Education Research and Development (UCERD). I am extremely thankful to all these organizations for their full support during the work.

## **Abstract**

Increasingly High-Performance Computing (HPC) applications run on heterogeneous multi-core platforms. The basic reason of the growing popularity of these architectures is their low power consumption, and high throughput oriented nature. However, this throughput imposes a requirement on the data to be supplied in a high throughput manner for the multicore system. This results in the necessity of an efficient management of on-chip and off-chip memory data transfers, which is a significant challenge. Complex regular and irregular memory data transfer patterns are becoming widely dominant for a range of application domains including the scientific, image and signal processing. Data accesses can be arranged in independent patterns that an efficient memory management can exploit. The software based approaches using general purpose caches and on-chip memories are beneficial to some extent. However, the task of efficient data management for the throughput oriented devices could be improved by providing hardware mechanisms that exploit the knowledge of access patterns in memory management and scheduling of accesses for a heterogeneous multi-core architecture.

The focus of this thesis is to present architectural explorations for a novel access pattern-based multi-core memory architecture. In general, the thesis covers four main aspects of memory system in this research. These aspects can be categorized as: i) Uni-core Memory System for Regular Data Pattern. ii) Multi-core Memory System for Regular Data Pattern. iii) Uni-core Memory System for Irregular Data Pattern. and iv) Multi-core Memory System for Irregular Data Pattern.

# **Contents**

| List of Figures |                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |

|-----------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Li              | List of Tables |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |

| Ι               | Int            | trodu   | ction and Research Proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1    |  |

| 1               | Intr           | oductio | on Control of the Con | 3    |  |

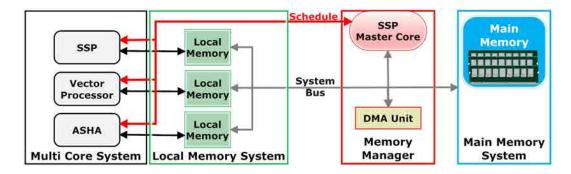

|                 | 1.1            | Target  | t Heterogeneous Multi-core Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 6  |  |

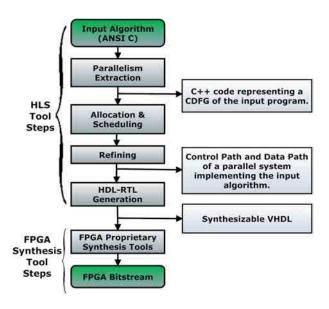

|                 |                | 1.1.1   | Field Programmable Gate Arrays (FPGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 7  |  |

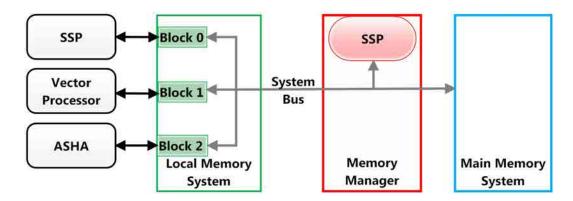

|                 |                | 1.1.2   | Scalar Soft Processor core (SSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 8  |  |

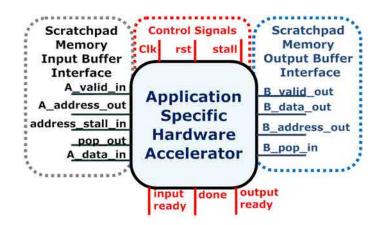

|                 |                | 1.1.3   | Application Specific Hardware Accelerator (ASHA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 9  |  |

|                 |                | 1.1.4   | Vector Processor (VP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 11 |  |

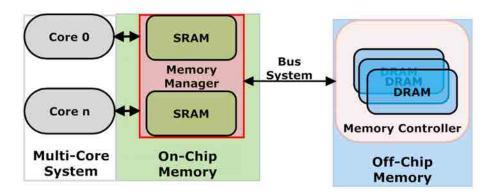

|                 | 1.2            | A Con   | nventional Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 12 |  |

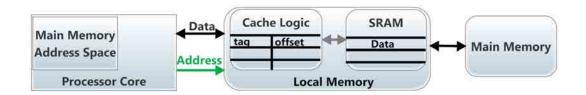

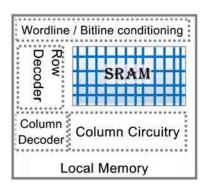

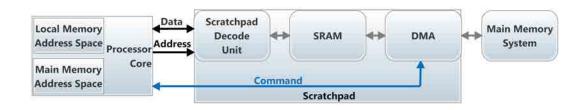

|                 |                | 1.2.1   | Local Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 12 |  |

|                 |                |         | 1.2.1.1 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 13 |  |

|                 |                |         | 1.2.1.2 Scratchpad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 14 |  |

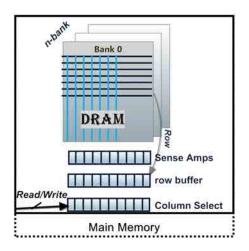

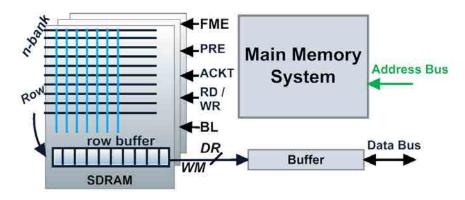

|                 |                | 1.2.2   | Main Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 15 |  |

|                 | 1.3            | Proble  | em and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 17 |  |

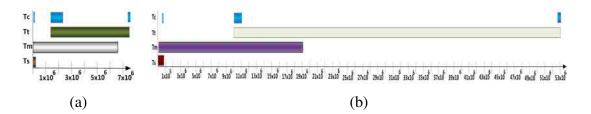

|                 |                | 1.3.1   | Multi-core System Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 17 |  |

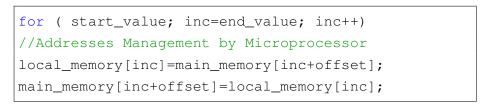

|                 |                |         | 1.3.1.1 Memory Management Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 17 |  |

|                 |                |         | 1.3.1.2 Bus Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 19 |  |

|                 |                |         | 1.3.1.3 Scheduling Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 20 |  |

|                 |                |         | 1.3.1.4 Memory Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 20 |  |

|                 |                | 1.3.2   | Access Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 21 |  |

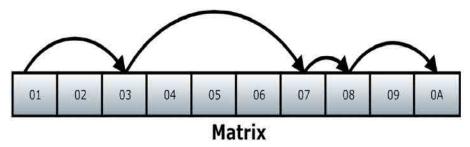

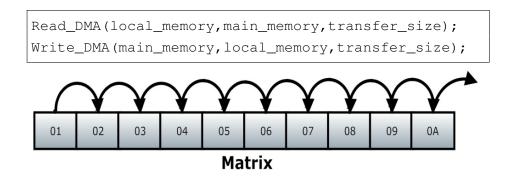

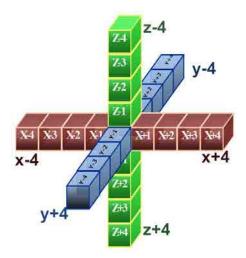

|                 |                |         | 1.3.2.1 Regular Access Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 21 |  |

|                 |                |         | 1.3.2.2 Irregular Access Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 22 |  |

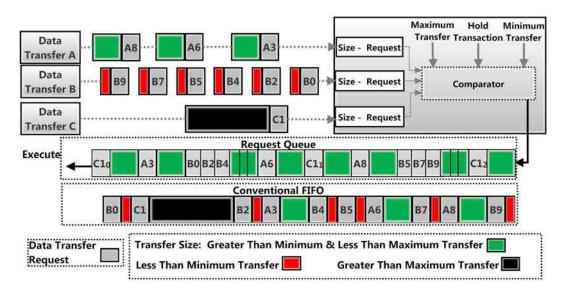

|                 |                | 133     | Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23   |  |

|    |      |         | 1.3.3.1 Symmetric Scheduling                            | 23 |

|----|------|---------|---------------------------------------------------------|----|

|    |      |         | 1.3.3.2 Asymmetric Scheduling                           | 23 |

|    |      |         | 1.3.3.3 Run-time Scheduling                             | 24 |

|    | 1.4  | Thesis  | Contributions                                           | 24 |

|    |      | 1.4.1   | Regular Data Access Patterns For Single Core            | 24 |

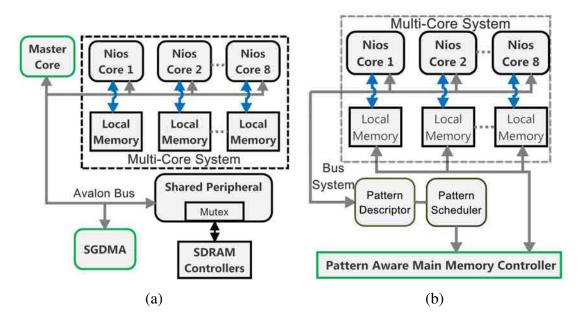

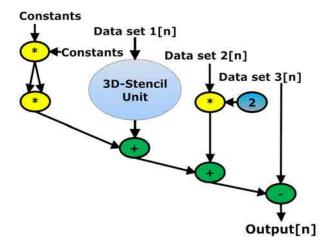

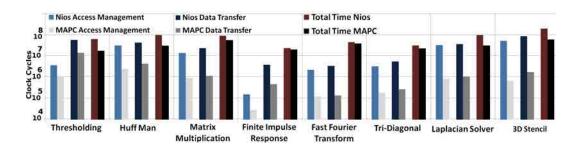

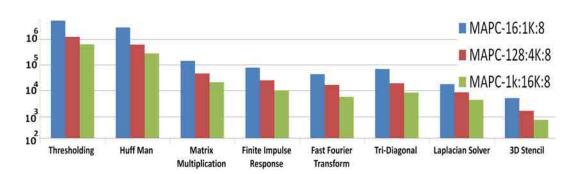

|    |      | 1.4.2   | Multi Core System with Regular Data Patterns            | 25 |

|    |      | 1.4.3   | Single Core System with Irregular Data Transfer Support | 26 |

|    |      | 1.4.4   | Multi Core System with Irregular Data Transfer Support  | 26 |

|    | 1.5  | Thesis  | Organization                                            | 26 |

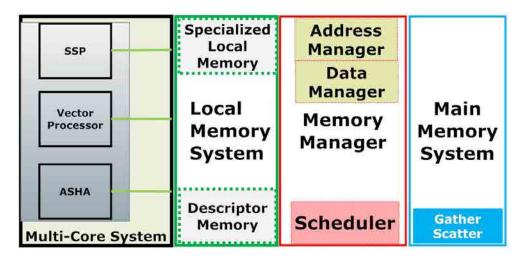

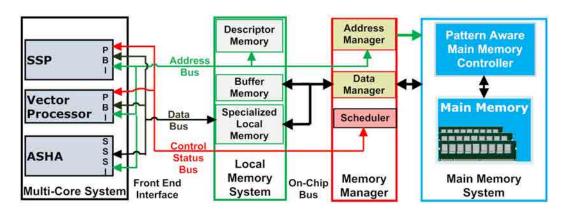

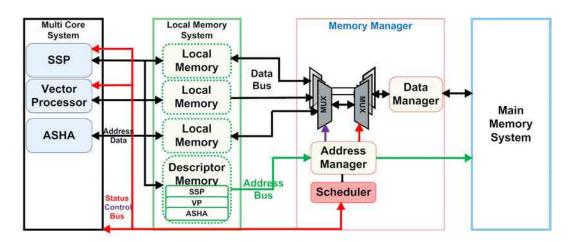

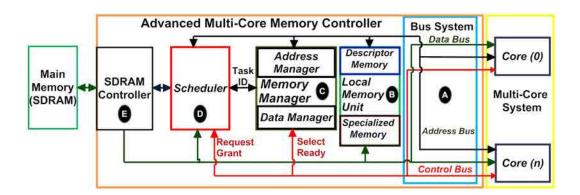

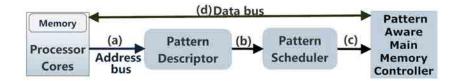

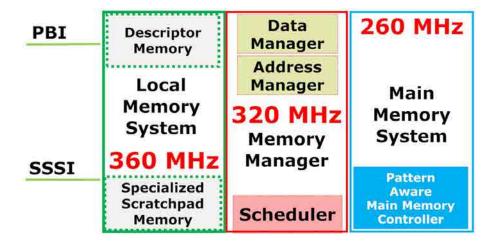

| 2  | Proj | posed H | eterogeneous Multi-Core Memory System                   | 29 |

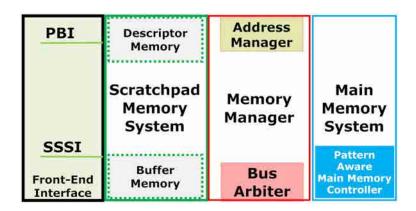

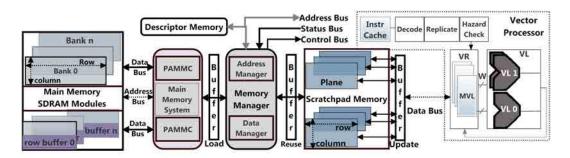

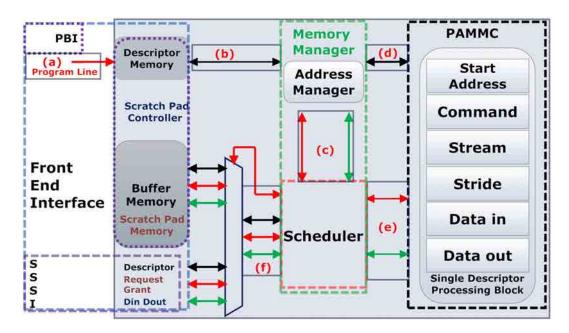

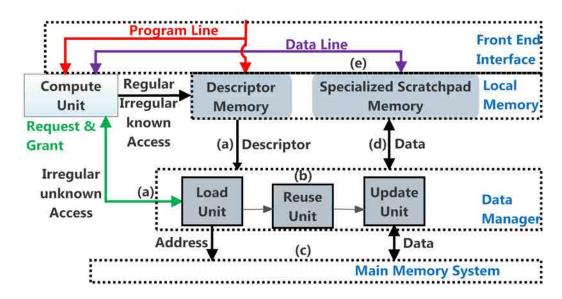

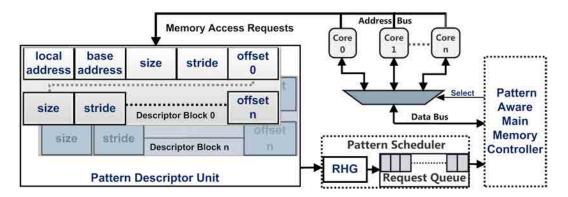

|    | 2.1  | Progra  | mmable Memory Controller Architecture                   | 32 |

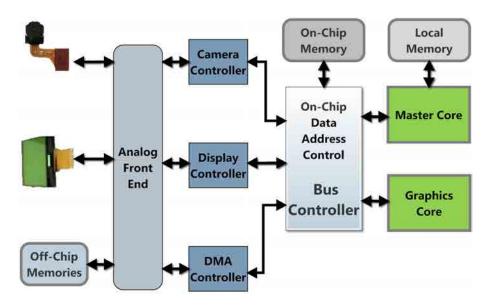

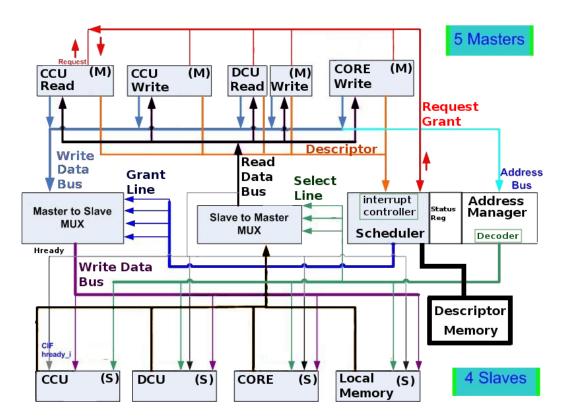

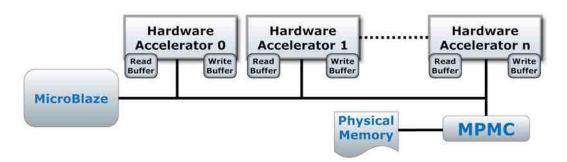

|    |      | 2.1.1   | Bus System                                              | 32 |

|    |      |         | 2.1.1.1 Front-End Interface                             | 32 |

|    |      |         | 2.1.1.2 On-Chip Bus System                              | 33 |

|    |      | 2.1.2   | Local Memory System                                     | 34 |

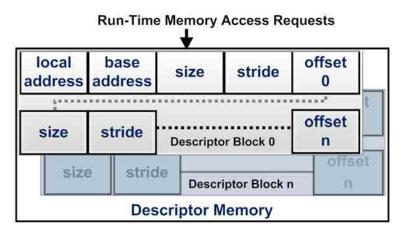

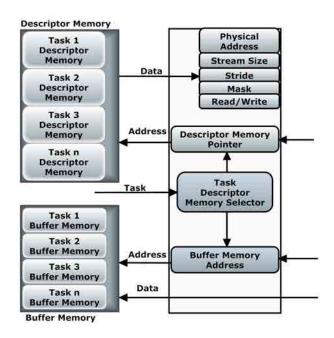

|    |      |         | 2.1.2.1 Descriptor Memory                               | 35 |

|    |      |         | 2.1.2.2 Buffer Memory                                   | 36 |

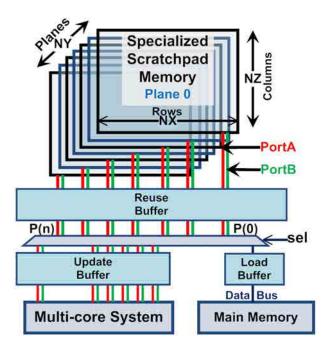

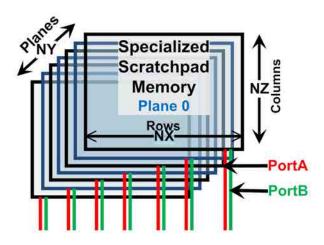

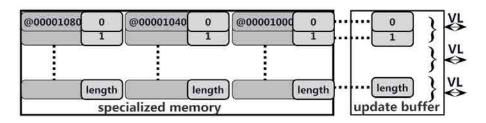

|    |      |         | 2.1.2.3 Specialized Scratchpad Memory                   | 36 |

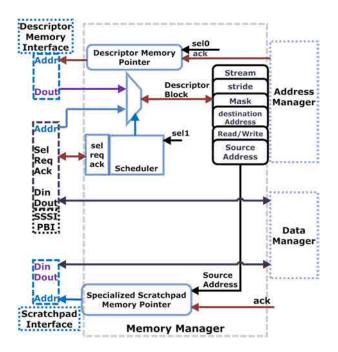

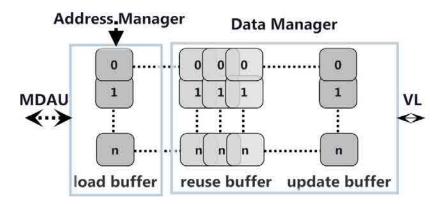

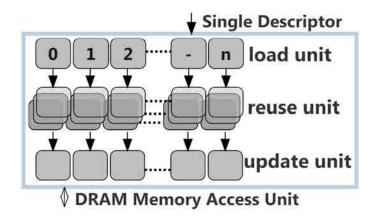

|    |      | 2.1.3   | Memory Manager                                          | 39 |

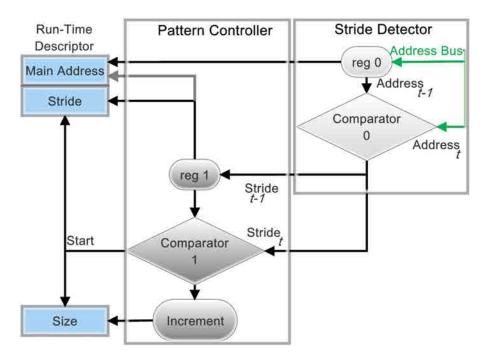

|    |      |         | 2.1.3.1 Address Manager                                 | 4( |

|    |      |         | 2.1.3.2 Data Manager                                    | 42 |

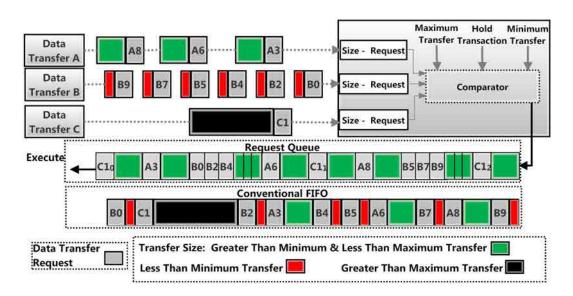

|    |      |         | 2.1.3.3 Scheduler                                       | 43 |

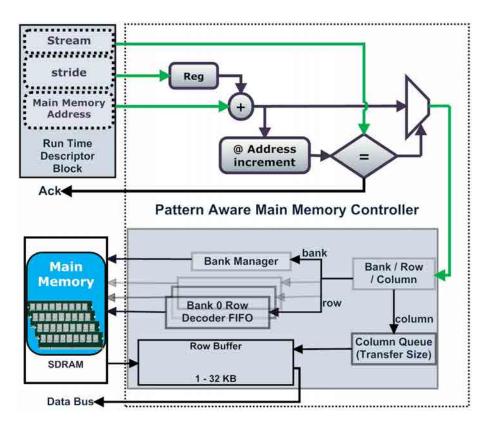

|    |      | 2.1.4   | Main Memory System                                      | 48 |

|    | 2.2  | Progra  | mming Model                                             | 50 |

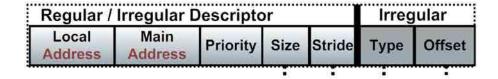

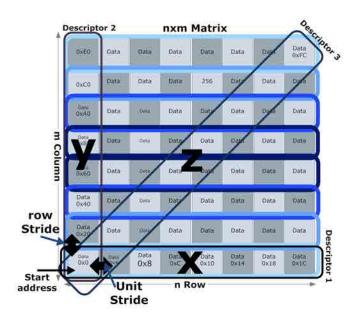

|    |      | 2.2.1   | Descriptors and Data Structures                         | 51 |

|    |      | 2.2.2   | Working Examples                                        | 53 |

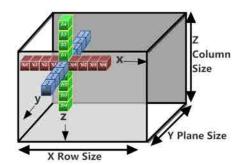

|    |      | 2.2.3   | Access Patterns                                         | 58 |

|    |      |         | 2.2.3.1 Vector Access Pattern                           | 58 |

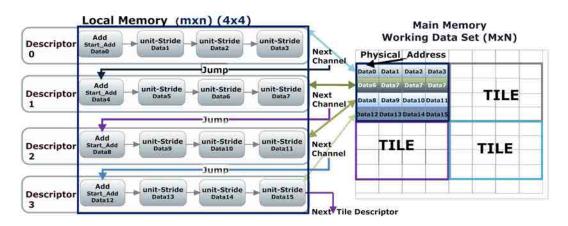

|    |      |         | 2.2.3.2 Tiling Access                                   | 60 |

|    |      | 2.2.4   | Programming PMC                                         | 6  |

|    |      |         |                                                         |    |

| II | U    | ni-coı  | re Memory System for Regular Data Pattern               | 65 |

| 3  | PPN  | /С: А Р | rogrammable Pattern Based Memory Controller             | 67 |

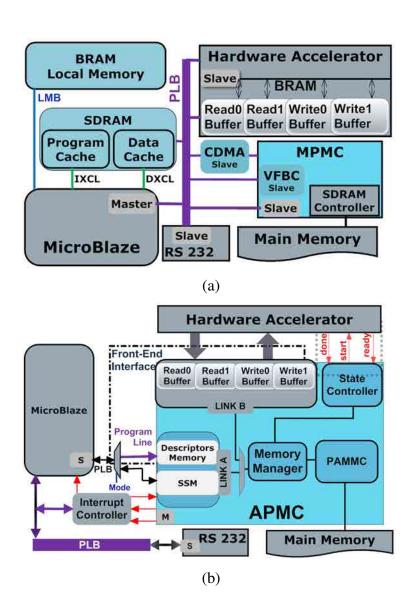

| -  |      |         | Architecture                                            | 68 |

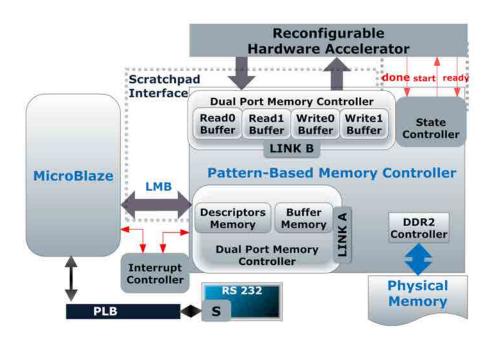

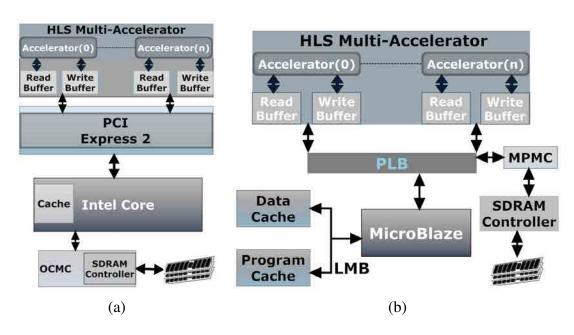

|   | 3.2  | Evalua  | tion Architecture                      |

|---|------|---------|----------------------------------------|

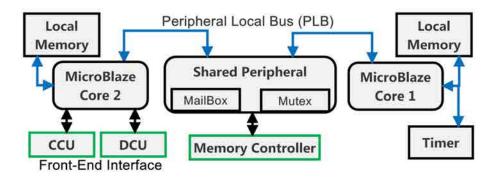

|   |      | 3.2.1   | MicroBlaze SSP                         |

|   |      | 3.2.2   | ROCCC ASHA                             |

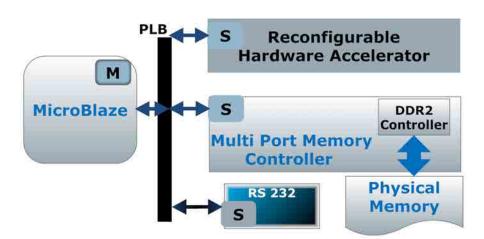

|   |      | 3.2.3   | PPMC based SoC                         |

|   |      | 3.2.4   | Baseline MPMC based SoC                |

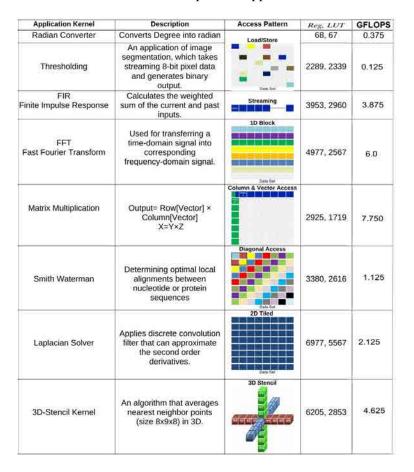

|   |      | 3.2.5   | Test Applications                      |

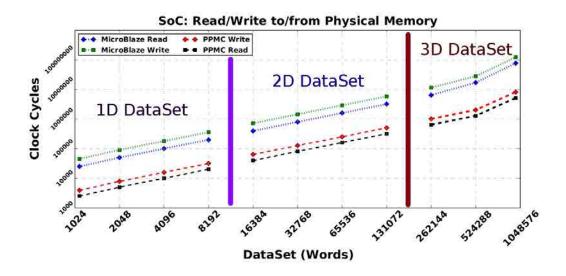

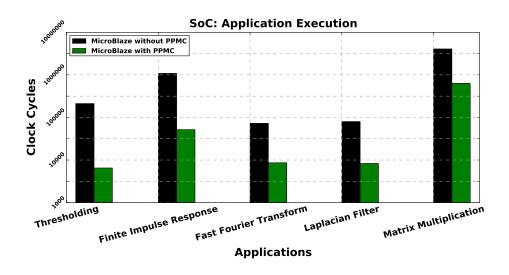

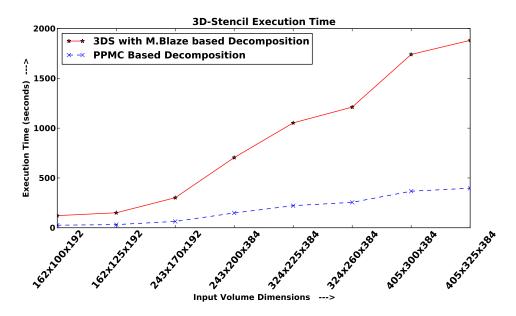

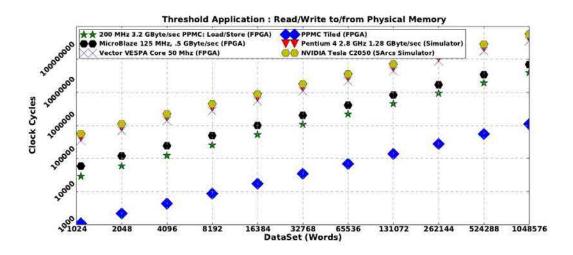

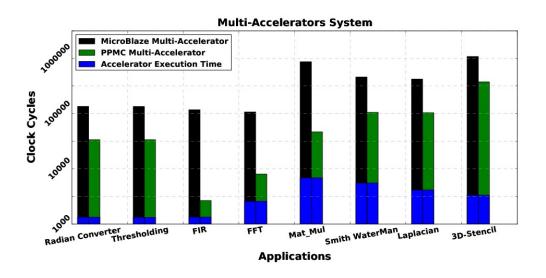

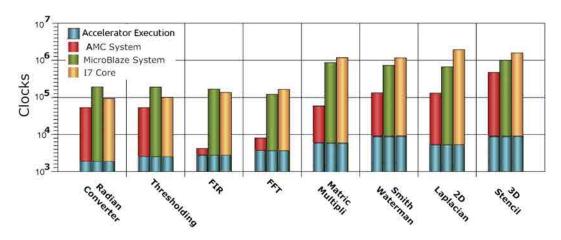

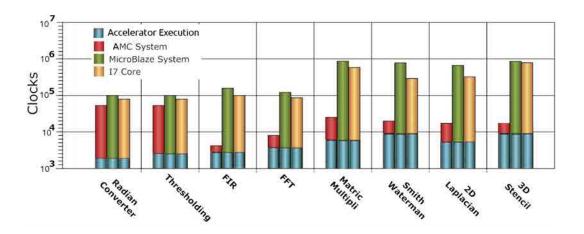

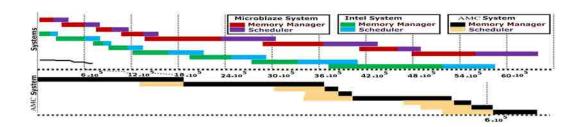

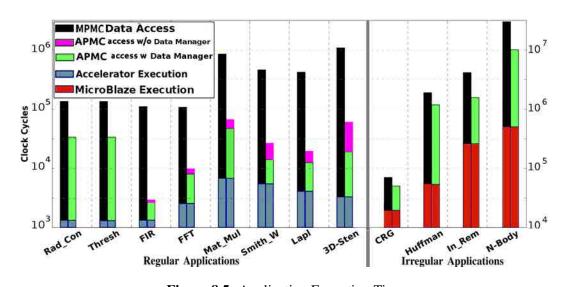

|   | 3.3  | Results | s and Discussion                       |

|   | 3.4  | Conclu  | sion                                   |

| 4 | A Bu | ıs Cont | roller for Graphics System 77          |

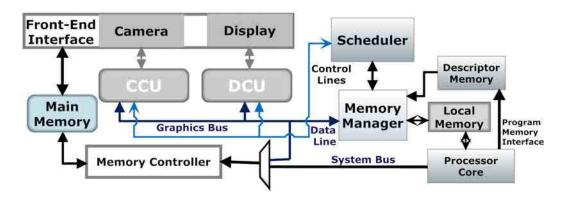

|   | 4.1  | PGC C   | Sraphics System Specification          |

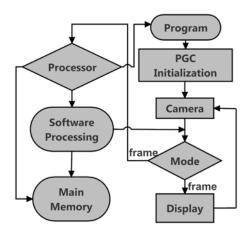

|   |      | 4.1.1   | Overview of PGC System                 |

|   |      | 4.1.2   | Processing Unit                        |

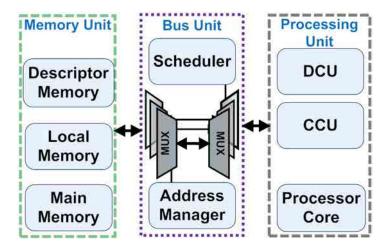

|   |      | 4.1.3   | Bus Unit                               |

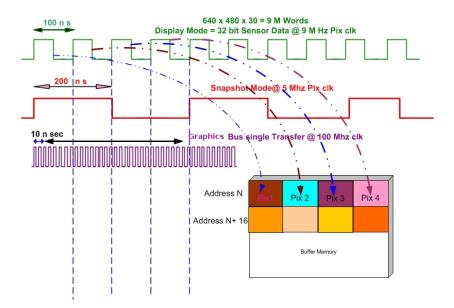

|   |      |         | 4.1.3.1 Bus Specification              |

|   |      |         | 4.1.3.2 Bus Control unit               |

|   |      |         | 4.1.3.3 Bus Interconnect               |

|   | 4.2  | Experi  | mental Framework                       |

|   |      | 4.2.1   | MicroBlaze based Graphics System       |

|   |      | 4.2.2   | PGC based Graphics System              |

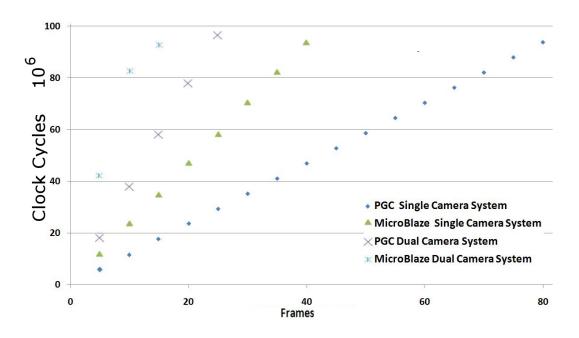

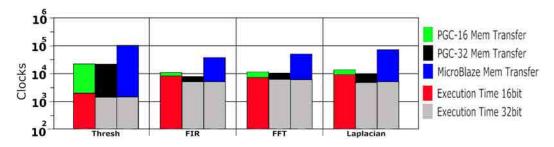

|   | 4.3  | Results | s and Discussion                       |

|   |      | 4.3.1   | Bus Performance                        |

|   |      |         | 4.3.1.1 Single-Camera Bus Bandwidth 91 |

|   |      |         | 4.3.1.2 Multi-Camera Bus Bandwidth 91  |

|   |      | 4.3.2   | Snapshot Mode Performance              |

|   |      | 4.3.3   | Applications Performance               |

|   |      | 4.3.4   | Power                                  |

|   | 4.4  | Conclu  | sion                                   |

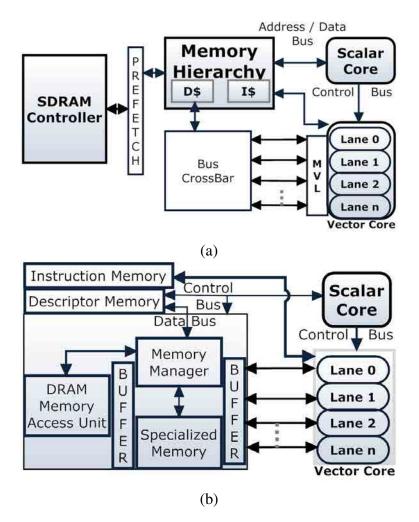

| 5 | PVN  | 1C: Pro | grammable Vector Memory Controller 95  |

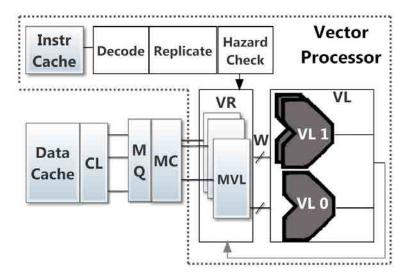

|   | 5.1  | Vector  | Processor                              |

|   | 5.2  | Progra  | mmable Vector Memory Controller        |

|   | 5.3  | PVMC    | Functionality                          |

|   |      | 5.3.1   | Memory Hierarchy                       |

|   |      | 5.3.2   | Address Registers                      |

|   |      | 5.3.3   | Main Memory Controller                 |

|   |      | 534     | Programming Vector Accesses 101        |

|         | 5.4                | Experi                                       | mental Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103                                                                              |

|---------|--------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|         |                    | 5.4.1                                        | The VESPA System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103                                                                              |

|         |                    |                                              | 5.4.1.1 SSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 103                                                                              |

|         |                    |                                              | 5.4.1.2 Vector Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | l 04                                                                             |

|         |                    |                                              | 5.4.1.3 Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | l 04                                                                             |

|         |                    | 5.4.2                                        | The Proposed PVMC System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                              |

|         |                    | 5.4.3                                        | The Baseline Nios System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                              |

|         |                    | 5.4.4                                        | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106                                                                              |

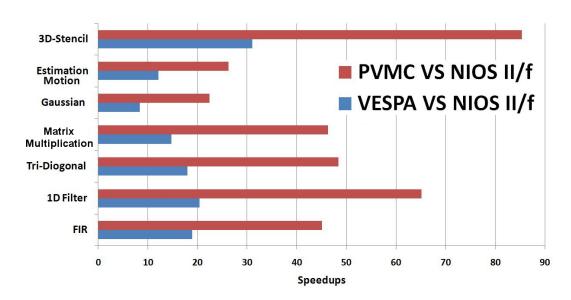

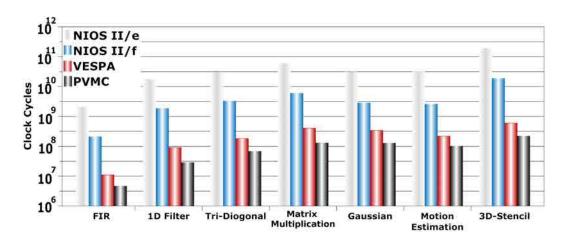

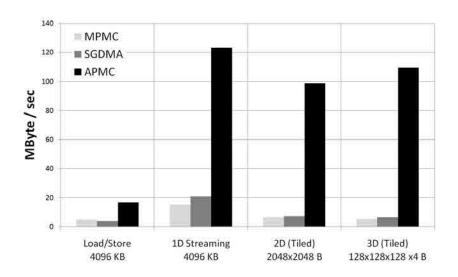

|         | 5.5                | Results                                      | s and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106                                                                              |

|         |                    | 5.5.1                                        | Memory & Bus System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 106                                                                              |

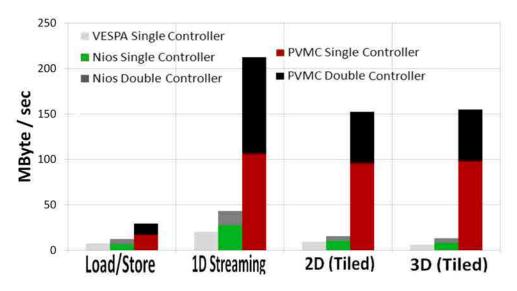

|         |                    | 5.5.2                                        | Performance Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108                                                                              |

|         |                    | 5.5.3                                        | Dynamic Power & Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110                                                                              |

|         |                    | 5.5.4                                        | Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111                                                                              |

|         | 5.6                | Conclu                                       | asion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113                                                                              |

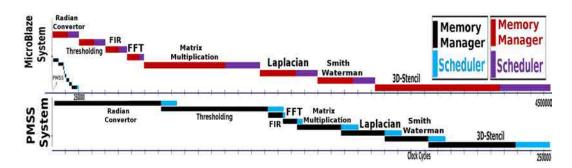

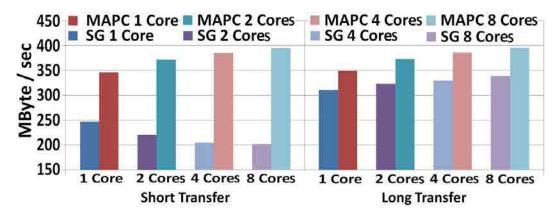

| IJ      | I N                | Multi-                                       | core Memory System for Regular Data Pattern 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                               |

| II<br>6 |                    |                                              | core Memory System for Regular Data Pattern 1  Programmable Memory System and Scheduler for Complex Memory                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                                                               |

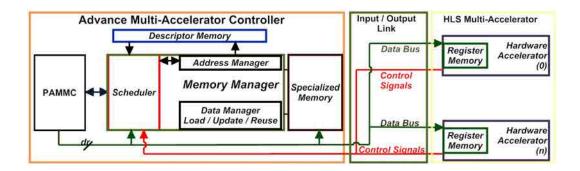

|         |                    | SS: A P                                      | Programmable Memory System and Scheduler for Complex Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15<br>117                                                                        |

|         | PMS                | SS: A P                                      | Programmable Memory System and Scheduler for Complex Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117                                                                              |

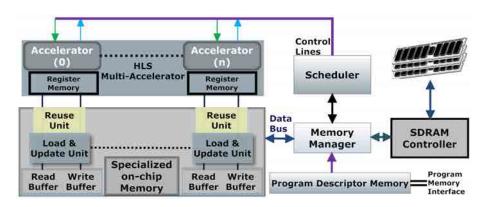

|         | PMS<br>Patt        | SS: A P                                      | Programmable Memory System and Scheduler for Complex Memory  1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 <b>17</b><br>119                                                               |

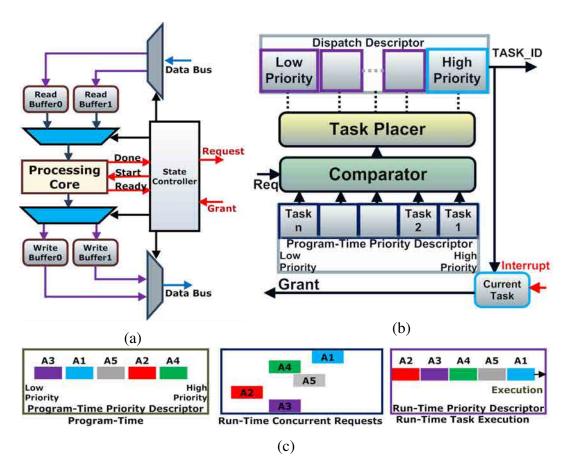

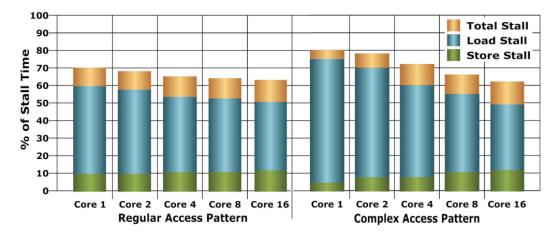

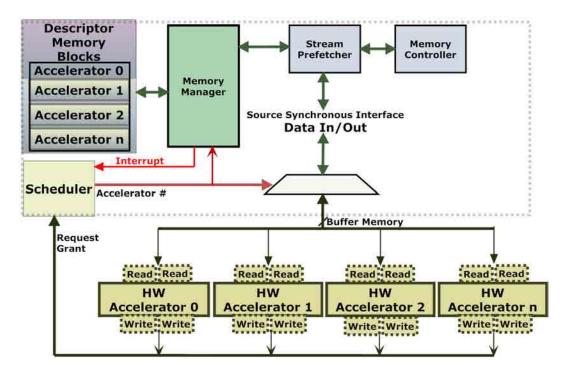

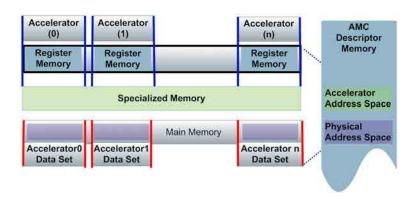

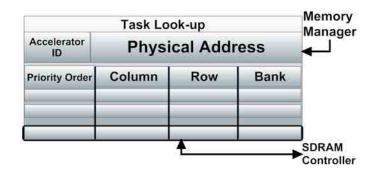

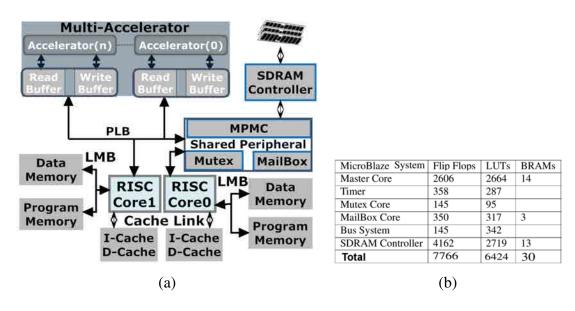

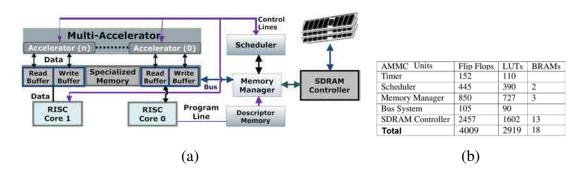

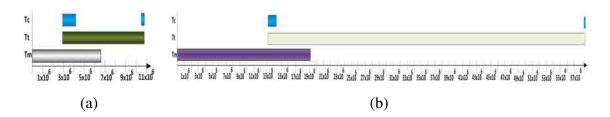

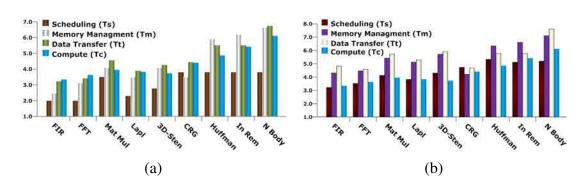

|         | PMS<br>Patt        | SS: A P<br>erns<br>PMSS                      | Programmable Memory System and Scheduler for Complex Memory  Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 <b>17</b><br>119<br>120                                                        |

|         | PMS<br>Patt        | SS: A P<br>erns<br>PMSS                      | Programmable Memory System and Scheduler for Complex Memory  Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 <b>17</b><br>119<br>120                                                        |

|         | PMS<br>Patt        | SS: A P<br>erns<br>PMSS                      | Programmable Memory System and Scheduler for Complex Memory           1           Architecture         1           Memory Manager         1           6.1.1.1         Scheduling                                                                                                                                                                                                                                                                                                                               | 117<br>119<br>120<br>121                                                         |

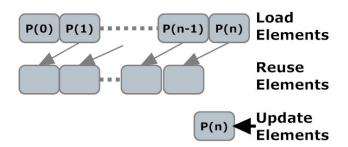

|         | PMS<br>Patt        | SS: A P<br>erns<br>PMSS                      | Programmable Memory System and Scheduler for Complex Memory           1           Architecture         1           Memory Manager         1           6.1.1.1         Scheduling         1           6.1.1.2         Memory Organization         1                                                                                                                                                                                                                                                             | 117<br>119<br>120<br>121<br>122                                                  |