**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

MareNostrum, the name of "our" supercomputer, means literally "our sea". It was a Roman name for the Mediterranean Sea on which Barcelona is a port.

Ancient Roman Ship

## Optimizing programming models for massively parallel computers

By Montse Farreras

Advisor:

Toni Cortés

A dissertation submitted in partial fulfillment of the requirements for the degree of:

Doctor per la Universitat Politècnica de Catalunya Barcelona (Spain) 2008

All rights reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author.

### ACTA DE QUALIFICACIÓ DE LA TESI DOCTORAL

Reunit el tribunal integrat pels sota signants per jutjar la tesi doctoral: Titol de la tesi: Optimizing programming models for massively parallel computers ....... Autor de la tesi: Montse Farreras Esclusa..... Acorda atorgar la qualificació de: ■ No apte □ Aprovat Notable Excel·lent □ Excel·lent Cum Laude El President El Secretari (nom | cognoms) (nom | cognoms) El vocal El vocal El vocal (nom | cognoms) (nom | cognoms) (nom | cognoms)

(nom I cognoms)

### **Abstract**

Since the invention of the transistor, clock frequency increase was the primary method of improving computing performance. As the reach of Moore's law came to an end, however, technology driven performance gains became increasingly harder to achieve, and the research community was forced to come up with innovative system architectures. Today increasing parallelism is the primary method of improving performance: single processors are being replaced by multiprocessor systems and multicore architectures.

The challenge faced by computer architects is to increase performance while limited by cost and power consumption. The appearance of cheap and fast interconnection networks has promoted designs based on distributed memory computing. Most modern massively parallel computers, as reflected by the Top 500 list, are clusters of workstations using commodity processors connected by high speed interconnects.

Today's massively parallel systems consist of hundreds of thousands of processors. Software technology to program these large systems is still in its infancy. Optimizing communication has become a key to overall system performance. To cope with the increasing burden of communication, the following methods have been explored:

- (i) Scalability in the messaging system: The messaging system itself needs to scale up to the 100K processor range.

- (ii) Scalable algorithms reducing communication: As the machine grows in size the amount of communication also increases, and the resulting overhead negatively impacts performance. New programming models and algorithms allow programmers to better exploit locality and reduce communication.

- (iii) Speed up communication: reducing and hiding communication latency, and improving bandwidth.

Following the three items described above, this thesis contributes to the improvement of the communication system (i) by proposing a scalable memory management of the communication system, that guarantees the correct reception of data and control-data, (ii) by proposing a language extension that allows programmers to better exploit data locality to reduce inter-node communication, and (iii) by presenting and evaluating a

cache of remote addresses that aims to reduce control-data and exploit the RDMA native network capabilities, resulting in latency reduction and better overlap of communication and computation.

Our contributions are analyzed in two different parallel programming models: Message Passing Interface (MPI) and Unified Parallel C (UPC). Many different programing models exist today, and the programmer usually needs to choose one or another depending on the problem and the machine architecture. MPI has been chosen because it is the de facto standard for parallel programming in distributed memory machines. UPC was considered because it constitutes a promising easy-to-use approach to parallelism. Since parallelism is everywhere, programmability is becoming important and languages such as UPC are gaining attention as a potential future of high performance computing.

Concerning the communication system, the languages chosen are relevant because, while MPI offers two-sided communication, UPC relays on a one-sided communication model. This difference potentially influences the communication system requirements of the language. These requirements as well as our contributions are analyzed and discussed for both programming models and we state whether they apply to both programming models. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>This work has been partially supported by the Ministry of Science and Technology of Spain and the European Union (FEDER funds) under contract TIC2001-0995-C02-01, TIN2004-07739-C02-01 and TIN2007-60625, and by the BSC-IBM collaboration agreement SoW Scalability for BGL. I acknowledge the European Center for Parallelism of Barcelona (CEPBA), the Barcelona Supercomputing Center (BSC), the Lawrence Livermore National Laboratory, the IBM Poughkeepsie Benchmarking Center and the IBM Research T.J. Watson for supplying the computing resources for the experiments presented in this thesis.

### **Agraiments**

Cap al Febrer del 2002, vaig iniciar una experiència que poc em pensava que tingués un impacte tan gran en la meva vida. Aquests anys de formació com investigadora han sigut una experiència molt enriquidora, tan des del punt de vista professional com personal.

Durant aquests gairebé 7 anys, he tingut el plaer de conèixer moltíssimes persones i cadascuna d'elles m'ha aportat alguna cosa, la llista de persones a qui m'agradaria donar les gràcies és tan llarga que em caldria tot un annex a la tesis, i com sempre escric això amb presses així que si em descuido algú no m'ho tingueu en compte.

En primer lloc el meu *advisor*, el Toni Cortés, que ha resistit en tot moment al meu costat a les verdes i a les madures. Li vull agrair el suport que m'ha donat, el guiar-me quan m'he encallat i la confiança que m'ha demostrat. I sobretot el que més m'ha ajudat: el seu optimisme i bon humor.

També vull mencionar el Jesus Labarta i l'Eduard Ayguadé, per l'experiència que m'han transmès, i pels seus comentaris en diferents etapes de la tesis que m'han ajudat a millorar-la. I al Xavier Martorell per la seva disposició a ajudar en tot moment i pel seu suport tècnic i logístic.

En segon lloc el George Almasi i el Calin Cascaval amb qui he treballat els darrers quatre estius durant les meves estades a IBM T.J. Watson. Són els investigadors més brillants que he conegut fins al moment i també unes grans persones. D'ells he après molt i són un gran estímul professional per continuar fent recerca.

Tot l'equip de IBM T.J. Watson mereix una menció, per omplir de bones vivències els meus estius a Yorktown Heights i pels seus bons consells: Jose B., Jose C i sobretot a Gabor, a qui també vull agrair les correccions. També l'equip amb qui he colŢlaborat de IBM Toronto, Kit, Philip i Ettore.

En tercer lloc tots els companys i amics que he fet al departament, la llista és molt llarga. Els companys de doctorat des dels inicis de la sala CEPBA: Juanjo, Alex, també Rogeli, Raul i Vicenç. Els companys d'aventures: Carles, Jesus. El meu company d'assignatura: Pau Bofill un exemple a seguir. Les meves companyes: Ana, Yolanda i

Marta. Al Pau per les converses i cafès. Els companys de Parallel Models: Jordi, Javi, Xavi i Roger. Els administradors de sistemes tant del DAC com del BSC. I totes aquelles persones amb qui he compartit el menjador, festes, esmorzars o bons moments en general.

Especialmet vull remarcar el David, el meu *roomie* amb qui he compartit més hores que ningú, sempre disposat a donar un cop de mà a les 7h del matí si cal, *a on no arriba un roomie* ..., i que m'ha marcat clarament el camí cap al final de la tesis.

En quart lloc, la meva família, per què malgrat tot és la millor família del món. I a tots els meus amics que sort n'he tingut.

I per últim vull dedicar la tesis a la persona més especial de la meva vida: al Sergi, a ell vull agrair tots els bons moments que hem compartit però també la paciència que ha tingut per haver viscut molt d'aprop tot l'esforç que he dedicat a aquesta tesis.

### Acknowledgements

In February 2002, I took a challenge that has had an impact in my life: undertake a PhD in Computer Science. These years of research training have provided me with an intellectually enriching experience, from both professional and personal point of view.

Along the last seven years, I have had the pleasure to meet many people, each of them has brought some novelty and good to my life. The list of people whom I would like to thank is such a long one that I would need to add a new annex to the thesis, and as usual I rush so please do not get upset with me if I am forgetting someone.

First of all, my *advisor*, professor Toni Cortés. He has held out at my side for the good and the bad times. I am grateful to him for his support, for his guidance when I was blocked, and for his faith in me. And specially, his optimism and sense of humor have been really helpful.

I would also like to mention Jesus Labarta and Eduard Ayguadé. They have imparted their experience, and given me remarks at different stages of the development of this thesis that have improved it. Also thanks to Xavi Martorell, who has always been ready to help me with any kind of technical or logistic support.

Secondly, I have been working for the last four years during my summer internships with George Almasi and Calin Cascaval. They are the most brilliant researchers I have met so far and also very kind people. I have learned a lot from them and they inspire and encourage me to keep doing research. Thanks for your time and dedication.

The whole team at IBM T.J. Watson deserves a place here, to fill up my summers in Yorktown Heights with very nice memories and to give me good advices: Jose B., Jose C and specially Gabor, of whom I appreciate his reviews. I have also been collaborating with the compiler team in IBM Toronto: Kit, Philip and Ettore.

Thirdly, I want to mention all my department colleagues and the list is long. My PhD mates from the very beginning at the CEPBA room: Juanjo, Alex, also Rogeli, Raul and Vicenç. My adventure buddies: Carles and Jesus. My workmate in the classroom: Pau Bofill, who is a role model. My girlfriends: Ana, Yolanda and Marta. My classmate Pau for the nice coffee breaks. My teammates: Jordi, Javi, Xavi i Roger. The system

administrators, from DAC and from BSC. And all the people whom I have shared beautiful moments, breakfast, lunch, dinner or parties.

I would like to emphasize David, my official *roomie*, with whom I have shared more office hours than with anybody else. He is always ready to lend a hand, even at 7am in the morning: *a on no arriba un roomie*.... He has show me the way to graduation.

Fourthly, my family, despite of the difficulties, they are the best possible family in the world. And all my friends, I am very happy to count on them.

And finally, I would like to dedicate this thesis to the most special person in my life: Sergi. I thank him for all the great time we have spent together and I also appreciate his patience because he has followed my efforts on this work closely.

# **Contents**

| Al | bstrac  | et             |                                                    |      |

|----|---------|----------------|----------------------------------------------------|------|

| Ą  | graïm   | ents           |                                                    | •    |

| A  | cknov   | vledgme        | ents                                               | ix   |

| Ta | ble of  | f conten       | its                                                | XV   |

| Li | st of l | Figures        |                                                    | XX   |

| Li | st of [ | <b>Fables</b>  |                                                    | xxii |

| 1  | Intr    | oductio        | n                                                  | 1    |

|    | 1.1     | Introd         | uction                                             | 3    |

|    |         | 1.1.1          | Future trends in High Performance Computing        | 3    |

|    |         | 1.1.2          | Programming trends in HPC                          | 4    |

|    | 1.2     | Global         | I picture                                          | Ģ    |

|    | 1.3     | Contri         | butions                                            | 10   |

|    |         | 1.3.1<br>1.3.2 | Scale up the communication memory management       | 11   |

|    |         | 1.3.3          | munication                                         | 12   |

|    |         |                | languages                                          | 14   |

|    | 1.4     | Thesis         | Organization                                       | 15   |

| 2  | Rela    | ited Wo        | rk                                                 | 17   |

|    | 2.1     | Paralle        | el programming models                              | 19   |

|    |         | 2.1.1          | MPI                                                | 19   |

|    |         | 2.1.2          | UPC                                                | 20   |

|    | 2.2     | Impro          | ving memory management in the communication system | 21   |

|    |         | 2.2.1          | Communication Patterns Prediction                  | 21   |

|    |         | 2.2.2          | Memory management in the communication system      | 22   |

|    | 2.3     | Extend         | ling the language to reduce communication          | 24   |

|    |         | 2.3.1          | Scalability                                        | 24   |

|             | 2.3.2                                    | Reducing communication                                        |

|-------------|------------------------------------------|---------------------------------------------------------------|

| 2.4         | Speed                                    | up communication                                              |

|             | 2.4.1                                    | Optimizing data transfer                                      |

|             | 2.4.2                                    | Remote Address Cache                                          |

| Pred        | liction t                                | o scale up the communication system memory management         |

| 3.1         | Introdu                                  | action                                                        |

| 3.2         | Explor                                   | ing the predictability of MPI messages                        |

|             | 3.2.1                                    | Experimental framework                                        |

|             | 3.2.2                                    | Predictor design                                              |

|             | 3.2.3                                    | Evaluation of the MPI message predictability                  |

| 3.3         | Toward                                   | ds a zero-copy mechanism by predicting buffer addresses       |

|             | 3.3.1                                    | Our zero message-copying approach                             |

|             | 3.3.2                                    | Evaluation                                                    |

| 3.4         | Predict                                  | tability to improve the memory management                     |

|             | 3.4.1                                    | The prediction mechanism                                      |

|             | 3.4.2                                    | The rendezvous protocol                                       |

|             | 3.4.3                                    | Evaluation                                                    |

| 3.5         | Conclu                                   | isions                                                        |

|             | 3.5.1                                    | Our Prediction mechanism in UPC                               |

| Con         | trol flov                                | v for control data                                            |

| 4.1         |                                          | action                                                        |

| 4.2         |                                          | work                                                          |

|             | 4.2.1                                    | BlueGene/L                                                    |

|             | 4.2.2                                    | MPI on BG/L                                                   |

| 4.3         | The pr                                   | oposed memory management algorithm                            |

|             | 4.3.1                                    | High level overview of algorithm                              |

|             | 4.3.2                                    | Data structures                                               |

|             | 4.3.3                                    | Detailed description                                          |

|             | 4.3.4                                    | Deadlock issues                                               |

| 4.4         | Evalua                                   | tion                                                          |

|             | 4.4.1                                    | The killer microbenchmark                                     |

|             | 4.4.2                                    | NAS benchmarks                                                |

| 4.5         | Conclu                                   | isions                                                        |

|             | 4.5.1                                    | Our Memory management protocol in UPC                         |

| Mul         | tidimen                                  | sional blocking: a language extension to reduce communication |

|             |                                          | action                                                        |

|             |                                          | Memory Programming for Large Scale Machines                   |

| J. <u>_</u> |                                          | UPC programming model considerations                          |

|             |                                          | The Runtime System                                            |

|             |                                          | Optimizations                                                 |

|             | Pred 3.1 3.2 3.3 3.4 3.5 Con 4.1 4.2 4.3 | 2.4 Speed                                                     |

|    |        | 5.2.4    | Evaluation                                                | 99  |

|----|--------|----------|-----------------------------------------------------------|-----|

|    |        | 5.2.5    | Summary                                                   | 105 |

|    | 5.3    | Multid   | limensional blocking in UPC                               | 105 |

|    |        | 5.3.1    | Multidimensional Blocking of UPC arrays                   | 106 |

|    |        | 5.3.2    | UPC RTS Implementation Issues                             |     |

|    |        | 5.3.3    | Locality Analysis                                         |     |

|    |        | 5.3.4    | Evaluation                                                | 113 |

|    | 5.4    | Conclu   | usions                                                    | 120 |

|    |        | 5.4.1    | Data layout in MPI                                        |     |

| 6  | Rem    | ote Ad   | dress Cache: Scalable RDMA performance for PGAS languages | 123 |

|    | 6.1    | Introdu  | uction                                                    | 125 |

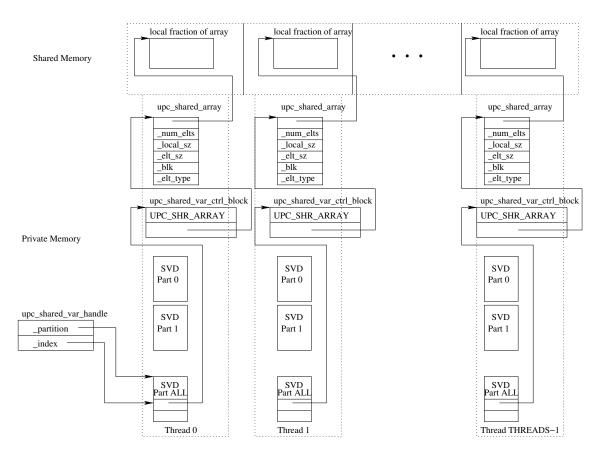

|    | 6.2    | The IB   | BM XLUPC runtime                                          | 126 |

|    |        | 6.2.1    | The Shared Variable Directory                             | 127 |

|    |        | 6.2.2    | The performance compromise of the SVD design              | 128 |

|    | 6.3    | Remot    | te Address Cache                                          | 129 |

|    |        | 6.3.1    | Considerations for a LAPI based implementation            | 132 |

|    |        | 6.3.2    | Considerations for the Myrinet/GM implementation          | 132 |

|    |        | 6.3.3    | Memory Registration Issues                                | 134 |

|    |        | 6.3.4    | Pin-everything registration strategy                      | 137 |

|    |        | 6.3.5    | Chunk-based Pin on-demand registration strategie          | 138 |

|    | 6.4    | Evalua   | ntion                                                     | 141 |

|    |        | 6.4.1    | Evaluation environment: MareNostrum                       | 141 |

|    |        | 6.4.2    | Evaluation environment: Power5 cluster                    | 142 |

|    |        | 6.4.3    | Microbenchmarks                                           | 142 |

|    |        | 6.4.4    | DIS Stressmark Suite                                      | 144 |

|    |        | 6.4.5    | Cache size considerations                                 | 145 |

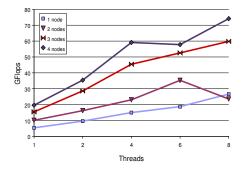

|    |        | 6.4.6    | Stressmark evaluation on MareNostrum                      | 147 |

|    |        | 6.4.7    | Stressmark evaluation on Power5 cluster                   | 149 |

|    | 6.5    | Conclu   | usions and future work                                    | 154 |

|    |        | 6.5.1    | MPI                                                       | 155 |

| 7  | Con    | clusions | s and Future Work                                         | 157 |

|    | 7.1    | Conclu   | asions                                                    | 159 |

|    |        | 7.1.1    | Improving memory management in the communication system   | 159 |

|    |        | 7.1.2    | Extending the language to reduce communication            |     |

|    |        | 7.1.3    | Caching the final address to speed up communication       |     |

|    |        | 7.1.4    | MPI and UPC                                               | 163 |

|    | 7.2    |          | Work                                                      |     |

|    |        | 7.2.1    | Shortcomings                                              | 165 |

|    |        | 7.2.2    | Future research directions                                | 166 |

| Bi | bliogr | aphy     |                                                           | 171 |

| A | App         | endix 1 | : Architectures         | 191   |

|---|-------------|---------|-------------------------|-------|

|   | <b>A.</b> 1 | Cluster | rs                      | . 192 |

|   |             | A.1.1   | IBM RS-6000 SP2         | . 192 |

|   |             | A.1.2   | IBM Squadron cluster    | . 192 |

|   |             | A.1.3   | 28-node IBM cluster     | . 192 |

|   | A.2         | Massiv  | vely Parallel Computers | . 192 |

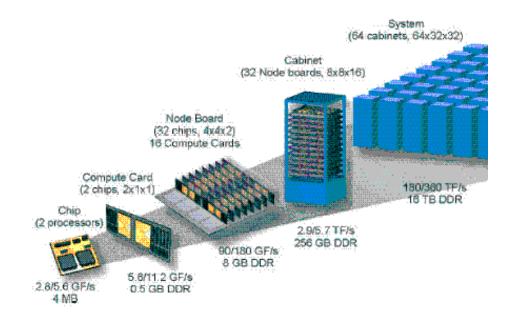

|   |             | A.2.1   | BlueGene/L              | . 192 |

|   |             | A.2.2   | MareNostrum             | . 194 |

CONTENTS xvii

# **List of Figures**

| 1.1  | Global Picture of our thesis                                              | 9  |

|------|---------------------------------------------------------------------------|----|

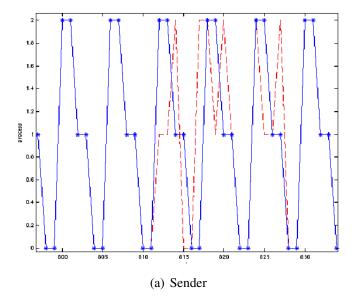

| 3.1  | Tracing Points for Logical and Physical communication                     | 33 |

| 3.2  | Communication pattern NAS BT                                              | 35 |

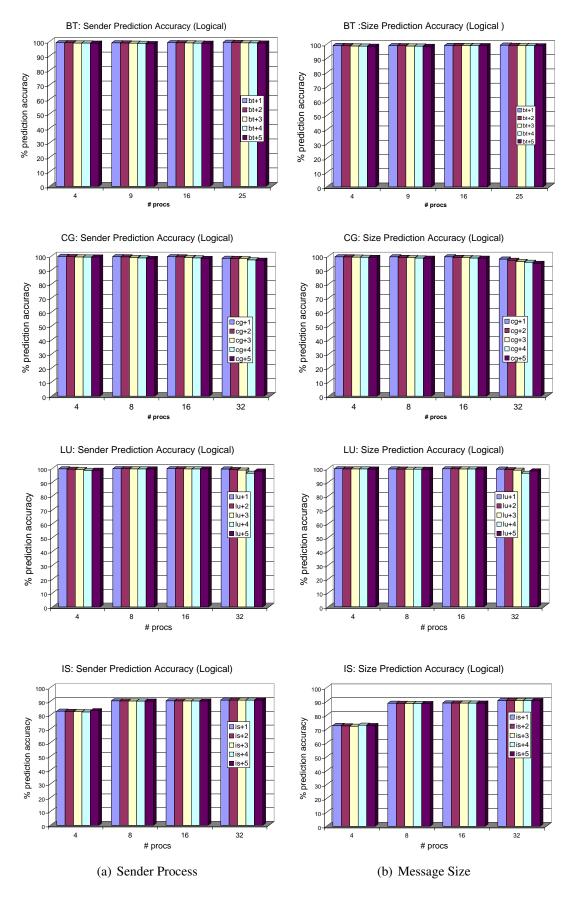

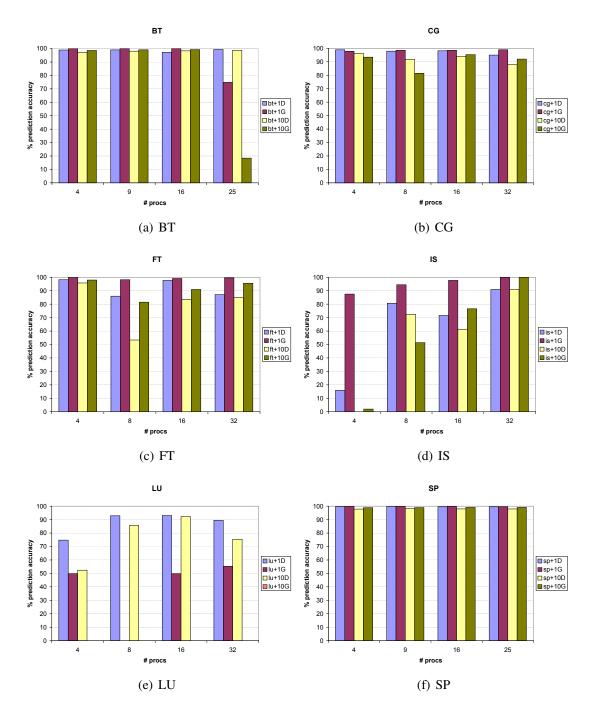

| 3.3  | Logical MPI Communication Prediction Accuracy in Class A NAS Benchmarks   | 38 |

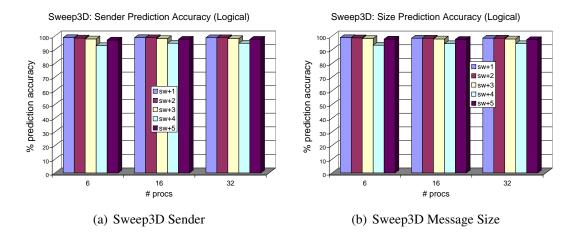

| 3.4  | Logical MPI Communication Prediction Accuracy in Sweep3D ASCI Benchmark   | 39 |

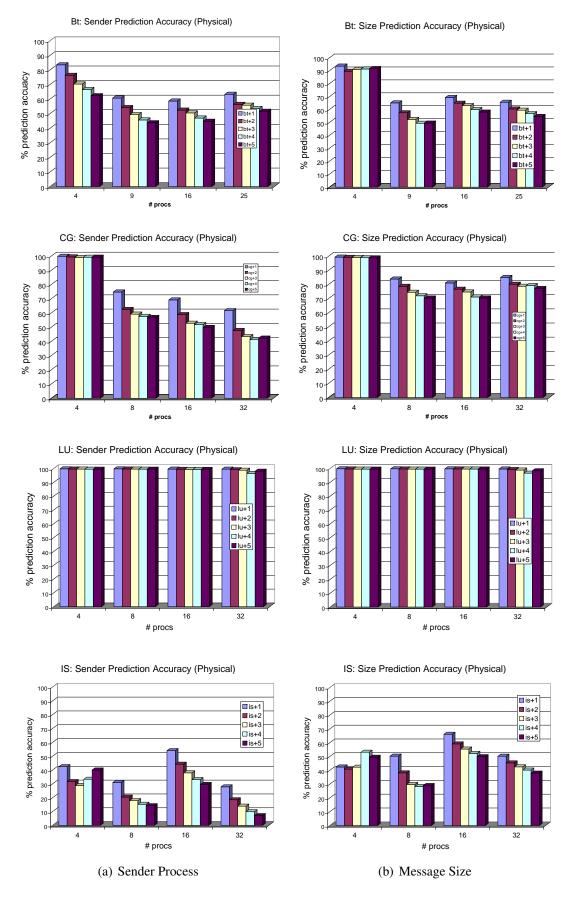

| 3.5  | Physical MPI Communication Prediction Accuracy in Class A NAS Benchmarks  | 40 |

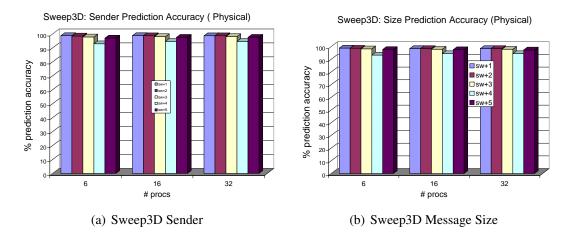

| 3.6  | Physical MPI Communication Prediction Accuracy in Sweep3D ASCI            | 41 |

| 3.7  | Benchmark                                                                 | 41 |

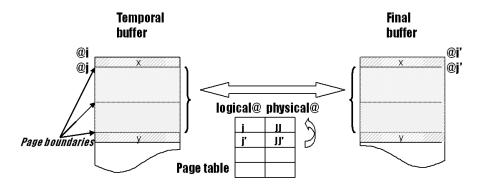

| 3.8  | Zero message-copying approach                                             | 43 |

| 3.9  | Long-term buffer address and message size prediction rates                | 47 |

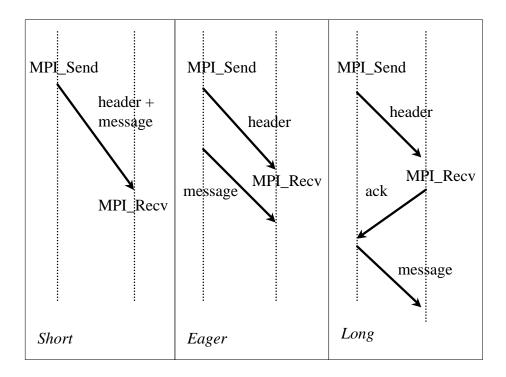

|      | MPICH 1.2.4 Protocols depending on message size                           | 49 |

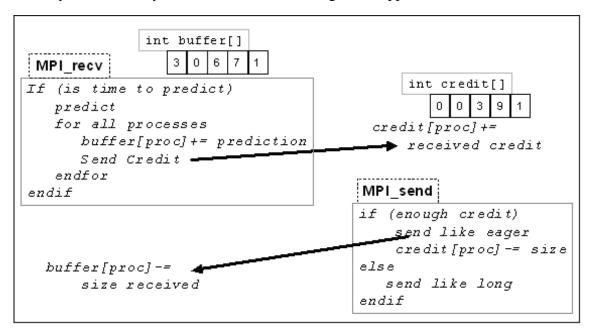

|      | Prediction Mechanism                                                      | 50 |

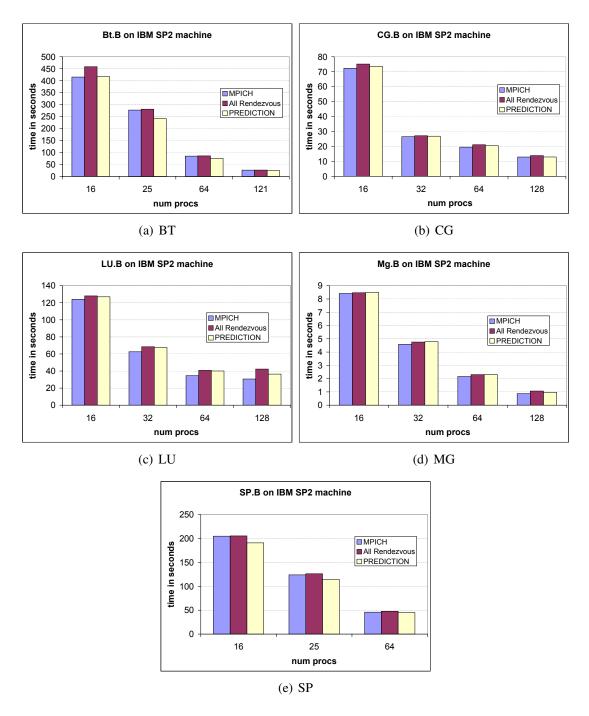

|      | Performance evaluation of prediction mechanism IBM RS6000                 | 54 |

|      | Performance benefit of prediction mechanism IBM RS6000                    | 55 |

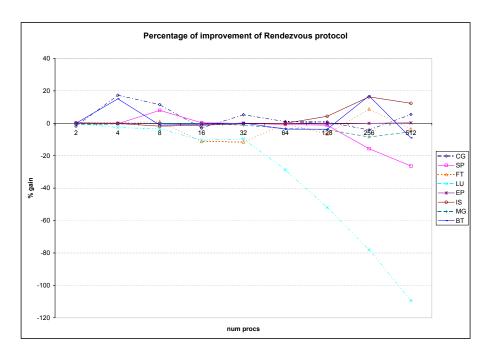

| 3.14 | Performance evaluation of rendezvous protocol in MareNostrum              | 57 |

| 3.15 | Performance benefit of rendezvous protocol in MareNostrum                 | 58 |

| 3.16 | Performance evaluation of rendezvous protocol in BG/L                     | 60 |

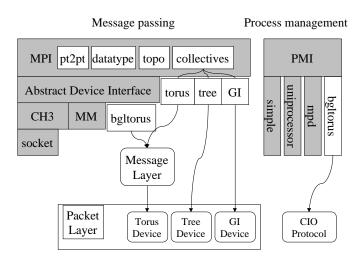

| 4.1  | The BlueGene/L MPI architecture                                           | 68 |

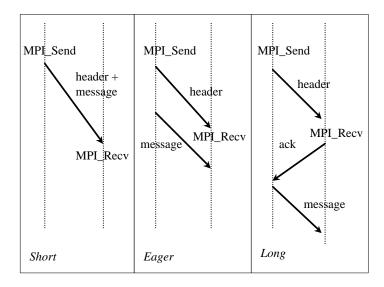

| 4.2  | MPI Protocols.                                                            | 69 |

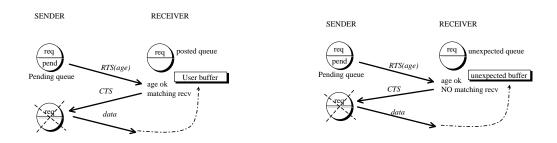

| 4.3  | Age OK and matching MPI_recv                                              | 73 |

| 4.4  | Age OK, no matching MPI_recv and enough memory                            | 73 |

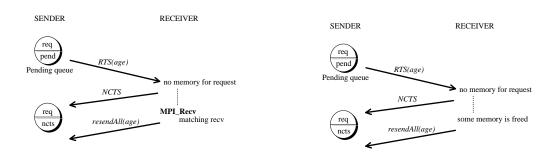

| 4.5  | Age NOT OK and no matching MPI_recv                                       | 74 |

| 4.6  | Age NOT OK and matching MPI_recv                                          | 74 |

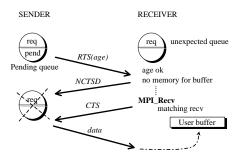

| 4.7  | Enough memory for request but NOT for the buffer: delay data transmission | 74 |

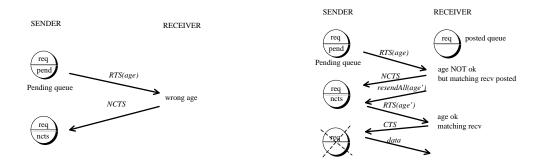

| 4.8  | Not enough memory for request on receiver's side                          | 75 |

| 4.9  | Some memory is freed                                                      | 75 |

| 4.10 | Killer benchmark structure                                                | 77 |

XX LIST OF FIGURES

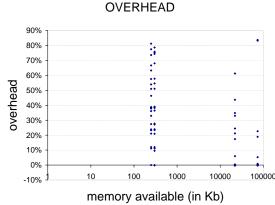

| 4.11                                | Overhead when memory management protocol is activated                             | 77  |

|-------------------------------------|-----------------------------------------------------------------------------------|-----|

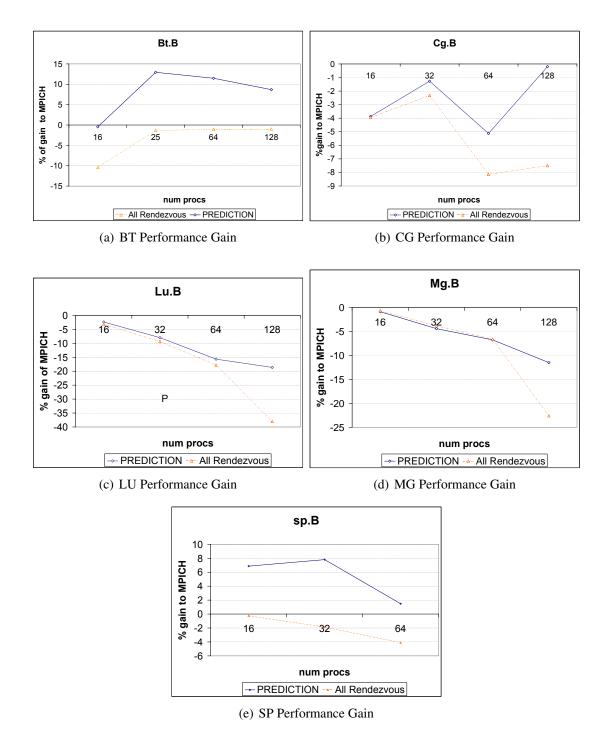

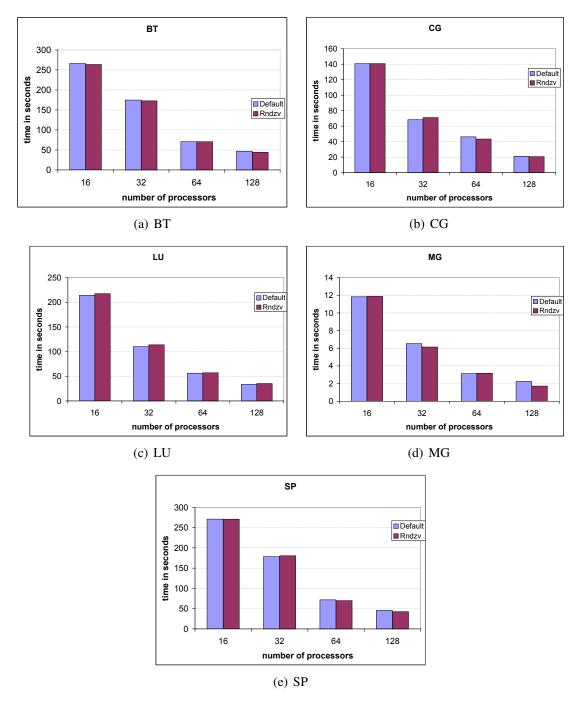

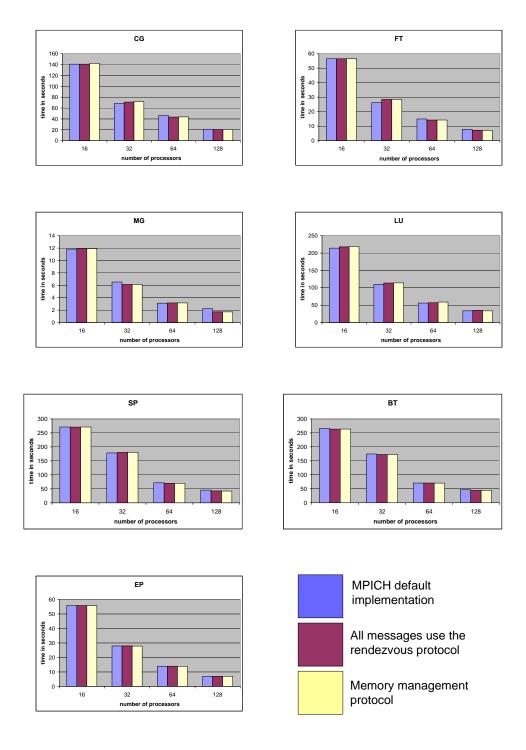

| 4.12                                | NAS Benchmarks evaluation                                                         | 79  |

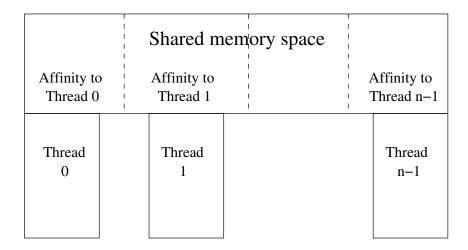

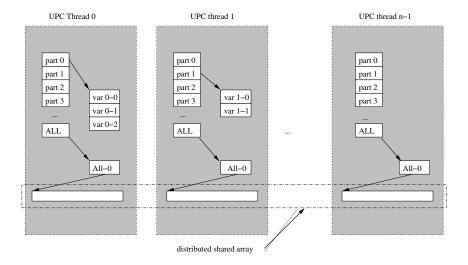

| 5.1                                 | UPC Memory View                                                                   | 88  |

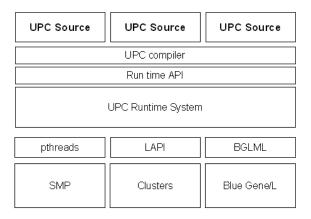

| 5.2                                 | XL UPC Compiler and Runtime System                                                | 88  |

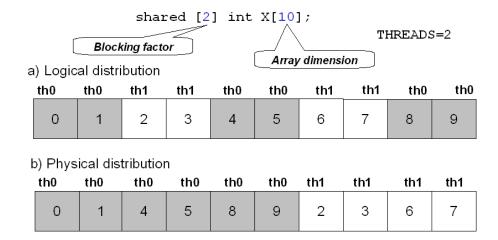

| 5.3                                 | Example of UPC Array distribution                                                 | 89  |

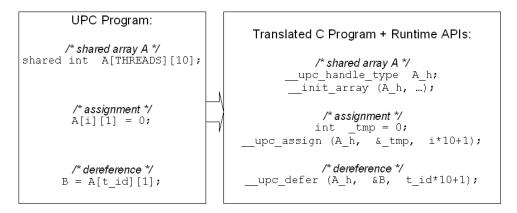

| 5.4                                 | Example of UPC source code and its correspondent C code with the added            |     |

|                                     | runtime calls                                                                     | 90  |

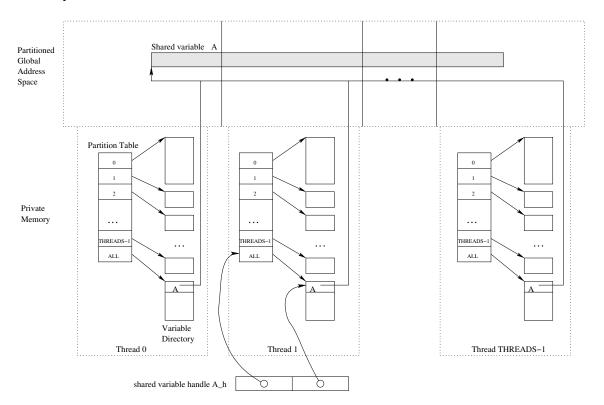

| 5.5                                 | Shared Variable Directory in a PGAS distributed memory machine                    | 92  |

| 5.6                                 | Shared array access through the SVD in Distributed Memory                         | 94  |

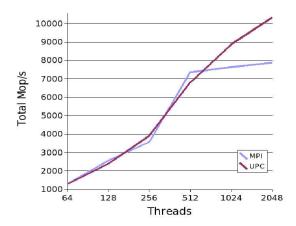

| 5.7                                 | UPC vs MPI scaling on CG class C                                                  | 104 |

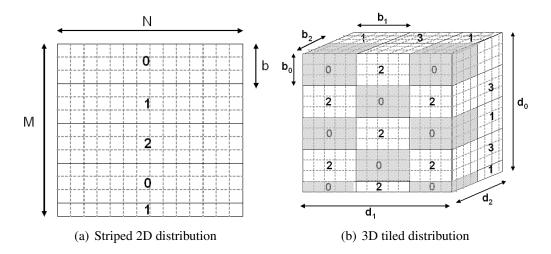

| 5.8                                 | Array distribution comparison                                                     | 107 |

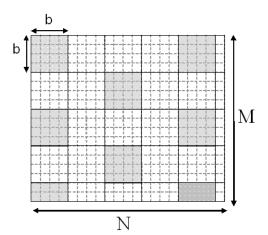

| 5.9                                 | Example of UPC Block-cyclic array distribution                                    | 108 |

| 5.10                                | Multi-level loop nest that accesses a multi-dimensional array in UPC 1            | 113 |

| 5.11                                | Matrix-vector multiplication and stencil benchmark evaluation                     | 114 |

| 5.12                                | Cholesky. Distributed symmetric rank-k update routine                             | 114 |

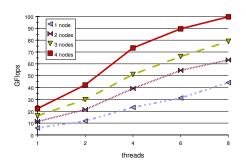

| 5.13                                | Performance of multiblocked Cholesky and matrix multiply                          | 115 |

| 5.14                                | Array distribution used in UPC HPL                                                | 117 |

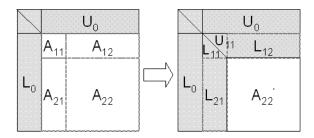

| 5.15                                | A snapshot of block LU factorization                                              | 118 |

| 5.16                                | Panel factorization routine                                                       | 119 |

| 5.17                                | HPL Performance (GFlops)                                                          | 119 |

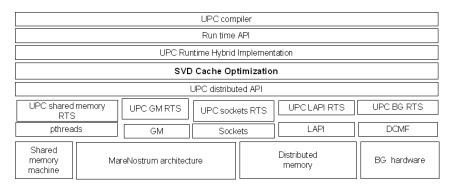

| 6.1                                 | Software organization of RTS                                                      | 126 |

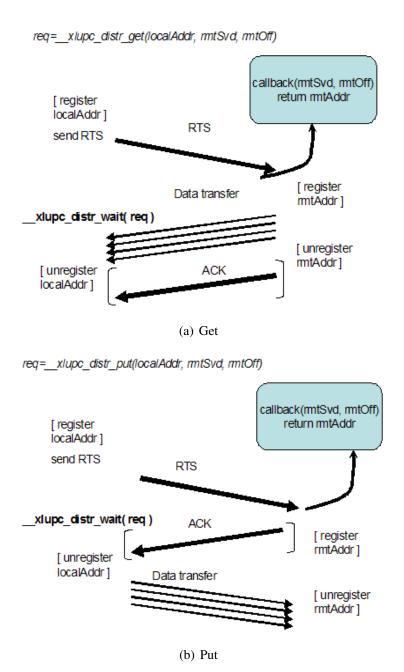

| 6.2                                 | Shared Variable Directory in a distributed memory machine                         | 129 |

| 6.3                                 | Protocols for XLUPC GET and PUT operations when the remote address                |     |

|                                     |                                                                                   | 130 |

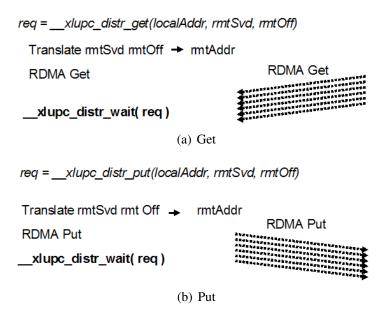

| 6.4                                 | Protocol for GET and PUT operations with RDMA operations when                     |     |

|                                     |                                                                                   | 131 |

| 6.5                                 | 1 1                                                                               | 132 |

| 6.6                                 |                                                                                   | 133 |

| 6.7                                 | GM implementation of GET                                                          |     |

| 6.8                                 | GM implementation of PUT                                                          |     |

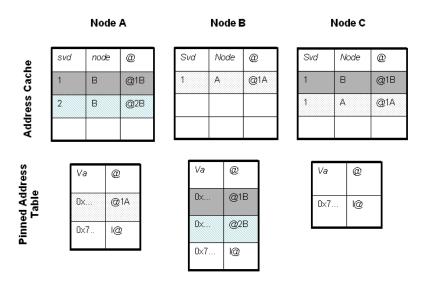

| 6.9                                 | Runtime snapshot the address cache in three nodes                                 |     |

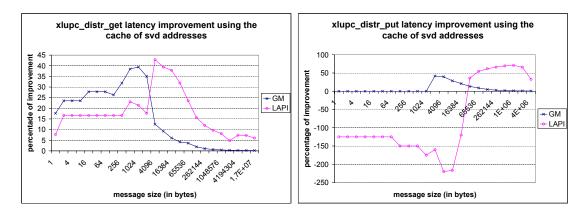

|                                     | Latency improvement by using the address cache 1                                  |     |

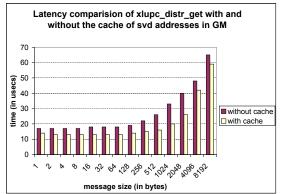

|                                     | GET latency with and without the address cache                                    |     |

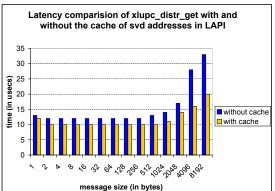

|                                     | Address Cache Size Evaluation                                                     |     |

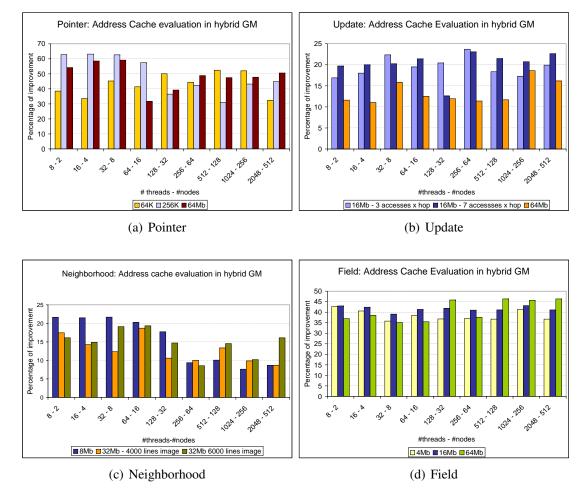

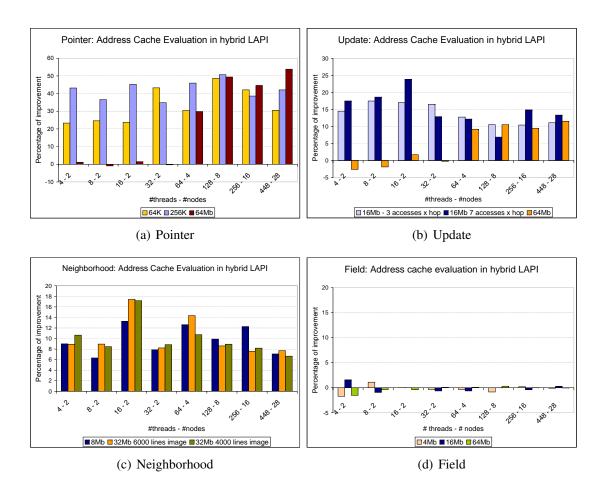

|                                     | Address Cache Evaluation on GM using DIS Stressmark Suite                         |     |

| 6.14                                | Registration Strategy Comparison on GM                                            | 150 |

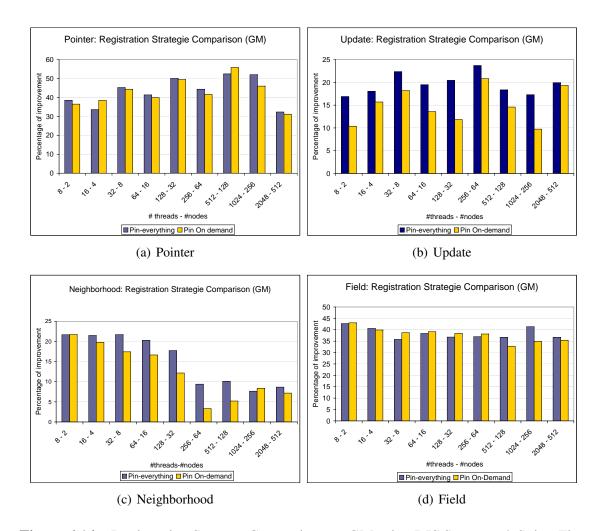

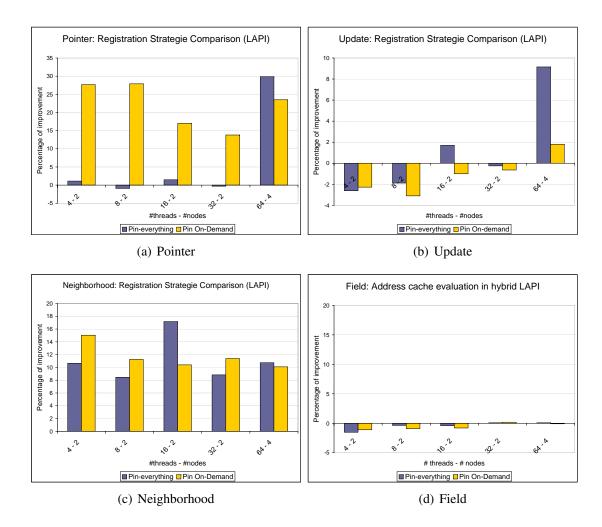

|                                     | Address Cache Evaluation on Power5 machines with LAPI using DIS                   |     |

|                                     | Address Cache Evaluation on Power5 machines with LAPI using DIS Stressmark Suite  | 151 |

| 6.15                                | Address Cache Evaluation on Power5 machines with LAPI using DIS  Stressmark Suite |     |

| <ul><li>6.15</li><li>6.16</li></ul> | Stressmark Suite                                                                  |     |

LIST OF FIGURES xxi

xxii LIST OF FIGURES

## **List of Tables**

| 1.1 | MPI UPC Programming Models (PM) comparison                       |

|-----|------------------------------------------------------------------|

| 3.1 | MPI benchmarks analysis                                          |

| 3.2 | Evaluated benchmarks and communication characteristics           |

| 5.1 | Optimizations effects on Random Access and Stream Benchmarks 102 |

| 5.2 | Random Access performance results                                |

| 5.3 | STREAM Triad performance results                                 |

| 5.4 | Access times in microseconds for shared array elements           |

| 5.5 | Line countage of the HPL UPC code                                |

| 6.1 | Data structure for the address cache                             |

| A.1 | Summary of used machine platforms                                |

xxiv LIST OF TABLES

# **Chapter 1**

## Introduction

2 Introduction

1.1 Introduction 3

### 1.1 Introduction

In 1958, IBM researchers John Cocke and Daniel Slotnick discussed the use of parallelism in numerical calculations for the first time [196].

In 1964, Slotnick had proposed building a massively parallel computer for the Lawrence Livermore National Laboratory. His design was funded by the US Air Force, which was the earliest SIMD parallel-computing effort, ILLIAC IV. The key to its design was a fairly high parallelism, with up to 256 processors, which allowed the machine to work on large data sets in what would later be known as vector processing. However, ILLIAC IV was called "the most infamous of Supercomputers", because only one fourth of the project goals were completed, it took 11 years and cost almost four times the original estimate [154]. When it was finally ready to run its first real application in 1976, it was outperformed by existing commercial supercomputers such as the Cray-1.

In the 1980s it was believed computer performance was best improved by creating faster and more efficient processors. This idea was challenged by parallel processing in the 90s, and attention turned from vector processors to massive parallel processing systems with thousands of ordinary CPUs. Since then, there has been an increasing trend to move away from shared memory parallel supercomputers toward networks of computers (clusters). This transition has been mostly driven by the fast improvement in the availability of commodity high-performance networks and highly influenced by power and cost limitations.

As a result, scalable computing clusters, ranging from cluster of PCs or workstations to clusters of Shared Memory Processors (SMPs) have become a low-cost standard platform for high-performance and large-scale computing. Emphasis has moved away somehow from fast sequential processing toward fast communications and distributed computing.

### 1.1.1 Future trends in High Performance Computing

Nowadays in the highlights of top500 list, recently updated in June 2008, we read that 400 (from 500) systems are labeled as clusters, making this the most common architecture in the TOP500 with a stable share of 80 percent. Moreover, looking at the TOP50, it is stated that the dominant architectures are custom build massively parallel systems (MPPs) with 56 percent ahead of commodity clusters with 40 percent.

The headline of TOP500 introduces: *The new number one system,* **Roadrunner**, located at Los Alamos National Laboratory (LANL) built by IBM broke (as first system ever) the petaflop/s Linpack barrier with 1.026 petaflop/s. Roadrunner is based on 6,562 dual-core AMD Opteron chips plus 12,240 Cell chips connected with a commodity

4 Introduction

InfiniBand network.

Some other staggering statistics from the last released top500: The entry level to the list moved up to the 9.0 Tflop/s mark on the Linpack benchmark, compared to 5.9 Tflop/s six months ago. This is the largest turnover rate in the 16 years of the history of the TOP500 project. And The average concurrency level in the TOP500 is 4,850 cores per system up from 3,290 six month ago

If we look at the news, along the years we find more evidence that innovative system architectures go for distributed designs where communication becomes a key issue: *I.B.M. Supercomputer Sets World Record for Speed By John Markoff Published*. September 2004: An *I.B.M. machine has reclaimed the title of world's fastest supercomputer, overtaking a Japanese computer that had caused shock waves at United States government agencies when it set a computing speed record in 2002*. The machine was BlueGene/L with 65,536 dual-core nodes (later upgraded to 106,496 nodes) connected through a High speed 3-dimensional torus network. It took the place of Earth Simulator, a highly parallel vector supercomputer system consisting of 640 nodes with 8 vector processors connected by 640x640 single-stage crossbar switches.

June 2005: The 5 spot was captured by the upgraded MareNostrum system at the Barcelona Supercomputer Center. It is an IBM BladeCenter JS20-based system with a Myrinet connection network and achieved 27.91 TFlop/s - just ahead of a third Blue Gene system owned by ASTRON and installed at the University of Groningen with 27.45 TFlop/s. The four machines, MareNostrum, Earth Simulator, Blue Gene and Roadrunner among many others are based on distributed memory and High Performance Networks.

Apparently, the focus has moved to distributed computing and MPPs lead the HPC market. Performance is then, delivered by exploiting the application parallelism in these massively parallel systems connected through High-performance Networks and two issues become critical in order to improve efficiency and gain scalability: (i) Optimize the communication management (ii) and provide a suitable parallel programming model.

The aim of this thesis is to improve scalability of programming models for current massively parallel computers, as a key issue, we will focus on the optimization of communications, and two different parallel programming models, both suitable for Large Scale Machines, will be studied. Next section examines the future trends on programming models for High Performance Computing.

### 1.1.2 Programming trends in HPC

Since many real world applications are naturally parallel and hardware is naturally parallel, what we need is a programming model, system software, and a supporting

1.1 Introduction 5

architecture that are naturally parallel.

Supercomputers are used for highly calculation-intensive tasks such as problems involving quantum mechanical physics, weather forecasting, climate research, molecular modeling, physical simulations, cryptanalysis, and the like.

Although the technology of clusters is currently being deployed, the development of parallel applications is really a complex task. Adequate software and tools need to be provided. Over the years, many research on High Performance Computing has been focused on analyzing, improving or creating parallel programming models adapting to the new computer architectures with the ultimate goal of improving productivity of programming. As a result, nowadays, there is a wide spectrum of different *parallel programming environments or models* to exploit parallel processing.

We understand parallel programming model as a set of software technologies to express parallel algorithms and match applications with the underlying parallel systems. Parallel models are implemented in several ways: as libraries invoked from traditional sequential languages, as language extensions, or as complete new execution models. They are also roughly categorized for two kinds of systems: shared-memory system and distributed-memory system, though the lines between them are largely blurred nowadays.

Also, from the language point of view, we could broadly identify two main approaches to parallelism: message passing (explicit communication) and data-parallel (implicit communication). The first approach is treated as an assembler for parallel programming, since the programmer is responsible for most of the parallelization effort such as task decomposition, mapping tasks to processors, and the communication structure. This approach is based on the assumption that the user is often the best judge of how parallelism can be exploited for a particular application. While in the second approach the user has the illusion of a shared address space and it offers ease of programming since the user does not specify, and thus cannot control, the scheduling of calculations and/or the placement of data. A programming model is usually judged by its expressibility and simplicity, which are by all means conflicting factors.

Due to the difficulties in automatic parallelization, people have to choose a proper parallel programming model or a form of mixture of them to develop their parallel applications on a particular platform. Moreover, parallelism is everywhere and people writing parallel programs may not be computer specialists any longer, as a result programmability is winning attention, becoming a required characteristic of new programming models.

In this thesis we take two different parallel programming models as our case studies: the well known communication library *Message Passing Interface* (MPI), as an explicit communication programming model. And a parallel extension to the C language: *Unified*

6 Introduction

Parallel C (UPC), where communication is implicit.

Whereas MPI is a communication library, UPC is a parallel language, it relies on a compiler that translates code to a Run Time System (RTS) library in charge of the communication.

#### **Explicit communication: MPI**

Message passing libraries allow efficient parallel programs to be written for distributed memory systems. These libraries provide routines to initiate and configure the messaging environment as well as sending and receiving packets of data. Various message passing environments were developed in early 80s. Some were developed for special purpose machines such as the Caltech's N-cube, some were developed for networks of UNIX workstations, e.g., the Argonne's P4 library and PVM (Parallel Virtual Machine) [179], which was one of the most popular, from the Oak Ridge National Laboratories. The Ohio Supercomputer Center developed a message passing library called LAM [118]. By early 1992 it was clear that the authors of these numerous libraries were duplicating their efforts.

In late 1992 a meeting was set up during the Supercomputing 92 conference and the attendants agreed to develop and then implement a common standard for message passing that would incorporate all the interesting existing ideas and build on them. And this is how MPI, the Message Passing Interface, was born. Nowadays MPI has become the **de facto standard** of parallel models for distributed memory systems and it is by far the most popular due to its portability, flexibility and good performance. MPI defines an API that allows portability while the library implementation permits multiple platform dependent optimizations. As a result, parallel applications can have good performance without having to port them to different architectures.

The first MPI specification draft [130] was introduced at Supercomputing on 1994. At this time the top MPP on the TOP500 list [188], coming from Sandia National Labs, had 3800 processors. Nowadays, the top two on the list are: Blue Gene Light, recently updated, it is installed at Lawrence Livermore National Labs, it has 212992 cores, and Roadrunner, recently created, with 122400 cores. And during the last twelve years the peak performance has increased from 180Gflops to 1,026Pflops (more than one quadrillion floating point operations per second, achieved this June 2008 by Roadrunner). The trend is to increase the number of processors, connected through different topologies of high-speed networks to gain performance, and parallel models need to catch up.

Despite of the fact that MPI specification was designed to be performant and scalable, the truth is that current implementations still need to be adjusted to this evolution on 1.1 Introduction 7

the new architectures and MPI scalability proves to be a weakness of current MPI implementations.

#### **Implicit communication: UPC**

Concerning the data-parallel models, this approach has been followed by parallel languages such as SISAL and PCN, but they found little favor with application programmers. This is because users are reluctant to learn a completely new language for parallel programming. They really would prefer to use their traditional high-level languages (like C and Fortran) and try to recycle their already available sequential software. For these programmers, the extensions to existing languages or runtime libraries are a viable alternative.

Taking this into account the partitioned global address space (PGAS) parallel programming models appeared. A PGAS programming model is a Single Program Multiple Data (SPMD) paradigm that presents the user with both a private memory space and a shared memory space. By default, all variables are private and every instruction is executed by each thread. However, the user may declare that some data be shared and that loop iterations be divided among threads. The novelty of PGAS is that the portions of the shared memory space may have an affinity for a particular thread, thereby exploiting locality of reference. The PGAS model is the basis of Unified Parallel C, Co-array Fortran, and Titanium (Java).

Unified Parallel C (UPC) is an extension of the C programming language designed for high-performance computing on large-scale parallel machines, including those with a common global address space (SMP and NUMA) and those with distributed memory (clusters). The programmer is presented with a single shared, partitioned address space, where variables may be directly read and written by any processor, but each variable is physically associated with a single processor. UPC fixes the amount of parallelism at program startup time.

In order to express parallelism, UPC extends ISO C 99 with the following constructs: an explicitly parallel execution model, a shared address space, synchronization primitives and a memory consistency model and memory management primitives.

The UPC language, as opposed to MPI, is quite new (the first language specifications appeared on 2001) and it evolved from experiences with three other earlier languages that proposed parallel extensions to ISO C 99: AC, Split-C, and Parallel C Preprocessor (PCP). UPC is not a superset of these three languages, but rather an attempt to distill the best characteristics of each. UPC combines the programmability advantages of the shared memory programming paradigm and the control over data layout and performance of the

8 Introduction

| MPI                            | UPC                           |  |  |

|--------------------------------|-------------------------------|--|--|

| SPMD                           | SPMD                          |  |  |

| Static (MPI-1) Dynamic (MPI-2) | Static threads                |  |  |

| Shared and distributed memory  | Shared and distributed memory |  |  |

| Specified Data distribution    | Specified Data distribution   |  |  |

| Message Passing PM             | Shared Memory PM              |  |  |

| Explicit communication         | Implicit communication        |  |  |

One-sided

**Table 1.1** MPI UPC Programming Models (PM) comparison

message passing programming paradigm.

Two-sided

Regarding UPC performance, UPC community emphasized performance and scalability when the language was designed, and there are promising preliminary results [75]. However UPC scalability and efficiency still need to be proved.

#### **MPI versus UPC Comparison**

Table 1.1 summarizes the most relevant characteristics of both languages. Both languages are built on the Single Program Multiple Data (SPMD) paradigm. In MPI-1 and UPC the number of threads is static, defined at startup time, while dynamic creation of processes has been enabled in MPI-2. In both models a process may access its private memory and share data with the other processes, and the data distribution has to be specified by the programmer. The difference is that in UPC the user is presented with a global shared address space while MPI provides the user with a set of primitives allowing explicit communication among processes. In UPC the communication is hidden by the compiler and runtime while in MPI it is made explicitly by the programmer.

From the communication point of view, which is the main concern of this thesis, one relevant difference must be emphasized: MPI offers a two-sided communication model, a process sends a message to another process that has to explicitly receive it (send, receive), and both processes are involved in the communication (and synchronized). Whereas UPC is based on one-sided communication and only the process that initiates the communication needs to be involved (get, put).

1.2 Global picture

# 1.2 Global picture

We have stated that optimized communication is crucial for scalability of large scale architectures. The aim of this thesis is to improve scalability of programming models for current massively parallel computers. As a key issue, we will focus on the optimization of communication, and two different parallel programming models will be considered: MPI following the explicit communication approach and UPC following the implicit approach. As long as they run on distributed memory machines, both languages need an underlying messaging system that is performant and scalable.

We state that in spite of the fact that UPC and MPI take rather different approaches, as far as performance and scalability concerns they may have a lot in common. In this study we will find out whether both models suffer from the same problems, and the same optimizations could be applied or on the contrary we need different solutions to end up with a scalable model. Notice that if all the experiences in one model could be applied to the other one, the contribution is doubled.

Therefore the goal of this work is to analyze the weaknesses of parallel models for massively parallel computers and propose optimizations related to the communication system in terms of scalability and efficiency.

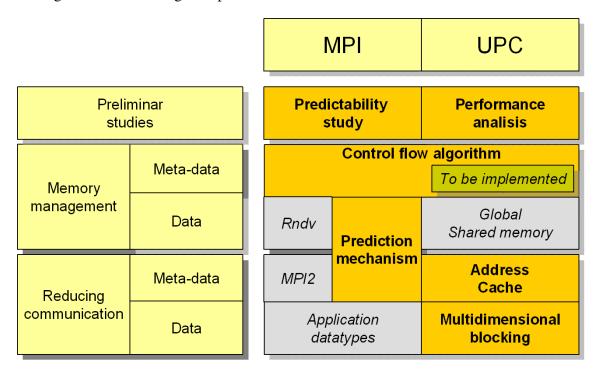

Figure 1.1 shows the global picture of our work. Two main directions have been taken:

**Figure 1.1** Global Picture of our thesis.

10 Introduction

• Optimize the communication system memory management to make it scalable to hundreds of thousands of nodes. And we distinguish between: (i) The memory management required to receive and process the application *data*. And (ii) The memory management for *meta-data* (aka. *control data*), we call meta-data the information required to manage the data transfer but not containing application data.

• **Reduce the communication** between nodes, will obviously result in a better efficiency and scalability. Here we also distinguish between: (i) Communication of *Data* and (ii) *Meta-data* messages.

Each aspect is being considered for both the MPI and UPC parallel models. Our contributions are shown in bold face, italics denotes either the problem was already being considered in the bibliography or the language did not show this problem and in the case of the control flow algorithm it means that although the same solution applies it has not been yet implemented.

As shown in the figure, a preliminary study of MPI predictability was done to come up with a **prediction mechanism** that accomplishes two goals, it improves the communication system memory management, guaranteeing message reception for large scale machines and reduces the control-data communication. To solve the problem of control-data memory management a **memory management control flow algorithm** was proposed. This constitutes the first contribution of this thesis.

In UPC a preliminary study was also done to assure that UPC was able to scale to hundreds of thousands of nodes. Then an extension to the language was proposed, **Multidimensional Blocking in UPC** to better exploit locality and reduce communication of application data. This is our second contribution.

And finally, a mechanism to reduce control-data communication was proposed in UPC, by means of a **Remote address Cache**, accomplishing two goals: First, it reduces control-data communication, similar to the prediction mechanism in MPI. And second, it exploits the RDMA network capabilities whenever possible. It results in an improvement in terms of data communication latency. This is our third contribution.

#### 1.3 Contributions

The main contributions of this thesis can be outlined as follows. We:

• Scale up the communication memory management: (i) Prediction to scale up the communication system memory management (ii) Control flow for control data

1.3 Contributions

• Reduce communication: we introduce the *Multidimensional blocking: a language* extension to reduce communication

• Speed up communication: we present the *Remote Address Cache: Scalable RDMA* performance for PGAS languages.

#### 1.3.1 Scale up the communication memory management

As we have seen the current trend on parallel computing is moving from big shared memory machines to large scale distributed memory machines connected through high performance networks. An increase in the number of nodes directly implies an increase in the communication requirements in terms of robustness, scalability and efficiency.

Moreover applications become more complex and resource demanding which also affects communication by increasing the amount of communication required and the communication system is stressed.

The communication system needs to be designed with scalability in mind. It needs to handle the correct reception of messages, as well as to take care of unexpected message reception despite of current resource availability.

Any message arriving before being required by the application needs to be stored somewhere into the library and solid and efficient memory management becomes essential for scalability. The scalability problem arises due to fact that available messaging systems take assumptions about resource availability (memory) which are not always true, specially considering the system architecture of current massively parallel computers.

Our *first contribution* focuses on **improving the memory management in the communication system**, dealing with memory shortage in two different scenarios: control-data and application data. This contribution has been split in two chapters:

• In the first chapter we focus on user's data message reception. In most current implementations, preference is given to the performance and control messages are avoided, so a message may be sent without receiver's permission and it is not guaranteed that the receiver will have enough memory to keep this message. Two solutions are provided: first, **prediction** was used to **improve communication system memory management on user's data reception**. The communication pattern predictability was studied showing high predictability rates. And a mechanism to guarantee the correct message reception by predicting the communication pattern and allocating the required resources in-advance was introduced, this mechanism was also reducing the amount of control-data exchanged between processes. And

12 Introduction

second, a simpler solution based on a three-way handshake protocol is also considered and analyzed.

• The second part of this contribution, *Control Flow for control data*, focuses on **short-memory MPPs memory management for meta-data reception**. For every message arrival, control-data needs to be saved in order to manage the message. When memory is short, thousands of control-data messages can flood up the receiver's memory, specially in the new era of supercomputers having very hard memory restrictions (BG/L, ASCI-Red, ASCI-White). In this chapter we present a new memory management protocol that guarantees scalability of messaging systems for large scale supercomputers.

MPI has been chosen to carry on this study since it is the most popular parallel language widely used among the HPC community and portable. MPICH has been chosen because it is an open source and broadly used implementation of the MPI standard.

The work performed in this area has resulted in the following publications:

- [82] Felix Freitag, Jordi Caubet, Montse Farreras, Toni Cortes, Jesus Labarta. Exploring the Predictability of MPI Messages. IPDPS '03: Proceedings of the 17th IEEE International Parallel and Distributed Processing Symposium (IPDPS'03)

- [84] Felix Freitag, Montse Farreras, Toni Cortes, Jesus Labarta. Predicting MPI Buffer addresses. ICCS2004: The International Conference on Computer Sciences 2004 (ICCS'04)

- [80] Montse Farreras, Toni Cortes, Jesus Labarta, George Almasi. Scaling MPI to short-memory MPPs such as BG/L. ICS06: Proceedings of the 2006 International Conference on Supercomputing (ICS'06)

# 1.3.2 Multidimensional blocking: a language extension to reduce communication

In the era of large scale machines, system-optimization is winning attention and performance is delivered by exploiting application parallelism. Despite the more and more efficient modern High-performance Networks being deployed, time spend in communication reduces application performance and it is crucial to provide appropriate parallel programming models that exploit data locality as much as possible.

Partitioned Global Address Space (PGAS) languages offer an attractive, high productivity programming model for programming large-scale parallel machines. PGAS languages, such as Unified Parallel C (UPC), combine the simplicity of shared-memory

1.3 Contributions

programming with the efficiency of the message-passing paradigm by allowing users' control over the data layout. PGAS languages distinguish between private, shared-local, and shared-remote memory, with shared-remote accesses typically much more expensive than shared-local and private accesses, especially on distributed memory machines where shared-remote access implies communication over a network.

The *second contribution* of our thesis aims to **reduce communication**, by a simple extension to the UPC language that allows for better control of locality, and therefore performance, in the language.

This work has been carried on in the UPC language because MPI, as an explicit programming model, distributes the "shared" data explicitly among the processes, all the responsibility is left to the programmer and the complexity of the program increases substantially.

A preliminary study was performed to evaluate the use of a shared memory programming language, Unified Parallel C (UPC) on large scale distributed memory machines. We demonstrate not only that shared memory programming for hundreds of thousands of processors is possible, but also that with the right support from the compiler and runtime system, the performance of the resulting codes is comparable to MPI implementations. A good balance in productivity and performance is demonstrated.

The work performed in this area has been done in collaboration with IBM. The proposed language extension, although at this point it is not yet part of the standard UPC language specifications, is supported by the IBM XLUPC compiler and this contribution will be part of the final product to be released in December 2009.

This contribution results from a collaborative effort involving work in two areas: the UPC compiler and the UPC Run Time System (RTS). For the purpose of this thesis we present the proposed language extension and the necessary support in the UPC RTS.

This work has resulted in the following publications:

- [17] Christopher Barton, Calin Cascaval, George Almasi, Yili Zheng, Montse Farreras and Jose Nelson Amaral. Shared Memory Programming for Large Scale Machines. In PLDI 2006: ACM SIGPLAN Conference on Programming Language Design and Implementation

- [16] Christopher Barton, Calin Cascaval, George Almasi, Rahul Garg, Jose Nelson Amaral and Montse Farreras. Multidimensional Blocking in UPC. LCPC 2007: International Workshop on Languages and Compilers for Parallel Computing

And two High Performance Computing (HPC) Challenge Competition Awards:

[34] C.Cascaval, C.Barton, G.Almási, Y.Zheng, M.Farreras, P.Luk, R.Mak. The UPC/BlueGene Class II Submission to the HPC Challenge Award Competition. HPCC

14 Introduction

2005.

[35] C. Cascaval, G. Almási, C. Barton, E. Tiotto, G. Dózsa, M. Farreras, P. Luk, T. Spelce. HPC Challenge 2006 Awards Competition: xlUPC on BlueGene/L. HPCC 2006.

# 1.3.3 Remote Address Cache: Scalable RDMA performance for PGAS languages

Parallel programming for both multicore and large scale parallel machines is becoming evermore challenging; adequate programming tools offering both ease of programming and productivity are essential.

PGAS languages provide a unique programming model that can span shared-memory multiprocessor (SMP) architectures, distributed memory machines and cluster of SMPs. User can program large scale machines with easy-to-use, shared memory paradigms.

Moreover, PGAS languages are based on one-sided communication, which offers some advantages in terms of performance over the traditional two-sided communication model mostly used in MPI. In a two-sided model, the processes involved in the communication need to synchronize. In contrast, one-sided model splits communication from synchronization offering primitives for communication (get, put) and for synchronization (barrier, fence). Which allows to better overlap of communication and computation.

However, in order to exploit efficiently large scale machines, PGAS language implementations and their runtime system must be designed for scalability and performance. The IBM XLUPC compiler and runtime system provide a scalable design through the use of the Shared Variable Directory (SVD). The SVD stores meta-information needed to access shared data. The information includes the virtual memory address of data for each shared variable on the local node, the type and shape of the shared data, etc. The SVD is managed by the compiler, which creates and deletes entries in the directory whenever shared variables are allocated and de-allocated. The SVD is dereferenced, in the worst case, for every shared memory access, thus exposing a potential performance problem. In addition, the runtime system implements a protocol for obtaining the remote address of a shared variable, and thus a handshake is required to exchange this control-information which limits the exploitation of native (remote) direct memory accesses that most modern High Performance Networks offer (Infiniband and Myrinet among others).

In the *third contribution* of our thesis we present a **cache of remote addresses** as an optimization that will reduce the SVD access overhead, the handshake will not be necessary thus synchronization would be avoided and the native direct memory access will be exploited. It results in a significant performance improvement while maintaining

the portability and scalability of the runtime system.

This work has been carried on in the UPC language and it applies to any other PGAS language but not to MPI. MPI is an explicit programming model, although MPI-2 offers one-sided communication, communication is explicit, the remote shared address of any one-sided communication is exchanged through a collective before the one-sided takes place. As the remote address is known the cache is not required, and all the benefits of one-sided communication apply.

The work performed in this area has resulted in the following publication:

[79] Montse Farreras, George Almási, Calin Cascaval and Toni Cortes. Scalable RDMA performance in PGAS languages. In submission process

# 1.4 Thesis Organization

The rest of the thesis is organized as follows: Chapter 2 presents the state of the art related to our work. In the direction of improving the memory management in the communication system of massively parallel computers, Chapter 3 explores the use of predictability to scale up the communication system memory management and Chapter 4 presents and evaluates a memory control flow algorithm that deals with control data reception in short-memory scenarios. Chapter 5 introduces a language extension that allows for better exploitation of data locality thus reducing inter-node communication. Chapter 6 presents and evaluates a cache of remote addresses that aims to reduce communication latency by reducing control-data communication and exploiting the RDMA network capabilities. Finally, Chapter 7 draws up the conclusions of our research work and discusses the future directions.

16 Introduction

# Chapter 2

# **Related Work**

18 Related Work

# 2.1 Parallel programming models

Over the years, many research on High Performance Computing has been focused on analyzing, improving or creating parallel programming models adapting to the new computer architectures with the ultimate goal of improving productivity of programming.

Among the most popular programming languages: PThreads [33] (POSIX Threads) and OpenMP [148] are two of most widely used for shared memory machines. Whereas Message Passing Interface (MPI) stands out in High Performance Computing among other message-passing systems PM [184], CORBA [147] or SOAP [178] for distributed memory machines. In MPI, communication between processes is made explicit which allows better performance to the detriment of programmability.

Due to its complexity, there have been many projects over the years that have aimed to improve productivity of parallel programmers. One of the major directions has been to provide important computational tasks as sets of libraries that run over MPI. Popular examples include SCALAPACK [117, 48] and PBLAS [49]. Large software engineering efforts such as PETSc [15] provide a common framework that encompass many popular tools. In practice these distributions have been successful.

In order to provide a richer abstraction and expression of the higher level semantics there have been many language efforts to improve productivity. Popular examples of these language include UPC, Co-Array Fortran [146, 51], Titanium [200], ZPL [43], HPF [81], Chapel [42, 36], Fortress [5], X10 [198], Cilk [180], Charm++ [151], and many others.

While each of the languages has its own corresponding performance and scalability studies, we highlight those related to the once we choose to study on our thesis: UPC and MPI.

#### 2.1.1 MPI

Concerning MPI, there exist many research groups that have provided their own MPI implementation: MVPICH [138, 134], MP-LITE [126], LAM [118], CHIMP [47] or OpenMPI [149]. The most relevant are:

• Argone National Laboratory develop MPICH [132]. It is high-performance widely portable implementation supporting different computation and communication platforms such as commodity clusters, high-speed networks and propietary high-end computing systems (BlueGene, Cray). It provides a very modular design framework that allows an easy extension to other derived implementations. For this reason it is by far the most popular and widely used implementation.

20 Related Work

• Ohio State University develops and does research over MVAPICH, extending MPICH over InfiniBand [186].

- Sandia National Laboratory implements MPICH over Portals: Portals MPI [133].

- Myricom provides two Myrinet [140] drivers: GM and MX, with its correspondent MPICH extensions: MPICH-GM and MPICH-MX [140].

- IBM provides its own MPI implementation based also on MPICH for the BlueGene family [6].

#### 2.1.2 UPC

Concerning UPC, the family of UPC implementations include:

- Berkeley UPC: The goal of the UPC effort at **UC Berkely** is to build portable, high performance implementations of UPC for large-scale multiprocessors, PC clusters, and clusters of shared memory multiprocessors. There are three major components to this effort: lightweight communication, compilation techniques and application benchmarks.

- MTU-UPC: Michigan Technological University (MTU) [168] projects include the recent release of the MuPC run time system for UPC as well as collective specification development, memory model research, programmability studies, and test suite development.

- GCC-based Intrepid UPC[87] toolset provides a compilation and execution environment for programs written in UPC. The GCC UPC compiler extends the capabilities of the GNU GCC compiler. The GCC UPC compiler is implemented as a C Language dialect translator, in a fashion similar to the implementation of the GNU Objective C compiler.

- The High Performance Computing Laboratory of George Washington University (GWU) is involved in a number of efforts: UPC specification, UPC testing strategies, UPC documentation, testing suites, UPC benchmarking, and UPC collective and Parallel I/O specification.

- Other implementations are provided by HP UPC [95] and Cray UPC [58].

Our thesis is focused on optimizing the communication system for Massively Parallel Computers. The proposed optimization have been studied in these two parallel models:

MPI and UPC. Next sections present the research work found in the bibliography for each contribution of this thesis.

# 2.2 Improving memory management in the communication system

The first contribution of this thesis is focused on memory management in the communication system, dealing with memory shortage in two different scenarios: control-data and application data.

For every message arrival, control-data needs to be saved in order to manage the message. When memory is short thousands of control-data messages can flood up the receiver's memory.

Another memory management issue is to be aware of is the application data. In most current implementations, preference is given to the performance and control messages are avoided, so a message may be sent without receiver's permission and it is not guaranteed that the receiver will have enough memory to keep this message. Section 2.2.2 analyze both aspects of some messaging systems. Since one of our proposed solutions uses prediction to guarantee data message reception, a preliminary study about message predictability was done, research work related with predictability is presented in next section.

#### 2.2.1 Communication Patterns Prediction

Regarding the characterization of the temporal communication patterns of MPI applications and the proposal of a prediction scheme based on periodicity detection, there has been some research on the topic.

Kim and Lilja [113] describe the communication patterns of MPI applications in the spatial domain (communication locality). In their experiments it was found that the processes communicate only with a small number of the partners (message-destination locality). Also, it is observed that the MPI applications usually have only 2-3 distinct message sizes (message size locality). Another result is that while the problem size and the number of processes vary, the size and number of messages vary, but the observed communication localities are quite unaffected. The characteristics of the temporal patterns in MPI messages, however, were not reported.

In our work we considered the temporal domain of the message stream. We identified the size of the iterative patterns appearing in the temporal domain. Although the spatial 22 Related Work

locality shown in [113] suggests the possibility of an iterative behavior in the temporal domain, it is not guaranteed by the spatial locality. In fact, we observed in the data streams of the physical level that communication latencies can be affected by randomness, which as a consequence affects the temporal pattern. When the communication latencies become significant compared to the computation time, randomness will not influence in the spatial locality of the messages, but the temporal message behavior may become unknown and unpredictable.

In his work, Afsahi et al. [3, 1, 2] propose the prediction of MPI messages. In this work a number of heuristics for the prediction of MPI messages are presented. The prediction heuristics are used to predict only the next value of a given data stream. The proposed application is to cache the incoming message to be nearby when the consuming thread accesses it. It was shown that the prediction heuristics provide very high hit rates for the studied streams.

Alsahi et al. [3] also propose the use of prediction to handle dynamic memory allocation for user's data, to guarantee correct message arrival. Our work is different in that the predictor we propose is based on the computation of distances between patterns in the stream. This has the benefit that the iterative pattern in the data stream is identified. In contrast to these prediction heuristics, knowing the iterative pattern allows not only the next value to be predicted, but several future values of the data stream.

Regarding to the applicability of MPI predictions, Iwamoto et al. [105] use next message prediction to speculatively execute the message reception beforehand. Our work differs in the purpose. While Iwamoto et al. seek for performance improvement, correct message reception is not guaranteed. In our work prediction is not used to receive the message but to prepare the receiver's environment to guarantee enough resources for message reception.

Our approach analyzes and predicts MPI communication patterns at run time. This analysis is indeed possible at compiler time. Shao et al. [172] present a compiler framework which can identify communication patterns for MPI-based parallel applications. The analysis has been used to minimize power consumption [173], and to guide source code transformations [163]. This approach has the drawback that it is limited for those applications that show static communication patterns.

## 2.2.2 Memory management in the communication system

To guarantee message reception, some contributions have taken the approach of statically allocate memory space to guarantee message arrival, this is the case for AIX [103], it allocates space for user's data but not for control-data. Also Fast messages in its

credit-based control flow algorithm [150] preallocates space for both data and control-data for every other process in the system. PortalsMPI[133] pre-allocates space for control-data, while data is dropped if no memory is available. We should note though, that memory pre-allocation has the drawback that it does not scale well, just imagine if we decide to allocate 10Kb buffer per process in a 132K node machine like BGL, each process would need to allocate more than 1Gb of memory, while BGL has 512Mb of available memory per node. If we reduce the memory allocated, and use it only for control-data, it is always a limitation that turns to be too restrictive in practice, especially as applications scale beyond a thousand processes.

The next logical step is to allocate the memory dynamically. Portals 3.1 [29, 28] softens the problem with control-data reception by allocating memory for control-data dynamically and the number of outstanding unexpected messages becomes dependent on memory space rather than count, not having enough memory to allocate control-data is not considered, (probably because to our knowledge it has scaled up to 1792 nodes [29]).

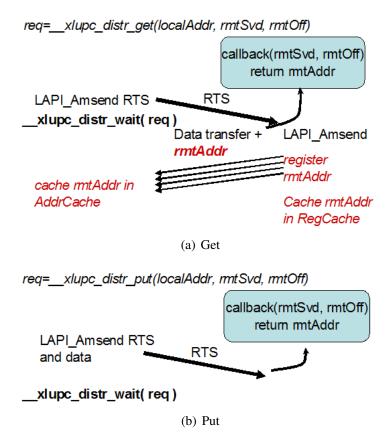

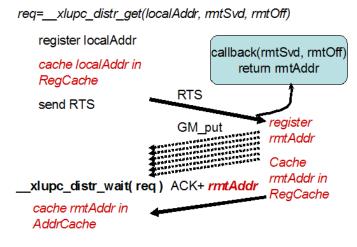

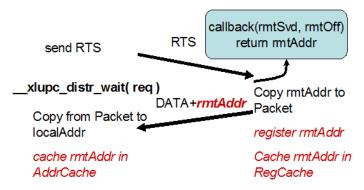

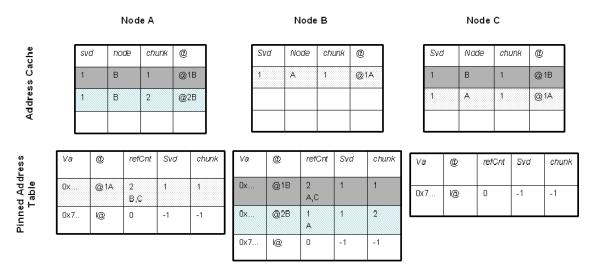

Regarding dynamic memory allocation for user's data other directions have been taken that do not use prediction. An on-demand credit management was explored for use in Fast Messages making the previous credit-based control flow mechanism more scalable[37, 116]. The idea is to distribute available credits on an on-demand basis so it does not depend on the number of processors and each process receives credit according to its communication needs.