# Towards instantaneous performance analysis using coarse-grain sampled and instrumented data

Author: Harald Servat Gelabert Advisor: Prof. Jesús Labarta Mancho

A THESIS SUBMITTED IN FULFILMENT OF

THE REQUIREMENTS FOR THE DEGREE OF **Doctor per la Universitat Politècnica de Catalunya**Departament d'Arquitectura de Computadors

A la memòria de la *iaia*. Sempre seràs als nostres records. Que el teu somriure i els teus panellets alegrin el cor als teus nous companys de viatge.

### **Abstract**

Computation is currently an integral part of scientific experimentation. There are many disciplines in which computers help to solve a myriad of scientific problems using a wide spectrum of algorithms implemented into programs. Some of these problems are so complex that a single computer would take too long that they become impractical to tackle. High-Performance Computing (HPC) systems (or informally, *supercomputers*) appeared to solve these problems and let the user do more science by offering more computational power. Current HPC systems consist of nodes containing multiple processors that communicate to each other using a fast network, resulting in a tightly coupled systems. If applications are to take advantage of these replicated resources they need to communicate and collaborate with one another to reach the final solution. To this end, applications need to divide their work into smaller work units and split them among the processors, so each processor works in parallel.

Nowadays, supercomputers deliver an enormous amount of computational power; however, it is well-known that applications only reach a fraction of it. There are several factors that limit the achieved application performance. One of the most important factors is the single processor performance (i.e. how fast a processor executes a work unit) because it ultimately dictates the overall achieved performance. Performance analysis tools are pieces of software that help to locate performance inefficiencies and identify their nature within applications to improve eventually the application performance. Performance tools rely on two collection techniques to invoke their performance monitors: instrumentation and sampling. The instrumentation mechanism is the ability inject performance monitors into concrete application locations whereas sampling it the capacity to invoke periodically monitors according to external events. Each technique has its advantages. The measurements obtained through instrumentation are directly associated with the application structure while sampling allows a simple way to determine the volume of the measurements captured. In any case, however, the granularity of the measurements that provides valuable insight cannot be easily determined a priori. Should analysts study the performance of an application for the first time, they may consider using a performance tool and instrument every routine or use high-frequency sampling rates in order to provide the most detailed results. More often than not, these approaches lead to large overheads that impact on the application performance and so altering the measurements gathered and therefore mislead the analyst.

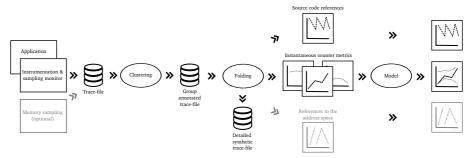

This thesis describes the folding mechanism that overcomes the overhead by taking advantage of the repetitiveness of many applications. This mechanism smartly combines punctual instrumented and inexpensive coarse-grain sampled information and then generates rich reports that show the instantaneous performance evolution within instrumented regions of code. In order to produce these reports, the folding processes performance metrics from different types of sources: performance and energy counters, source code and memory references. The folding processes these metrics according to their nature. While performance and energy counters represent continuous metrics, the source code and memory references refer to discrete values that point out locations within the application code or the application address space, respectively. This thesis evaluates and validates two fitting algorithms used in different areas to report continuous

metrics: a Gaussian interpolation process known as Kriging and piece-wise linear regressions. Also, when reporting performance counters, it is crucial to correlate the value from different events at the same time to unveil the nature of the bottlenecks. The folding takes advantage of of analytic performance models derived from performance counters to focus on a small set of performance metrics. This fact avoids the analyst to dig into all the available performance counters and search for multiple reports to look for correlations. The folding also presents the correlation with the source code. To this end, the work described here also proposes two alternatives: using the outcome of the piece-wise linear regressions and a mechanism inspired by Multi-Sequence Alignment techniques. Finally, this thesis explores the applicability of the folding mechanism to captured memory references to give insight regarding the accesses to the application data object and report their temporal accesses.

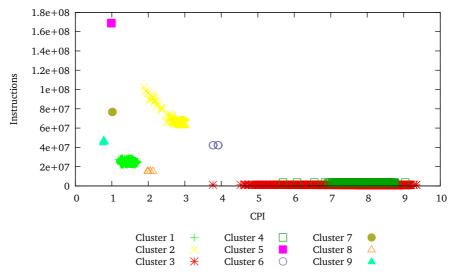

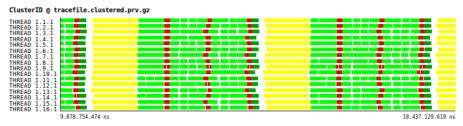

This thesis proposes an analysis methodology for the first-time seen parallel applications that focus on describing the most time-consuming computing regions. This methodology is implemented on top of a framework that is based on a previously existing clustering tool and the folding mechanism. The clustering tool explores an application trace-file exploring the structural behavior of the application based on the performance data captured by instrumenting parallel programming run-times (such as MPI and OpenMP). The folding mechanism then uses the information on the identified structures to report their internal evolution and correlate with the source code, making the folding the perfect companion for the clustering tool. As a result, the framework finely accurately depicts the application performance using coarse-grain sampling and minimal instrumentation with the consequent savings in terms of overhead.

To demonstrate the usefulness of the methodology and the framework and therefore the value of the folding mechanism, this thesis includes the discussion of multiple first-time seen parallel in-production applications executed in several supercomputers. The discussions include a high level of detail regarding the application performance bottlenecks and correlate with tiny pieces of code that are responsible for most the execution time. Although many analyzed applications have been compiled using aggressive compiler optimization flags, the insight obtained from the folding mechanism has turned into small code transformations based on widely-known optimization techniques that have improved the performance in some applications. In addition, this work also takes advantage of the power monitoring capabilities of recent processors and discusses the simultaneous performance and energy behavior on a selection of benchmarks and in-production applications.

# Contents

| Co  | ntent            | S                                                               |                                                                                                                                                                                                                                                                                                                                 |      |      | vii                                                                  |

|-----|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------------------------------------------------|

| Ta  | bles             |                                                                 |                                                                                                                                                                                                                                                                                                                                 |      |      | xi                                                                   |

| Fig | gures            |                                                                 |                                                                                                                                                                                                                                                                                                                                 |      |      | xiii                                                                 |

| Lis | stings           |                                                                 |                                                                                                                                                                                                                                                                                                                                 |      |      | xix                                                                  |

| Ac  | ronyr            | ns                                                              |                                                                                                                                                                                                                                                                                                                                 |      |      | xxi                                                                  |

| 1   | 1.1<br>1.2       | Perform<br>Contril<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5 | nance analysis butions Folding mechanism Applicability of performance models Source code and performance correlation Energy consumption analyses Detection of memory access patterns and their time evolution organization                                                                                                      | <br> | <br> | 3<br>5<br>5<br>6<br>7                                                |

| 2   | Para 2.1 2.2 2.3 | Amdah<br>Paralle                                                | gramming It's law I computer architecture taxonomy Ilization alternatives Message-passing paradigm Shared-memory paradigm Instruction-level parallelism 2.3.3.1 Pipelining 2.3.3.2 Out-of-order execution 2.3.3.3 Speculative execution 2.3.3.4 Superscalar and VLIW processors Vector processors Coprocessors and accelerators | <br> |      | . 10<br>. 11<br>. 12<br>. 14<br>. 17<br>. 18<br>. 19<br>. 20<br>. 21 |

| 3   | Perfe 3.1 3.2    | Descrip                                                         | e analysis btion                                                                                                                                                                                                                                                                                                                | <br> | <br> | . 26<br>. 26                                                         |

|   | 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | Perform<br>Measur<br>3.4.1<br>3.4.2<br>Perform<br>3.5.1<br>3.5.2<br>Source<br>Memory | Time-series profiles       37         Overview of simulation tools       37         nance analytics       38         ement collection techniques       41         Instrumentation alternatives       42         Sampling       46         nance metrics       46         Models based on performance counters       48         3.5.1.1 IBM CPIStack model       48         3.5.1.2 Intel Itanium2 model       49         3.5.1.3 Simple performance models using common performance counters       51         Active performance measurements       52         code references       52         y references       54         measurements       54 |

|---|----------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | The                                    | folding 1                                                                            | mechanism 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.1                                    |                                                                                      | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.2                                    |                                                                                      | tion of the mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 4.3                                    | Dotailo                                                                              | d performance counters evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.5                                    |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

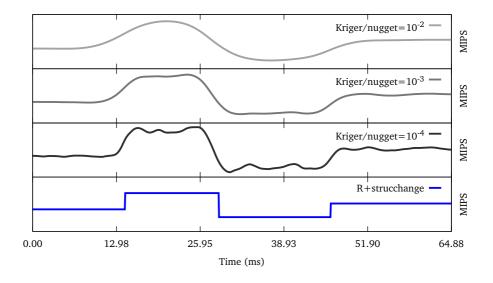

|   |                                        | 4.3.1                                                                                | Kriging fitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                        |                                                                                      | 4.3.1.1 Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                        | 4.3.2                                                                                | Piece-wise linear fitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                        |                                                                                      | 4.3.2.1 Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.4                                    | Correla                                                                              | tion of multiple performance counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        |                                                                                      | Applicability to performance models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.5                                    |                                                                                      | the source code attribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 4.5                                    | ACCUIAL                                                                              | This a phase determined has size a vice linear manner in a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                        | 4.5.1                                                                                | Using phases determined by piece-wise linear regressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                        |                                                                                      | 4.5.1.1 Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                        | 4.5.2                                                                                | Bio-inspired call-stack reconstruction 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                        |                                                                                      | 4.5.2.1 Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.6                                    | Detection                                                                            | ng time evolution of memory access patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 4.7                                    |                                                                                      | evolution of power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

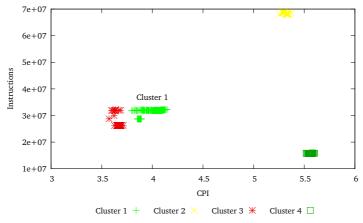

|   | 4.8                                    | Apolyoi                                                                              | s methodology for parallel applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                        |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 4.9                                    |                                                                                      | work for a productive node-level performance analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        | 4.9.1                                                                                | Trace-generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                        |                                                                                      | Framework data-flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

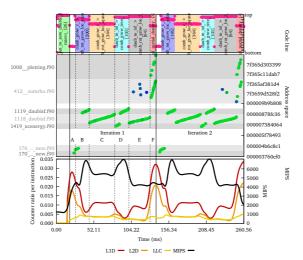

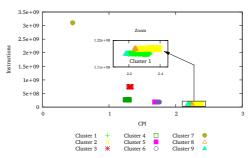

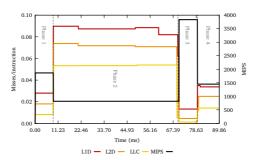

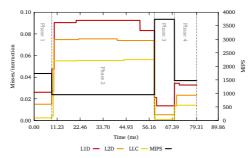

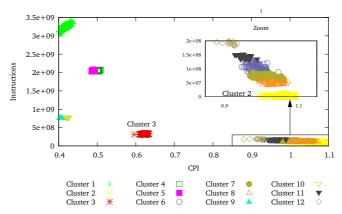

|   |                                        | 4.9.3                                                                                | Example of the result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5 | Prac                                   | tical use                                                                            | es of the framework 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.1                                    | <b>Applica</b>                                                                       | tion analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

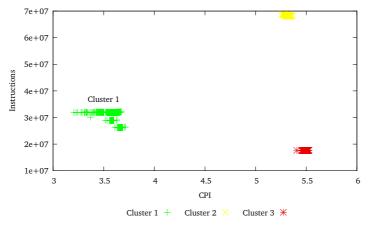

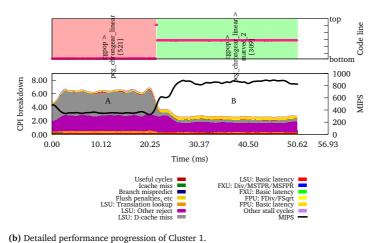

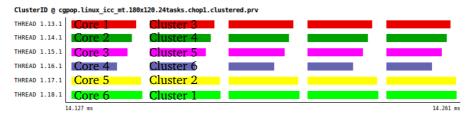

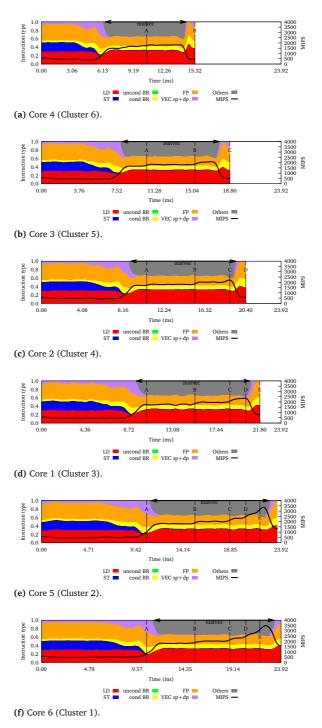

|   |                                        | 5.1.1                                                                                | CGPOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        | 0.1.1                                                                                | 5.1.1.1 Analysis in MareNostrum2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                        |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                        |                                                                                      | 5.1.1.2 Analysis on the impact of shared resources 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                        |                                                                                      | 5.1.1.3 Analysis of memory access patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                        | 5.1.2                                                                                | PMEMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                        | 5.1.3                                                                                | Mr. Genesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                        | 5.1.4                                                                                | BigDFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                        |                                                                                      | 5.1.4.1 Analysis in Juqueen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                        |                                                                                      | 5.1.4.2 Analysis of memory access patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                        | 5.1.5                                                                                | GTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                        |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                        | 5.1.6                                                                                | Arts_CF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                        | 5.1.7                                                                                | Nemo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                        | 5.1.8                                                                                | PEPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                        | 5.1.9                                                                                | Nest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                        | 5.1.10                                                                               | CESM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 5.2                | Simultaneous performance & power analysis       137         5.2.1       Serial benchmarks       138         5.2.1.1       Application of the DVFS techniques       138         5.2.2       Mr. Genesis       141         5.2.3       HydroC       146         5.2.4       SIESTA       148         Final remarks       149                                                                                                                                                                                                                                                                                 |

|----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | <b>Conc</b> 6.1    | lusions and future research directions153Conclusions6.1.1Performance metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 6.2                | 6.1.2 Source code time-evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 0.2                | Future research directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ap | pend               | 6.2.4 Syntactic-level application reconstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| U  | U.1                | guide       161         Quick start guide       161         U.1.1 Decompressing the package       161         U.1.2 Contents of the package       161         U.1.3 Quick run       162         U.1.3.1 Applied to manually instrumented regions       162         U.1.3.2 Applied to automatically characterized regions       163         U.1.4 Exploring the results       163         U.1.4.1 Using gnuplot       163         U.1.4.2 Using Paraver       165         Configuration, build and installation       166         U.2.1 Libtools package       166         U.2.2 Folding package       167 |

| G  | Gene               | rate a trace-file for the Folding Enabling the sampling mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | G.3                | Enlanding the sampling inectianism       109         Collecting the appropriate performance counters       170         G.2.1 Intel Haswell processors       170         G.2.2 Intel SandyBridge processors       171         G.2.3 Intel Nehalem processors       171         G.2.4 IBM Power8 processors       171         G.2.5 IBM Power7 processors       171         G.2.6 IBM Power5 processors       172         G.2.7 Other architectures       173         Capturing the call-stack at sample points       173                                                                                    |

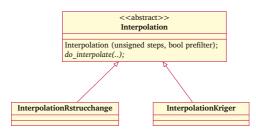

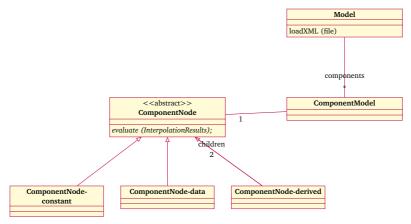

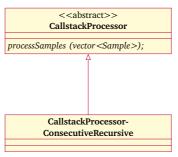

| Т  | Tool<br>T.1<br>T.2 | design175First component: trace-file processing175Second component: applying the folding176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A  | API<br>A.1         | Generation of input files for the Folding         181           A.1.1 Usage example         181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

R References 185

# **Tables**

| 1.1                               | Performance milestones of the Top500 list sorted by installation year                                                                                                                                                      | 3              |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5   | Flynn's taxonomy. Comparison of two versions of the same application that approximate the $\pi$ value. Comparison of two OpenMP versions that approximate the $\pi$ value. Comparison of scalar and vector codes for DAXPY | 15<br>17       |

|                                   | parallel programming                                                                                                                                                                                                       | 24             |

| 3.1<br>3.2                        | Instrumentation of entry and exit points of a routine                                                                                                                                                                      |                |

| 3.3<br>3.4<br>3.5                 | used                                                                                                                                                                                                                       | 47<br>48<br>55 |

|                                   | components.                                                                                                                                                                                                                | 55             |

| 4.1<br>4.2                        | Tabulated exemplification of the folded results                                                                                                                                                                            | 59             |

| 4.3                               | performance counter                                                                                                                                                                                                        |                |

| <ul><li>4.4</li><li>4.5</li></ul> | Tabulated exemplification of the folded results where samples include values of a performance counter and code line references                                                                                             |                |

|                                   | and its relationship with phases delimited in Figure 4.18                                                                                                                                                                  |                |

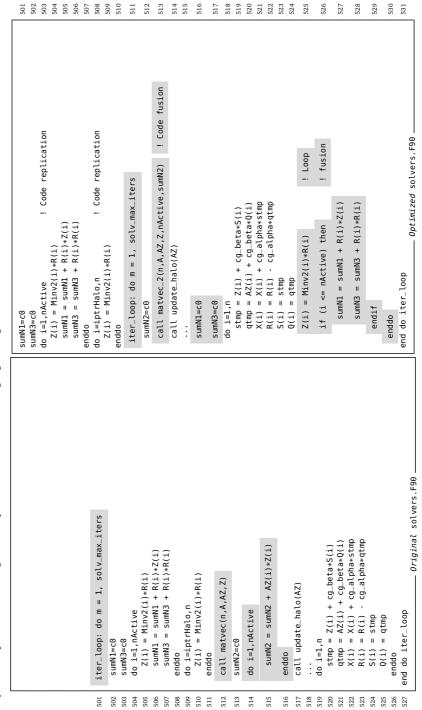

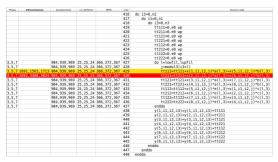

| 5.1<br>5.2<br>5.3<br>5.4          | Applications' characteristics.  Systems' characteristics.  Execution's characteristics.  Side-by-side comparison of both original and optimized CGPOP files. The highlighted                                               | 104            |

| 5.5                               | regions refer to the main differences between the two                                                                                                                                                                      |                |

| 5.6                               | Execution time for the CGPOP application using larger data sets                                                                                                                                                            |                |

| 5.7                               | Execution time for the PMEMD application using larger data sets                                                                                                                                                            |                |

| 5.8                               | Side-by-side comparison of both original and optimized Mr. Genesis files                                                                                                                                                   | 120            |

| 5.9                               | Execution time for the Mr. Genesis application using larger data sets                                                                                                                                                      |                |

| 5.10                              | Side-by-side comparison of both original and optimized PEPC files                                                                                                                                                          | 133            |

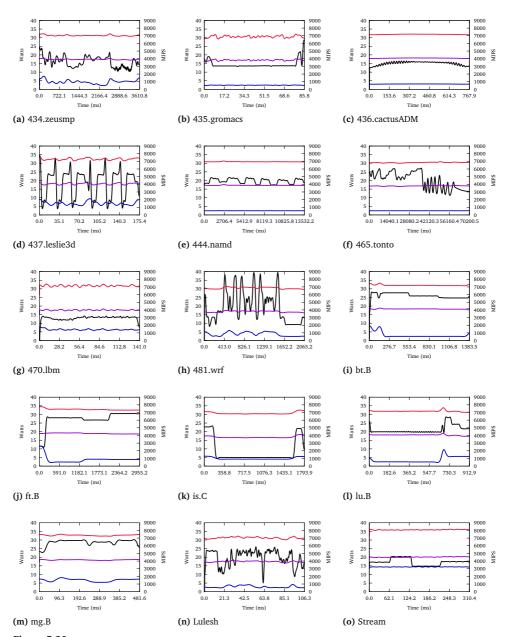

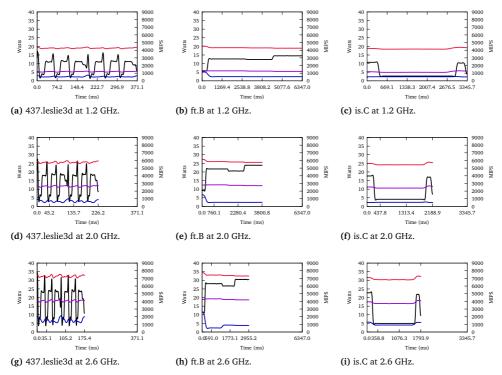

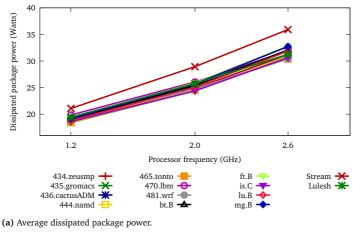

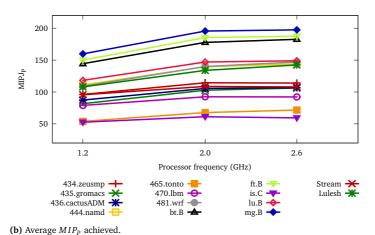

| 5.11 | Benchmarks used for the performance and power experiments and the location of        |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | the begin and end points to delimit the iterative part of the application            | 137 |

| 5.12 | Time and energy consumption for the selected benchmarks executing at different       |     |

|      | frequencies                                                                          | 142 |

| 5.13 | Performance and energy metrics for the selected benchmarks using different processor |     |

|      | frequencies                                                                          |     |

| 5.14 | Scalability of SIESTA. Energy is shown in KJoules and Duration is shown in seconds.  | 148 |

| 5.15 | Summary of the applications' modifications and their achieved overall improvement.   | 150 |

|      |                                                                                      |     |

| U.1  | Contents of the folding package                                                      | 162 |

|      |                                                                                      |     |

# **Figures**

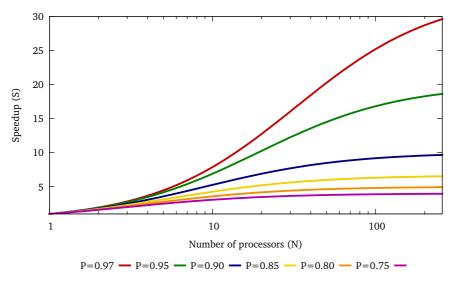

| 2.1  | _         | al representation of Amdani's law at different parallelization factors using up  | 10       |

|------|-----------|----------------------------------------------------------------------------------|----------|

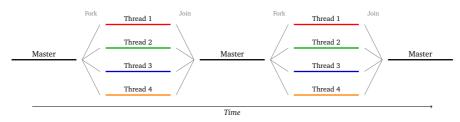

| 2.2  |           | processors                                                                       | 16       |

| 2.3  |           |                                                                                  | 18       |

|      |           | n of a pipelined execution of a sequence of instructions                         | 20       |

| 2.4  |           | execution with dependencies.                                                     |          |

|      |           | Needs to wait until instruction completes.                                       | 20       |

| 2.5  |           | Forwards instruction results as soon as they are generated                       | 20<br>21 |

| 2.5  | Tipellife | a execution of a sequence of histractions including a branch histraction         | 21       |

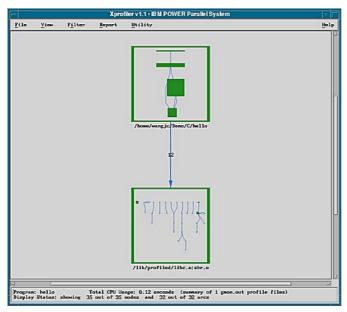

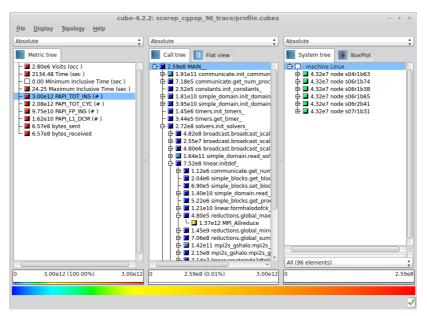

| 3.1  | Example   | e of results provided by the Xprofiler performance tool                          | 28       |

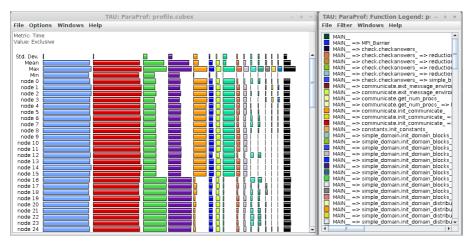

| 3.2  |           | e of results provided by the TAU performance tool                                | 30       |

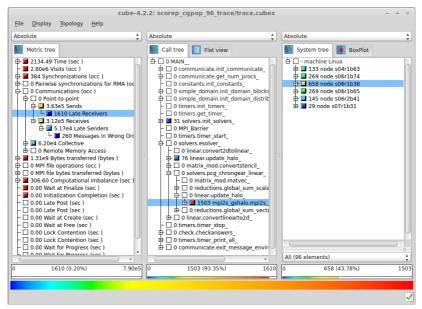

| 3.3  |           | a's Cube visualization tool                                                      | 31       |

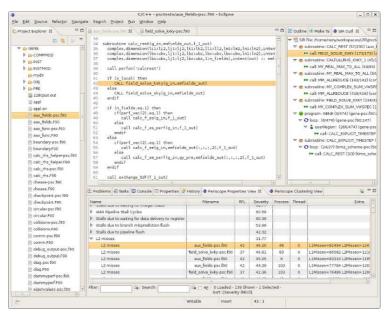

| 3.4  |           | be results shown in the Eclipse plugin                                           | 32       |

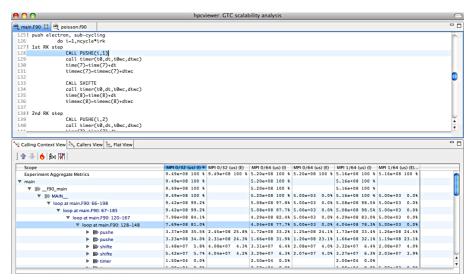

| 3.5  | Visualiz  | ation mechanisms available within the HPCToolkit suite                           | 33       |

|      | (a)       | HPCToolkit assessing the hot-spots in an application                             | 33       |

|      | (b)       | HPCToolkit showing a part of the execution of a parallel application             | 33       |

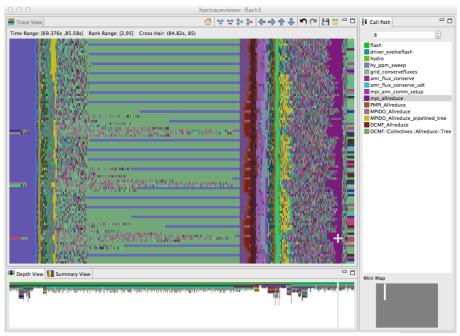

| 3.6  | Paraver   | representing trace-files as time-lines                                           | 34       |

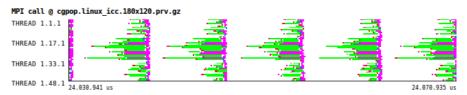

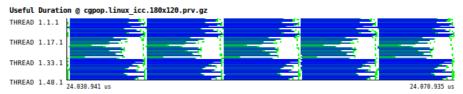

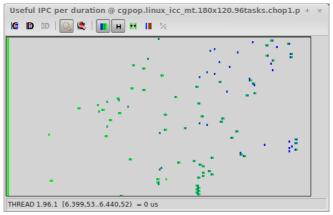

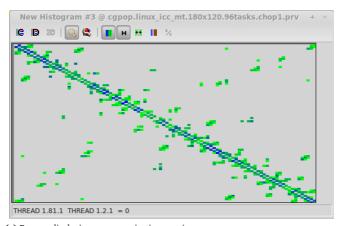

|      | (a)       | Paraver displaying MPI activity                                                  | 34       |

|      | (b)       | Paraver displaying a histogram                                                   | 34       |

| 3.7  | Paraver   | tabulating results                                                               | 35       |

|      | (a)       | Paraver displaying a profile                                                     | 35       |

|      | (b)       | Paraver displaying a histogram                                                   | 35       |

|      | (c)       | Paraver displaying a communication matrix                                        | 35       |

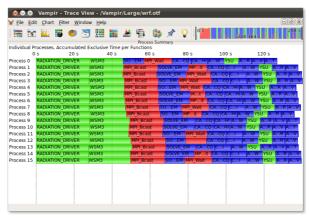

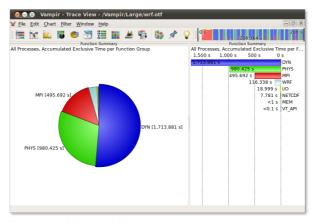

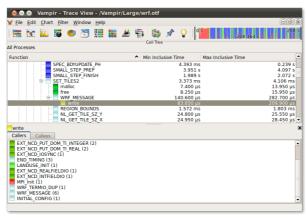

| 3.8  | Multiple  | e views from the Vampir performance tool-suite                                   | 36       |

|      | (a)       | Representation of the execution in a time-line                                   | 36       |

|      | (b)       | Summary of the executed function timings                                         | 36       |

|      | (c)       | Invocation hierarchy of instrumented routines                                    | 36       |

| 3.9  |           | e of results provided by the Scalasca performance tool                           | 39       |

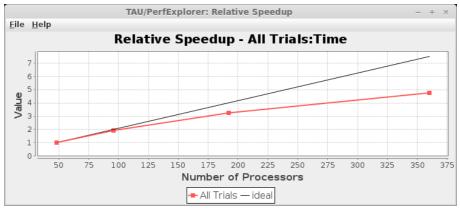

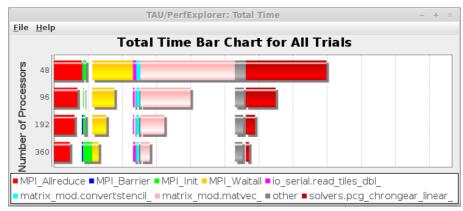

| 3.10 | PerfExp   | lorer showing an scalability analysis and its decomposition through experiments. |          |

|      | (a)       | Scalability analysis in PerfExplorer                                             | 41       |

|      | (b)       | Scalability decomposition as depicted in PerfExplorer                            | 41       |

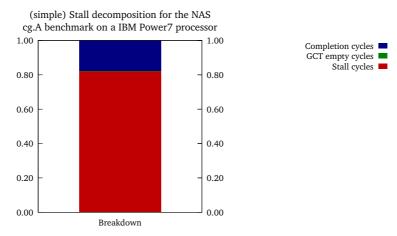

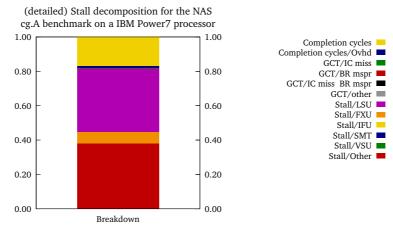

| 3.11 | Two dif   | ferent approaches on the IBM Power7 CPIstack breakdown model                     | 49       |

|      | (a)       | Basic Power7 breakdown model showing the three metrics of the first cate-        |          |

|      |           | gorical level                                                                    | 49       |

|      | (b)       | Detailed Power7 breakdown model showing the twelve metrics that compose          |          |

|      |           | the second categorical level                                                     | 49       |

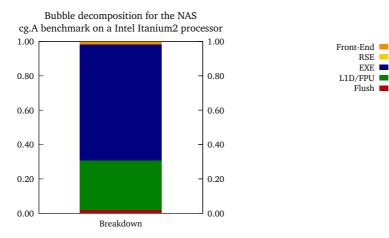

| 3.12 | Two bre   | eakdown models for the Intel Itanium2 processor                                  | 50       |

|      | (a)       | Decomposition of injected bubbles in the pipeline according to the pipeline      |          |

|      |           | component                                                                        | 50       |

| 2 12 | (b) Global stall decomposition                                                         |     |  |  |  |

|------|----------------------------------------------------------------------------------------|-----|--|--|--|

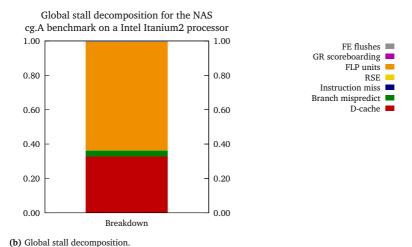

| 3.13 | (a) Instruction mix                                                                    |     |  |  |  |

|      | (a) Instruction link. (b) Architecture Impact.                                         | 51  |  |  |  |

|      | (b) Architecture impact                                                                | 31  |  |  |  |

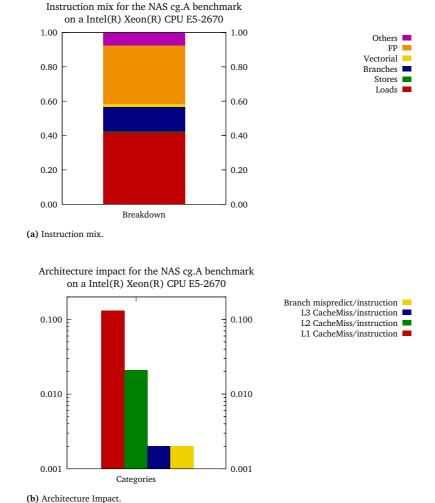

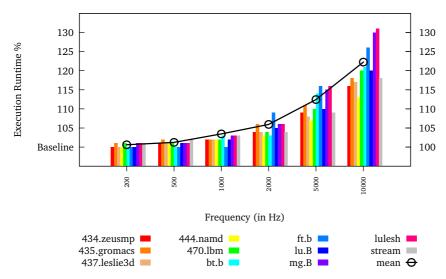

| 4.1  | Measured sampling overhead in the Extrae instrumentation package when tested           |     |  |  |  |

| 7.1  | using different benchmarks and sampling frequencies                                    | 58  |  |  |  |

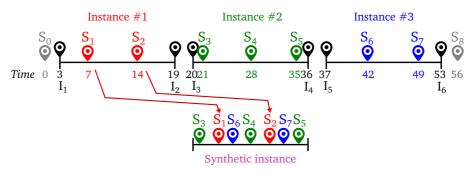

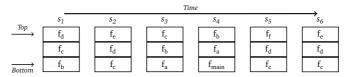

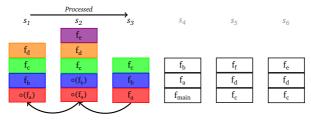

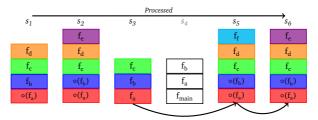

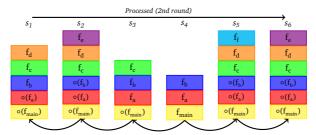

| 4.2  | Illustration of the folding process                                                    | 59  |  |  |  |

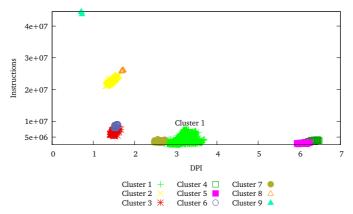

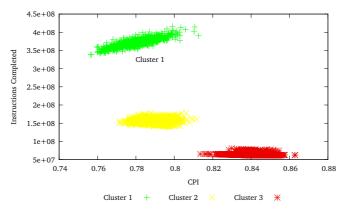

| 4.3  | Graphical representation of performance counter data from Table 4.2.                   | 61  |  |  |  |

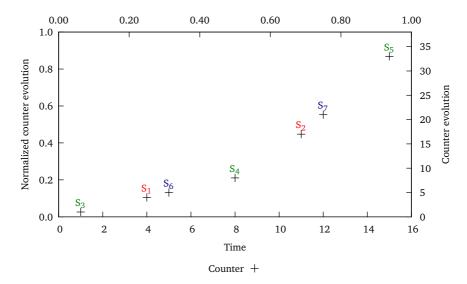

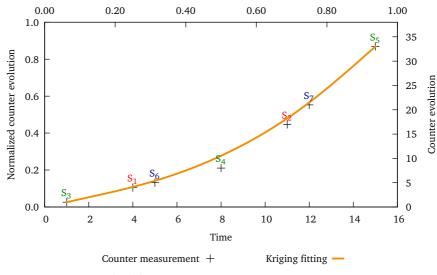

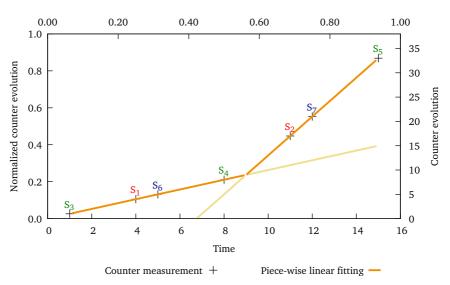

| 4.4  | Alternatives to fit hardware counters folded data                                      |     |  |  |  |

| 1. 1 | (a) Using a Gaussian process-based fitting.                                            |     |  |  |  |

|      | (b) Using piece-wise linear regressions.                                               | 63  |  |  |  |

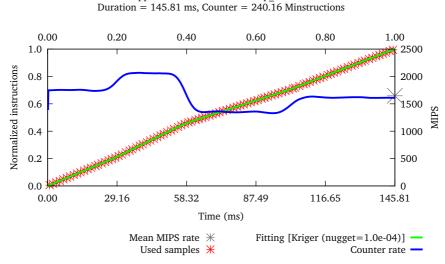

| 4.5  | Folding results for the instruction counter using Kriging interpolation on the Stream  | 00  |  |  |  |

| 7.5  | benchmark                                                                              | 65  |  |  |  |

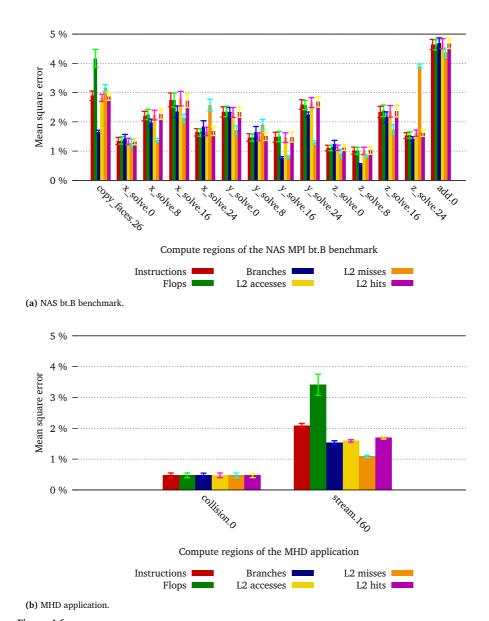

| 4.6  | Study of the mean square error on different applications comparing high frequency      | 05  |  |  |  |

| 1.0  | sampling and folded results with coarse grain sampling                                 | 67  |  |  |  |

|      | (a) NAS bt.B benchmark                                                                 | 67  |  |  |  |

|      | (b) MHD application.                                                                   | 67  |  |  |  |

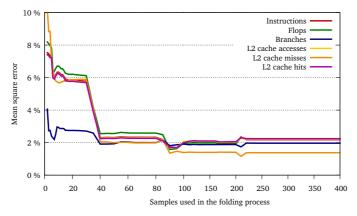

| 4.7  | Evaluation of how the number of samples involved in the folding mechanism influ-       | 07  |  |  |  |

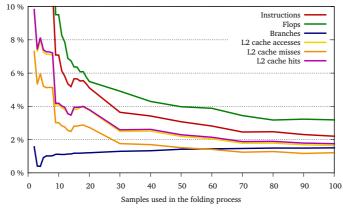

| 1.7  | ences on the mean square error when using Kriging interpolation                        | 68  |  |  |  |

|      | (a) Region x_solve.8 from NAS bt.B benchmark                                           | 68  |  |  |  |

|      | (b) Region copy faces.26 from NAS bt.B benchmark                                       | 68  |  |  |  |

|      | (c) Region stream.160 from MHD application                                             | 68  |  |  |  |

| 4.8  | Folding results for the instruction counter using piece-wise linear regressions on the | 00  |  |  |  |

| 1.0  | Stream benchmark                                                                       | 70  |  |  |  |

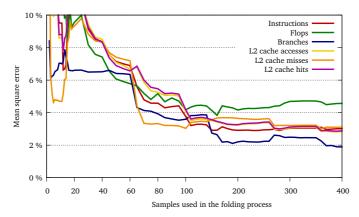

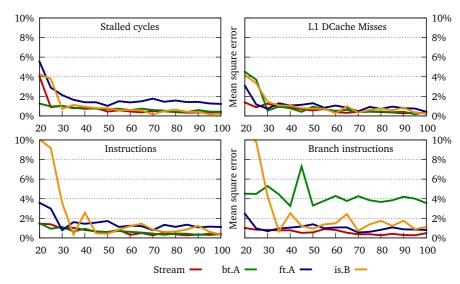

| 4.9  | Evaluation of how the number of samples involved in the folding mechanism influ-       | 70  |  |  |  |

| 1.7  | ences on the mean square error using piece-wise linear regressions                     | 71  |  |  |  |

| 4 10 | Visual comparison of the results obtained using Kriging and piece-wise linear regres-  | , 1 |  |  |  |

| 1.10 | sions for the Stream benchmark                                                         | 71  |  |  |  |

| 4 11 | Comparison of Mean Square Error obtained using Kriging and piece-wise linear           |     |  |  |  |

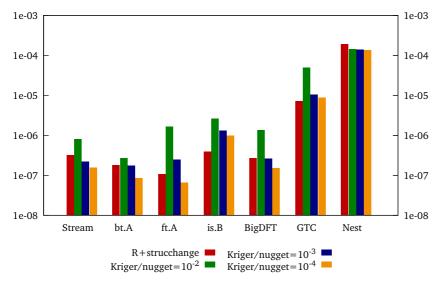

| 1.11 | regression on different applications.                                                  | 72  |  |  |  |

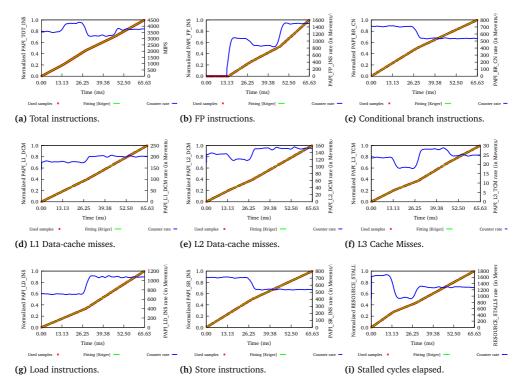

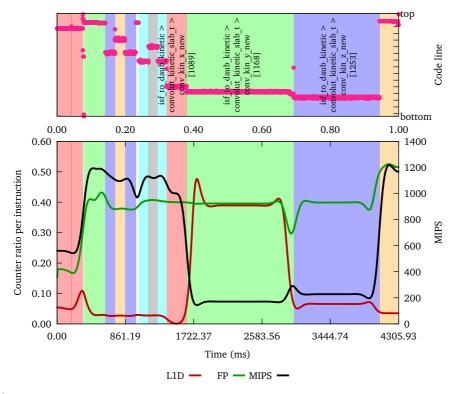

| 4 12 | Multiple performance views from the Stream benchmark                                   | 73  |  |  |  |

| 1.12 | (a) Total instructions                                                                 |     |  |  |  |

|      | (b) FP instructions.                                                                   |     |  |  |  |

|      | (c) Conditional branch instructions.                                                   | 73  |  |  |  |

|      | (d) L1 Data-cache misses                                                               | 73  |  |  |  |

|      | (e) L2 Data-cache misses.                                                              |     |  |  |  |

|      | (f) L3 Cache Misses                                                                    | 73  |  |  |  |

|      | (g) Load instructions                                                                  | 73  |  |  |  |

|      | (h) Store instructions.                                                                | 73  |  |  |  |

|      | (i) Stalled cycles elapsed                                                             | 73  |  |  |  |

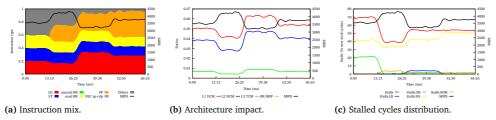

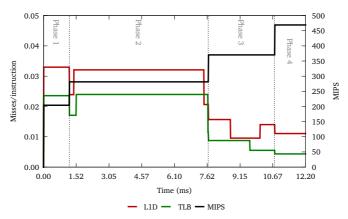

| 4.13 | Three different perspectives of the evolution of the main iteration of the Stream      | , - |  |  |  |

|      | benchmark                                                                              | 74  |  |  |  |

|      | (a) Instruction mix                                                                    | 74  |  |  |  |

|      | (b) Architecture impact                                                                | 74  |  |  |  |

|      | (c) Stalled cycles distribution                                                        | 74  |  |  |  |

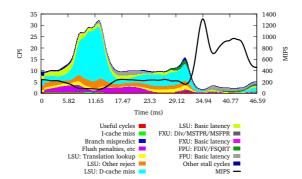

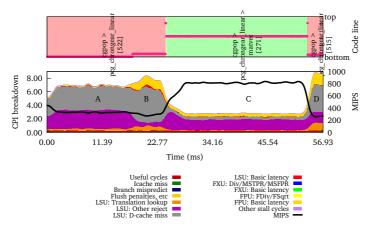

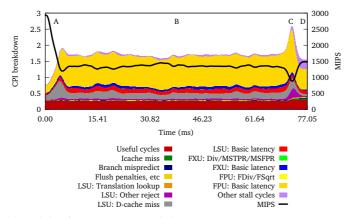

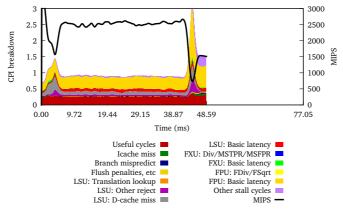

| 4.14 | Example of applying the IBM CPIstack performance model for the IBM Power5              |     |  |  |  |

|      | processor when analysing a compute region within the CCSM application                  | 75  |  |  |  |

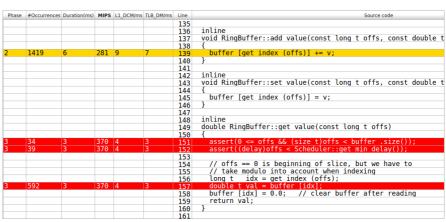

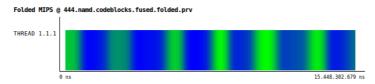

| 4.15 | MIPS rate shown in the GVIM editor in conjunction with the application source-code.    | 76  |  |  |  |

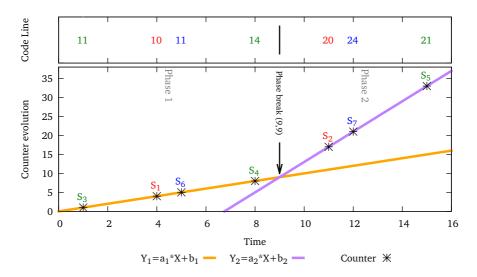

|      | Graphical representation from data contained in Table 4.4                              | 77  |  |  |  |

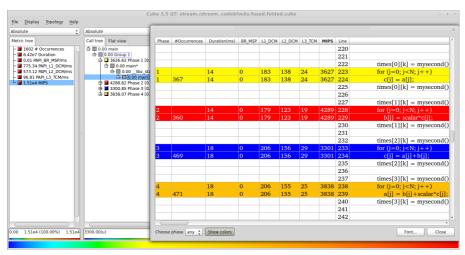

|      | CUBE visualizer correlating the Stream source code with branch mispredicts, L1 and     |     |  |  |  |

|      | L2 D-cache misses, L3 cache misses, and MIPS rates                                     | 78  |  |  |  |

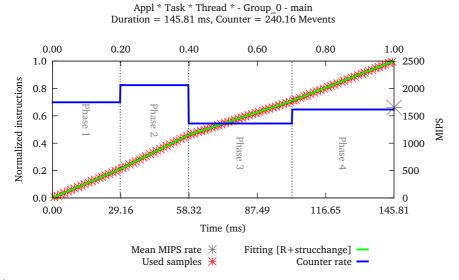

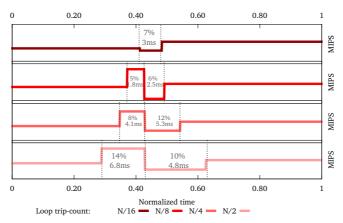

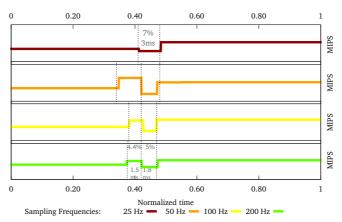

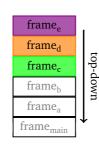

| 4.18 | Results of the folded instruction counter rate when changing some attributes of the    |     |  |  |  |

|      | execution of Stream.                                                                   | 79  |  |  |  |

|      | (a) Reducing the trip count of the central loop and using a sampling frequency         |     |  |  |  |

|      | of 25 Hz                                                                               | 79  |  |  |  |

|             | (b)        | Using different sampling frequencies with a trip count $N/16$ in the central loops                                                   | 79       |

|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | (c)        | Executing more iterations on the main loop with a trip count $N/16$ in the central loops and keeping the sampling frequency at 25 Hz | 79       |

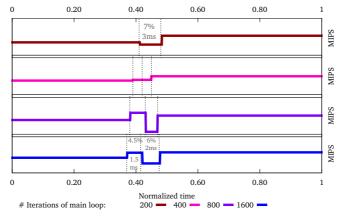

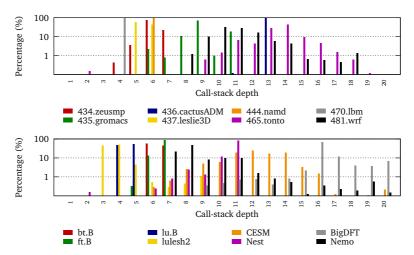

| 4 19        | Costs as   | sociated to the call-stack unwinding process.                                                                                        | 81       |

| т.17        | (a)        | Sampled call-stack depth histogram observed in applications.                                                                         | 81       |

|             | (b)        | Unwind overhead for many call-stack depths in several processors                                                                     | 81       |

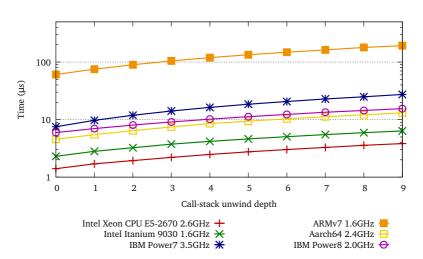

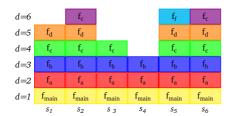

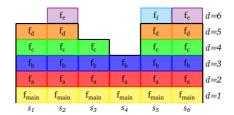

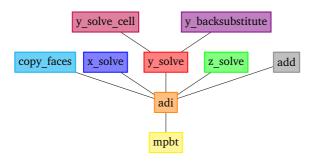

| 4 20        |            | ck tree when routine e is active and its selected subset                                                                             | 82       |

| 7.20        | (a)        | Call-stack frames activated are represented in color.                                                                                | 82       |

|             | (b)        | Top-down selection of 2 frames (in addition of the top of the call-stack) from                                                       | 02       |

|             | (D)        | the call-graph.                                                                                                                      | 82       |

| <b>4 21</b> | Evample    | e of alignment of a set of samples.                                                                                                  | 84       |

| 4.21        | (a)        | Samples as collected                                                                                                                 | 84       |

|             | (a)<br>(b) |                                                                                                                                      | 84       |

|             |            | Alignment of s <sub>1</sub> and s <sub>2</sub>                                                                                       |          |

|             | (c)        | Alignment of s <sub>2</sub> and s <sub>3</sub>                                                                                       | 84<br>84 |

|             | (d)        | Alignment of $s_3$ and $s_5$ , $s_6$                                                                                                 | 84       |

| 4 22        | (e)        |                                                                                                                                      |          |

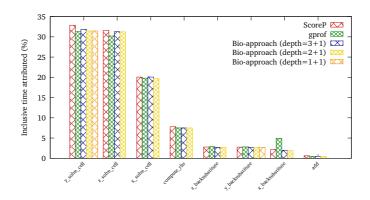

| 4.22        |            | decessing the alignment samples to choose the routines of interest.                                                                  | 85       |

|             | (a)        | Matrix representation of the call-stacks depicted in Figure 4.21e                                                                    | 85       |

| 4 22        | (b)        | Selection of routines of interest with a threshold \( \geq 2 \).                                                                     | 85       |

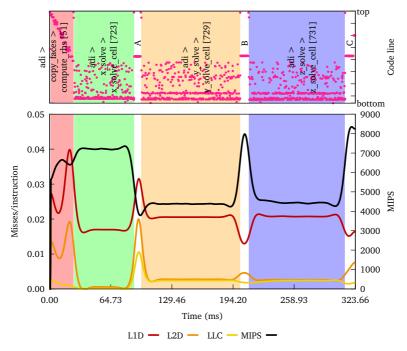

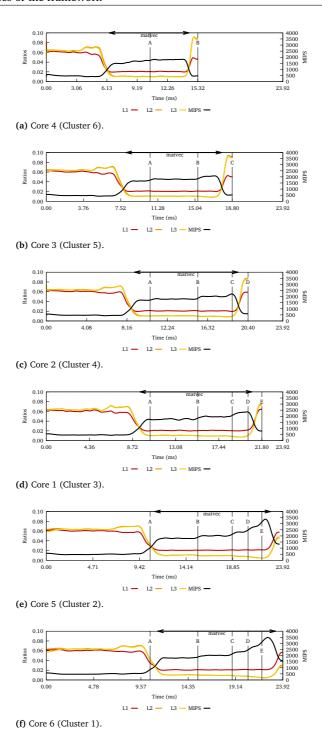

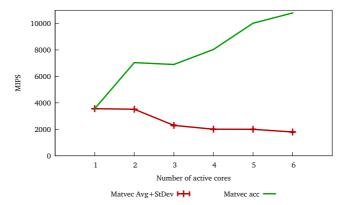

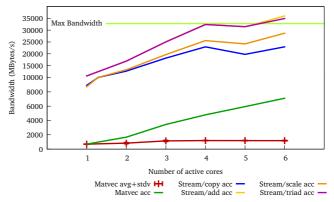

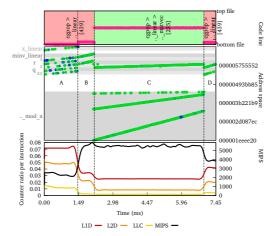

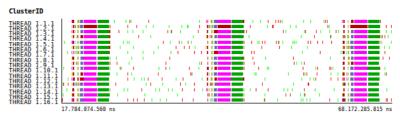

| 4.23        |            | code-references and performance metrics collocated for the MPI version of                                                            | 06       |

| 1 24        |            | bt.A benchmark                                                                                                                       | 86       |

| 4.24        |            |                                                                                                                                      | 07       |

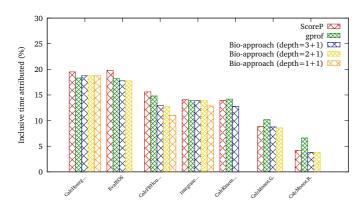

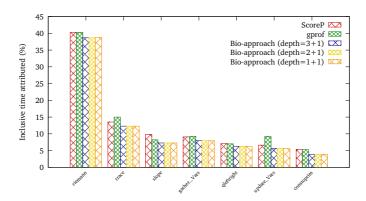

|             |            | f call-stack unwind when applied to different applications                                                                           | 87<br>87 |

|             | (a)        | NAS bt.B benchmark                                                                                                                   | 87       |

|             | (b)        | Lulesh mini-app.                                                                                                                     | 87       |

| 4 2E        | (c)        | HydroC application                                                                                                                   | 88       |

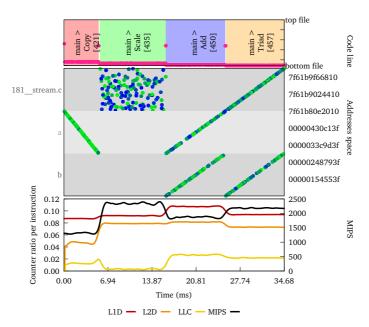

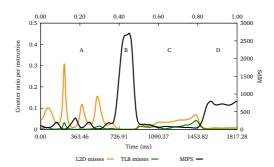

|             |            | s of the modified Stream benchmark. Triple correlation time-lines for the                                                            | 00       |

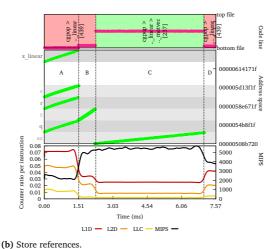

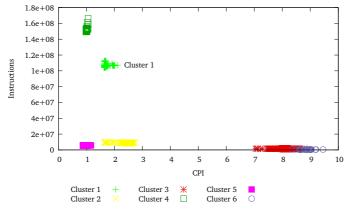

| 4.20        |            | eration: source code, addresses referenced and performance.                                                                          | 90       |

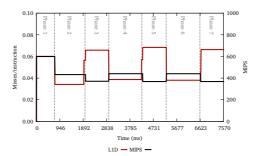

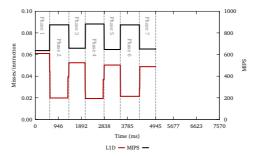

| 1 27        |            | on of the MIPS counter (top) and the package power consumption (bottom)                                                              | 90       |

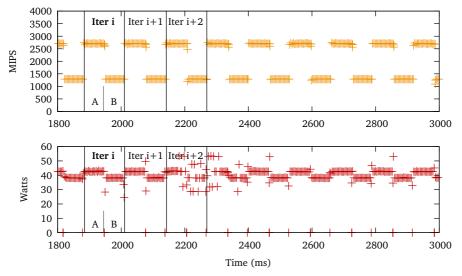

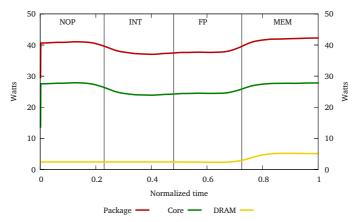

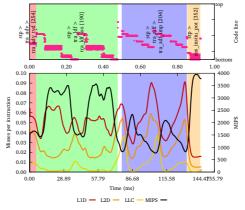

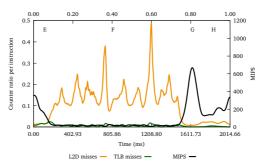

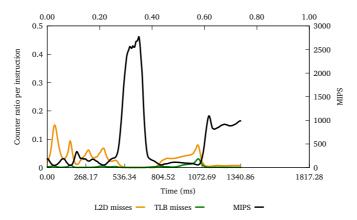

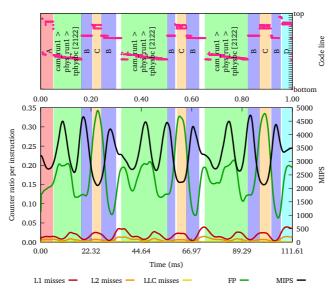

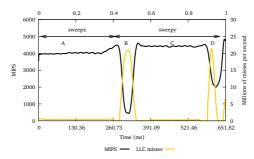

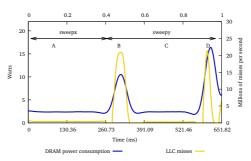

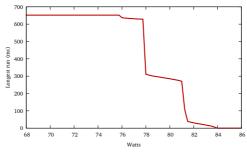

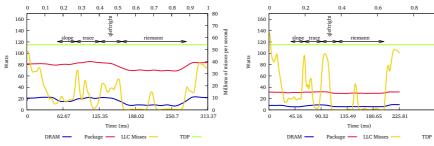

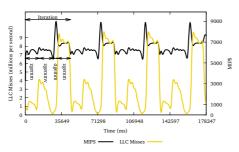

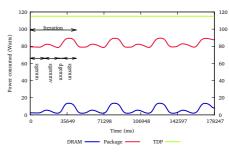

| 7.4/        |            | nchmark that executes two different kernels                                                                                          | 92       |

|             | (a)        | Raw evolution of the instruction rate executed (top) and the package power                                                           | 74       |

|             | (4)        | consumption (bottom)                                                                                                                 | 92       |

|             | (b)        | Superimposed MIPS (top) and power metrics (bottom) for the two different                                                             | /4       |

|             | (D)        | kernels                                                                                                                              | 92       |

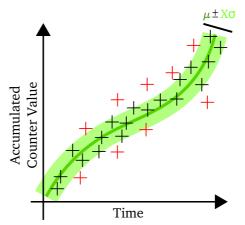

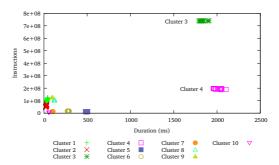

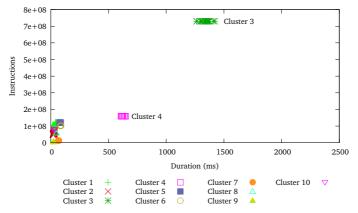

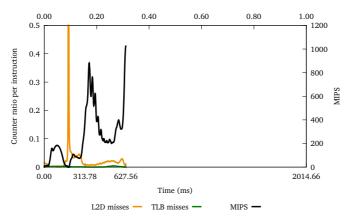

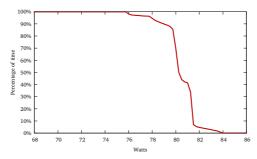

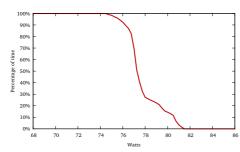

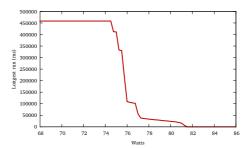

| 4 28        | Distance   | e-based instance filtering used in the folding.                                                                                      | 93       |

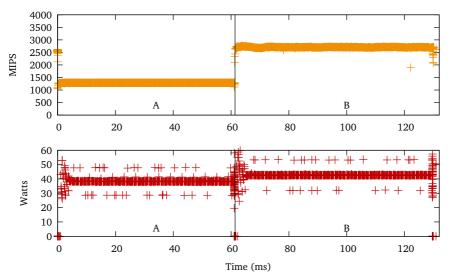

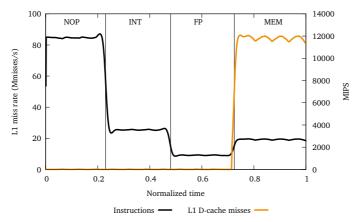

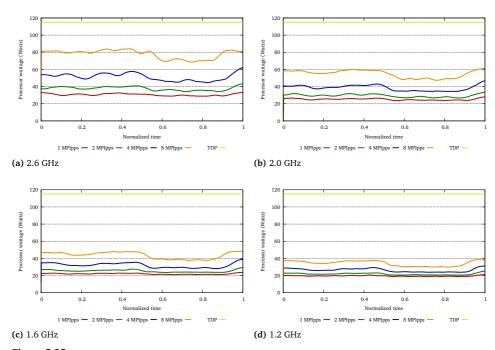

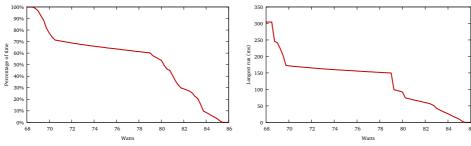

|             |            | f the folded results for performance and energy measurements by using a                                                              | /5       |

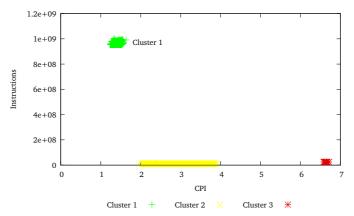

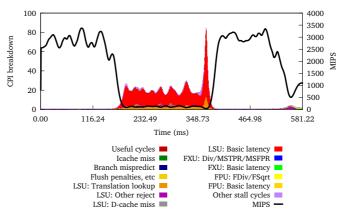

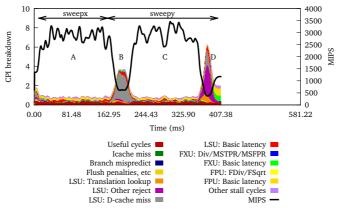

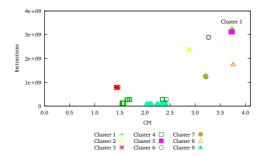

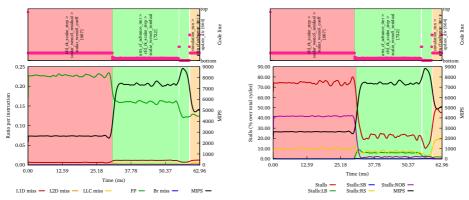

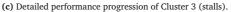

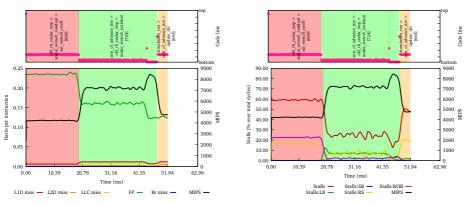

| 1.47        |            | enchmark that executes four different types of kernels                                                                               | 94       |