## SIMD@OpenMP: A Programming Model Approach to Leverage SIMD Features

**Ph.D. Dissertation**

Diego Luis Caballero de Gea

Department of Computer Architecture Universitat Politècnica de Catalunya

November 2015

Documento maquetado con TEXIS v.1.0+.

## SIMD@OpenMP: A Programming Model Approach to Leverage SIMD Features

### Diego Luis Caballero de Gea

A dissertation submitted to the Department of Computer Architecture at Universitat Politècnica de Catalunya in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Thesis Supervisors:

Prof. Xavier Martorell Bofill, Universitat Politècnica de Catalunya Dr. Alejandro Duran González, Intel Corporation

**Dissertation Pre-defence Committee:**

Prof. Jesús José Labarta Mancho, Universitat Politècnica de Catalunya Prof. Daniel Jiménez González, Universitat Politècnica de Catalunya Prof. Roger Espasa Sans, Universitat Politècnica de Catalunya

**External Reviewers:**

Dr. Ayal Zaks, Intel Corporation Dr. Alexandre Eichenberger, IBM

**Dissertation Defence Committee:**

Dr. Albert Cohen, INRIA Prof. Jesús José Labarta Mancho, Universitat Politècnica de Catalunya Dr. Ayal Zaks, Intel Corporation

Prof. Roger Espasa Sans, Universitat Politècnica de Catalunya Dr. Francesc Guim Bernat, Intel Corporation

Barcelona, November 2015

| Acta de qualificació de tes                                                | si doctoral                |                        | Curs acadèmic: 2015                         |

|----------------------------------------------------------------------------|----------------------------|------------------------|---------------------------------------------|

| Nom i cognoms<br>Diego Luis Caballero de Gea                               |                            |                        |                                             |

| Programa de doctorat                                                       |                            |                        |                                             |

| Arquitectura de Computadors<br>Unitat estructural responsable del programa |                            |                        |                                             |

| Departament d'Arquitectura de Comp                                         | outadors                   |                        |                                             |

|                                                                            |                            |                        |                                             |

| Resolució del Tribunal                                                     |                            |                        |                                             |

| Reunit el Tribunal designat a l'efecte,                                    | el doctorand / la do       | octoranda exposa       | a el tema de la seva tesi doctoral titulada |

| SIMD@OpenMP: A Programming Mo                                              |                            |                        |                                             |

|                                                                            |                            |                        |                                             |

| Acabada la lectura i després de dor                                        | nar resposta a les o       | qüestions formula      | ades pels membres titulars del tribunal,    |

| aquest atorga la qualificació:                                             |                            |                        |                                             |

| NO APTE                                                                    | APROVAT                    | NOTABLE                | EXCEL·LENT                                  |

| _                                                                          |                            |                        | _                                           |

| (Nom, cognoms i signatura)                                                 |                            | (Nom, cognoms i signat | tura)                                       |

| (non, orginal rolginational)                                               |                            | (noni, cognonic roigha |                                             |

| Drasidant/a                                                                |                            | Secretari/ària         |                                             |

| President/a<br>(Nom, cognoms i signatura)                                  | (Nom, cognoms i signatura) |                        | (Nom, cognoms i signatura)                  |

|                                                                            |                            |                        |                                             |

| Vocal                                                                      | Vocal                      |                        | Vocal                                       |

|                                                                            |                            |                        | 1.000                                       |

|                                                                            | d'/de                      | do                     |                                             |

| ;;                                                                         | _ u/ue                     | ue                     |                                             |

|                                                                            |                            |                        |                                             |

|                                                                            |                            |                        |                                             |

| El resultat de l'escrutini dels vots em                                    | esos nels membres          | s titulars del tribu   | nal, efectuat per l'Escola de Doctorat, a   |

| instància de la Comissió de Doctorat                                       | -                          |                        |                                             |

|                                                                            |                            |                        |                                             |

| L SÍ L NO                                                                  |                            |                        |                                             |

|                                                                            |                            |                        |                                             |

| (Nom, cognoms i signatura)                                                 |                            | (Nom, cognoms i signat | tura)                                       |

|                                                                            |                            |                        |                                             |

| President de la Comissió Permanent de l'I                                  | Escola de Doctorat         | Secretari de la Co     | omissió Permanent de l'Escola de Doctorat   |

|                                                                            |                            |                        |                                             |

|                                                                            |                            |                        |                                             |

Barcelona, \_\_\_\_\_ d'/de \_\_\_\_\_ de \_\_\_\_\_

## Abstract

SIMD instruction sets are a key feature in current general purpose and high performance architectures. In contrast to regular instructions that operate on scalar operands, SIMD instructions apply in parallel the same operation to a group of data, commonly known as vector. A single SIMD/vector instruction can, thus, replace a sequence of isomorphic scalar instructions. Consequently, the number of instructions can be significantly reduced leading to improved execution times.

However, SIMD instructions are not widely exploited by the vast majority of programmers. In many cases, taking advantage of these instructions relies on the compiler, domain-specific libraries and programming model support libraries used in the application. Nevertheless, despite the fact that compilers have a sophisticated vectorization technology, they struggle with the automatic vectorization of codes. Domain-specific libraries usually have support for limited SIMD architectures and programming model support libraries are not designed to exploit SIMD instructions. Advanced programmers are then compelled to exploit SIMD units by hand, using low-level hardware-specific intrinsics. This approach is cumbersome, error prone and not portable across SIMD architectures.

This thesis targets OpenMP to tackle the underuse of SIMD instructions from three main areas of the programming model: language constructions, compiler code optimizations and runtime algorithms. We choose the Intel Xeon Phi coprocessor (Knights Corner) and its 512-bit SIMD instruction set for our evaluation process. We make four contributions aimed at improving the exploitation of SIMD instructions in this scope.

Our first contribution describes a compiler vectorization infrastructure suitable for OpenMP. This vectorization infrastructure targets for-loops and whole functions. We define a set of attributes for expressions that determine how the code is vectorized. Our vectorization infrastructure also implements support for several vector features, such as vector function versioning, gather/scatter memory operations, vector math functions (SVML library), software prefetching and predicated vectorization. This infrastructure is proven to be effective in the vectorization of complex codes and it is the basis upon which we build the following two contributions.

The second contribution introduces a proposal to extend OpenMP 3.1 with SIMD parallelism. Essential parts of this work have become key features of the SIMD proposal included in OpenMP 4.0. We define the simd and simd for directives

that allow programmers to describe SIMD parallelism and guide the compiler in the vectorization process of loops and whole functions. Furthermore, we propose a set of optional clauses that leads the compiler to generate a more efficient vector code. These SIMD extensions improve the programming efficiency when exploiting SIMD resources. At the same time, they allow programmers to exploit the advanced vectorization technology available in many compilers, overcoming the limitations found in automatic approaches. Our evaluation on the Intel Xeon Phi coprocessor shows that our SIMD proposal allows the compiler to efficiently vectorize codes poorly or not vectorized automatically with the Intel C/C++ compiler. For instance, we obtain up to a speed-up of 4.40 in the *Distq* benchmark and up to 12.90 in the Mandelbrot benchmark over their auto-vectorized versions.

In the third contribution, we propose a vector code optimization that enhances *overlapped* vector loads. These vector loads redundantly read scalar elements from memory that have been already loaded by other vector loads. Our vector code optimization improves the memory usage of these accesses building a vector register cache and exploiting register-to-register instructions. Our proposal also includes a new clause (*overlap*) in the context of the SIMD extensions for OpenMP of our first contribution. This new clause allows enabling, disabling and tuning this optimization on demand. Our evaluation on the Intel Xeon Phi coprocessor reports up to 29% improvement over the execution time of benchmarks highly optimized for this architecture.

The last contribution tackles the exploitation of SIMD instructions in runtime algorithms for OpenMP. We focus on the barrier and reduction primitives and propose a new combined barrier and reduction tree scheme specifically designed to make the most of SIMD instructions. Our barrier algorithm takes advantage of simultaneous multi-threading technology (SMT) and it utilizes SIMD memory instructions in the synchronization process. These instructions allow checking and releasing multiple barrier thread counters at a time. Our tree reduction algorithm performs vertical SIMD reduction throughout the different levels of the tree and a final horizontal SIMD reduction in the root node. Our evaluation on the Intel Xeon Phi coprocessor shows that our SIMD approach outperforms by up to 70% and 76% the best barrier and reduction algorithms in the Intel OpenMP Runtime Library, respectively. We obtained up to an 11% performance gain in the Cholesky kernel and up to 26% and 30% in the NAS CG and MG benchmarks, respectively.

The four contributions of this thesis are an important step in the direction of a more common and generalized use of SIMD instructions. Our work is having an outstanding impact on the whole OpenMP community, ranging from users of the programming models (through OpenMP 4.0) to compiler and runtime implementations. Our proposals in the context of OpenMP improves the programmability of the programming model, the overhead of runtime services and the execution time of applications by means of a better use of SIMD resources available in modern multiand many-core architectures.

## Acknowledgments

This thesis has come to a successful end thanks to the help, support and disposal of many extraordinary people that I have had the opportunity to meet and work with.

Firstly, I would like to thank my advisors, Xavier Martorell and Alejandro Duran for going ahead with this project despite all the difficulties that have arisen over the last five years and for pushing me beyond my limits in order to get the best of me. They have always supported me, giving me freedom to develop my own ideas. Their valuable guidance has allowed me to get this far and to have an exciting future ahead. I am extremely grateful.

I would also like to thank my closer workmates as well as all the people working in the Computer Sciences department at Barcelona Supercomputing Center. I must highlight how much I have learned from them, since they are really outstanding and special people. I would especially like to mention Xavier Teruel, who was my mentor on my first work trip and conference. I also want to thank all the members of the Mercurium compiler group. Although the group is going through a difficult time, we have managed to push all our projects forward by means of collaborating with each other. My deepest gratitude goes to Roger Ferrer and Sara Royuela. I have been fortunate to work with the two most outstanding compiler engineers I have ever known and even better people. They truly feel passion for compilers and fortunately, they transmitted that passion to me. They both have selflessly devoted a lot of time to help me with this thesis. I thank them for their priceless advice and all the discussions we had. They both were co-authors in most of my articles and I do hope they also feel co-authors of this thesis. I am very proud and grateful to have worked with them.

I must also thank people from the Department of Computer Applications in Science and Engineering for their willingness to collaborate with our department. In particular, I thank Albert Farrès, Mauricio Hanzich, Josep de la Puente, Raul de la Cruz and Maria Jose Cela for sharing their expertise and wisdom with me.

My gratitude is also to Jesús Labarta, Daniel González, Roger Espasa, Ayal Zacks and Alexandre Eichenberger for reviewing this thesis. They kindly helped me improve its quality with their detailed analysis and brilliant comments, suggestions and discussion. I really appreciate it.

I shall also mention and express my gratitude to Anton Lokhmotov and his team from ARM Ltd. Cambridge. Anton was my supervisor during my Ph.D. internship. I had the opportunity of working with an exceptional compiler team that allowed me to know how things work in industry.

Last but not least, I would like to thank all my family and friends. Especially, to my closest family, my source of inspiration and motivation: Tony, María Josefa, Felipe, Juan José, Felipe, Aurora, Isabel María, Juanjito and Adrián.

This Ph.D. candidacy has been funded by the FI-DGR grant from Agència de Gestió d'Ajuts Universitaris i de Recerca (AGAUR), Barcelona Supercomputing Center, the European projects EnCORE (FP7-248647), DEEP (FP7-ICT-287530) and DEEP-ER (FP7-ICT-610476), the HiPEAC-3 Network of Excellence (ICT FP7 NoE 287759), the Spanish Ministry of Education under contracts TIN2007-60625, TIN2012-34557 (Computación de Altas Prestaciones VI) and CSD2007-00050 (Supercomputación y e-Ciencia), and the Generalitat de Catalunya under contracts 2009-SGR-980 and 2014-SGR-1051 (MPEXPAR, Models de Programació i Entorns d'eXecució PARal.lels). Any opinions, findings and conclusions or recommendations expressed in this thesis are those of the author and do not necessarily reflect the views of the funding agencies.

Diego Caballero,

Barcelona, 2015

# Contents

| AJ | bstra          | ct vii                                                                                      |  |

|----|----------------|---------------------------------------------------------------------------------------------|--|

| A  | ckno           | wledgments ix                                                                               |  |

| G  | Glossary xxiii |                                                                                             |  |

| 1  | Intr           | oduction 1                                                                                  |  |

|    | 1.1            | The Problem                                                                                 |  |

|    |                | 1.1.1 SIMD Exploitation at Programmer Level                                                 |  |

|    |                | 1.1.2 Runtime Services                                                                      |  |

|    | 1.2            | Our Approach         7                                                                      |  |

|    | 1.3            | Objectives of the Thesis                                                                    |  |

|    | 1.4            | Contributions                                                                               |  |

|    | 1.5            | $Context\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                           |  |

|    | 1.6            | Document Organization 10                                                                    |  |

| 2  | Bac            | kground 11                                                                                  |  |

|    | 2.1            | Master's Thesis Contributions                                                               |  |

|    | 2.2            | The OpenMP Programming Model 11                                                             |  |

|    |                | 2.2.1 Execution Model                                                                       |  |

|    |                | 2.2.2 Memory Model                                                                          |  |

|    |                | 2.2.3 Barriers and Reductions in OpenMP                                                     |  |

|    | 2.3            | The Mercurium Source-to-source Compiler 15                                                  |  |

|    |                | 2.3.1 Intermediate Representation                                                           |  |

|    |                | 2.3.2 Analysis Infrastructure                                                               |  |

|    | 2.4            | The Intel OpenMP Runtime Library 18                                                         |  |

|    |                | 2.4.1 Threads and Teams of Threads                                                          |  |

|    |                | 2.4.2 Synchronization Barrier                                                               |  |

|    |                | 2.4.3 Waiting Mechanism                                                                     |  |

|    |                | 2.4.4 Reductions                                                                            |  |

|    | 2.5            | The Intel Xeon Phi Coprocessor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 24$ |  |

| 3 | Sou | rce-to | -source Vectorization in the Mercurium Compiler     | 27   |

|---|-----|--------|-----------------------------------------------------|------|

|   | 3.1 | Introd | luction                                             | . 27 |

|   | 3.2 | Motiv  | ation                                               | . 28 |

|   | 3.3 | Object | tives                                               | . 29 |

|   | 3.4 | Vector | ization Infrastructure                              | . 29 |

|   |     | 3.4.1  | Vector data types and SIMD instructions             | . 29 |

|   |     | 3.4.2  | Representing Vector Operations                      | . 30 |

|   |     | 3.4.3  | Phases                                              | . 32 |

|   | 3.5 | Vector | ization Algorithm                                   | . 36 |

|   |     | 3.5.1  | Vectorization of Loops                              | . 37 |

|   |     | 3.5.2  | Vectorization of Functions                          | . 39 |

|   |     | 3.5.3  | Vector Attributes                                   | . 40 |

|   |     | 3.5.4  | Vectorization of Local Variables                    | . 41 |

|   |     | 3.5.5  | Vectorization of Statements                         | . 42 |

|   |     | 3.5.6  | Vectorization of Expressions                        | . 44 |

|   |     | 3.5.7  | Contiguity and Alignment in Memory Accesses         | . 46 |

|   |     | 3.5.8  | Function Versioning                                 | . 49 |

|   |     | 3.5.9  | Vector Math Library Support                         |      |

|   |     | 3.5.10 | Software Prefetcher                                 | . 51 |

|   | 3.6 | Perfor | mance Evaluation                                    | . 52 |

|   | 3.7 | Use C  | ase: A 3D Elastic Wave Propagator                   | . 53 |

|   | 3.8 | Chapt  | er Summary and Discussion                           | . 55 |

|   |     | 3.8.1  | Impact                                              | . 56 |

| 4 | SIM | ID Ext | ensions for OpenMP                                  | 57   |

|   | 4.1 | Introd | $\operatorname{luction}$                            | . 57 |

|   |     | 4.1.1  | Motivation                                          | . 57 |

|   |     | 4.1.2  | Objectives                                          | . 63 |

|   | 4.2 | Stand  | alone SIMD Directive                                | . 63 |

|   | 4.3 | SIMD   | Directive and Fork-Join Parallelism                 | . 65 |

|   |     | 4.3.1  | Loop Iteration Scheduling                           | . 66 |

|   |     | 4.3.2  | Distribution of Prologue/Epilogue Loop Iterations   |      |

|   | 4.4 | Option | nal Clauses                                         | . 66 |

|   |     | 4.4.1  | The aligned clause                                  | . 67 |

|   |     | 4.4.2  | The <i>suitable</i> clause                          | . 68 |

|   |     | 4.4.3  | The <i>uniform</i> and <i>linear</i> clauses        | . 69 |

|   |     | 4.4.4  | The vector length and the vector length for clauses | . 71 |

|   |     | 4.4.5  | The reduction clause                                | . 73 |

|   |     | 4.4.6  | The <i>mask</i> and <i>nomask</i> clauses           | . 74 |

|   |     | 4.4.7  | The unroll clause                                   | . 75 |

|   |     | 4.4.8  | The prologue and epilogue clauses                   | . 76 |

|   |     |        | The nontemporal clause                            |     |     |

|---|-----|--------|---------------------------------------------------|-----|-----|

|   |     | 4.4.10 | The <i>prefetch</i> and <i>noprefetch</i> clauses |     | 79  |

|   | 4.5 |        | Guidelines                                        |     |     |

|   | 4.6 | Legac  | y and Relationship of SIMD Extensions             |     | 81  |

|   | 4.7 | Evalu  | ation                                             |     | 83  |

|   |     | 4.7.1  | Goals and Interpretation of Results               |     | 83  |

|   |     | 4.7.2  | Benchmarks                                        |     | 84  |

|   |     | 4.7.3  | Environment and Methodology                       |     | 85  |

|   |     | 4.7.4  | Results                                           |     | 86  |

|   | 4.8 | Sumn   | nary and Discussion                               |     | 100 |

|   |     | 4.8.1  | Where is the limit?                               |     | 101 |

|   |     | 4.8.2  | OpenMP 4.0                                        | • • | 102 |

| 5 | Opt | imizir | ng Overlapped Vector Memory Accesses              |     | 105 |

|   | 5.1 | Introd | luction                                           |     | 105 |

|   |     | 5.1.1  | Motivation                                        |     | 105 |

|   |     | 5.1.2  | Objectives                                        |     | 109 |

|   | 5.2 | Overv  | riew of the Overlap Optimization                  |     |     |

|   | 5.3 | Forma  | al Framework and Definitions                      |     | 110 |

|   |     | 5.3.1  | Preliminaries                                     |     | 111 |

|   |     | 5.3.2  | Overlap Relations                                 |     | 112 |

|   |     | 5.3.3  | Overlap Groups                                    |     | 112 |

|   | 5.4 | The O  | Overlap Optimization                              |     | 114 |

|   |     | 5.4.1  | Overlap Group Constraints                         |     | 115 |

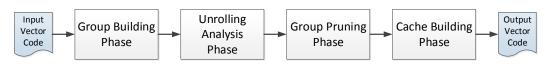

|   |     | 5.4.2  | Group Building Phase                              |     | 115 |

|   |     | 5.4.3  | Unrolling Analysis Phase                          |     | 116 |

|   |     | 5.4.4  | Group Pruning Phase                               |     | 118 |

|   |     | 5.4.5  | Cache Building Phase                              |     | 120 |

|   | 5.5 | The O  | overlap Optimization in OpenMP                    |     | 122 |

|   | 5.6 | User ( | Guidelines                                        |     | 123 |

|   | 5.7 | Imple  | mentation                                         |     | 125 |

|   | 5.8 | Evalu  | ation                                             |     | 126 |

|   |     | 5.8.1  | Benchmarks                                        |     | 126 |

|   |     | 5.8.2  | Environment and Methodology                       |     | 127 |

|   |     | 5.8.3  | Generic Optimizations                             |     | 128 |

|   |     | 5.8.4  | Overlap Optimization Performance                  |     | 131 |

|   | 5.9 | Chapt  | ter Summary and Discussion                        |     | 133 |

|   |     | 5.9.1  | Automatic Application of the Overlap Optimization |     | 134 |

|   |     | 5.9.2  | Incorporation into the OpenMP Standard            |     | 135 |

| 6 | SIM | ID Syn | chronization Barrier and Reductions in OpenMP     |     | 137 |

|   | 6.1 | Introduction                                          | 137 |

|---|-----|-------------------------------------------------------|-----|

|   |     | 6.1.1 Motivation                                      | 137 |

|   |     | 6.1.2 Objectives                                      | 141 |

|   | 6.2 | SIMD Combining Tree Barrier Algorithm                 | 141 |

|   |     | 6.2.1 Barrier Scheme                                  | 142 |

|   |     | 6.2.2 Gather Phase                                    | 143 |

|   |     | 6.2.3 Release Phase                                   | 145 |

|   | 6.3 | SIMD Reduction Algorithm                              | 146 |

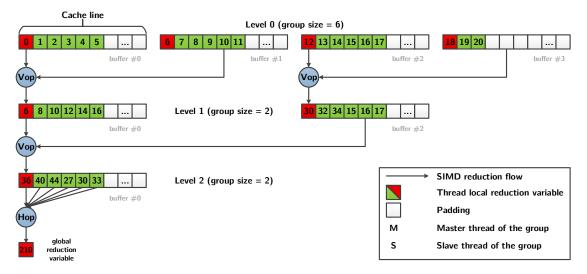

|   |     | 6.3.1 Reduction Scheme                                | 146 |

|   |     | 6.3.2 SIMD Reduction Steps                            | 148 |

|   | 6.4 | Implementation on the Intel OpenMP RTL                | 150 |

|   |     | 6.4.1 SIMD Barrier                                    | 150 |

|   |     | 6.4.2 SIMD Reductions                                 | 154 |

|   | 6.5 | Evaluation                                            | 158 |

|   |     | 6.5.1 Benchmarks                                      | 159 |

|   |     | 6.5.2 Environment and Methodology                     | 161 |

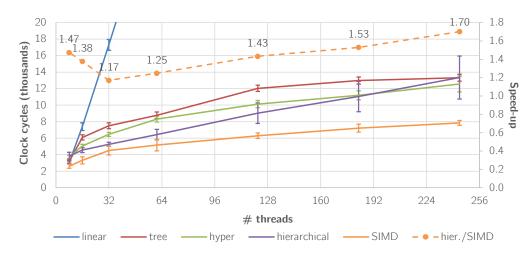

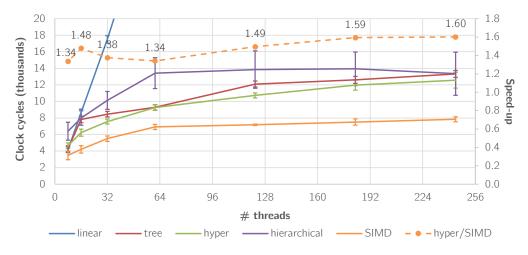

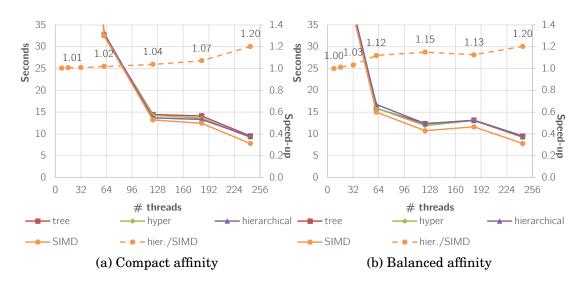

|   |     | 6.5.3 Calibration Phase                               | 162 |

|   |     | 6.5.4 Performance Results                             | 168 |

|   | 6.6 | Chapter Summary and Discussion                        | 179 |

|   |     | 6.6.1 Dissemination Barrier versus SIMD Barrier       | 179 |

|   |     | 6.6.2 Alternative Tree Barrier Implementations        | 180 |

|   |     | 6.6.3 Packing Multiple SIMD Reductions per Cache Line | 180 |

|   |     | 6.6.4 SIMD Reductions in User-defined Reductions      | 181 |

| 7 | Rel | ated Work                                             | 183 |

|   | 7.1 | Vectorization                                         | 183 |

|   |     | 7.1.1 Programming Technology for Vectorization        | 184 |

|   |     | 7.1.2 Source-to-source Vectorization Infrastructures  | 185 |

|   |     | 7.1.3 Vectorization Techniques                        | 187 |

|   | 7.2 | The Overlap Optimization                              | 188 |

|   | 7.3 | Synchronization Barrier and Reduction Algorithms      | 190 |

|   |     | 7.3.1 Synchronization Barriers                        | 190 |

|   |     | 7.3.2 Reductions                                      | 191 |

| 8 | Cor | nclusions and Future Work                             | 195 |

|   | 8.1 | Conclusions of the Thesis                             | 195 |

|   | 8.2 | Publications                                          | 196 |

|   | 8.3 | Impact                                                | 197 |

|   | 8.4 | Future Work                                           | 198 |

| Α | Ben | nchmarks Source Code                                  | 201 |

### Bibliography

207

# **List of Figures**

| 1.1  | Vector length evolution of some SIMD instruction sets (time axis is                                                                                     |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | just illustrative and it is not to scale)                                                                                                               | 2   |

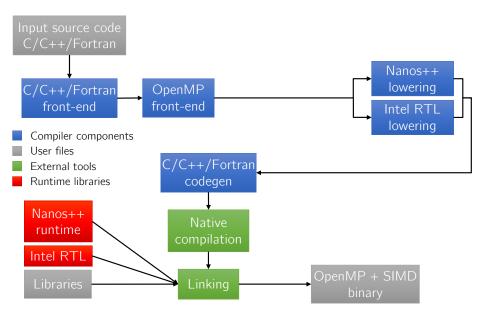

| 2.1  | Mercurium compilation diagram                                                                                                                           | 15  |

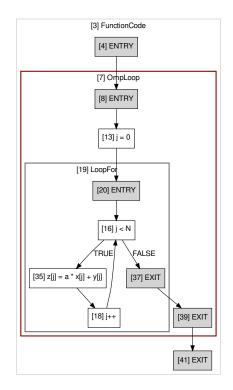

| 2.2  | Example of a parallel control flow graph of the Saxpy computation $\ . \ .$                                                                             | 17  |

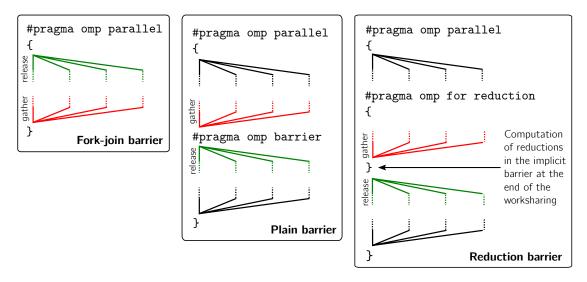

| 2.3  | Gather (red) and release (green) phases of the fork-join, plain and reduction barriers                                                                  | 20  |

| 2.4  | Intel Xeon Phi coprocessor diagram (Knights Corner)                                                                                                     | 25  |

| 3.1  | Mercurium compilation diagram including new phases of the vector-<br>ization infrastructure (original diagram is shown in Figure 2.1, Sec-<br>tion 2.3) | 33  |

| 3.2  | Internal scheme of the Vectorizer phase                                                                                                                 | 34  |

| 3.3  | Internal scheme of the Vector Lowering phase                                                                                                            | 35  |

| 3.4  | Example of prologue, main vector and epilogue loops (b) resulting                                                                                       |     |

|      | from the vectorization of a simple loop (a), assuming 16-byte vector                                                                                    | ~ = |

| 3.5  | units and VF = 4                                                                                                                                        | 37  |

|      | loop, and the vectorization factor, respectively                                                                                                        | 39  |

| 3.6  | Rules for the vectorization of basic data types. Other data types have                                                                                  |     |

|      | limited support or are not supported in our implementation                                                                                              | 41  |

| 3.7  | Some of the rules for the vectorization of an <i>Assignment</i> node                                                                                    | 44  |

| 3.8  | Some of the rules for the vectorization of value expressions                                                                                            | 45  |

| 3.9  | Some rules used in the computation of the <i>adjacent</i> attribute for the subscript expression of an array subscript                                  | 48  |

| 3.10 | Some simplified rules used in the computation of the alignment (in elements) caused by subscript expression of an array subscript                       | 49  |

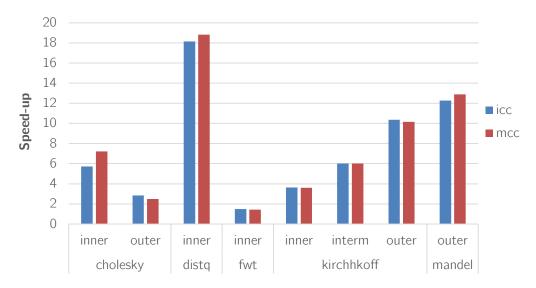

| 3.11 | Performance summary of our Mercurium vectorization infrastructure                                                                                       |     |

|      | (mcc). Baseline scalar version. Intel Xeon Phi coprocessor (1 core, 4 threads/core)                                                                     | 53  |

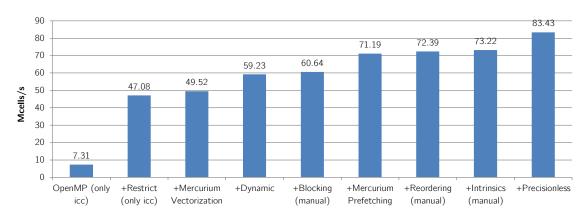

| 3.12         | Absolute performance evolution (Mcells/s) of a Full Anisotropic Elas-<br>tic Wave Propagator after applying incrementally a set of optimiza-<br>tions [23]. Run on the Intel Xeon Phi coprocessor using 61 cores and                                                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 4 threads/core (244 threads in total)                                                                                                                                                                                                                                                                                   |

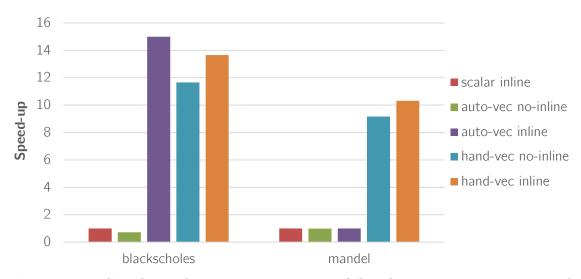

| 4.1          | Speed-up of auto-vectorization and hand-vectorization versions of Black-<br>scholes and Mandelbrot benchmarks with inlined and not inlined func-<br>tions. Baseline: scalar version with inlined functions. Intel C/C++<br>Compiler 13.1.3. Running on an Intel Xeon Phi coprocessor using 1<br>core and 4 threads/core |

| 4.2          | C/C++ syntax of the standalone simd construct                                                                                                                                                                                                                                                                           |

| 4.3          | C/C++ syntax of the SIMD-for construct                                                                                                                                                                                                                                                                                  |

| 4.4          | Syntax of the <i>aligned</i> clause                                                                                                                                                                                                                                                                                     |

| 4.5          | Syntax of the <i>suitable</i> clause                                                                                                                                                                                                                                                                                    |

| 4.6          | Syntax of the <i>uniform</i> and <i>linear</i> clauses                                                                                                                                                                                                                                                                  |

| 4.7          | Syntax of the vector length and the vector length for clauses                                                                                                                                                                                                                                                           |

| 4.8          | Syntax of the <i>reduction</i> clause                                                                                                                                                                                                                                                                                   |

| 4.9          | Examples of the <i>reduction</i> clause                                                                                                                                                                                                                                                                                 |

| 4.10         | Syntax of the <i>unroll</i> clause                                                                                                                                                                                                                                                                                      |

|              | Syntax of the <i>prologue</i> and <i>epilogue</i> clauses                                                                                                                                                                                                                                                               |

|              | Syntax of the <i>nontemporal</i> clause                                                                                                                                                                                                                                                                                 |

|              | Syntax of the <i>prefetch</i> and <i>noprefetch</i> clauses                                                                                                                                                                                                                                                             |

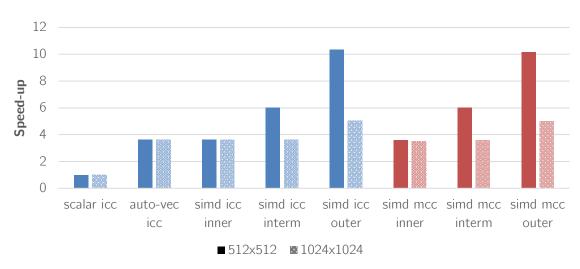

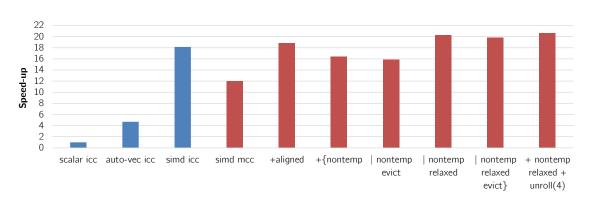

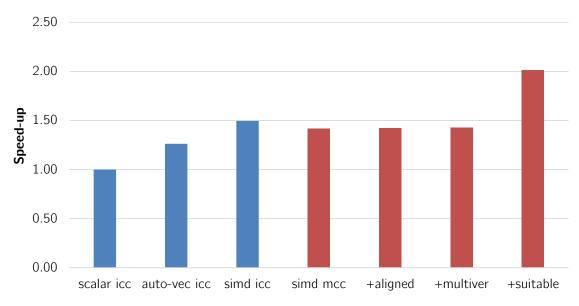

|              | Speed-up of the Kirchhoff benchmark (float data types) $87$                                                                                                                                                                                                                                                             |

| 4.15         | Speed-up of the Distsq benchmark (float data types)                                                                                                                                                                                                                                                                     |

| 4.16         | Speed-up of the Cholesky benchmark (float data types) 91                                                                                                                                                                                                                                                                |

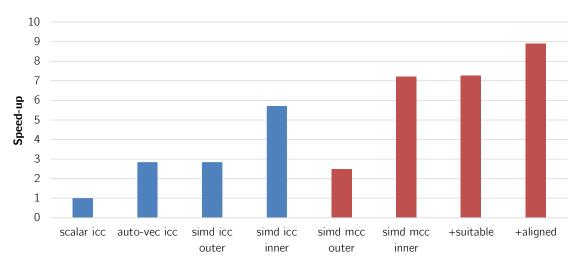

| 4.17         | Speed-up of the Nbody benchmark (float data types)                                                                                                                                                                                                                                                                      |

|              | Code size variation of the main functions of the Nbody benchmark $\ . \ . \ 95$                                                                                                                                                                                                                                         |

|              | Speed-up of the FastWalsh benchmark (float data types) $\ldots \ldots 97$                                                                                                                                                                                                                                               |

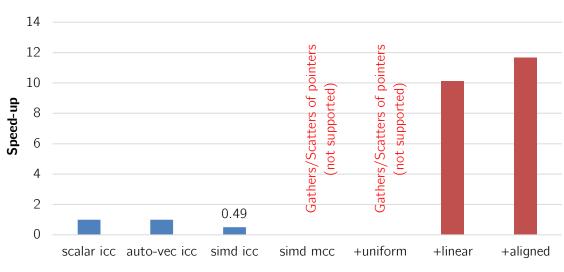

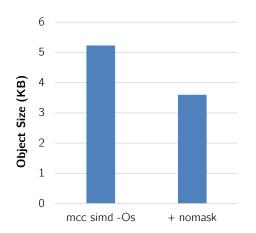

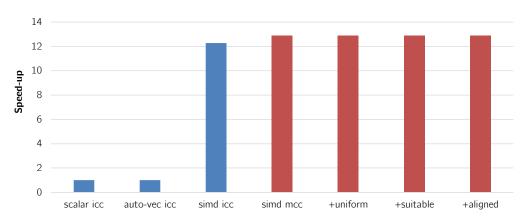

|              | Speed-up of the Mandelbrot benchmark (int data types) 99                                                                                                                                                                                                                                                                |

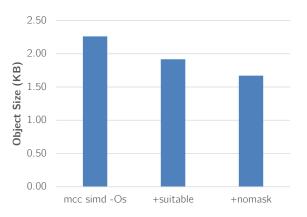

| 4.21         | Code size variation of the main functions of the Mandelbrot benchmark 99                                                                                                                                                                                                                                                |

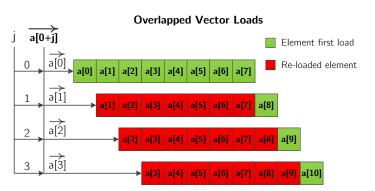

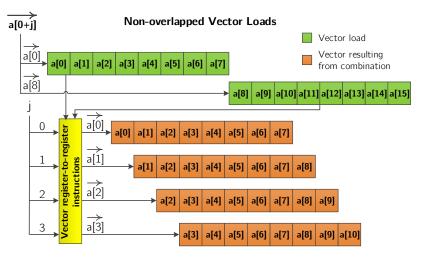

| $5.1 \\ 5.2$ | Moving Average motivating example                                                                                                                                                                                                                                                                                       |

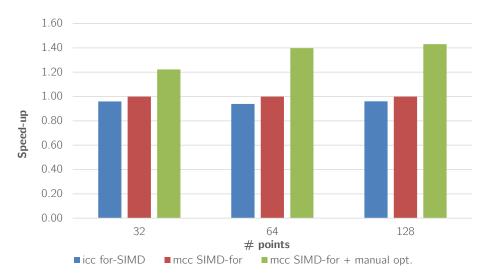

| 0.2          | Phi coprocessor 7120. Running with 183 threads (61 cores, 3 threads/-<br>core. The best experimental thread configuration). N=536M, points=128.                                                                                                                                                                         |

|              | Baseline mcc SIMD-for                                                                                                                                                                                                                                                                                                   |

| 5.3          | The overlap optimization applied to vector loads of the array a in Figure 5.1                                                                                                                                                                                                                                           |

| 5.4          | Code of a 2D Jacobi solver for heat diffusion                                                                                                                                                                                                                                                                           |

| 5.5          | Phases of the overlap optimization                                                                                                                                                                                                                                                                                      |

| 5.6          | Graphical representation of $dist$ for increasing $UF$ in the Moving Av-                                                                                                                                                                                                                                                |

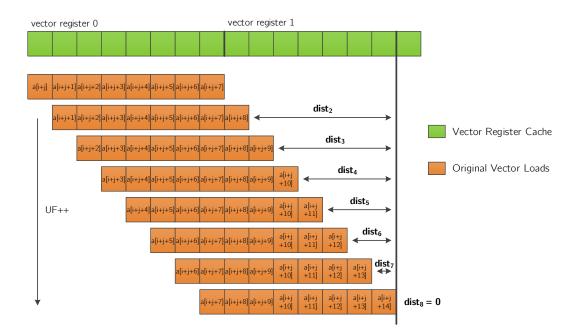

| 2.0          | erage example                                                                                                                                                                                                                                                                                                           |

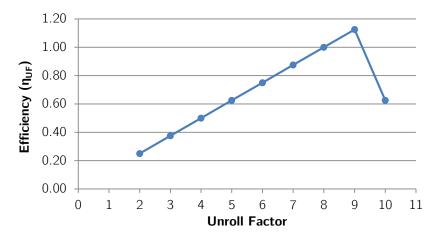

| 5.7  | Evolution of efficiency $(\eta_{UF})$ for increasing $UF$ in the Moving Average example                                                                                                                                                                                                                                                                                                                   | 119   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.8  | The overlap group pruning algorithm                                                                                                                                                                                                                                                                                                                                                                       | 120   |

| 5.9  | The cache building algorithm                                                                                                                                                                                                                                                                                                                                                                              | 120   |

| 5.10 | Example of the overlap clause for Figure 5.1                                                                                                                                                                                                                                                                                                                                                              | 122   |

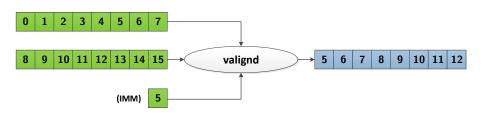

| 5.11 | Example of the functionality of the <i>valignd</i> instruction                                                                                                                                                                                                                                                                                                                                            | 125   |

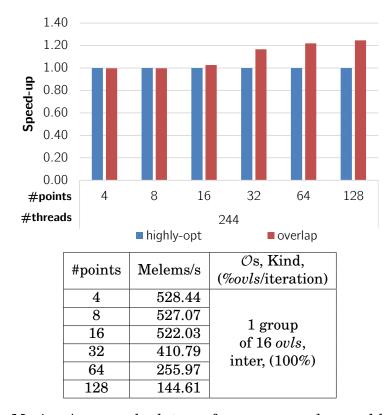

| 5.12 | Moving Average absolute performance, speed-up and kind of groups (244 threads)                                                                                                                                                                                                                                                                                                                            | 130   |

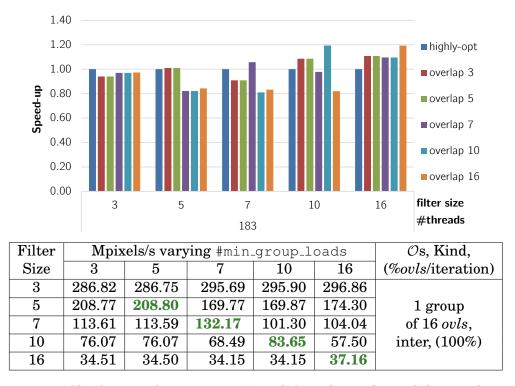

| 5.13 | Absolute performance in Mpixels/s and speed-up of the overlap optimization on the Convolution Filter (183 theads, 3 threads/core) $\ldots$ .                                                                                                                                                                                                                                                              | 132   |

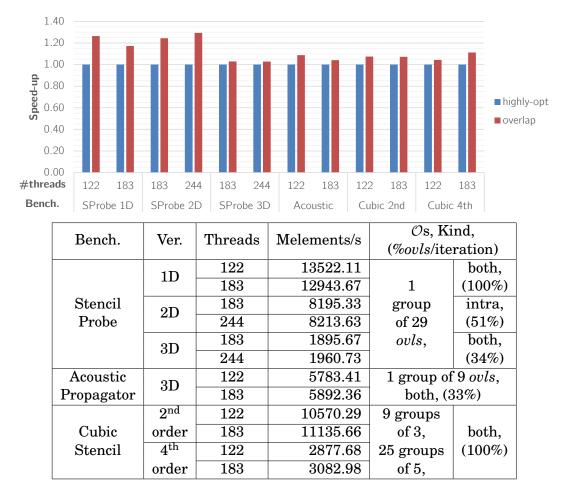

| 5.14 | Acoustic Propagator, Cubic Stencil and StencilProbe                                                                                                                                                                                                                                                                                                                                                       | 133   |

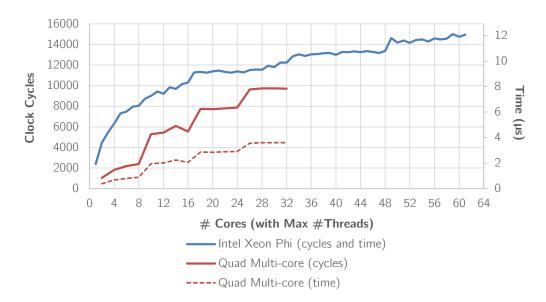

| 6.1  | Clock cycles (left axis) and execution time (right axis) of EPCC barrier with the default Intel OpenMP barrier (Intel Composer XE 2013 Update 4). Quad-socket Intel Xeon E5-4650 at 2.7 GHz (2 threads per core / 32 cores / 64 threads) and Intel Xeon Phi 7120P at 1.238 GHz (4 threads per core / 61 cores / 244 threads). Running with the maximum number of threads per core. Mean of 10 executions. | . 140 |

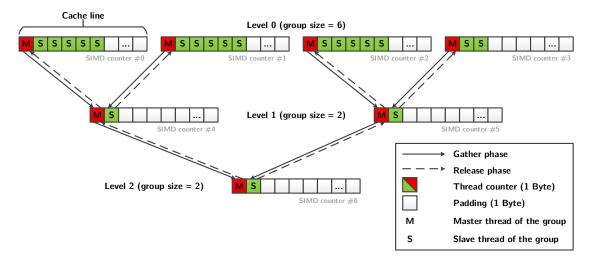

| 6.2  | SIMD Combining tree barrier scheme for 21 threads. Group sizes of level 0, 1 and 2 are 6, 2 and 2, respectively. Seven tree nodes in total with their respective distributed SIMD counters.                                                                                                                                                                                                               | 143   |

| 6.3  | SIMD reduction scheme for 21 threads. Addition reduction defined on<br>an integer data type. Tree group sizes of level 0, 1 and 2 are 6, 2 and<br>2, respectively. 4 SIMD reduction buffers                                                                                                                                                                                                               | 149   |

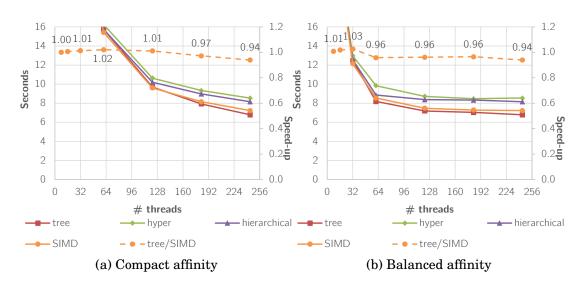

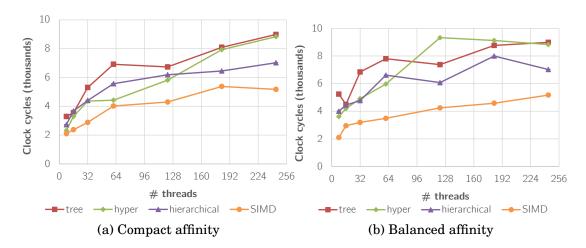

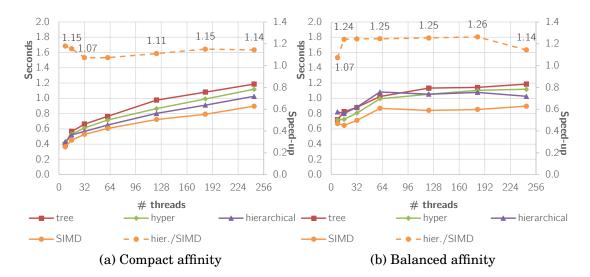

| 6.4  | Performance of a single barrier on the EPCC barrier benchmark using compact affinity. Clock cycles with standard deviation whiskers (solid series, left axis) and speed-up (dashed series, right axis)                                                                                                                                                                                                    | 168   |

| 6.5  | Performance of a single barrier on the EPCC barrier benchmark us-<br>ing balanced affinity. Clock cycles with standard deviation whiskers<br>(solid series, left axis) and speed-up (dashed series, right axis)                                                                                                                                                                                           | 169   |

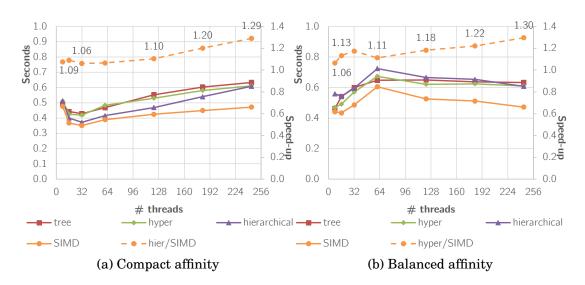

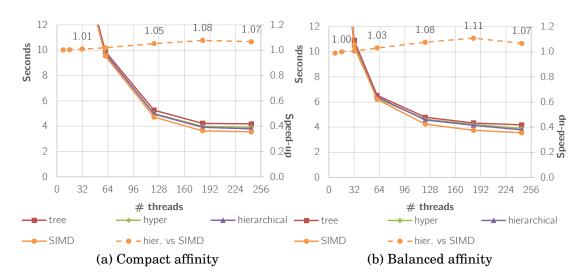

| 6.6  | MCBench: Execution time (solid series, left axis) and speed-up (dashed series, right axis)                                                                                                                                                                                                                                                                                                                |       |

| 6.7  | Livermore Loop: Execution time (solid series, left axis) and speed-up (dashed series, right axis)                                                                                                                                                                                                                                                                                                         | 172   |

| 6.8  | MG: Execution time (solid series, left axis) and speed-up (dashed series, right axis)                                                                                                                                                                                                                                                                                                                     | 173   |

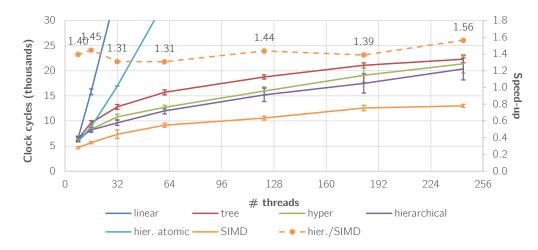

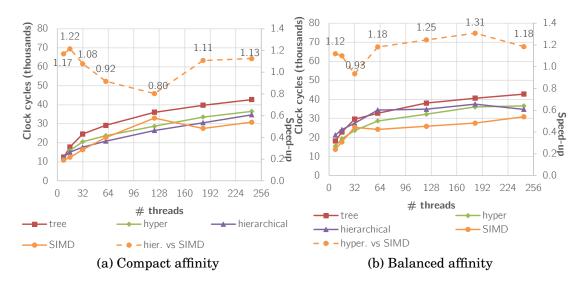

| 6.9  | Performance of a single float reduction (barrier included) on the Re-<br>duction Loop benchmark using compact affinity. Clock cycles with<br>standard deviation whiskers (solid series, left axis) and speed-up (dashe<br>series, right axis)                                                                                                                                                             |       |

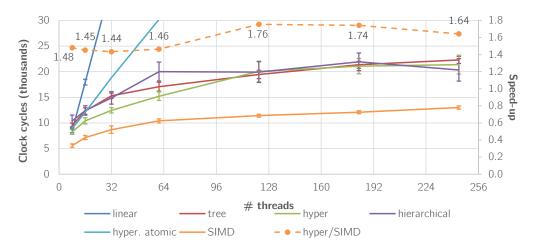

| 6.10 | Performance of a single float reduction (barrier included) on the Re-      |

|------|----------------------------------------------------------------------------|

|      | duction Loop benchmark using balanced affinity. Clock cycles with          |

|      | standard deviation whiskers (solid series, left axis) and speed-up (dashed |

|      | series, right axis)                                                        |

| 6.11 | Clock cycles of a single float reduction without including the syn-        |

|      | chronization barrier on the Reduction Loop benchmark. Only the             |

|      | SIMD reduction and the best three Intel algorithms are shown 176           |

| 6.12 | Scalability of the reduction algorithms (including barrier) with the       |

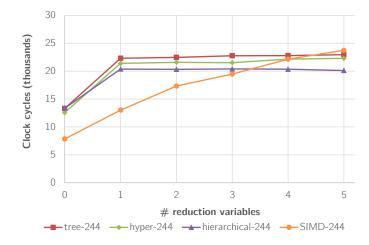

|      | number of float reductions per loop                                        |

| 6.13 | EPCC Reduction: Clock cycles (solid series, left axis) and speed-up        |

|      | (dashed series, right axis)                                                |

| 6.14 | Cholesky: Execution time (solid series, left axis) and speed-up (dashed    |

|      | series, right axis)                                                        |

| 6.15 | CG: Execution time (solid series, left axis) and speed-up (dashed se-      |

|      | ries, right axis)                                                          |

|      |                                                                            |

# **List of Tables**

| 2.1        | Characteristics of the Intel Xeon Phi coprocessor 7120P                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1        | Comparison of our proposal, the Intel C/C++ proposal [147] and the<br>SIMD extensions included in OpenMP 4.0 [117]. Checkmark means<br>that the directive/clause is included in that proposal but it is inspired<br>by other proposal. Crossmark means that the directive/clause is not<br>included in that proposal. Same directive/ clause in multiple propos-<br>als without checkmark means independent development |

| 5.1        | -                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1<br>5.2 | Default policies and values adopted in our implementation                                                                                                                                                                                                                                                                                                                                                               |

| 5.3        | Generic optimizations applied to each benchmark. Absolute perfor-<br>mance (in M{elements/pixels}/s) of the best thread configurations for<br>the baseline. Speed-up of the optimizations over the baseline. The<br>input parameters for Moving Average is the number of points and                                                                                                                                     |

|            | for Convolution is the filter size                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.1        | Main characteristics of the benchmark sets                                                                                                                                                                                                                                                                                                                                                                              |

| 6.2        | Exploration of the SIMD barrier using EPCC barrier with <i>compact</i> thread policy. Clock cycles of the best three group size configurations of the SIMD barrier on the Intel Xeon Phi 7120 coprocessor using 1,                                                                                                                                                                                                      |

| 6.3        | 2, 3 and 4 threads/core. *Last core has a fewer number of threads 163<br>Exploration of the SIMD Barrier using EPCC barrier with <i>balanced</i>                                                                                                                                                                                                                                                                        |

| 0.3        | thread policy. Clock cycles of the best three group size configurations                                                                                                                                                                                                                                                                                                                                                 |

|            | of the SIMD barrier on the Intel Xeon Phi 7120 coprocessor using 1, 2,                                                                                                                                                                                                                                                                                                                                                  |

|            | 3 and 4 threads/core. Balanced policy is equivalent to compact policy with 244 threads                                                                                                                                                                                                                                                                                                                                  |

| 6.4        | with 244 threads                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0.1        | <i>pact</i> thread policy. Clock cycles (including SIMD barrier) of the best                                                                                                                                                                                                                                                                                                                                            |

|            | three group size configurations of the SIMD reduction on the Intel                                                                                                                                                                                                                                                                                                                                                      |

|            | Xeon Phi 7120 coprocessor using 1, 2, 3 and 4 threads/core . *Last core has a fewer number of threads                                                                                                                                                                                                                                                                                                                   |

|            | core has a rewer number of tilleaus                                                                                                                                                                                                                                                                                                                                                                                     |

xxi

# **List of Listings**

| 1.1  | Mandelbrot scalar code snippet                                                                         | 5   |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 1.2  | Mandelbrot vector code snippet using intrinsics for the Intel Xeon Phi<br>coprocessor (Knights Corner) | 6   |

| 2.1  | Saxpy kernel annotated with OpenMP constructs                                                          | 12  |

| 2.2  | Example of nodes of the intermediate representation of Mercurium.                                      |     |

|      | The whole grammar can be found in the file cxx-nodecl.def [124] .                                      | 16  |

| 2.3  | Reduction code of a float variable generated for the Intel OpenMP                                      |     |

|      | Runtime Library                                                                                        | 22  |

| 2.4  | Main function prototype of the reduction API                                                           | 23  |

| 3.1  | Example of the new vector nodes in the intermediate representation                                     |     |

|      | of Mercurium. The whole grammar can be found in the source file                                        |     |

|      | cxx-nodecl.def of the compiler [124]                                                                   | 32  |

| 4.1  | Motivating code with potential problems for auto-vectorizing compilers                                 | 58  |

| 4.2  | Simple example using the standalone SIMD directive                                                     | 64  |

| 4.3  | Simple example using the SIMD-for directive                                                            | 65  |

| 4.4  | Example of the <i>aligned</i> clause in the Saxpy kernel                                               | 67  |

| 4.5  | Example of the <i>suitable</i> and the <i>aligned</i> clauses                                          | 68  |

| 4.6  | Example of the <i>linear</i> and the <i>uniform</i> clauses                                            | 70  |

| 4.7  | Example of the <i>vectorlength</i> clause                                                              | 72  |

| 4.8  | Example of the <i>vectorlengthfor</i> clause                                                           | 72  |

| 4.9  | Example of the <i>mask</i> clause                                                                      | 74  |

| 4.10 | Example using the <i>unroll</i> clause                                                                 | 76  |

| 4.11 | Example using the <i>prologue</i> and the <i>epilogue</i> clauses                                      | 77  |

| 4.12 | Example of the <i>nontemporal</i> clause                                                               | 78  |

| 4.13 | Example of the <i>prefetch</i> and <i>noprefetch</i> clauses                                           | 80  |

| 4.14 | Multiversion code snippet of the Fastwalsh benchmark without SIMD                                      |     |

|      | constructs                                                                                             | 96  |

| 5.1  | Pseudo-code resulting from the overlap optimization on the Moving                                      |     |

|      | Average example from Figure 5.1. Assuming $VF=VL=16$ . $vr2r_op_{16}$                                  |     |

|      | refers to vector register-to-register instructions                                                     |     |

| 6.1  | Generic scheme of the SIMD barrier gather phase (pseudo-code)                                          |     |

| 6.2  | Generic scheme of the SIMD barrier release phase (pseudo-code)                                         | 145 |

|      |                                                                                                        |     |

xxiii

| 6.3        | SIMD reduction steps of the master thread (pseudo-code)                            |

|------------|------------------------------------------------------------------------------------|

| 6.4        | Snippet of the team-local barrier state structure of the SIMD barrier . 151        |

| 6.5        | Snippet of the thread-local barrier state structure of the SIMD barrier 151        |

| 6.6        | Snippet of the two new waiting flag classes for the SIMD barrier 153               |

| 6.7        | Snippet of the gather phase implementation in the Intel OpenMP                     |

|            | Runtime Library following the generic scheme from Listing 6.1 154                  |

| 6.8        | Snippet of the release phase implementation in the Intel OpenMP                    |

|            | Runtime Library following the generic scheme from Listing 6.2 155                  |

| 6.9        | Prototype of the function for the estimation of reductions in a parallel           |

|            | region                                                                             |

| 6.10       | On the top, snippet of the data structure that contains information of             |

|            | SIMD reductions at team level. On the bottom, new fields added to                  |

|            | the team-local structure of the barrier to support SIMD reductions $\ . \ . \ 156$ |

| 6.11       | On the top, snippet of the data structure that contains information of             |

|            | SIMD reductions at thread level. On the bottom, new fields added to                |

|            | the thread-local structure of the barrier to support SIMD reductions . 157         |

|            | Prototype of the new main reduction function of the API                            |

| 6.13       | SIMD reduction code of two float variables (red1 and red2) and                     |

|            | addition combiner operator generated for the Intel OpenMP Runtime                  |

|            | Library targeting the Intel Xeon Phi coprocessor. Code not shown is                |

| A 1        | similar to Listing 2.3                                                             |

| A.1        | Kirchhoff benchmark kernel                                                         |

| A.2        | Distsq benchmark kernel                                                            |

| A.3        | Cholesky benchmark kernel                                                          |

| A.4        | Nbody benchmark: functions to compute the position of an AOSOA                     |

| ۸ F        | block of particles                                                                 |

| A.5        | Nbody benchmark: functions to compute forces of an AOSOA block of particles        |

| A.6        | Fastwalsh benchmark main kernel                                                    |

| A.0<br>A.7 |                                                                                    |

|            | Code snippet of the Reduction Loop benchmark                                       |

| A.8        | Mandelbrot benchmark main kernel                                                   |

## Glossary

- **barrier** Synchronization point for a group of threads where a thread waits until all the other threads have reached this point before proceeding with the execution.

- **compiler directive** Language construction that provides the compiler with information about how to process a piece of code.

- **intrinsic** Function that is handled specially by the compiler. In vectorization, SIMD intrinsics provide programmers with direct access to SIMD assembly instructions of a particular architecture.

- **OpenMP** Parallel programming model for shared-memory machines based on compiler directives.

- **reduction** Operation that consists of aggregating a set of values into a single one using a combiner operation.

- **SIMD** It stands for Single-Instruction-Multiple-Data. It is a kind of data parallelism where a single instruction is simultaneously executed on a set of data at a time.

- **vector** Synonym of *SIMD* in most of cases. It also refers to data parallelism exploited in traditional vector processors. We use this last meaning when vector processors are explicitly referenced.

- **vectorization factor** In loop vectorization, number of scalar iterations of the loop computed within a single vector iteration. It is not necessarily related with the *vector register* of the architecture.

- **vector lane** Independent sub-unit that represents each scalar element within a *vector register*.

- **vector length** Number of data elements that fits into a physical *vector register*. This number can vary for the same architecture depending on the size of the data element used.

- **vector mask** Special data type that is optionally used in vector operations to represent which *vector lanes* are enabled and disabled in the execution of a vector instruction.

- **vector register** Hardware component used to host vector operands when executing vector instructions.

## Chapter 1

## Introduction

In the last decades, computer architecture research and development has experienced a fundamental shift in the way to increase performance of future generations of processors. Performance improvements mainly based on scaling clock frequency are no longer an option due to the arising of intractable physical barriers. These physical barriers, such as the well-known *power wall* (unaffordable overall temperature and power consumption mainly due to increasing too much the clock frequency of the processor), and energy efficiency [123, 31, 18], have turned aggressive hardware improvements focused on single-core performance into more energy-aware parallel solutions.

Particularly, in the High Performance Computing (HPC) segment, new highly parallel processors have been released with a huge aggregate performance, moderate power consumption but considerably low performance per single core. Examples of these processors are the new Power 8 CPU [102], the latest NVIDIA GPUs [41] and the Intel Xeon Phi processors family [38].

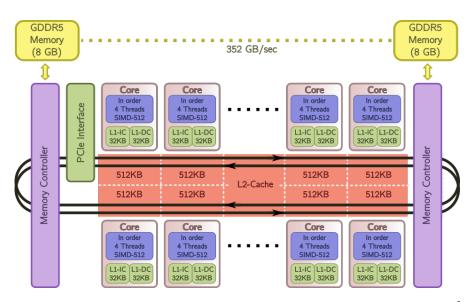

The first product of the Intel Xeon Phi family, a co-processor code-named *Knights Corner*, has up to 61 cores per chip and 4 hardware threads per core (up to 244 threads overall). Every individual core features 512-bit Single-Instruction-Multiple-Data (SIMD) units that are vital to achieve a peak performance of 1 TeraFLOPS in double precision with a Thermal Design Power (TDP) of 300W [76, 136, 65].

In this context of energy-aware high performance processors, SIMD instruction sets play a key role, as in the mentioned case of the Intel Xeon Phi coprocessor. Their appealing power consumption-to-performance ratio has led to a higher investment on these hardware components. Hardware architects are devoting more die area in wider vector units that can execute the same operation on a progressively larger amount of data at a time, without increasing the power consumption of that operation drastically.

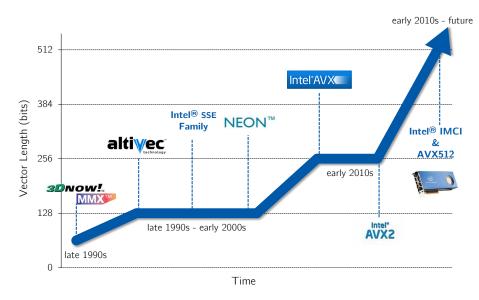

The evolution of SIMD instruction sets from Intel and other vendors throughout the years attests this widening of the vector length of SIMD units, as shown in Figure 1.1. AMD 3DNOW! and Intel MMX were the first approaches that introduced 64-bit vector units in their general purpose processor. Later on, 128-bit SIMD in-

Figure 1.1: Vector length evolution of some SIMD instruction sets (time axis is just illustrative and it is not to scale)

structions arose from different hardware companies. The first one was AltiVec, also known as Velocity Engine and Vector/SIMD Multimedia eXtensions (VMX). It was proposed by Apple, IBM and Motorola in 1999 [33]. These extensions have been used in a wide variety of devices, ranging from embedded systems to HPC processors (Cell B.E.) and video game consoles [27].

Intel also released a series of 128-bit SIMD extensions called Streaming SIMD Extensions (SSE, SSE2, SSE3, SSSE3, SSE4.1 and SSE4.2) from 1999 to 2007 [72]. These extensions are used, even currently, in general purpose and HPC processors.

Meanwhile, ARM announced its advanced 64-bit and 128-bit SIMD extensions under the name Neon in 2004 [11]. These extensions are mainly included in lowpower and mobile devices.

After some years, Intel stepped forward and released Advanced Vector Extensions versions 1 (AVX) and 2 (AVX2) with 256-bit vector units [37]. More recently, Intel moved to 512-bit vector extensions with the Initial Many Core Instructions (IMCI) [39] included in the Intel Xeon Phi coprocessor (Knights Corner). They also unveiled their continuation with this vector length in the upcoming AVX-512 SIMD instruction set [74] for general purpose and HPC processors.

Furthermore, SIMD extensions have gradually included more sophisticated, powerful and flexible instructions that bring vectorization to a broader range of applications and domains. In newer instruction sets, we can find, for instance, support for combined horizontal operations, improved support for unaligned memory accesses, gather and scatter memory operations, advanced support for predicated vectorization, improved shuffle and permutation instructions, non-temporal streaming stores, advanced software prefetching instructions for vector memory operations and instructions to detect write conflicts in scatter memory operations, among others [74].

In conclusion, this brief summary of some SIMD instruction sets shows that their relevance is increasing with time. These extensions are used in processors from different fields ranging from mobile and embedded devices to HPC systems. We observe the trend of increasing the vector length and features over generations, at least regarding Intel architectures. This fact also confirms that architects are relying more on these devices to achieve performance and energy goals.

We foresee that SIMD instructions will be determinant in future processors. Therefore, their optimal exploitation turns essential to take fully advantage of all the computational power of current and future architectures at a lower energy rate.

### **1.1 The Problem**

The higher investment in SIMD resources per core makes extracting the full computational power of these vector units more important than ever before. However, on the software side, there still exists a considerable underuse of these vector resources which leads to not fully exploiting all the computational power of these new architectures. In the context of programming models, we find deficiencies from two different perspectives: exploitation of SIMD resources at programmer level and exploitation of SIMD resources in services and algorithms used in programming model support runtime libraries.

#### 1.1.1 SIMD Exploitation at Programmer Level

As far as programmers are concerned, there exist three major ways of exploiting these vector units: compiler auto-vectorization, low-level intrinsics or assembly code and programming models/languages with explicit SIMD support [153].

Regarding auto-vectorizing compilers, fully automatic techniques do not always exploit SIMD parallelism successfully in real applications. The reasons that can prevent the compiler to auto-vectorize a code can be very varied: unknown tripcount of loops, pointer aliasing, data alignment constraints, complex data and control flow, mixed data lengths and complex data dependences (loop cross-iteration dependences), among others. Function calls are another highly limiting factor for auto-vectorization and for many code optimizations in general. They affect the flow of the execution hindering the analysis of the code.

A lot of work has been done by the community to overcome these limitations [54, 110, 157, 158, 108, 112, 80, 111, 92]. However, the truth is that many techniques have not stepped into production compilers [99]. The main reasons are the limitations found when applying aggressive code optimizations in general. Some of these limitations are the following:

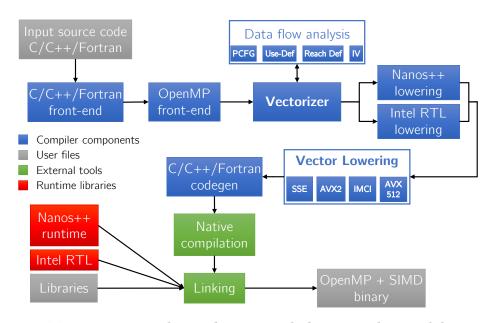

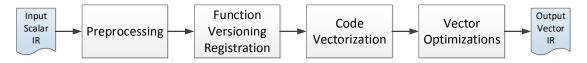

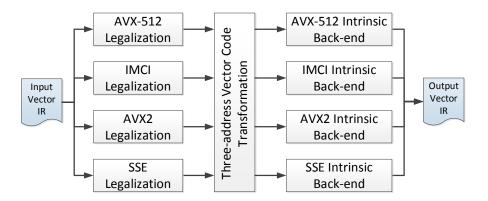

Lack of compilation technology: limits in static analyses, cost models, idiom