## Hardware Thread Scheduling Algorithms for Single-ISA Asymmetric CMPs

#### Nikola Markovic

Department of Computer Architecture

Universitat Politècnica de Catalunya

A dissertation submitted in fulfillment of the requirements for the degree of

Doctor of Philosophy / Doctor per la UPC

November 2015

Advisor: Adrian Cristal Coadvisors: Mateo Valero, Osman Unsal

|     | UNIVERSITAT POLITÈCNICA DE CATALUNYA<br>BARCELONATECH |

|-----|-------------------------------------------------------|

| UPC | Escola de Doctorat                                    |

Acta de calificación de tesis doctoral

Curso académico:

NOTABLE SOBRESALIENTE

Programa de doctorado

Nombre y apellido

Unidad estructural responsable del programa

#### Resolución del Tribunal

🔲 ΝΟ ΑΡΤΟ

Reunido el Tribunal designado a tal efecto, el doctorando / la doctoranda expone el tema de la su tesis doctoral titulada

Acabada la lectura y después de dar respuesta a las cuestiones formuladas por los miembros titulares del tribunal, éste otorga la calificación:

| (Nombre, apellidos y firma) |                             | (Nombre, apellidos y firma) |                             |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Presidente/a                |                             | Secretario/a                |                             |

| (Nombre, apellidos y firma) | (Nombre, apellidos y firma) |                             | (Nombre, apellidos y firma) |

| Vocal                       | Vocal                       |                             | Vocal                       |

\_\_\_\_\_, \_\_\_\_\_ de \_\_\_\_\_\_ de \_\_\_\_\_

APROBADO

El resultado del escrutinio de los votos emitidos por los miembros titulares del tribunal, efectuado por la Escuela de Doctorado, a instancia de la Comisión de Doctorado de la UPC, otorga la MENCIÓN CUM LAUDE:

Sí NO

| (Nombre, apellidos y firma)                                     | (Nombre, apellidos y firma)                                     |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

|                                                                 |                                                                 |  |  |  |

|                                                                 |                                                                 |  |  |  |

| Presidente de la Comisión Permanente de la Escuela de Doctorado | Secretaria de la Comisión Permanente de la Escuela de Doctorado |  |  |  |

Barcelona a \_\_\_\_\_ de \_\_\_\_\_ de \_\_\_\_\_

#### Abstract

Through the past several decades, based on the Moore's law, the semiconductor industry was doubling the number of transistors on the single chip roughly every eighteen months. For a long time this continuous increase in transistor budget drove the increase in performance as the processors continued to exploit the instruction level parallelism (ILP) of the sequential programs. This pattern hit the wall in the early years of the twentieth century when designing larger and more complex cores became difficult because of the power and complexity reasons. Computer architects responded by integrating many cores on the same die thereby creating Chip Multicore Processors (CMP). In the last decade, the computing technology experienced tremendous developments, Chip Multiprocessors (CMP) expanded from the symmetric and homogeneous to the asymmetric or heterogeneous Multiprocessors. Having cores of different types in a single processor enables optimizing performance, power and energy efficiency for a wider range of workloads. It enables chip designers to employ specialization (that is, we can use each type of core for the type of computation where it delivers the best performance/energy trade-off). The benefits of Asymmetric Chip Multiprocessors (ACMP) are intuitive as it is well known that different workloads have different resource requirements.

The CMPs improve the performance of applications by exploiting the Thread Level Parallelism (TLP). Parallel applications relying on multiple threads must be efficiently managed and dispatched for execution if the parallelism is to be properly exploited. Since more and more applications become multi-threaded we expect to find a growing number of threads executing on a machine. Consequently, the operating system will require increasingly larger amounts of CPU time to schedule these threads efficiently. Thus, dynamic thread scheduling techniques are of paramount importance in ACMP designs since they can make or break performance benefits derived from the asymmetric hardware or parallel software. Several thread scheduling methods have been proposed and applied to ACMPs.

In this thesis, we first study the state of the art thread scheduling techniques and identify the main reasons limiting the thread level parallelism in an ACMP systems. We propose three novel approaches to schedule and manage threads and exploit thread level parallelism implemented in hardware, instead of perpetuating the trend of performing more complex thread scheduling in the operating system. Our first goal is to improve the performance of an ACMP systems by improving thread scheduling at the hardware level. We also show that the hardware thread scheduling reduces the energy consumption of an ACMP systems by allowing better utilization of the underlying hardware.

### Acknowledgement

This is to express my gratitude to the Universitat Politecnica de Catalunya (UPC) committee and the Barcelona Supercomputing Center (BSC) for providing me with the necessary resources that allowed me to perform my PhD studies in a highly competitive, but at the same time friendly international atmosphere. A special thank goes to Prof. Mateo Valero and Computer Science - Computer Architecture for Parallel Paradigms research group for giving me an opportunity to work in the challenging field of Hardware Thread Scheduling. I would further like to thank my advisors Adrian Cristal and Osman Unsal. I really appreciate their valuable guidance, constructive criticism and the time and concentration they spent reading all the versions of this thesis. Many thanks go to all my current and past colleagues, with whom I spent last seven years (Srdjan, Vladimir, Gokcen, Nehir, Vesna, Milovan, Adria, Oriol, Gulay, Ferad, Oscar, Tim, Xavier, Gina, Sasa, Mario, Damian, Azam, and Santosh). Maybe the best achievement in Barcelona is getting to know them. Furthermore a special thank goes to my friends (Aleksandar, Darko, Milan, Daniel, Jelena and Nikola) and my girlfriend (Marica) for encouraging me during my PhD time. I wish to sincerely thank my family (my mother Olga, my father Radovan and my brothers Nenad and Novak) for supporting me, morally above all, but also financially, and sharing all the useful life experience.

Nikola Markovic

## Contents

| Co | onten   | ts       |                                                          | ix   |

|----|---------|----------|----------------------------------------------------------|------|

| Li | st of ] | Figures  |                                                          | xiii |

| Li | st of ' | Fables   |                                                          | xvii |

| 1  | Intr    | oductio  | n                                                        | 1    |

|    | 1.1     | Motiva   | ation and Scope of the Thesis                            | 2    |

|    |         | 1.1.1    | Importance of Scheduling                                 | 3    |

|    | 1.2     | Key C    | hallenges                                                | 5    |

|    | 1.3     | Contri   | butions of Thesis                                        | 8    |

|    |         | 1.3.1    | Hardware Round-Robin Scheduling Algorithm                | 8    |

|    |         | 1.3.2    | Kernel to User mode Transition aware Hardware Scheduling |      |

|    |         |          | Algorithm                                                | 9    |

|    |         | 1.3.3    | Trait-aware Criticality Scheduling Algorithm             | 10   |

|    | 1.4     | Thesis   | Organization                                             | 11   |

| 2  | Stat    | e-of-the | e-Art and Background in                                  |      |

|    | Sch     | eduling  | Policies on an ACMP                                      | 13   |

|    | 2.1     | Contex   | xt Switching                                             | 13   |

|    |         | 2.1.1    | Performance Impact of Context Switching                  | 14   |

|    |         | 2.1.2    | Analytical Models for characterizing Context Switches    | 14   |

|    |         | 2.1.3    | Managing Cache Misses caused by Context Switches         | 15   |

|    | 2.2     | Schedu   | uling Policies                                           | 16   |

|   |     | 2.2.1          | First Studies on Scheduling Policies on an ACMP             | 16      |

|---|-----|----------------|-------------------------------------------------------------|---------|

|   |     | 2.2.2          | Scheduling based on Profiling and Sampling                  | 17      |

|   |     | 2.2.3          | Scheduling focused on Power and Energy                      | 18      |

|   |     | 2.2.4          | Scheduling based on Workload Characteristics                | 19      |

|   |     | 2.2.5          | Fairness-aware Scheduling                                   | 20      |

|   |     | 2.2.6          | Scheduling targeting Bottlenecks in Parallel Applications   | 22      |

| 3 | Met | hodolog        | gy                                                          | 25      |

|   | 3.1 | Bench          | mark Suites                                                 | 25      |

|   |     | 3.1.1          | SPEC Benchmark Suites                                       | 26      |

|   |     | 3.1.2          | SPLASH2 Benchmark Suites                                    | 29      |

|   | 3.2 | Sniper         | Infrastructure                                              | 32      |

|   |     | 3.2.1          | Sniper Extensions                                           | 34      |

|   |     | 3.2.2          | Simulated Architecture - Sniper configuration               | 35      |

| 4 | Con | text Sw        | vitch on the CMP                                            | 37      |

|   | 4.1 | Manag          | ging the Context Switches                                   | 37      |

|   | 4.2 | Conte          | xt Switch Cost                                              | 39      |

| 5 | HR  | RS: Ha         | rdware Round-Robin Scheduler for Hardware Threads           | 43      |

|   | 5.1 | HRRS           | Algorithm                                                   | 44      |

|   |     | 5.1.1          | Hardware Implementation                                     | 46      |

|   | 5.2 | Evalua         | ation                                                       | 48      |

|   |     | 5.2.1          | Simulated Architecture and Workloads                        | 49      |

|   |     | 5.2.2          | Ideal Performance gains and Scalability                     | 50      |

|   |     | 5.2.3          | Performance Evaluation                                      | 52      |

|   |     | 5.2.4          | Energy Efficiency Analysis                                  | 56      |

|   | 5.3 | Summ           | nary                                                        | 57      |

|   |     |                |                                                             |         |

| 6 | KU  | ГНS: К         | ernel to User mode Transition aware Scheduler for Hardware  | e       |

| 0 |     | ГНS: К<br>eads | ernel to User mode Transition aware Scheduler for Hardware  | e<br>61 |

| 0 |     | eads           | Ternel to User mode Transition aware Scheduler for Hardware |         |

| 0 | Thr | eads           |                                                             | 61      |

#### CONTENTS

|   | 6.3 | Evalua    | tion                                                        | 66 |

|---|-----|-----------|-------------------------------------------------------------|----|

|   |     | 6.3.1     | Simulated Architecture and Workloads                        | 66 |

|   |     | 6.3.2     | Performance and Energy Efficiency evaluation on a Shared    |    |

|   |     |           | LLC System                                                  | 68 |

|   |     | 6.3.3     | Hardware vs Software Implementation                         | 70 |

|   |     | 6.3.4     | Performance Evaluation on Private LLC System                | 72 |

|   | 6.4 | Summ      | ary                                                         | 73 |

| 7 | TCS | 5: Trait- | aware Criticality Scheduler for Hardware-Threads            | 75 |

|   | 7.1 | TCS A     | lgorithm Basis                                              | 76 |

|   |     | 7.1.1     | Differences to the HRRS Algorithm                           | 76 |

|   | 7.2 | TCS a     | pproach of determining Critical Threads                     | 78 |

|   |     | 7.2.1     | Differences to the other Criticality Schedulers             | 80 |

|   | 7.3 | Hardw     | are Implementation                                          | 81 |

|   |     | 7.3.1     | Identification of the Running Threads                       | 81 |

|   |     | 7.3.2     | Hardware Component Description                              | 82 |

|   |     | 7.3.3     | Managing the Context Switches                               | 83 |

|   | 7.4 | Evalua    | tion                                                        | 83 |

|   |     | 7.4.1     | Simulated Architecture and Workloads                        | 84 |

|   |     | 7.4.2     | Comparison to the Scheduling for Fairness                   | 85 |

|   |     | 7.4.3     | Comparison to the Scheduling for Workload Characteristics . | 86 |

|   |     | 7.4.4     | Comparison to the Scheduling for Criticality                | 87 |

|   | 7.5 | Summ      | ary                                                         | 89 |

| 8 | Con | clusion   | and Future Work                                             | 91 |

|   | 8.1 | Future    | Work                                                        | 93 |

| 9 | Pub | lication  | List                                                        | 95 |

#### Bibliography

**97**

## List of Figures

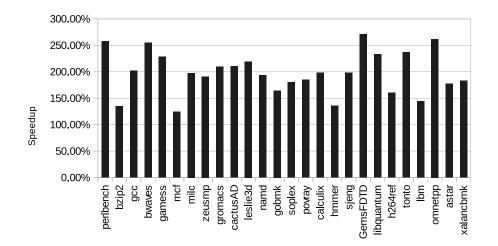

| 1.1 | Large core speedup compared to the small cores when running the SPEC2006 benchmark.                                                                                                                                                                                                                                                                                                                                                                 | 6  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

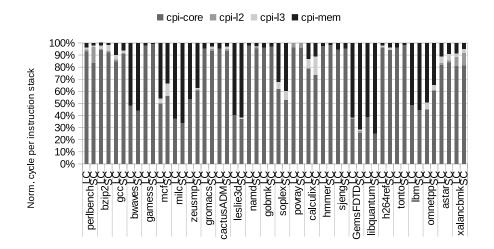

| 1.2 | Normalized cycle per instruction stack breakdown for the large core and for the small cores when running the SPEC2006 benchmark                                                                                                                                                                                                                                                                                                                     | 7  |

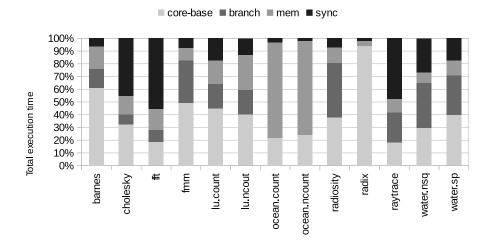

| 3.1 | Breakdown of the execution time for the problem sizes in Table 3.3<br>on a four processor machine. The execution time is broken down into<br>total time application spends in computation (core-base), in branches<br>(branch), in memory accesses (mem) and in synchronization (sync).<br>The synchronization represents the time spent in the barriers, locks<br>and pauses (flag-based synchronizations) encountered across all pro-<br>cessors. | 31 |

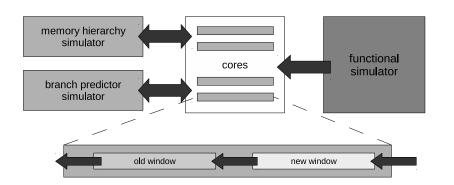

| 3.2 | Sniper interval simulation model                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

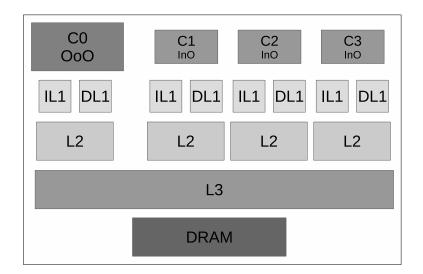

| 3.3 | Simulated Architecture                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

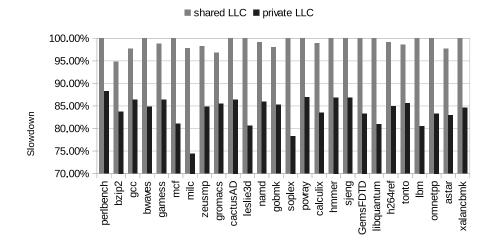

| 4.1 | Context switch cost including flushing cores pipeline and register file<br>as well as working set transfer (warming of the cache hierarchy) be-<br>tween two out-of-order cores on the CMP with the shared and private<br>last level cache for the SPEC2006 benchmark                                                                                                                                                                               | 39 |

| 4.2 | Context switch cost including flushing cores pipeline and register file<br>as well as working set transfer (warming of the cache hierarchy) be-                                                                                                                                                                                                                                                                                                     |    |

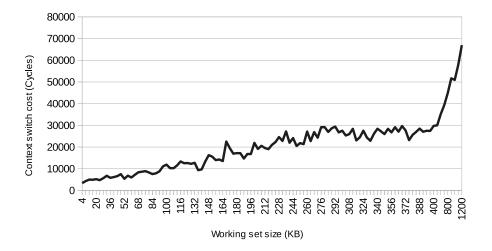

|     | tween cores on Intel(R) Core(TM) i7-4600U CMP[1]                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

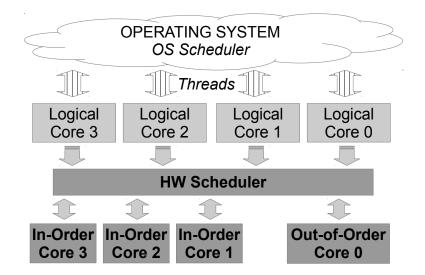

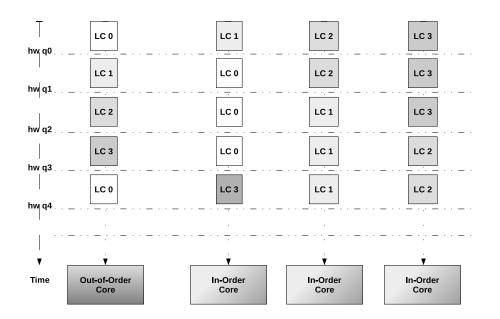

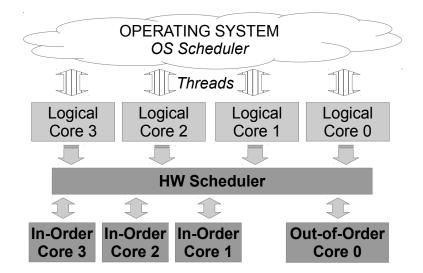

| 5.1 | HRRS scheduling - All logical cores (which correlate to hardware threads) are the same while the large physical core is represented by Core 0 and the small physical cores are shown as Cores 1,2 and 3                                                                                                                                                                                                           | 45 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

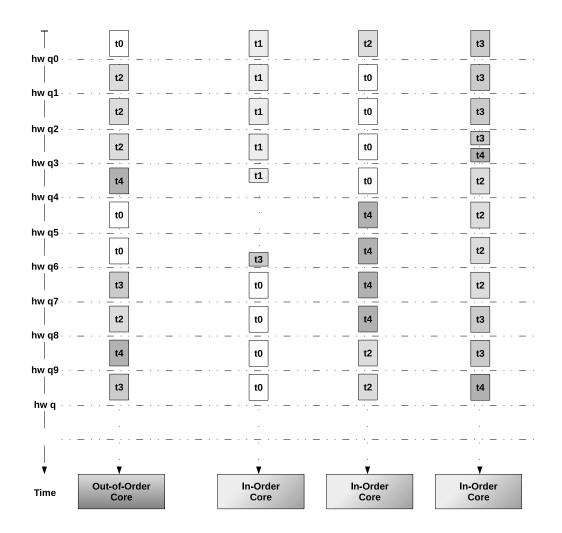

| 5.2 | An example of the HRRS scheduling logical cores on actual physical cores at every hardware-scheduling quantum. At the beginning logical core 0 is running on the large physical core while logical cores 2, 3 and 4 are running on small physical cores. After a first hardware scheduling quantum, Logical core 1 will be moved to large physical core and logical core 0 will be moved to a small physical core | 47 |

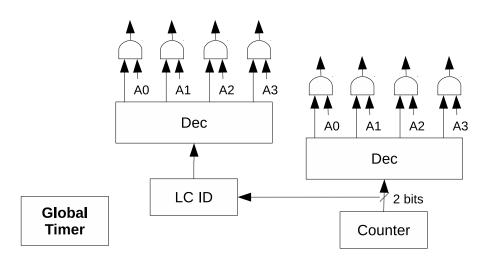

| 5.3 | Hardware implementation layout example for HRRS scheduling pol-<br>icy on the four core ACMP consisting of one large and three small<br>cores ( $1 \text{ OoO} + 3 \text{ InO}$ ), where 'A' is the active bit per hardware thread.                                                                                                                                                                               | 48 |

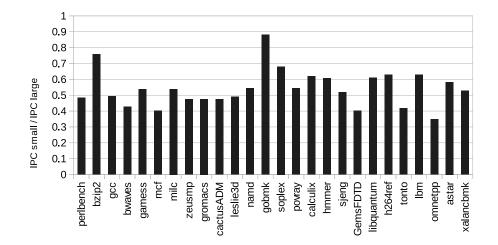

| 5.4 | Small core slowdown (expressed as IPC small / IPC large) compared to the large cores when running SPEC2006 benchmark                                                                                                                                                                                                                                                                                              | 50 |

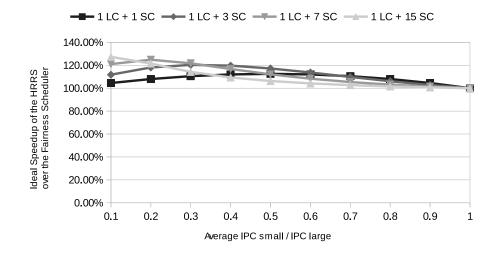

| 5.5 | Ideal Speedup comparison of the HRRS over Fairness scheduler on an ACMP systems consisted of 2 (1 OoO + 1 InO), 4 (1 OoO + 3 InO), 8 (1 OoO + 7 InO) and 16 (1 OoO + 15 InO) cores respectively                                                                                                                                                                                                                   | 52 |

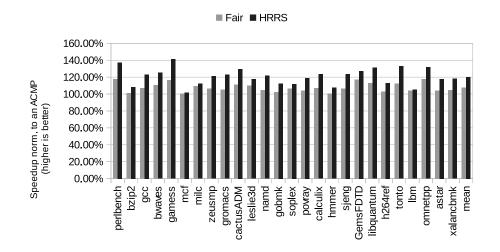

| 5.6 | Speedup comparison of the HRRS and Fairness scheduler normalized to Linux OS scheduler for the SPEC2006 benchmark suite running multiple instances of traces collected from different phases of an application on four cores ACMP (1 OoO + 3 InO)                                                                                                                                                                 | 53 |

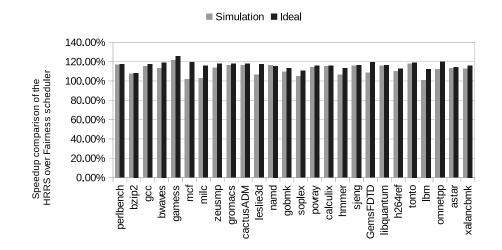

| 5.7 | Speedup comparison of the ideal and simulation results of the HRRS over Fairness scheduler for the SPEC2006 benchmark suite running four instances of traces collected from different phases of an application on four cores ACMP ( $1 \text{ OoO} + 3 \text{ InO}$ )                                                                                                                                             | 54 |

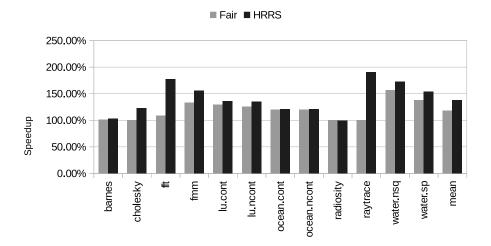

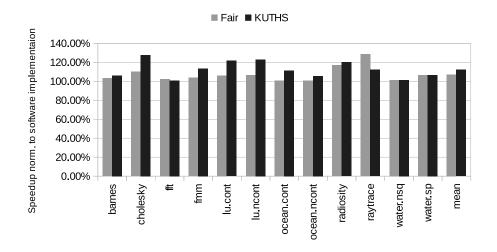

| 5.8 | Speedup comparison of the HRRS and Fairness scheduler normalized to Linux OS scheduler for the SPLASH-2 benchmark suite running on four cores (1 OoO + 3 InO)                                                                                                                                                                                                                                                     | 55 |

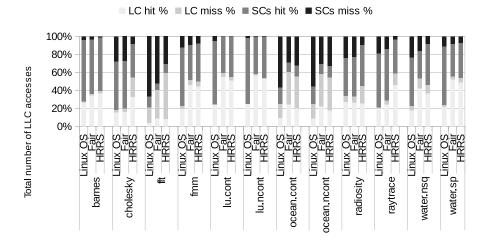

| 5.9 | The LLC cache accesses breakdown for the large and small cores of the Linux OS, Fairness and HRRS scheduler for the SPLASH-2 benchmark running on four cores ACMP (1 OoO + 3 InO)                                                                                                                                                                                                                                 | 55 |

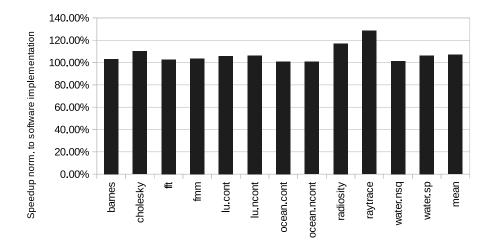

| 5.10 | Speedup of the hardware over the software implementation (baseline) for the HRRS scheduler, where scheduling quanta are 1ms and 4ms for hardware and software implementations respectively                               | 57 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

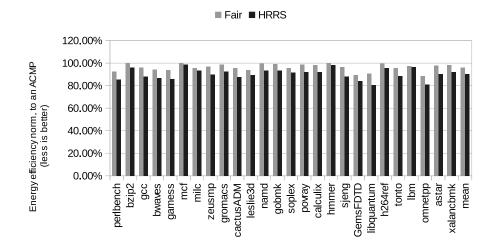

| 5.11 | Energy efficiency comparison of the HRRS and Fairness scheduler<br>normalized to Linux OS scheduler for the SPEC2006 benchmark suite<br>running four instances of an application on four cores ACMP (1 OoO<br>+ 3 InO)   | 58 |

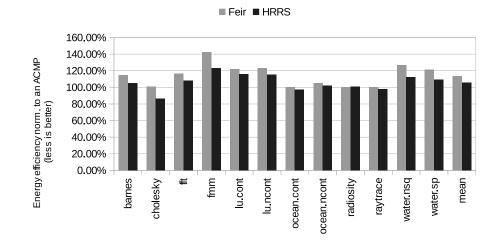

| 5.12 | Energy efficiency comparison of the HRRS and Fairness scheduler<br>normalized to Linux OS scheduler for the SPLASH-2 benchmark suite<br>running on four cores ACMP (1 OoO + 3 InO)                                       | 58 |

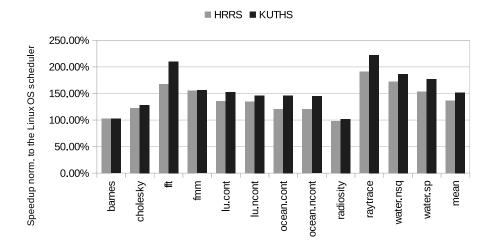

| 6.1  | Speedup and Energy efficiency comparison of the KUTHS and the Fair scheduler for the SPLASH-2 benchmark suite in a shared LLC four core system (1 large + 3 small)                                                       | 67 |

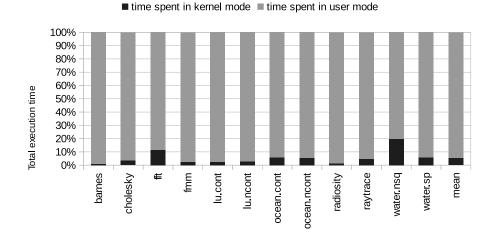

| 6.2  | Distribution of the total execution time of the SPLASH-2 benchmark applications                                                                                                                                          | 68 |

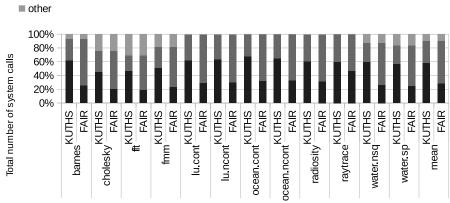

| 6.3  | Percentage of threads that continue execution on the large or small core after synchronization based system calls in the parallel section of the application for the Fairness-aware and the KUTHS scheduler respectively | 69 |

| 6.4  | Speedup comparison of the KUTHS and the HRRS scheduler for the SPLASH-2 benchmark suite in a shared LLC four core system (1 large + 3 small)                                                                             | 70 |

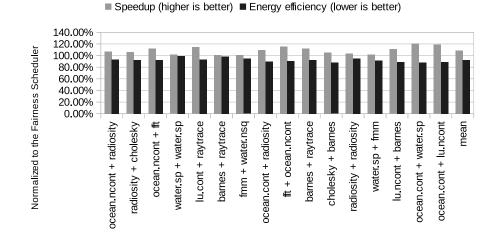

| 6.5  | Speedup and Energy efficiency comparison of the KUTHS and the Fair scheduler running two applications from the SPLASH-2 benchmark suite in a shared LLC four core system (1 large + 3 small)                             | 71 |

| 6.6  | Speedup of the hardware over the software implementation (baseline)<br>for the Fairness-aware and the KUTHS scheduler, where scheduling<br>quanta are 1ms and 4ms for hardware and software implementations              |    |

|      | respectively                                                                                                                                                                                                             | 72 |

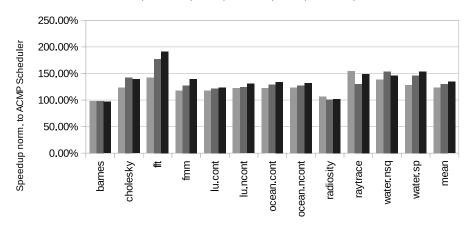

| 6.7 | Speedup comparison of the KUTHS and the Linux OS (ACMP) Sched-<br>uler for the SPLASH-2 benchmark suite in the private last-level L3<br>cache 8/16/32 cores system configurations where each group of one<br>large and three small share a 4MB L3 cache                                                                                                                                                                                                                   | 73 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | TCS scheduling - All logical cores (which correlate to hardware threads) are the same while the large physical core is represented by Core 0 and                                                                                                                                                                                                                                                                                                                          |    |

| 7.2 | the small physical cores are shown as Cores 1,2 and 3 An example of the TCS scheduling threads on physical cores during every hardware-scheduling quantum. At the beginning, thread 0 is running on the large physical core while threads 2, 3 and 4 are running on the small physical cores. After every hardware scheduling quantum, threads will be rescheduled based on their short-term characteristics. Whenever a thread stalls or continues, rescheduling is per- | 77 |

|     | formed based on the long-term thread characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      | 79 |

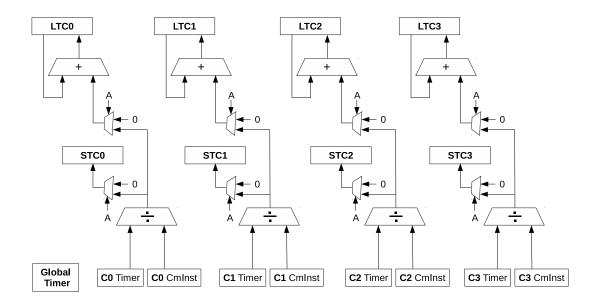

| 7.3 | Hardware implementation layout example for TCS scheduling policy<br>on the four core ACMP consisting of one large and three small cores<br>(1  OoO + 3  InO), where "A" is the active bit per hardware thread<br>and "CmInst" is the number of committed instructions in given time                                                                                                                                                                                       |    |

|     | quantum per hardware thread.                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84 |

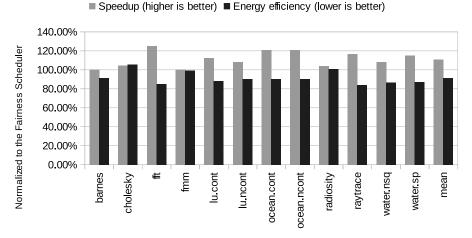

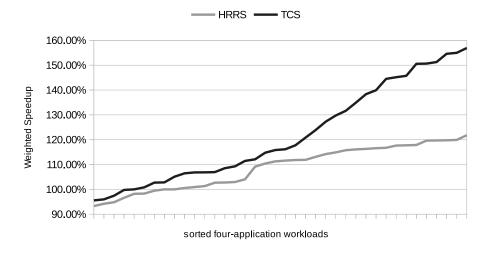

| 7.4 | Weighed speedup (system throughput) comparison of the TCS and<br>HRRS scheduler normalized to the pinned scheduler on an ACMP                                                                                                                                                                                                                                                                                                                                             |    |

| 7.5 | consisting of four cores (1 OoO + 3 InO) for the SPEC2006 benchmark.<br>Weighed Speedup (system throughput) comparison of the TCS over<br>the pinned scheduler on an ACMP consisting of two cores (1 OoO +                                                                                                                                                                                                                                                                | 86 |

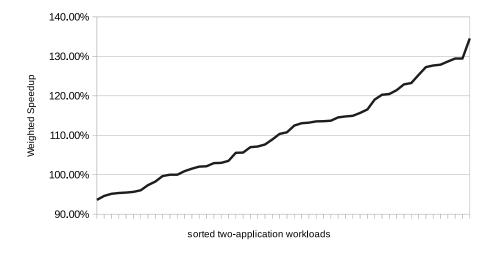

|     | 1 InO) for the SPEC2006 benchmark.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87 |

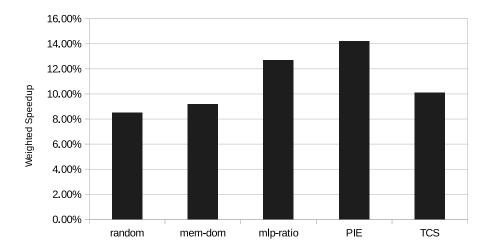

| 7.6 | Comparing absolute average weighed speedup (system throughput)                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | of the different scheduling policies over the pinned scheduler on an $ACMP$ consisting of two cores (1.0c0 + 1.1rO)                                                                                                                                                                                                                                                                                                                                                       | 00 |

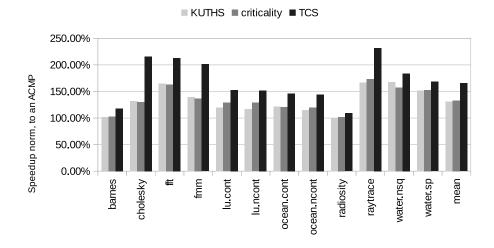

| 7.7 | ACMP consisting of two cores (1 OoO + 1 InO)                                                                                                                                                                                                                                                                                                                                                                                                                              | 88 |

| 1.1 | criticality and TCS schedulers normalized to the pinned scheduler on                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | an ACMP consisting of four cores $(1 \text{ OoO} + 3 \text{ InO})$ for the SPLASH2                                                                                                                                                                                                                                                                                                                                                                                        | 00 |

|     | benchmark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89 |

## List of Tables

| 3.1 | A list of the SPEC Benchmarks used in simulations, along with the      |    |

|-----|------------------------------------------------------------------------|----|

|     | most relevant execution command-line arguments                         | 27 |

| 3.2 | Dynamic Instruction Count and Instruction Mix of SPEC CPU2006          |    |

|     | Integer and Floating-Point Benchmarks.                                 | 28 |

| 3.3 | SPLASH2 Benchmarks used in simulations, along with the problem         |    |

|     | sizes                                                                  | 30 |

| 3.4 | Asymmetric Chip Mmultprocessor System configurations for Sniper        |    |

|     | simulator used in experiments                                          | 36 |

| 6.1 | Cost of workload migration (in cycles) during context switch for work- |    |

|     | loads ranging from a few kilobytes to a few thousand kilobytes         | 66 |

## Introduction

The relentless push in technology scaling driven by Moore's law has resulted in more transistors packed into a very small area. Overtime, computer architects responded by integrating many cores on the same die. Chip multiprocessors, or CMPs for short, are now the most common way to build high-performance microprocessors, for a variety of reasons. First of al, large uniprocessors are no longer scaling in performance, because it is only possible to extract a limited amount of parallelism from a typical instruction stream using conventional superscalar instruction issue techniques. In addition, one cannot simply ratchet up the clock speed on today's processors, or the power budget would become prohibitive. Compounding these problems is the simple fact that with the immense numbers of transistors available on today's microprocessor chips, it is too costly to design and debug ever-larger single-core processors every year or two.

CMPs avoid these problems by filling up a processor die with multiple, relatively simpler processor cores instead of one huge core. The complexity of a CMP's cores can vary from very simple pipelines to moderately complex superscalar processors, but once a core has been selected the CMP's performance can easily scale across silicon process generations simply by stamping down more copies of the hard-to-design, high-speed processor core in each successive chip generation.

In addition, parallel code execution, obtained by spreading multiple threads of execution across the various cores, can achieve significantly higher performance than would be possible using only a single core with comparable amount of resources. Though, this is truth, it is not that simple to utilize the parallelism bearing in mind the interconnection networks, the cache coherency, cache/memiry bandwidth etc. of the CMP. While parallel threads are already common in many useful workloads, there are important workloads that are hard to divide into parallel threads. Nevertheless, the low inter-processor communication latency between the cores in a CMP helps make a much wider range of applications viable candidates for parallel execution than was possible with traditional, multi-chip multiprocessors.

#### **1.1 Motivation and Scope of the Thesis**

Nowadays, chip multiprocessors (CMPs) may be symmetric (SCMP), consisting of many cores of the same type, or asymmetric (ACMP), where cores may differ from one another with respect to their functionality and/or performance [2], [3]. As is shown by a number of recent studies ACMPs are likely to outperform SCMPs for a fixed budget (area or power or both) [4], [5]. Since it is well known that different workloads have different resource requirements, the benefits of ACMPs are intuitive.

The exciting rise of asymmetric multi core processors (ACMPs) has fostered a critical reevaluation of the traditional scheduling mechanisms in order to take full advantage of the new hardware resources in relation to the increasingly common thread level parallelism as well as in meeting certain system performance and power requisites. The operating system scheduler module orchestrates critical execution time junctures, selecting which jobs to be admitted next into the system and the next process to run. A technique known as fair-share scheduling is used by computer operating systems where CPU usage is equitably divided between system users or groups, in contrast to equal distribution among processes. The Linux OS scheduler, based on a fair-share scheduler strategy, is a process scheduler which was merged into the 2.6.23 release of the Linux kernel as its default scheduler [6]. It handles CPU resource allo-

cation for executing processes aimed at maximizing overall CPU utilization as well as interactive performance. Operating systems may feature up to three distinct types of schedulers, a long-term scheduler (also known as an admission scheduler or high-level scheduler), a mid-term or medium-term scheduler and a short-term or CPU scheduler. The names suggest the relative frequency with which these functions are performed.

The third type of scheduler, the short-term scheduler, commonly referred to as the CPU scheduler is the primary focus of this work. It is responsible for determining which of the ready processes (loaded into the memory by the other schedulers) should be sent for execution and on which computational core. This decision takes place periodically at interrupt points caused principally by the clock, I/O events, or OS system level calls. In relation to the long and short-term schedulers, the short-term scheduler must make scheduling decisions much more frequently. Furthermore, the short-term scheduler can be preemptive or non-preemptive based on its ability to force processes off the CPU. The preemptive method depends on a programmable interval timer that invokes a kernel level interrupt handler which implements the scheduling algorithm. A key function involved in the CPU-scheduling decision is the dispatcher which gives control of the CPU to the process selected. This function involves the context switching, changing to user mode, and jumping to the proper location of a program once it is restarted. The actual time it takes for the dispatcher to perform its job stopping one process and starting another is known as the dispatch latency typically requiring several thousands of cycles [7]. Since the dispatcher needs to analyze the program counter values, fetch instructions, and load data into the registers of the CPU every time a process switch occurs, minimizing the dispatcher latency should be a primary objective. Moreover, it is also important to avoid unnecessary context switches due to the fact that the processor remains idle for a period of time during context switches.

#### **1.1.1 Importance of Scheduling**

The need for a scheduling algorithm arises from the requirement for CMP and ACMP systems to perform multitasking (executing more than one process or thread at a time). Scheduling is the method by which threads, processes or data flows are given access per core to system resources (e.g. processor time). This is usually done to load balance and share system resources effectively or to achieve a target quality of service. Parallel

applications relying on multiple threads must be efficiently managed and dispatched for execution if the parallelism is to be properly exploited.

Multi-cores usually operate under the shared memory model, allowing parallel tasks of an application to cooperate by concurrently accessing shared resources using a common address space. Each task can be seen as a sequential thread of execution that performes useful computation. Thus, a parallel programming model has to create and manage several tasks that need to synchronize and communicate to each other. However, having concurrent parallel tasks may introduce several new classes of potential problems, of which data races (e.g., data dependencies) are the most common [8]. Today's programming models commonly target this problem via lock-based approaches.

Unfortunately, when using locks, programmers must pick between two undesirable choices. Use coarse-grain locks, where large regions of code are included as critical regions. This makes the task of adding coarse-grain locks to a program quite straightforward, but introduces unnecessary serialization that degrades system performance. On the other side, fine-grain locking aims at critical sections of minimum size. Smaller critical sections permit greater concurrency, and thus scalability. However, this scheme leads to higher complexity, and it is usually difficult to prove the correctness of the resulting algorithm.

These two choices establish a programming effort versus performance trade-off. The complexity associated with fine-grain locking can lead to incorrect synchronization, e.g., data races, which could manifest in the form of non-deterministic execution, producing incorrect results for certain executions of an application. This fact makes lock based programs difficult to debug, because bugs are hard to reproduce. Synchronization errors may also result in deadlock or livelock conditions. Using multiple locks requires strict programmer discipline to avoid cyclic dependencies where two or more threads create circular requests to acquire locks, leading to a deadlock scenario where threads are blocked and no forward progress is made. On the other hand, livelocks occur when two or more threads cease to make forward progress while performing the same piece of work repeatedly.

Nevertheless, even correctly parallelised applications may behave poorly due to coherence or unnecessary contention in critical sections caused by inappropriate thread scheduling on the CMP. Parallel applications have to modify a certain amount of shared data. Modifying the same data in different cores causes cache-lines to move between private caches, penalizing system throughput and overall application performance. Correct mapping of parallel threads to the underlying cores is of utmost importance for further development of the chip multiprocessors as well as parallel applications.

#### **Goal of the Thesis**

Parallel applications relying on multiple threads must be efficiently managed and dispatched for execution if the parallelism is to be properly exploited. Thus, dynamic thread scheduling techniques are of paramount importance in ACMP designs since they can make or break performance benefits derived from the asymmetric hardware or parallel software. Several thread scheduling methods have been proposed and applied to ACMPs. Most of these make use of online or offline profiling as well as sampling or estimation techniques to determine the optimum thread to core mapping (in relation to performance and/or power) whenever a specific event is detected or scheduling time quantum is completed [9], [10], [11] among others. Though these scheduling techniques include certain performance or energy efficiency gains, their broad application remains stifled due to scalability limitations, runtime overheads, and additional hardware requirements and complexities. Our goal is to develop a scheduling policy that can be used as a foundation upon which to build practical and scalable hardware scheduling designs in order to increase the performance capabilities of ACMPs.

#### **1.2 Key Challenges**

Although parallel applications and multiapplication workloads provide opportunities for greater performance and efficiency gains, thanks in part to the amount of hardware resources or cores that can be activated to execute the different parallel portions of the workload. In order to take full advantage of these parallelism opportunities, several key concerns must be tackled, namely application bottlenecks, runtime imbalances of multithreaded programs, workload characteristics, and implementation complexity of the scheduling policy.

Firstly, to tackle the runtime imbalances, we can consider and implement different

Figure 1.1: Large core speedup compared to the small cores when running the SPEC2006 benchmark.

thread scheduling techniques to achieve as much fairness as possible. For example, Van Craeynest et al. showed that in a asymmetric multicore system, a round-robin scheduler using threads pinned to cores produces no speedup compared to a lighter symmetric multicore system for most multithreaded benchmarks [12]. This behavior is caused by barrier-synchronized multithreaded workloads, because the execution progress is limited by the slowest thread. This has little meaning in a symmetric system but is significant for asymmetric systems, because the thread pinned to the simplest core will be the weakest link that all other threads will have to wait for at every barrier.

Work-stealing workloads, in contrast, allow idle large cores to steal work that normally would be run on the small cores, so that the execution time isn't as constrained. Therefore, in asymmetric multicore systems, guaranteeing fairness is fundamental for improving performance for barrier-synchronized multithreaded workloads. Fairness, defined as giving each thread equal execution time on each core or allowing each thread to make equal progress, enables all threads to reach the barriers simultaneously, and has been shown to provide average performance improvements of 14 percent (and up to 25 percent) compared with a pinned scheduler [12] for the system configuration we are using.

Figure 1.2: Normalized cycle per instruction stack breakdown for the large core and for the small cores when running the SPEC2006 benchmark.

Secondly, bottlenecks arising from distinct thread and memory management and sharing approaches have significant effects on performance and system usage efficiency. Moreover, code segments that produce long waits for threads tend to reduce the total amount of thread-level parallelism and can even negate the potential speedup gained by parallelization of an application. In particular, inter-thread synchronization bottlenecks (such as contended critical sections), as well as different memory structures and behaviors, can cause thread imbalances at runtime, leading to adverse performance effects. The state of the art in bottleneck acceleration on an ACMP is bottleneck identification and scheduling (BIS) [13], which outperforms the best mechanisms by 15 percent for single-application workloads. Utility-based acceleration (UBA) of multithreaded applications on ACMPs provides about 8.2 percent of additional performance improvement over BIS for an ACMP with one large core in the system [14].

Thirdly, the performance behavior of workloads on small and large cores (Fig. 1.1) can be explained by the design characteristics of each core. Fig. 1.1 compares the slowdown for SPEC CPU2006 workloads on a small core relative to a large core. A particular workload can be characterized as either compute-intensive or memory-intensive based upon the normalized CPI stack as given in Fig. 1.2. For example, milc has a memory dominant CPI stack making it memory intensive whilst the reverse is

true for tonto. These distinctions are relevant to asymmetric systems because workloads will perform differently on different cores based on their characteristics. For instance, workloads that contain large amounts of memory level parallelism (MLP) or instruction level parallelism (ILP) would be more suited to run on large cores capable of out of order execution. Conversely, workloads consisting of high amounts of thread level parallelism (TLP) and explicit ILP (i.e. parallelism that does not require dynamic extraction) are good candidates for execution on smaller cores. For example, a compute-intensive workload consisting of significant ILP may achieve adequate performance on a small core and leave the large core vacant for memory-intensive workloads which would suffer from substantial performance degradation if run on a small core. Therefore, in an asymmetric system, it may be useful to correlate a workload's execution performance with a particular core type in order to dynamically ascertain the workload's characteristics and improve the scheduler strategy.

Finally, scheduling policy applicability is directly affected by the complexity of its implementation. Most of scheduling methods proposed and applied to SCMPs as well as to ACMPs rely on the sampling or other estimation techniques, together with online or offline profiling of the performance and/or power to decide up on the most favorable thread to core mapping, when a particular event is detected or scheduling time quantum is completed, [4], [11], [15] among others. They usually require ISA extensions or changes to be made in OS or user application code along with several tables and necessary logic, implemented in hardware, to keep and manage information about threads.

#### **1.3 Contributions of Thesis**

We present the contributions of this thesis that address the previously mentioned challenges that thread scheduling faces on an ACMP in the Section 1.2.

#### **1.3.1 Hardware Round-Robin Scheduling Algorithm**

To tackle the problem of runtime imbalances during execution of multiple threads, we propose the Hardware Round-Robin Scheduling (HRRS) policy. This technique is influenced by Fairness Scheduling techniques thereby reducing thread serialization and improving parallel thread performance.

The HRRS technique remaps hardware threads on the actual physical cores of the system at every hardware scheduling quantum, while Operating System maps and reschedules software threads on those hardware threads. The scheduler remaps hardware threads between different core types (such as large - Out-of-Order and small - In-Order) in a round-robin fashion after every time quantum expires. In this way, the HRRS approach fairly balances the workload among different cores in as ACMP system. In contrast, the Fairness Scheduler technique [12] has special hardware structure that keeps track of all software threads while mapping and rescheduling them on actual physical cores. This is explained in more detail in the section 2.2.5. Since scheduling policy applicability is directly affected by the complexity of its implementation, a possible hardware implementation of the Hardware Round-Robin Scheduling policy is also given and discussed.

We analyze the performance and energy efficiency of the HRRS policy on an ACMP and compare it to the Fairness Scheduler when running multi-threaded application workloads and when running multiple instances of the single-threaded application workloads respectively. We show that it lowers total execution time by 17.2 percent and 11.71 percent on average, while being on average 7.57 percent and 6.56 percent more energy efficient respectively.

#### **1.3.2** Kernel to User mode Transition aware Hardware Scheduling Algorithm

The bottlenecks arising from a particular thread and memory management and sharing approaches may have significant effects on performance of the multithreaded applications. To tackle this issue, we propose a Kernel to User Mode Transition aware Hardware Scheduling Algorithm (KUTHS), which is influenced by the scheduling for fairness as well as the bottleneck identification techniques thereby reducing thread serialization and improving parallel thread performance.

The KUTHS technique builds upon the previously proposed HRRS technique. The KUTHS scheduler utilizes the kernel to user code execution transitions on cores to identify bottlenecks in multithreaded applications and make the rescheduling decision. These transitions occur when Operating System makes execution switches on the hardware threads from executing kernel to user code and vice versa. The KUTHS remaps hardware threads after every time quantum expires. Presuming an ACMP system composed of an Out-of-Order and an In-Order core, if the "transition" does not occur on any of the cores the KUTHS remaps hardware threads between different core types in the round-robin, like the HRRS scheduler. On the other hand, if the "transition" occurs on one of the cores, the KUTHS will promote hardware thread from that core to run on an Out-of-Order core.

We analyze and evaluate the performance of the KUTHS policy on an ACMP and show that it lowers total execution time of the application by 11.5 percent (geometric mean) compared to a Fairness-aware Scheduler. It lowers total execution time of the single application and the mix of two applications by 11.1 and 8.7 percent respectively (geometric mean) compared to a Fairness-aware Scheduler on shared LLC configuration. Besides evaluating performance, we also analyze the energy efficiency of the KUTHS scheduler on an ACMP with a shared LLC and show that it is on average 9.4 percent more energy efficient than the Fairness Scheduler.

#### **Application of KUTHS on Manycore processors**

We propose the extension of the KUTHS policy to be applicable to larger many-core systems and systems where the last-level caches are private to the group of cores. It is influenced by the Fairness-aware Scheduling and bottleneck identification techniques and thereby aims at reducing thread serialization and improving parallel thread performance. An analysis and evaluation is given for the performance of the KUTHS policy on a private LLC ACMP and show that it lowers total execution time of the application by 30 percent (geometric mean) compared to Linux OS Scheduler (ACMP Scheduler).

#### **1.3.3 Trait-aware Criticality Scheduling Algorithm**

When scheduling a workload on an ACMP the performance will be affected by the fairness of scheduling, schedulers ability to identify application bottlenecks and to make the scheduling decisions based on the workload's characteristics. In order to tackle all three important issues that scheduling of different types of workloads may encounter on an AMCP, we propose a Trait-aware Criticality Scheduling (TCS) policy which is influenced by scheduling fairness, criticality, and a workload's charac-

teristics, thereby reducing thread serialization and improving performance of multithreaded applications and multiprocess workloads on single-ISA asymmetric multicores.

The TCS method develops upon the earlier introduced HRRS method. The underlying technique of the TCS scheduling already tackles the problem of fairness, since the HRRS remaps hardware threads in round-robin way over different core types in an ACMP system after every time quantum expires. Besides, the TCS scheduling employs the short-term traits of workloads executing on hardware threads to improve the decision-making method during scheduling in a way that is more accustom with distinct characteristics of particular workloads. The TCS scheduler additionally uses the long-term traits of the software threads during the decision-making process to tackle the software thread criticality. A possible hardware implementation of the Trait-aware Criticality Scheduling policy is elaborated on since it is crucial for the applicability of the technique.

An analysis of the performance of the TCS policy on an ACMP is also given and is compared to the state-of-the-art schedulers in scheduling for fairness, criticality, and a workload's characteristics. It achieves an average speed up of 11 percent and 24.4 percent over the state-of-the-art mechanisms for scheduling for fairness and scheduling for criticality respectively. While being by only 2.6 percent slower compared to the state-of-the-art mechanisms on scheduling for workload characteristics.

#### **1.4 Thesis Organization**

Chapter 2 presents the scheduling in a computer system and the state-of-the art for thread scheduling schemes.

Chapter 3 describes benchmark suites and the simulator used for the experimental setup in this thesis.

Chapter 4 presents the cost that context switch of threads on the cores may have on the total execution time of the application running on the Chip Multiprocessor.

Chapter 5 introduces Hardware Round-Robin Scheduling Algorithm (HRRS) for Hardware Threads on the single-ISA asymmetric CMPs, a scheduler based on fairness scheduling techniques.

Chapter 6 presents Kernel to User mode Transition aware Hardware Scheduling Algo-

rithm (KUTHS), a scheduler based on scheduling for fairness amended by bottleneck identification for the single-ISA asymmetric CMPs.

Chapter 7 explains Trait-aware Criticality Scheduling Algorithm for Hardware Threads on the single-ISA asymmetric CMPs, a scheduler seeking the aggregation of the scheduling for fairness, scheduling for bottleneck identification and scheduling workload characteristics techniques.

Chapter 8 concludes this dissertation.

# 2

## State-of-the-Art and Background in Scheduling Policies on an ACMP

This chapter presents the background that is relevant to the thesis. The first section explains more broadly the concept of context switch in the chip multiprocessors and the implications it has on the scheduling policies. The chapter continues with the survey of the current state-of-the-art scheduling techniques used in multiprocessor computer architecture.

#### 2.1 Context Switching

Over the past few decades since the first CMPs emerged in 90's, both of the industry's and academia's attention have been keenly focused on conducting studies related to the practice and cost of context switching when moving thread from one core to the other. In the following sections we summarize and compare and contrast the most prominent studies which fall under three distinct categories.

#### 2.1.1 Performance Impact of Context Switching

Several context switching studies aimed at understanding the performance impact of context switching events. For instance, Agarwal et al. [16] demonstrated that multiprogramming execution substantially degrades cache performance and increases in impact as the cache size grows. Mogul et al. [17] conducted a performance reduction estimation based on the cost of context switching and found it to be on the order of tens to hundreds of microseconds, depending on the specific cache parameters. Suh et al. [18] measured the impact of context switching on page faults and performance and endorsed a speculative prefetching scheme to mitigate the performance penalties. A novel approach is proposed by Chiou et al. [19] who suggest that contrary to conventional CPU scheduling practices, it should be the memory scheduling method, potentially at all levels of the memory hierarchy, that should drive CPU scheduling and not the other way around.

Koka et al. [20] characterized context switch misses by quantifying their effects when running transactional workloads. They evaluated the possibility of intelligent process scheduling that would minimize cache misses across context switch boundaries. In other work, Li et al. [7] concluded that overheads due to burdensome cache activity from indirect context switches is more significant than the direct overhead, where direct context switches are those that occure when rescheduling threads on the same core while indirect are those that happend when moving thread from one to the other core. Similarly, Tsafrir [21] and David et al. [22] measured the separate indirect overheads caused by context switch events for the Intel and ARM platforms. In sum, nearly all of the relevant studies found that indirect overheads caused by cache activities associated with context switch events are significant. As a result, we have kept context switch overheads as a key factor to minimize in our work.

#### 2.1.2 Analytical Models for characterizing Context Switches

Various analytical models have been proposed which seek to justify the relationship between an application's temporal execution characteristics and its behavioral vulnerability to context switch misses. Such models require an ample scope of essential variables critical to the hardware, memory, and application workload and behavior in order to achieve an adequate conclusion detailing causality. An example of such work is the analytical model proposed by Agarwal et al. [16] and Suh et al. [23], [24] which estimate overall cache miss rates taking into regard context switch misses. In order to obtain a continuous cache miss rate curve, Suh et al. relied on a model based upon a small fully associative cache. However, applying a fully associative cache structure to the LLC would be unrealistic and would lead to inaccurate results. The model proposed by Hwu et al. [25] focused on predicting the quantity of context switch misses for the worst case scenario. Liu et al. [26] grouped context switch misses into two classes, namely replaced misses and reordered misses. In addition, their work elaborated on an analytical model that reveals the causal correlation between cache design parameters, an application's temporal execution pattern, and the amount of context switch misses which appear during the execution of the application. This model was utilized to study the effect which prefetching and cache size can have on the amount of context switch misses.

Certain assumptions must necessarily be made when developing analytical models. For example, the model designed by Liu et al. [26] is built with the assumption of an LRU replacement policy implementation even though alternative replacement algorithms have been advanced which perform better. Another characteristic particular to analytical models to consider is that though they may be suitable for offline analysis, they often lack implementation feasibility in hardware regarding incurring a low area overhead.

#### 2.1.3 Managing Cache Misses caused by Context Switches

Performance degradation penalties due to context switch misses may be addressed via two channels, namely either increasing the scheduling time slice or prefetching the cache state right before the new scheduling mapping is initiated. Increasing time slice is a preventive measure while cache state prefetching is more of a remedy. The general idea behind prefetching is to measure and save an application's locality at the moment when it gets swapped out due to a context switch. The locality is restored through prefetching the next time the application gets CPU time thereby mitigating the cost of additional cache misses incurred due to the context switch event. Previously advanced solutions that make use of prefetching differ in how the locality is stored and restored. An example is the work done by Cui et al. [27] who apply a Global-

history-list (GHL) in their method of prefetching. The GHL technique maintains a complete list of cache lines ordered by temporal of usage behavior. Another case is that of Daly et al. [28] who evaluated the impact of context switch miss events in highly partitioned virtualized systems. They proposed to warm the cache state by prefetching the application's working set and restoring the cache lines. The GHL and cache restoration methods differ in implementation specifics to some extent but perform relatively on par with one another although GHL performs slightly better at the cost of additional hardware overhead and complexity. In some of the most recent related work [29], the authors describe methods that mitigate the bandwidth overhead of these other prefetchers.

Brown et al. [30] proposed accelerating thread performance after a context switch event by predicting and prefetching the working set of the application. In their proposal, the access behavior of a thread is measured and saved in a compact form during pre-migration. This saved behavior is used to prefetch appropriate data to create a warm state on the core which the thread has been migrated to. Prefetching the data after a context switch event can help to solve or alleviate the problem of cold starts. However, this approach works to minimize the number of cold starts for those applications for which it matters. Zebchuk et al. [29] help to demonstrate the inability of all cache restoration prefetching techniques to dynamically adapt to the workload behavior as their main limitation.

#### 2.2 Scheduling Policies

Due to possible performance and efficiency gains, there has been increasing interest in heterogeneous multicore architectures, and various scheduling proposals have been presented throughout the past two decades. In this section, we present the state-of-the art of the scheduling schemes on the Chip multiprocessors. We summarize, compare, and contrast the works under five different categories.

#### 2.2.1 First Studies on Scheduling Policies on an ACMP

Since the early nineties and the introduction of the idea of the chip multiprocessor, research community have recognized the impact of scheduling. Miller [31] presented

a scheduling algorithm for an asymmetric system called Single Architecture Heterogeneous Multiprocessor or SAHM, which did not support multi-programming. Grochowski et al. [32] studied the usefulness of such cores for saving energy and improving throughput. Moncrieff et al. [33] and Menasce et al. [34] analytically studied tradeoffs of fast and slow processors in heterogeneous systems. They observe that a system with many slow and few fast processors are cost and performance effective.

An ACMP which consists of multiple cores of the same ISA but of different sizes was proposed by Kumar et al. in [35]. Their process consists of sampling for and choosing the core that will execute in the most power efficient manner each time a new phase or program is detected. This work was later expanded to include performance maximization of multithreaded applications [4].

#### 2.2.2 Scheduling based on Profiling and Sampling

Work by Becchi [9] consists of an ACMP that includes two distinct core sizes where thread to core assignment is managed by initiating a mandatory swap of threads between two different sized cores in order to measure the corresponding performance ratio. Based on this ratio, the threads are then scheduled to their core that will maximize the system performance. This work has given insight into ratio based ACMP scheduling techniques but is limited as the number of distinct core types used increases. Other work in this area has been done by Saez et al. [36] who use a utility factor, defined as the ratio of L1 miss latency compared to a baseline ACMP configuration (only small cores), with the aim of optimizing the performance of both single and multithreaded workloads. Likewise, Koufaty et al. [10] determine optimal thread to ACMP core mapping using a biasing method estimated by the quantity of external memory stalls and internal pipeline stalls. Another approach is detailed in the work by Srinivasan et al. [15] who propose a formula based ACMP thread to core scheduling method which is used to estimate and compare thread performance on individual cores.

A main concern of sampling approaches towards thread scheduling is the runtime overhead produced when running multithreaded applications. In their work, [37] Shelepov et al. use an architectural signature based on the cache misses for different thread to core mappings collected during offline profiling in order to appropriately schedule threads and a reduce runtime overhead. However, since the signatures are fixed and used for the duration of a program, the approach fails to take into regard the phases of the programs. On the other hand, phase classification and regression analysis is used by Khan et al. in their work [38] to optimize thread to core mapping in an ACMP.

#### 2.2.3 Scheduling focused on Power and Energy

The first works that address the energy issue in shared-memory multiprocessors look at energy savings in cache coherence management [39], [40]. Motivated by the perception that a large part of snoops do not locate copies of data in multiple of the other caches in a snooping bus-based SMP, Moshovos, et al [39] propose Jetty to reduce the energy consumed by snoop requests. Saldanha and Lipasti [40] study the impacts of decreasing speculation in a scalable snoop-based scheme, and note significant potential of energy conservation by utilizing serial snooping for load misses.

Instead, the thrifty barrier [41] works on the CPU energy savings potential stemming from barrier imbalance in parallel applications. These techniques are not exclusive of each other and could be combined for improved overall results. With respect to microarchitectural differences, Chen et al. [42] chose to implement their ACMP with cores consisting of separate branch predictor, issue width, and L1 cache sizes that together with their scheduling method, achieve throughput and energy efficiency improvements. In a separate scheduling approach, Annavaram et al. [43] focus on staying withing a power budget by measuring the Energy per Instruction of an ACMP running multithreaded applications and using the small cores to run the parallel sections of code and then migrating to execute on the larger cores for the sequential sections. Scheduling based power management techniques have also been studied in the work by Winter et al. [44] which used several sampling based algorithms to analyze the optimal thread to core mapping.

Liu et al. [26] studied optimal scheduling of independent programs on a preemptive heterogeneous multiprocessor system. They use past non-critical thread barrier stall times to predict future thread criticality and DVFS accordingly. In contrast to this history-based approach, thread criticality predictor [45] predicts thread criticality based on current behavior, regardless of barriers. They also use the predictor to improve threading building blocks task stealing, building from the occupancy-based approach of Contreras and Martonosi [46]. But the work by Bhattacharjee and Martonosi [45] is distincts, in that they use criticality to guide task stealing for performance gains with little hardware overhead.

## 2.2.4 Scheduling based on Workload Characteristics

Exploiting counters for the improvement of hardware-aware scheduling policies has been elaborated on in related research work [47]. For instance, hardware performance counters are utilized to coordinate the scheduling of various independent threads which do not belong to the same application in order to reduce power consumption on CMPs. Along with similar approaches [48], [49], [50], these works demonstrate how lowlevel counter measurements can potentially greatly benefit the optimization of performance. The authors of [51] make use of cache-related performance measurements in order to enforce threads sharing a common data structure to also share a common last-level cache.

In a similar work, [52] the researchers demonstrate a NUMA-aware scheduler based on performance counters. Their scheduler observes memory related counters and calculates which corresponding threads are sharing data on a common Non-Uniform Memory Access (NUMA) node. The scheduler, therefore, can manage thread mapping tasks easier by placing them based on the same resource they are sharing common to the most efficient NUMA node. While approach is particular to OpenMP type of parallel applications, a more generic approach is presented in [53] where a NUMA-aware scheduler has also been introduced. The authors demonstrate that schedulers which are not necessarily aware of the hardware architecture could very well have a negative impact upon performance. Another non-NUMA approach has also been presented in [54]. The whole of these approaches best illustrate how detailed and precise scheduling policies improve performance when there is contention of hardware resources. Lastly, the works [55] and [56] provide an extra discussion of the accuracy and the benefits of different counters measurement libraries and approaches.

## 2.2.5 Fairness-aware Scheduling

For heterogeneous CMPs based on a single-ISA, optimizing scheduling based on a fairness criteria is of key significance. There are several fairness scheduling schemes available but an excellent example of achieving equal time and progress balancing is presented by Van Craeynest et. al. [12] detailed below.

#### **Equal-time Scheduling**

In order to properly balance the threads on different core types, the equal-time scheduling method assigns threads to cores in such a manner that all threads get equal amount of execution time on each different core type. This is achieved by observing the amount of time (in terms of scheduling quanta or time slices) each thread has been running on the distinct types of cores. If there are imbalances between threads and the amount of time each has had on a core type, then the scheduler will subsequently remap the threads at the next scheduling quantum to ameliorate the imbalance.

A straightforward implementation of a equal time scheduling scheme is a roundrobin or random thread to core mapping. These methods generally ensure that all threads will spend equal time running on all core types dependent upon the duration of the scheduling quantum and the total execution time of the application. These schemes may be modified to consider preserving data locality by not migrating threads among identical cores (i.e. cores of the same type).

A drawback with equal time approaches, however, is that fairness in a broader sense is not necessarily guaranteed. For instance, while all threads may receive equal time on all core types, not all threads may be making equal progress due to slowdown from different workload characteristics and memory requisites. Therefore, unfairness may still be present in an equal time scheme due to some threads making proportionally less progress than others. Conversely, if the threads are mainly homogeneous, namely exhibiting close to identical behavior, this imbalance ceases to exist and equal time scheduling will have the same effect as equal progress scheduling. Heterogeneous workloads, on the other hand, do not experience an identical one to one relationship of time running and progress made between different threads and hence must be managed more carefully than an equal time scheme to ensure fairness. Some homogeneous workloads may actually also end up exhibiting these same characteristics as heterogeneous workloads especially if the different threads end up processing separate sections of an application's input data.

Van Craeynest et. al. take this possible imbalance into regard in their solution by proposing a scheduling scheme that uses equal progress in order to more closely achieve fairness.

### **Equal-progress Scheduling**

To achieve fairness for all threads, equal progress scheduling's main focus is on enabling all threads to make equal progress or at least experience equal slowdown. This scheme hence involves observing the slowdown of each thread and producing a thread to core mapping such that the slowest threads are accelerated by scheduling them to execute on the fastest cores. As the thread experiencing the most slowdown (compared to the other threads) is accelerated, the other threads will end up running on the smaller and slower cores. Fairness is consequentially achieved as the slowdown of all threads converge.

Correctly calculating a thread's slowdown is a critical feature in the equal progress approach and is computed by comparing the total execution time of the thread on the heterogeneous CMP with the total execution time when running the thread only on a large core. The execution time of the thread on the heterogeneous CMP can be observed by accumulating the number of scheduling quanta or time slices  $TS_i$  the thread has been executing thus far on all core types. The total execution time of the thread on the single large core, however, is non-trivial to know in real time and must be estimated dynamically. For instance, Van Craeynest et. al. estimate the execution time of a thread running solely on the large core by firstly observing the number of quanta the thread was run on the large core compared with the smaller cores. Then, they rescale the time a thread has spent running on the small cores using an approximate scaling factor *R* of the large versus small cores, see Equation (2.1).

$$S_i = \frac{T_{het,i}}{T_{big,i}} = \frac{TS_{big,i} + TS_{small,i}}{TS_{big,i} + TS_{small,i}/R_i}$$

(2.1)

This scaling factor is estimated using a model-based scheduling technique which constantly monitors the CPI on both core types. This information is fed into an analytical model which produces the corresponding large versus small core scaling factor. An advantage of using this technique is that the scaling factor is continuously updated as the monitored CPI values change on the different core types. In contrast to other static methods of gathering CPI values such as history-based or sampling scheduling techniques, Van Craeynest et. al. use what they term the PIE model [11] to estimate the large versus small core scaling factor.

It is important to note that model-based approaches, such as PIE, require substantial hardware support for constant CPI monitoring and analysis. The effectiveness of PIE relies on the accuracy in monitoring and the analytical model.

## 2.2.6 Scheduling targeting Bottlenecks in Parallel Applications