#### ALGORITHMS ACCELERATION OF PATTERN-MATCHING IN MULTI-CORE ARCHITECTURES David Ródenas Picó

Dipòsit Legal: T-1350-2011

**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

David Ródenas Picó

# ALGORITHMS ACCELERATION OF PATTERN-MATCHING IN MULTI-CORE ARCHITECTURES

### DOCTORAL THESIS

directed by Dr. Francesc Serratosa Casanelles

Departament d'Enginyeria Informàtica i Matemàtiques

Universitat Rovira i Virgili

Tarragona 2011

# Index

1

2

|      | Index                                                   | i    |

|------|---------------------------------------------------------|------|

|      | List of publications of this thesis                     | V    |

|      | Glossary                                                | vii  |

|      | Figure index                                            | ix   |

|      | Index of tables                                         | xi   |

|      | Index of algorithms                                     | xiii |

|      | Abstract                                                | xv   |

| Intr | oduction                                                | 19   |

| 1.1  | Current Desktop Processors                              | 22   |

|      | 1.1.1. Architectures                                    | 22   |

| 1.2  | Algorithms and Parallelism                              | 24   |

|      | 1.2.1. Parallelization tools                            | 24   |

| 1.3  | Graph Matching algorithms                               | 27   |

| 1.4  | Streaming and Scientific applications                   | 28   |

| Obj  | ectives                                                 | 31   |

| 2.1  | Graph Matching and Scientific applications              | 32   |

| 2.2  | Annotated Programming Model over Multi-Core             | 33   |

| 2.3  | Annotated Programming Model over Distributed Memory     | 35   |

| 2.4  | Heterogeneous processor simulator                       |      |

| 2.5  | Graph Matching preprocessing and Streaming applications | 41   |

| 2.6  | Annotation based programming models and streaming       | 43   |

| 2.7  | Graph matching on current architectures                 | 47   |

#### ii

## INDEX

| 3 | State | e Of The Art51                                                     |

|---|-------|--------------------------------------------------------------------|

|   | 3.1   | Graph matching51                                                   |

|   | 3.2   | Benchmarks55                                                       |

|   | 3.3   | Architectures                                                      |

|   | 3.4   | Tools                                                              |

| 4 | Rela  | ted Work                                                           |

| 5 | New   | v Contributions107                                                 |

|   | 5.1   | Multi-Processor tools over Multi-Core Homogeneous Shared Memory107 |

|   | 5.2   | Annotation based Programming Model over Distributed Memory113      |

|   | 5.3   | Heterogeneous Modular Multi-Core simulator116                      |

|   | 5.4   | Annotation Based Programming Model For Streaming Applications121   |

|   | 5.5   | Graph Matching on Current Architectures129                         |

|   | 5.6   | New Tools                                                          |

| 6 | Prac  | tical Evaluation135                                                |

|   | 6.1   | Multi-Processor tools over multi-core135                           |

|   | 6.2   | Annotation programming model over distributed memory141            |

|   | 6.3   | Heterogeneous modular multi-core simulator143                      |

|   | 6.4   | Annotation Based Programming Model Over Heterogeneous Distributed  |

|   |       | Memory Streaming Applications146                                   |

|   | 6.5   | Graph Matching on Current Architectures152                         |

| 7 | Com   | munity Results Based On This Thesis159                             |

| 8 | Con   | clusions165                                                        |

|   | 8.1   | Future work167                                                     |

| 9 | Refe  | erences169                                                         |

## List Of Publications Of This Thesis

- D. Ródenas et al., "Optimizing NANOS OpenMP for the IBM Cyclops multithreaded architecture," 19TH IEEE International Parallel & Distributed Processing Symposium (IPDPS 2005), 2005.

- [2] D. Rodenas, X. Martorell, J. Costa, T. Cortes, and J. Labarta, "Running BT Multi-Zone on non-shared memory machines with OpenMP SDSM instead of MPI," *Proceedings of the XVI Jornadas de Paralelismo*, Sep. 2005.

- [3] D. Ródenas et al., "Exploiting multilevel parallelism using OpenMP on a massive multithreaded architecture," *Journal of Embedded Computing*, vol. 2, p. 141–155, Apr. 2006.

- [4] P. Carpenter, D. Rodenas, X. Martorell, A. Ramirez, and E. Ayguade, "Code generation for streaming applications based on an abstract machine description," *Universitat Politécnica de Catalunya, UPC-DAC-RR-CAP-2007-3*, 2007.

- [5] F. Cabarcas, A. Rico, D. Rodenas, X. Martorell, A. Ramirez, and E. Ayguade, "A module-based cell processor simulator," 3rd HiPEAC Advanced Computer Architecture and Compilation for Embedded Systems. ISBN: 978-90-382-1127-5, 2007.

- [6] A. Rico, F. Cabarcas, D. Rodenas, X. Martorell, A. Ramirez, and E. Ayguade, "Implementation and validation of a Cell simulator using UNISIM," 3rd HiPEAC Industrial Workshop, IBM Haifa, Israel, 2007

- [7] F. Cabarcas, A. Rico, D. Rodenas, X. Martorell, and A. Ramirez, "CellSim: A Validated Modular Heterogeneous Multiprocessor Simulator," *Proceedings of the XVII Jornadas de paralelismo*, Apr. 2007.

vi

#### LIST OF PUBLICATIONS OF THIS THESIS

- [8] P. Carpenter, D. Rodenas, X. Martorell, A. Ramirez, and E. Ayguadé, "A streaming machine description and programming model," in *Proceedings of the* 7th international conference on Embedded computer systems: architectures, modeling, and simulation, Berlin, Heidelberg, 2007, p. 107–116.

- [9] P. Carpenter, D. Rodenas, A. Ramirez, X. Martorell, and E. Ayguade, "Code generation for streaming applications based on an abstract machine description." IST ACOTES Project Deliverable D2.2, May-2007.

- [10] P. Carpenter, A. Ramirez, X. Martorell, D. Rodenas, and R. Ferrer, "Report on Streaming Programming Model and Abstract Streaming Machine Description 1st version." IST ACOTES Project Deliverable D2.1, Sep-2007.

- [11] F. Cabarcas, A. Rico, D. Rodenas, X. Martorell, A. Ramirez, and E. Ayguade, "CellSim: A Cell Processor Simulation Infrastructure," 4th HiPEAC Advanced Computer Architecture and Compilation for Embedded Systems. ISBN: 978-90-382-1288-3, 2008.

- [12] D. Rodenas, R. Ferrer, X. Martorell, and E. Ayguade, "ACOTES Stream Programming Model," 4th HiPEAC Advanced Computer Architecture and Compilation for Embedded Systems. ISBN: 978-90-382-1288-3, pp. 19-22, Jul. 2008.

- [13] P. Carpenter, A. Ramirez, X. Martorell, D. Rodenas, and R. Ferrer, "Report on Streaming Programming Model and Abstract Streaming Machine Description Final version." IST ACOTES Project Deliverable D2.2, Sep-2008.

- [14] D. Rodenas, F. Serratosa, and A. Solé-Ribalta, "Graph Matching on a Low-cost & Parallel Architecture," *Iberian Conference on Pattern Recognition and Image Analysis, IbPRIA 2011, LNCS 6669*, p. 508–515, 2011.

- [15] D. Rodenas, F. Serratosa, and A. Solé-Ribalta, "Parallel Graduated Assignment Algorithm for Multiple Graph Matching based on a Common Labelling," *Graph based Representations, GbR2011, Münster, Germany, LNCS 6658*, pp. 164-174.

- [16] D. Rodenas, F. Serratosa, and A. Solé-Ribalta, "Massive Parallel Graduated Assignment Graph Matching Experiences on Low Power Architectures," *Submited to IJPRAI*.

## Glossary

- **annotation based programming model**: programming model which extends an existing programming models with annotations, as directives or comments. Annotations improves the existing information and the capacity of taking advantage of underlying architecture without changing application structure significantly.

- **cache**: small memory with a small latency that contains a partial copy of main memory data.

- **cluster**: group of one or more processing units sharing the same memory on a distributed memory system.

- **core**: part of a microprocessor which is composed by one or more execution threads, functional units and data cache.

- **distributed memory**: system with multiple process units which each process unit has its own memory and restricted access to memory of other process units. It is required explicit communication between process units in order to receive or to send required information.

- execution thread: set of ordered instructions with its own register file.

- **functional unit**: process hardware which executions mathematical computations usually real computations.

- **hardware**: physical part of a computer, normally part that electronically computes a function.

viii

#### GLOSSARY

- **heterogeneous system**: system with multiple process units which has more than one instruction set and characteristics.

- **homogeneous system**: system with multiple process units which all its units share the same instruction set and characteristics.

- many-core processor: a multi-core with many cores.

- multi-core: micro-processor containing two or more cores.

- **multi-threading (processor)**: processor that contains multiple execution threads at any of its cores.

- **multiprocessor**: system composed with multiple processors interconnected, and, if not is explicit, with shared memory and homogeneous.

process unit: core.

programming model: set of tools of compilation and programming.

- **register file**: set of small and very fast memories directly accessible by assembler instructions used as temporal values, it includes the program counter which contains the address of next instruction.

- **shared memory**: system which all its process units have access with no restrictions to all available memory, but small time penalizations.

- software: data that encodes instructions to execute an algorithm.

- **system with lineal memory address**: system which all its process units can access to memory of all other units without restrictions but paying a great time penalization. It is possible found specific instructions designed to send and receive information as memory distributed.

thread: execution thread.

# **Figure Index**

| Figure 3.1: NPB-MZ [41] BT-MZ visual mesh of zones58                              |

|-----------------------------------------------------------------------------------|

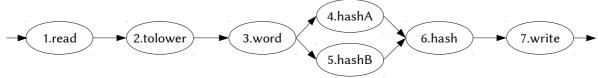

| Figure 3.2: Tolower stream graph61                                                |

| Figure 3.3: Wordhash stream graph61                                               |

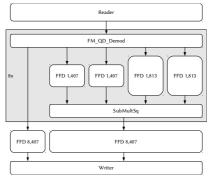

| Figure 3.4: FMradio stream graph62                                                |

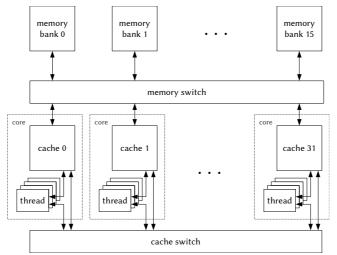

| Figure 3.5: Overview of the BlueGene/Cyclops processor architecture               |

| Figure 3.6: Overview of the BlueGene/Cyclops memory hierarchy                     |

| Figure 3.7: Cell B.E. Sony Playstation3 processor implementation block diagram68  |

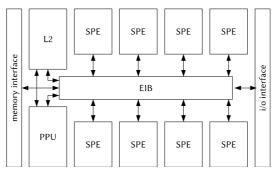

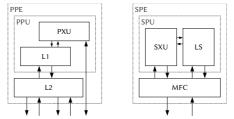

| Figure 3.8: Cell B.E. PPE (main processor) and SPE (auxiliary vector processors)  |

| blocks diagrams70                                                                 |

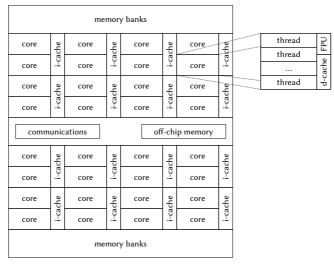

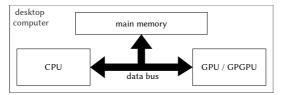

| Figure 3.9: Current desktop computer overview72                                   |

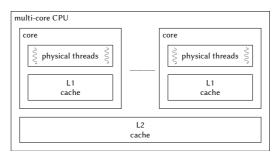

| Figure 3.10: Overview of a desktop computer multi-core CPU72                      |

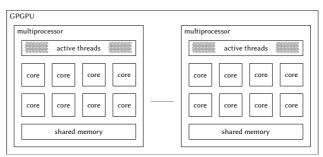

| Figure 3.11: NVIDIA GPGPU architecture overview73                                 |

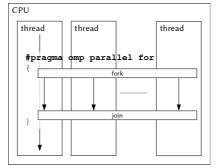

| Figure 3.12: OpenMP fork/join thread execution model                              |

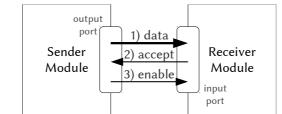

| Figure 3.13: Unisim connection model based on ports and three signals             |

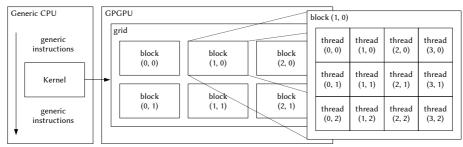

| Figure 3.14: CUDA logical execution space                                         |

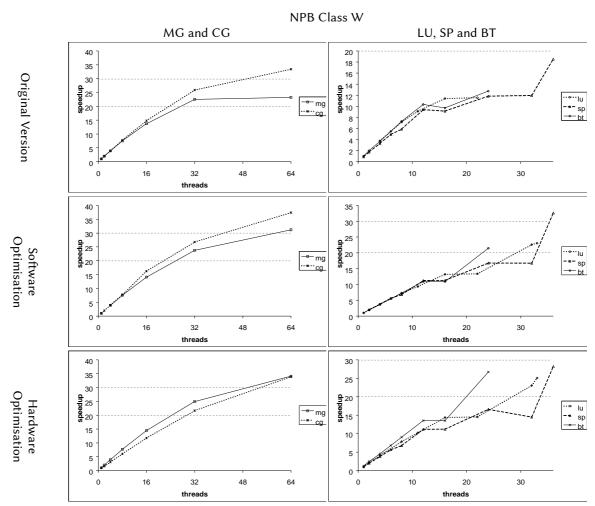

| Figure 6.1: Cache behaviour for the MG Class W program in the IBM                 |

| BlueGene/Cyclops architecture                                                     |

| Figure 6.2: Scalability of the NPB programs Class W in the IBM BlueGene/Cyclops   |

| architecture137                                                                   |

| Figure 6.3: Scalability of the NPB-MZ programs class W in the IBM                 |

| BlueGene/Cyclops138                                                               |

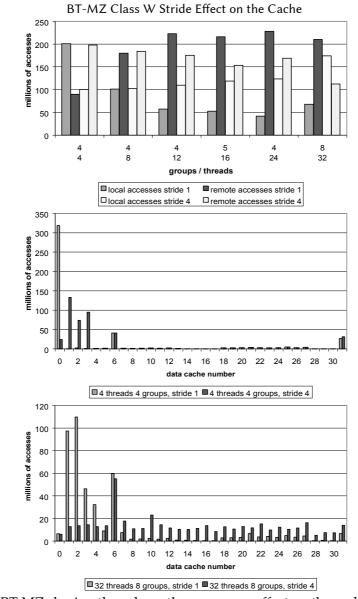

| Figure 6.4: SP-MZ groups effect on the cache of the IBM BlueGene/Cyclops139       |

| Figure 6.5: BT-MZ sharing threads on the same core effect on the cache of the IBM |

х

## FIGURE INDEX

| BlueGene/Cyclops                                                                         |

|------------------------------------------------------------------------------------------|

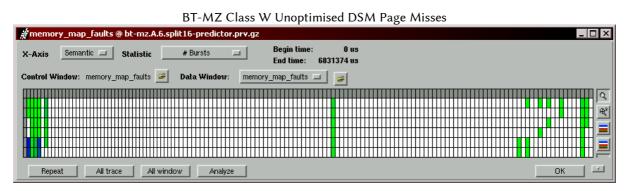

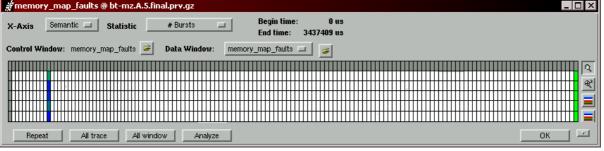

| Figure 6.6: BT-MZ Class W memory map of page misses for each node on a SDSM.             |

|                                                                                          |

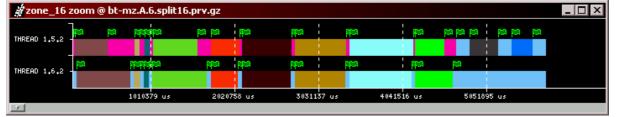

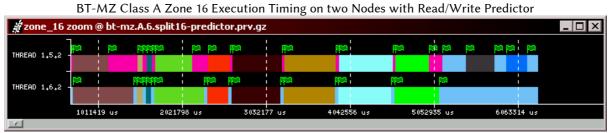

| Figure 6.7: BT-MZ Class A zone 16 execution timing142                                    |

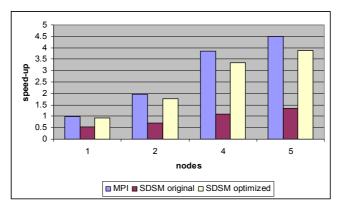

| Figure 6.8: BT-MZ Class A performance comparison for MPI and SDSM143                     |

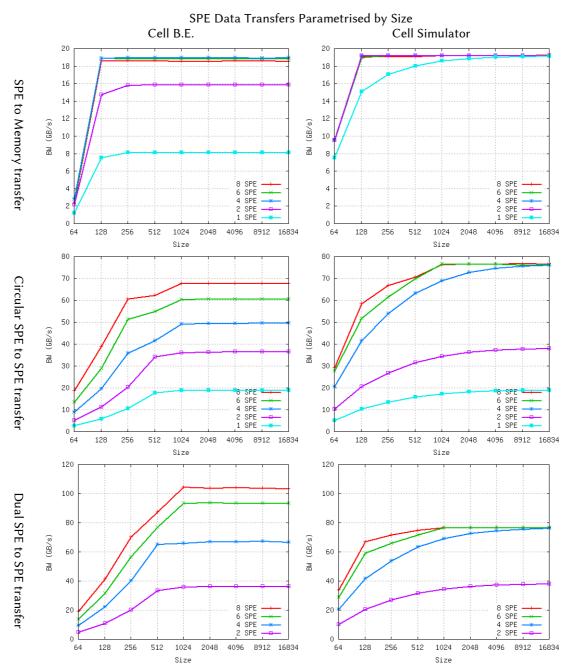

| Figure 6.9: Cell B.E. versus Cell Sim SPE interconnection bus behaviour study145         |

| Figure 6.10: Stream programming model prototype scalability of FMradio and               |

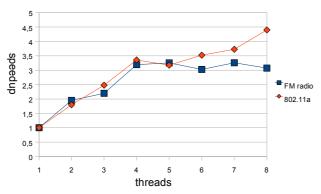

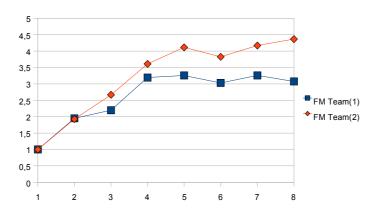

| Nokia's Wifi 802.11a using only task and pipeline parallelism147                         |

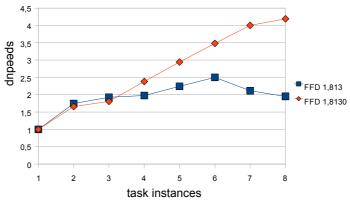

| Figure 6.11: Stream programming model prototype scalability of the FFD filter using      |

| only data parallelism147                                                                 |

| Figure 6.12: Stream programming model prototype scalability of the FMradio               |

| without data parallelism (1) and FMradio with data parallelism (2) both using task       |

| and pipeline parallelism148                                                              |

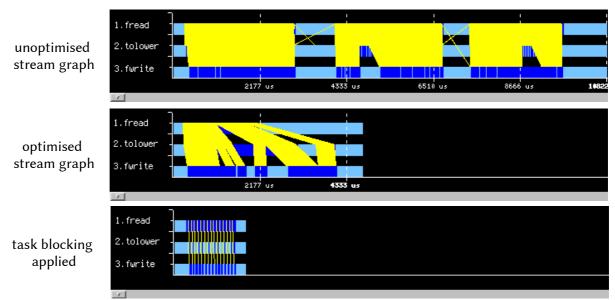

| Figure 6.13: Paraver traces of the tolower benchmark as stream program149                |

| Figure 6.14: Streaming annotated programming model characteristics by example.           |

|                                                                                          |

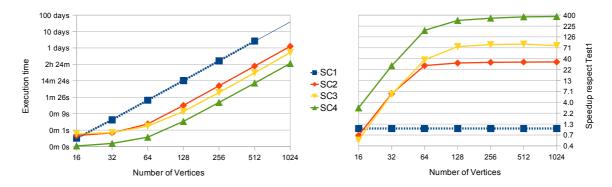

| Figure 6.15: Run time of the 4 scalability tests respect to the number of vertices and   |

| speed-up of the parallel solutions (SC2, SC3, SC4) respect to the serial solution (SC1). |

| Both plots vertical axis are in logarithmic scale154                                     |

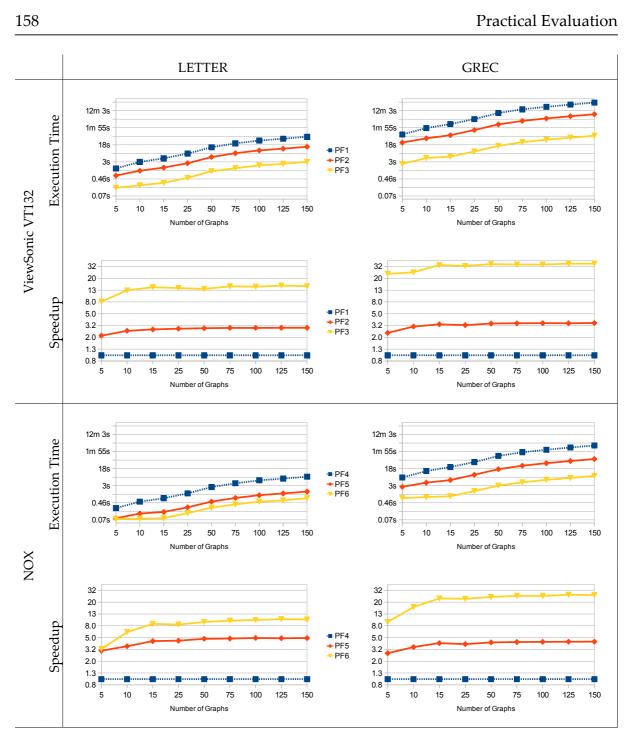

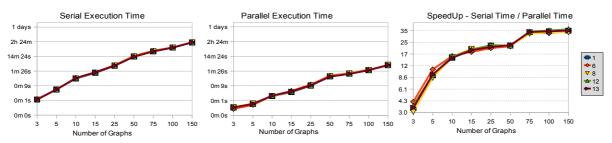

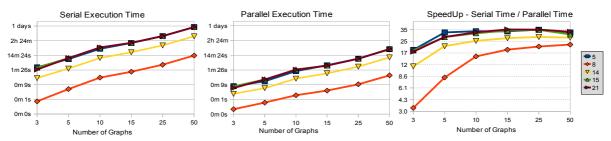

| Figure 6.16: Run time and speedup of the small graph multiple matching algorithm         |

| given an architecture, a dataset and the number of graphs                                |

# **Index Of Tables**

| Table 3.1: NPB 3.0 [40] characteristics                                     | 57  |

|-----------------------------------------------------------------------------|-----|

| Table 3.2: NPB-MZ [41] program SP-MZ Class W zone characteristics           | 58  |

| Table 3.3: NPB-MZ [41] BT-MZ Class W zone characteristics                   | 58  |

| Table 3.4: NPB-MZ [41] BT-MZ Class A zone characteristics                   | 59  |

| Table 3.5: BlueGene/Cyclops prototype configuration used on this thesis     | 66  |

| Table 3.6: Intel + NVIDIA GPGPU desktop computer architectures used on this |     |

| thesis                                                                      | 74  |

| Table 6.1. List of algorithms and architectures evaluated                   | 153 |

| Table 6.2. List of algorithms and architectures evaluated                   | 155 |

# **Index Of Algorithms**

| Algorithm 3.1 | 53 |

|---------------|----|

| Algorithm 3.2 |    |

| Algorithm 3.3 |    |

| Algorithm 3.4 |    |

| Algorithm 3.5 |    |

| Algorithm 3.6 |    |

| Algorithm 3.7 |    |

## Abstract

Pattern matching algorithms are a classification task of pattern recognition that attempts to assign each input value to one of a given set of classes. Some of these algorithms use graphs because they have more capacity to capture the knowledge of the model but their comparison or matching is also more computationally expensive. This restriction makes them computationally not suitable for real-time applications.

In the current market scenario desktop computer architectures have evolved towards supercomputing architectures. These architectures generally provide a vast computing capabilities, but they require parallelise existing applications in order to take advantage of existing hardware. Consequently, applications and algorithms must be modified and adapted in order to take advantage of all available resources.

Algorithms and programs must be redesigned to be able to work on parallel environments. In order to redesign algorithms, programmers and algorithm designers must be aware of architecture limitations and must know parallelism techniques. The parallelisation of any program is usually a very complex tasks, but in many cases these require an expert programmer who knows specialised techniques for parallelism. We focus on OpenMP. OpenMP is a programming model which allows to parallelise an application by adding just few directives or comments. This programming model is very easy to use, and almost a non-expert on parallelisation can use it in order to achieve a good parallelisation and resource usage. It was initially designed for supercomputers with shared-memory with multiple processors instead of multiple cores.

We group research on this thesis on two steps: 1) for developing tools to allow non-expert programmers to take advantage of parallel architectures and 2) for applying extracted knowledge and create a version of graph pattern-matching

#### ABSTRACT

algorithms able to run quasi real-time on current desktop computers, focusing on those having low power consumption.

We use supercomputers as a starting point. They have been computing parallel programs for many years and almost all their users are no computer scientists. We have selected OpenMP from all available tools because it is one of the tools with better usability. Supercomputers are not desktop computers. Supercomputer programs and benchmarks does not include our target algorithms.

Firsts steps of this thesis compare multi-core processors with supercomputers. General purpose multi-core, now available on almost any desktop computer, are very close to shared-memory multiprocessors supercomputers. We use OpenMP as a target programming model, and we use existing and well known parallel supercomputing benchmarks in order to validate our affirmation. We will explore some critical differences as cache behaviour and we will solve how to overcome them and have good results on multi-core. We also will focus on one kind of parallel applications which has multiple levels of parallelism, having an external level of parallelism working with coarse-grain parallelism. Firsts distributed-memory and heterogeneous multi-core processor have been introduced, and we try to validate OpenMP on these architectures. First we prove that OpenMP is able to have a good performance on distributed-memory architectures. In this case we found that it have a special good performance on programs with multiples levels of parallelism. We also realise that OpenMP has an important lack of expressiveness for distributedmemory and heterogeneity. We propose a programming model derived from OpenMP able to extract streaming parallelism from serial applications. This model introduces two clauses able to convert a serial program into a streaming program. Proposed directives are able to create a graph representation of a streaming program, nodes are executing kernels and edges communication nodes. In that point we realise that multi-core can become very complex, and we collaborate in the creation of a modular simulator of heterogeneous multi-core. We contribute with an abstraction which allows to connect each module in any configuration. We expect from this simulator to help to create architectures closer to programmer needs and programming models restrictions.

In the lasts steps of the thesis we use extracted knowledge to effectively create parallel versions of the pattern matching algorithms. We focus on graph matching algorithms and we implement them on desktop computers. Target computer used

xvi

> are desktop computers, but we do not limit our implementations to the generalpurpose CPU: our target processors are either main processor and graphic processor. Main processor is a shared-memory homogeneous multi-core, very close to our firsts steps, on the other hand, graphic processor unit is a massive parallel processor which has distributed-memory and heterogeneous environment. We adapt previous OpenMP like tools to these final architecture and we use them to parallelise serial algorithms. We also introduce two common techniques in parallel programming which allows to redesign existing algorithms but without changing algorithm results. We show a methodology which allows to apply previous techniques, it transforms program equations in order to obtain an optimal parallelisable performance. We also show how to take advantage of existing private memory inside graphic processors but without rewriting the application. We evaluate presented algorithms and transformations to show how they effectively use underlying existing resources on desktop computers.

> Nowadays desktop computers are indeed desktop supercomputers, not only by its performance, but also because its complexity and programmability. We show how a programming model can help to create parallel applications and how this applications can take advantage of existing hardware. One thing we have for sure, serial programs will not use efficiently existing hardware on desktop computers. This thesis has the objective to help to overcome this limitation.

xvii

## **Chapter 1. Introduction**

Classification is a task of pattern recognition that attempts to assign each input value to one of a given set of classes. Pattern recognition algorithms generally aim to provide a reasonable answer for all possible inputs and to do inexact matching of inputs. Pattern recognition is studied in many fields such as psychology, cognitive science, computer science and so on. Depending on the application, inputs of the pattern recognition model or objects to be classified are described by different representations. The most usual representation is a set of real values but other common ones are strings, trees or graphs. These structures have more capacity to capture the knowledge of the model but their comparison or matching is also more computationally expensive. The distance between a pair of strings or trees is computed in polynomial time; nevertheless, the computation of the distance between a pair of graphs is exponential respect the number of vertices. For this reason, some algorithms that compute the distance between graphs have been presented obtains a sub-optimal distance. Although these last algorithms have a polynomial computational cost, the real run time is not acceptable for some applications such as fingerprint classification, on-line face identification or robot navigation, between others.

Nowadays desktop computer architectures have evolved towards supercomputing architectures. These architectures generally provide multiple processors and complex memory hierarchy [17]. A simple desktop computer may contain tens of small processors called cores [18], some of them present at main processor [19], but most of them are present as auxiliary coprocessors like graphical processors [20]. Main processor is usually a general-purpose processor [21]: a processor that contains at least one core able to execute almost any algorithm with an

#### Introduction

acceptable trade off in efficiency. As a counterpart, some specialized algorithms, like video decoding or 3D computations can not be executed on reasonable time and real-time is not possible on such processors. Specialized cores [22], like graphical processor cores, are provided in order to speed-up these algorithms. As the number of cores grows, the complexity of the memory hierarchy and its interconnection network also grows. Consequently, applications and algorithms must be modified and adapted in order to take advantage of all available resources.

Most graph-matching algorithms are designed to be executed on a single core and general-purpose processor [23-25]. Consequently, they are not designed to take advantage of all available resources on current desktop computers. On the other hand, as the number of cores on desktop computers grows, the execution speed of a generic core remains unchanged [26], that means that classical graph-matching algorithms have no faster execution on improved architectures. Graph-matching algorithms must be redesigned to take advantage of all present resources in order to achieve real time applications.

There are three major challenges on new paradigm programming: work distribution, data distribution and synchronization [27]. The implementation of classical algorithms assumes that there is only one processor, which means that all instructions are executed in sequential order. Adaptation of these algorithms to the parallel paradigm starts in the identification of independent algorithm steps, those that can be executed concurrently. Each step access to a certain group of data, data can be accessed locally or must be transferred from another location. All steps must process data to achieve the final algorithm result, which means that synchronization is required to ensure a correct computation. Algorithms parallelisation is a complex task that usually requires a deep knowledge of the underlying architecture and, for the same reason, their performance are limited to computers with analogous architectures.

Compilers do not transform or adapt algorithms automatically. Automatic parallelisation might be perfect to this task: they are able to transform automatically applications to their underlying architecture. Unfortunately there is not much practical application: a compiler does not know programmer intentions, compiler can not go beyond information presented at compile time [28-30]. Some recompilejust-in-time techniques are able to overcome this limitation by collecting statistical

20

#### 1. Introduction

data from current execution. This technique allow to modify code from the original program in order to obtain statistically re-engineered code. Therefore, once again, the compiler does not know the programmer's intentions, just the programmer's instructions. Because of that, the compiler is not able to know for sure which transformations are safe and coherent with ideas beyond the original code. There is only one solution: programming model must allow the addition of relevant information to the compiler. The compiler must use these provided information to optimize a program to the underlying architecture. Nevertheless, while defining this new programming model, it has to be considered that there are a large number of programmers that implement their algorithms in current languages, and so, any addition of information must respect existing programming models and take advantage of already written code.

The aim of this thesis is to present a new research on multi-core architectures applied to graph-matching algorithms in order to easy their adaptation. The starting point are supercomputers: they already have multiple processors and a large list of programming models and compilers. Supercomputer's programming models and compilers help non expert programmers to take advantage of supercomputers resources. The first steps of this thesis are to compare graph-match algorithms against typical supercomputer algorithms and check their similarities. The second step is to compare multi-processors against multi-core processors. They can be quite similar, but memory hierarchy and cache behaviours can affect algorithms performance. As third step we will compare and adapt shared memory multiprocessor programming models to distributed memory. Our aim is to increase distributed-memory usability. The fourth step is to develop a model to help to understand current architectures and close incoming architectures. The fifth step is to compare data acquisition from graph-matching algorithms to streaming applications. The sixth step is to adapt existing multi-processor programming models to streaming applications. The final step is to validate created programming model by presenting a version of the graph-matching algorithms which takes advantage of present resources on a desktop computers with a reasonable effort to a programmer or algorithm designer.

#### Introduction

### Section 1.1. Current Desktop Processors

Since the first desktop computers to first years of XXI century all market processor has followed the same tendency: each new generation has improved significantly the execution time of programs in comparison to previous generations. These improvements have been implied an exponential improvement related to time. As a consequence, algorithm design and programming has used the same tools to describe tasks for decades.

Limitations over instruction level parallelism (ILP) and energy consumption has broken this tendency [26]. Nowadays desktop computers increases the number of cores and execution units in order to maintain the exponential improvement, but, now it is required to re-engineer existing programs and algorithms to use additional execution units.

#### 1.1.1. Architectures

We focus on three main topics: multi-core, homogeneous versus heterogeneous, and memory hierarchy (distributed versus shared memory).

Market has demonstrated that multi-core are present on most of our homes and offices, we have to deal with them. Multi-core processors are quite close to multiprocessors, both have similar structure: multi-core are a kind of multiprocessor embedded into a simple chip die. Multi-core distances are shorter than multiprocessor, so communication and synchronization are faster (between cores). As a counter part, multi-core have less room for cache memory for each core and memory bandwidth, both are shared between all cores of the same die.

Homogeneous systems are simpler to deal with than heterogeneous systems. Homogeneous systems have basically the same unit processors replicated, and any of them can execute the same functions at almost the same speed. Heterogeneous are quite more complex, they have many kinds of unit processors. Each unit processor can have its specific characteristics. The main advantage of heterogeneous architectures is that they have specialized computing units, so there are some computations are many times faster. As a drawback, each unit processor from a heterogeneous architecture can execute only a set of functions. The programmer must decide how to create each set of functions and how may them interact. As the

number of cores grows, there are more chances to have specialized cores, like happens on CellBE, Fusion, Larrabee, or even on desktop computers with CPU and GPGPUs.

Memory hierarchy is usually defined by multiple levels of cache. As smaller is the memory component faster it is. Main memory usually is slow in comparison to the processor. In order to reduce latency there are caches between memory and processor. Caches near to the processor are smaller, but at the same time they are faster. Closer caches to the processors (Level 1, and Level 2) are usually embedded on the same die with the processing units. That is the big problem of caches and multi-core/multi-processor: multiple processing units are sharing the same main memory, so they should have a consistent view of its content. Unfortunately, it means that either all of them share the same caches or all caches must be aware of all memory changes. There are two schemas to face this problem of memory hierarchies: shared memory (add some kind of coherence protocol) and distributed memory (avoid the problem and be inconsistent). Shared memory assumes that all processors are sharing the same data, so changes must be coherently notified to all caches. On the other hand, distributed memory slices memory into multiple isolated regions. It avoids the problem, so there is no need to maintain coherency between all caches. Shared memory is easier to use, programmer does not need to know where is the data located, just use it. Distributed memory require a strict control about data location and synchronization, programmer must decide where to store data, and how synchronize parameters and results. In other words: someone has to solve the problem. Shared-memory implies that the architecture solves the problem, distributed-memory implies that the programmer must solve the problem of data distribution.

Original desktop computers started as single core homogeneous (there is only one processor, so there is only one kind of processor) shared memory (there is only one coherent cache hierarchy), but they are now multiple core homogeneous shared memory [19], and it seems that they are turning heterogeneous with distributed memory [31]. We also can consider that they are becoming dual processor systems, one generic CPU and one general-purpose graphics processing unit [20].

## Section 1.2. Algorithms And Parallelism

Most algorithms are designed to be executed on a single core and general-purpose processor. Consequently, they are not designed to take advantage of all available resources on current desktop computers. By not taking into account available resources, it appears a gap between effective algorithm performance and potential algorithm performance. This gap will increase at the same rate that cores count on computers increases.

There are many approaches to solve the gap between existing algorithms and existing architectures. The first and naive way is to rewrite completely existing algorithms and applications to work in those new architectures. This approach is very complex, requires a great effort, and also requires a large amount of qualified people able to transform algorithms. As we have already stated: a perfect approach would be automatic transformations, like automatic parallelisation, but there is a lack of required information at compile level. Our selected approach is using annotations.

Annotated programming model is a programming model based on an existing model, but annotations are added to increases the available compile time information. A good example of annotated programming model is OpenMP. OpenMP is designed as a set of annotations over C, C++ and Fortran applications. OpenMP targets multiprocessors and split the algorithm into multiple parallel computations. In order to enable parallel computation on OpenMP, programmers should add a few annotations on their programs. OpenMP will adapt the application to the many multiprocessors and use the underlying tools and thread libraries automatically.

## 1.2.1. Parallelization Tools

In order to parallelise an application we have to transform an application to use the underlying architecture, but we also must study the application to know which processes are critical to parallelise.

This parallelisation task requires many tools, each of them covers a partial set of requirements and some of them overlaps on their features. This tools are, from lower levels to higher levels: compiler, dynamic linker, auxiliary libraries (like libc), threads

#### 24

#### 1.2. Algorithms and Parallelism

library, synchronization libraries, communications libraries, runtimes, profilers, profiling libraries, profiler visualizers, and simulators.

Compiler is the most basic tool, it translates an algorithm to binary code. Compilers usually work with the higher level code: transforms code to low level operations. This transformation looses most of high level information. This information includes variable names, loops structures, ... The compiler is the first responsible to take advantage of underlying computer architecture. As a consequence it requires the maximum information about the algorithm and target architecture.

Execution environment is not fixed, even the same binary can run on machines with different configurations (as an example, each machine can have a different amount of physical memory). Compiler does not generate a binary for each architecture (mainly because it is not practical). Instead of this, compilers use auxiliary libraries (such libc or a run-time) to adapt the binary to a specific environment. Dynamic linkers are key on this process, they link, and completes the binary, with the most suitable library for the executing architecture.

Thread libraries and synchronization libraries are usually highly coupled and usually shipped as a single library (for instance pthreads library). There are two main classifications: user threads and kernel threads. User threads are threads controlled by user space, they are usually mapped onto a single kernel thread, and I/O operations may block all of them. Kernel threads are threads controlled by the operating system and they can be mapped over multiple physical threads or processor units. Most threads libraries mix user threads and kernel threads to achieve optimum performance.

Synchronization libraries are highly coupled to thread libraries, the main motivation is to select the most suitable wait policy and perform it. Default wait policy is usually suspending thread execution; this action requires the exact knowledge of threads implementation in order to change active thread. On the other hand, for high performance applications waiting kernel threads policy is based on active waits. They use this kind of waits in order to resume work as fast as possible. Two main synchronization primitives are mutexes and barriers. Mutex ensures mutual exclusion on critical shared structure manipulations. Some mutexes are replaced by the compiler with atomic instructions, if there are atomic instructions for

#### Introduction

the enclosed operation. Barriers are used to synchronize execution of multiple threads. Threads are collaborating on the same problem, for each step or point of synchronization a barrier primitive is used. Barrier ensures that all threads have reached a specific point.

Communications libraries are required for distributed memory systems, but they are uncommon on shared memory systems. There are four main primitives: send, receive, broadcast and reduce. Send and receive are designed to send or receive a simple piece of data, usually point to point. Broadcast sends the same data to many execution threads. Reduce primitive summarises many data into a single result, it receives a data set from many locations and performs the reduce operation (for example a summation operation). Synchronization primitives are often synchronous, that means that they require to use a synchronization library in order to wait on receive operations, if data is not yet present, or send operations, if there is not enough buffers to store the result (or if the operation is defined as completely synchronous).

Runtimes are libraries designed to support the compiler or the behaviour of a programming model. Runtime library provides a new set of primitives related to each programming model, it allows to express high level concepts. These primitives use other libraries to spawn threads, synchronize and communicate data. Compiler does not need to know how to deal with this low level libraries, it needs to know which primitives are implemented by the runtime. For example, there is an OpenMP runtime primitives defining a parallel region. Runtime decides how many threads are created to execute this parallel region. Compiler just creates a binary using this primitive. But there is a more important point, the resulting binary does not contain information limited to thread creation (as it should happen using low level libraries as pthreads), it also has information about parallel regions structures, and this information can be used to adapt the binary to each environment.

Annotated programming model and compilers are based on hints or comments over serial working code. That means that a starting point for an annotated program is a common serial well known and tested application. Annotations are just comments, they can be added one by one ensuring a correct behaviour. At the same time, they can be disabled (just removing or using common comments) to return to the serial behaviour.

#### 26

#### 1.2. Algorithms and Parallelism

Profiling tools are useful to achieve a good performance on parallel architectures. Amdahl's law [32] states that an application 95% parallelisable can be speedup x20, but no more (even if you use a thousand processing units). As a consequence, it is important to know which parts can be easily parallelised and how many threads can be used. Profiling tools are more than time watches: they report important information like data movements, false sharing, or load balancing. This information is usually collected while the application is running helped by profiling libraries. In addition, some profiling libraries also includes user events, they help to add runtime information or programmer relevant information.

Collected profiling information is usually studied by the user or programmer. Some times this information is also used by some compilers and runtimes to optimize future executions. Provided information allows to know the impact of the architecture on the program. There are some tools that just list some statistics, but there are some other tools that visualises the execution.

Simulators are one step further on profiling tools. They use profiling information and architecture information in order to extrapolate the behaviour on different architectures. Simulators also helps to predict algorithm performance on experimental architectures, when real hardware does not exist yet.

#### Section 1.3. Graph Matching Algorithms

One of the objectives of graph matching algorithms is the computer vision. In this premise real-time response is the requirement for the viability of an algorithm. There are many algorithms close to be executed on real time; in order to make them viable, these algorithms must be able to extract the maximum performance from current computer architectures.

Computer vision process is usually split in two processes: image acquisition and preprocessing and image recognition. Image acquisition transform a raw image information (a sequence of pixel colours) into a more usable information (as for example border maps, frequency maps or regions of adjacency maps). Image recognition tries to understand acquired information, in order to perform this task, it designates symbolic information to acquired information.

28

There are many processes and algorithms to do computer vision. From all of them we have selected a graph matching algorithms. These algorithms first require to transform acquired image into a graph representation. A typical transformation process is to convert input image into a segmented image by regions. Once this is converted, an adjacency regions graph is created. Result graph is matched against other representative graphs in order to detect known patterns.

### Section 1.4. Streaming And Scientific Applications

High performance computing is known by its effort to extract the maximum performance from underlying computer architecture. Moreover, high performance underlying architectures usually involve multiple processing units and complex memories hierarchies. For this reason, their target applications are a good candidate as a starting point for multi-core. These applications are usually scientific applications, and their structure seems to be very close to graph matching algorithms.

On the other hand, data acquisition systems are usually designed to work in realtime on embedded devices. These devices can have multiple processors and specialized units in order to achieve real-time and low consumption requirements. Embedded systems usually works with streaming programs, these programs are designed to process a continuous flow of data. Streaming programs are very close to acquisition image and transformation algorithms of computer vision, and even many of them are already converted to streaming programs [33].

Beyond instruction level parallelism (performed by processors themselves), there are two main kinds of parallelism on applications: task parallelism and data parallelism. Task parallelism assumes that there are multiple tasks (or functions), these functions can be executed simultaneously and independently. Data parallelism assumes that each task replicates the same computation over each element of a large set of elements, computation for each element can be performed simultaneously and independently.

There are two main operations on data parallelism: parallel map and parallel reduction. Parallel map applies the same operation over each element from a large set of elements. Parallel reduction applies an associative operation over all elements

#### 1.4. Streaming and Scientific applications

of a large set. As a result, parallel map obtains a set of elements. Each result element is computed in parallel, computation must be independent from other elements. All elements can (not as a requirement) be computed in parallel. An example of parallel map is to multiply per two all elements of a set. Parallel reduction computes as a single result element. This result is the computation of an associative operation over all elements of a set. In order to parallelise these operations, multiple associative operations can be performed over distinct sets of elements simultaneously (they must be independent). Resulting partial results are combined with the same associative operations until obtain a final result. An example of parallel reduction is summation of all elements of a set.

Streaming applications and algorithms are usually designed to exploit first task parallelism and, if there are enough free resources, then data parallelism. Streaming programs exploit task parallelism with techniques known as pipelining: data processing is split in stages, each stage computes over the result of the previous stage and produces the data required for the next stage; all stages are computed simultaneously for different time sliced sets of data.

Scientific applications and algorithms are usually designed to exploit data parallelism. These applications usually computes over a large sets of data, and usually computes iteratively over the set until reach to a solution or expected state. Each data element is computed in parallel, but the application must wait to finalise the processing of all data elements before starting a new iteration. A good example is a weather simulation: a grid represents values from the atmosphere (for example pressure, humidity or temperature). For each grid cell it computes the next time values using contiguous cell values. In order to simulate a large time weather prediction, this process is repeated many times. All cells can be processed in parallel for one algorithm iteration, but results of this process are required to start the next step.

## **Chapter 2. Objectives**

The objective is to find a set of tools and directives to help algorithm designers in computer vision and pattern matching. These tools and directives will allow to algorithm designers take advantage of current underlying computer architectures and their possibilities. We want to demonstrate that existing tools for supercomputers are helpful for multi-cores. We will focus on those tools that do not require a deep knowledge about computer architecture. We expect that this kind of tools are suitable for described task with an acceptable performance. We will evaluate these tools on many environments or architectures. Recommendations will be performed in order to improve their efficiency.

We define two main criteria to evaluate tools and directives: usability and performance. We expect from tools to be usable by people with no deep insights of underlying architectures. Adapted algorithms and applications must run with an acceptable performance. We are looking for a trade off between this two criteria: performance and usability. For example, it is worthy to lose a 20% of maximum performance if it can be achieved by a standard algorithm designer with a small effort. We do not expect to require an architecture expert plus a great effort on the algorithm or program parallelisation and distribution.

Usability criteria is related with required knowledge: the possibility to exploit a many kinds of architectures with the same source, and of course, the possibility of incremental code transformation and debugging. Usability criteria will benefit those solutions which hide architecture details and focus on algorithm semantics. We expect from an algorithm designer to know insights from its algorithm, but not to know from architecture details. That means that tools should be focused on algorithm semantics better than architecture details. Tools should allow to provide

Objectives

enough information to take advantage of current architecture. If the additional information is good enough, it should be useful for many kinds of architectures. On the other hand, we can not expect from a programmer to adapt a large application or algorithm at once to a new architecture. For this reason tools may help to change parts of the algorithm or application incrementally; at each step, the algorithm designer or programmer may be able to test if provided information is correct, and if results (algorithm and performance) are expected. If at any step the application do not works properly, we expect that the programmer will debug the application in order to solve any problem.

Performance criteria is more related with the possibility of increasing application performance on future processor architectures than to have a very good performance in a current or specific architecture. For years we have assumed that a single threaded will increase its performance over each new processor generation, now we know that it is not longer true. Current market trends seems to indicate that the number of cores and available threads will increase, in this scenario, a good performance criteria is scalability. Scalability studies how an algorithm or program is able to keep improving its performance in the same ratio that cores or hardware threads increases. A good scalability will ensure that future processors, with an increasing number of cores, will be able to speedup the application.

## Section 2.1. Graph Matching And Scientific Applications

Scientific applications have been used on supercomputers and many architectures for decades. In other words, scientific applications are a very well known problem. On the other hand, research and practical uses of graph matching algorithms on supercomputing environment are not common. In other words, graph matching algorithms are still in research and there are many potential problems to solve. By using scientific applications, instead of graph matching algorithms, on first steps of this thesis, we can reduce potential unexpected problems.

In our research we want to face only one problem at a time. When we have started this research there was little applicability of supercomputer tools in multi-cores. Doing graph matching and using supercomputer tools in multi-cores faces two

32

#### 2.1. Graph Matching and Scientific applications

problems at a time: 1) supercomputing tools on multi-core, and 2) graph matching with supercomputer tools. There are two approaches: 1) port graph matching to supercomputing using supercomputer tools, or 2) port a well tested scientific application with supercomputing tools to multi-cores. Approach one has a considerable drawback: supercomputers are really very expensive; moreover, results on supercomputers are not extensive to multi-core. Approach two, per contra, makes available a very large list of bibliography to solve the problem. We have selected approach two.

First steps of this thesis will start doing research with supercomputing scientific applications. As our objective is to port graph matching and computer vision algorithms to multi-core, we first will compare scientific and vision algorithms in order to find an equivalence.

**Hypothesis 1**: *Graph matching algorithms have common characteristics with scientific applications used at supercomputing.* There are many kinds of applications from scientific world used on supercomputing. Most of these applications shares patterns and structures, in addition they are focused to intensive computations. For example, scientific applications patterns and structures differ from classical administration applications.

**Objective 1**: *Prove that graph matching algorithms have common characteristics with scientific applications.* From all available scientific applications, we focus only on a set of applications that 1) have potentially common characteristics with target graph algorithms and 2) have been successfully adapted to many supercomputing environments using tools that satisfies our criteria of usability and performance.

### Section 2.2. Annotated Programming Model Over Multi-Core

A homogeneous multiprocessor with shared memory is the most usable supercomputer architecture. Annotated programming models for these architectures have one of the best trade off between usability and performance. We want to achieve the same trade off in multi-core architectures.

Objectives

Multi-processor are basically multiple processors of the same kind and characteristics interconnected sharing the same data. In other words: all threads have the same computations capabilities and can use the same data simultaneously. Complex memory operations like data synchronization are hidden from application programmer by hardware.

Annotated programming models uses annotations in order to extend available information at compile time. As less information is required, and less specific, more usable is the programming model. Most popular multi-processor annotated programming models are born in multi-processor homogeneous shared memory architectures. Shared memory implies no need for data partitioning or explicit communications annotations (like any standard application). Homogeneous property allows to execute the same code in any arbitrary hardware thread.

Shared memory homogeneous multi-processor annotated programming model, as OpenMP, focus on annotations to express algorithm parallelism. These annotations help the compiler to identify which parts can be executed in parallel, in other words, which parts have no dependences. It allows the compiler and the runtime to decide how many threads use and how to perform synchronizations. This decisions can be different for each architecture, ensuring a good performance under many architectures. At the same time, OpenMP can hide architecture to the programmer. These properties enable usability and performance.

We focus only in tools for multi-processor homogeneous shared memory. Multiprocessor and multi-core differs on communication and synchronization velocity, cache size, and memory bandwidth. On the other hand, multi-processor and multicore both run multiple hardware threads. A set of annotations based on expressing algorithm parallelism help the compiler to take advantage of hardware threads, no matter if threads are multiple processors or multiple cores. We expect to overcome differences like communication velocity or cache by changes on the compiler/runtime. We also expect to allow applications to exploit multi-core improved communication and synchronization latencies.

**Hypothesis 2**: Supercomputer architectures based on multiprocessors have similar characteristics to multi-core and multi-threading processors in order to execute scientific applications. Both architectures execute multiple hardware threads and have multiple functional units allowing true parallelism. But, on the other hand, there are some

# 2.2. Annotated Programming Model over Multi-Core

important differences related to communication and synchronization (multi-core are faster) or related to memory hierarchies (multiprocessor have more high speed cache capacity). Communication and synchronization speed should open new opportunities on fine grain parallelism (parallelism which more frequent synchronizations), but low capacity on cache might affect negatively to execution of large data sets. We expect that low capacity on cache might be compensated by high speed synchronizations.

**Objective 2**: *Prove that multi-core processors present similar characteristics to supercomputer architectures and they execute successfully scientific applications.* Our objective is not to create a new adaptation of scientific applications for multi-core architecture, but use the same tools for multiprocessors on multi-core processors. We have explained in main objectives that selected scientific applications use tools that provides usability and performance. We focus on programming models based on annotations, which provides desired usability. Target scientific applications must execute successfully (with good performance) on multi-core with minimum changes. Runtime and compilers might be adapted in order to help performance.

# Section 2.3. Annotated Programming Model Over Distributed Memory

As the number of processors increases and memory hierarchies becomes more complex architectures are more likely to be distributed memory ([17], [31], [34]). Annotated programming models are not designed for distributed memory, and they do not specify data movement. We want to study if it is possible to use annotated programming models under distributed memory and which changes are required.

Shared-memory is logical view of the physical memory. When there are multiple processors or cores, multiple caches, and many levels for replication, there is not a unique real data view. Each cache can contain many versions of the same data. When we talk about shared memory systems, or either we have a unique memory hierarchy, or we have a very complex piece of hardware that creates a logical shared memory.

#### Objectives

Shared memory illusion is usually kept by cache coherence protocols. These protocols coordinate all caches for all levels sharing the same memory in order to synchronize values. Special hardware, implemented at caches and communication buses, maintain the coherency between all caches. When memory hierarchies are very complex, this hardware is also very complex and coherency becomes very expensive.

Distributed memory architectures avoids shared memory complexity by not implementing it. Distributed memory architectures are organized in clusters: groups of computing resources (like processors, nodes) sharing the same memory. Distributed memory architectures have a specialized communication network in order to transfer data between all nodes of the same system. This network allows to send and to receive data explicitly from hardware threads of the network. Each node logical memory is like an independent computer which it is connected through a network. Nodes uses the network to send and receive data to complete its computation in collaboration with all other nodes.

Distributed memory architectures expect from the application programmer and from the algorithm designer to deal with multiple memories. All complexity and responsibilities taken from hardware architecture are given to the programmer. For this reason programming for such architectures is harder than programming for shared memory architectures. Programmer must distribute the data and the program itself into multiple nodes, in addition it must design its communication and synchronization.

Distribution work made by the programmer is usually better than any distribution performed automatically. Programmer knows perfectly application behaviour, programmer can foresee program necessities and rearrange application behaviour in order to reduce required communication. On distributed memory architectures, latencies are usually high and all synchronizations and communications must be minimised. This minimisation impact is so important that is the key to the design of distributed algorithms and distributed applications. Communications and synchronizations becomes critical. The viability of an application usually depends on the capacity to minimise such communications on a large number of nodes. Usually best policy is trying to keep together data and computations, in other words, best policy is having a high locality.

#### 2.3. Annotated Programming Model over Distributed Memory

Annotated programming models were designed to simplify multi-processor programming. Shared-memory architectures are simple to use, and in order to avoid complexity, most annotated programming models focus on shared-memory. These programming models relay on shared-memory in order to avoid explicit data communication annotations and data distribution.

Some annotated programming models have experimental run-times that allows to simulated a shared memory on distributed memory architectures, they are called software-distributed-shared-memory systems (SDSM). These run-times uses software techniques to emulate shared memory. For example, not locally present memory pages can be invalidated on the current node and page fault can be used as a substitute for a cache miss. SDSM run-times allow that applications created for run shared memory architectures to work on distributed memory systems. Unfortunately, most of these applications are not able to have a good performance and scalability on SDSMs. Some benchmarks even presents a slowdown: performance is worst two nodes (more execution resources) than one single node. This behaviour is not surprising: shared memory applications are not designed to work on distributed shared memory and they are prone to compute with pieces of data spread through all cluster, in other words, they have a low locality. Locality was important but not critical on shared-memory architectures.

Distributed shared memory systems faces two problems: 1) some decisions about the design of applications are not aware of distributed nature of architecture and 2) there is a large latency to receive required data not present locally. Solving problem 1 requires the expertise from the algorithm designer or from the application programmer, so some applications must be rewritten in order to increase its locality. Nature of problem two is a little more tricky. All shared-memory hardware threads stalls (halts) when data is not ready (for example, if data is not present on the cache, thread must wait until data is received). When data is not locally present, it is likely that it is being used by another node, the latter node must send the data to the former in order to be used.

Prefetch technique allows to send or receive a data from another cluster before the execution requires the data. Prefetch technique is able to avoid thread stalls for data by advancing data communication. Data communication can be performed in parallel with computations to hide its transference cost. A good prefetch

# Objectives

performance is able to hide all communication costs and show a performance comparable to shared architectures. A poor prefetch performance can send wrong pages and invalidate them on source node. As a result, source node will have to ask again for data that originally was present. Distributed shared memory run-times uses prefetch, but annotations does not have information related about data movements, so they have to perform predictions.

**Hypothesis 3**: Annotation based programming models are also valid on environments of *distributed memory*. Algorithms and applications designed to have a high locality, in addition to good prefetch predictors (or some annotations) can have a good usability and performance on distributed memory architectures.

**Objective 3**: *Prove that annotation based programming models can effectively (usability + performance) run on distributed memory architectures.* Addition information required by the programming model should be minimal and do not require a great effort on application restructuration. We deal with a trade off between application transformation and performance. We expect a little effort from the algorithm designer or programmer in order to increase locality and performance, but not the same complexity required by explicitly programming for distributed memory.

# Section 2.4. Heterogeneous Processor Simulator

Not every architecture is designed to have a good usability. There are many architectures designed to be used by expert programmers on such architectures, usually limited for target tasks. Small changes on those architectures can jeopardize the maximum performance, but can enable better results from non expert programmers. One of the biggest problems is distributed memory, but distributed memory having a global linear address space can improve its usability. In other words, a mechanism to use memory remotely, even at expenses of paying a large latency.

As more complex is an architecture, more knowledge it is required from the algorithm designed and application programmer of underlying architecture. General-purpose old fashioned processors allows to achieve a good performance

#### 2.4. Heterogeneous processor simulator

without any special knowledge. Some specific architectures have special features that allows performances many times better than any general-purpose processor. Unfortunately to achieve such performance it is required to use such special features. Using these features requires a high knowledge of architecture. On most of the specific architectures, if especial features are not used, their performance can be lower than generic architectures.

As the number of cores grows, there are more chances of having specialized cores. Having 16 cores identical for general-purpose is not a good idea: there are many tasks running on general-purpose computers that can take advantage of special cores (graphics processing, video streaming, ...). But there are not too much tasks able to take advantage of multiple identical general-purpose threads. It even is likely to have dedicated cores for each kind of task, in order to achieve a high performance.

There are two main problems of heterogeneous architectures: each core is specialized in computing a kind of code, and they usually have distributed memory. It has two consequences: the programmer must deal with code distribution (which function or task is executed by which core) and data distribution (where data will be located and how will be transferred).

Having specialized cores implies that the programmer or algorithm designer must decide how to use each core. In other words, the programmer must create applications for multiple processor kinds on the same code. It is not usable, kinds of cores can change between processor generations as available and require a very complex task for a programmer. This problem is already present on general-purpose processors, like Intel ones: specialized vectorial instructions have evolved, specialized programs must be rewritten in order to take advantage of each generation (MMX, 3DNow!, SSE, SSE2, SSE3, SSSE3, AVX, CVT16, FMA3, FMA4, XOP). Some compilers enable automatic vectorisation (they choose for a target architecture which instructions to use), but their usually require to use annotations like #pragma ivdep (equivalent to #pragma omp parallel for) in order to enable some optimizations (in this case, the programmer reports that there are no dependences between loop iterations, even if compiler can not ensure). Nowadays, maximum support in this line is to allow the addition of some annotations in order to enable optimizations (ignored if the underlying architecture does not support some features) or describe requirements in some parts of the code (used to decide target processor).

Distributed memory is a difficult problem. In Objective 3 we try to show that there is possible to use distributed memory as shared memory, so programming task can be lighter, but we also add one requirement: some mechanism to allow specify address to be read. Usually all pointers on distributed memory architectures focus only on certain nodes: all pointers are relative to one node and there is no information related to which machine has the information. That limitation requires from the user to know where a pointer points, to which node memory. This information usually is nowhere else than the programmers mind, and prone to errors.

There is a concept, global linearly addressable memory, that allows to have global pointers, even in distributed memory. It can be seen as an architecture with distributed memory which pointers mix local address to current relative node plus a cluster id. On this kind of architecture, addresses from other clusters can be read (with a simple load or store instruction) but they may be slow and require special instructions in order to keep local pointers fast.

Global linearly addressable memory allows to increase usability: a programmer can iteratively optimise an application. First the programmer creates an application assuming shared-memory (even if it is very slow), and then, iteratively step by step, the programmer transforms global accesses by local accesses. With this model, distribution on firsts steps may have poor performance, but the programmer can start to distribute data (or add annotations for such finality) without writing all process from scratch (or even paying small penalties for few distributed accesses).

There are already some architectures that are distributed and they are a good challenge for theirs programmers. We state that to modify such architectures in order to have global linearly addressable memory may be worth. This change is not free, it requires to pay some kind of penalty. We propose to use a simulator in order to modify the hardware and to evaluate the performance for non expert programmers.

A simulator for a heterogeneous multi-core is relative new. Most simulators provides capability to simulate one processor, with one kind of ISA, with one memory hierarchy. Distributed heterogeneous multi-core are a bigger issue. We require a modular simulator able to create almost an arbitrary hierarchy with

#### 2.4. Heterogeneous processor simulator

multiple local addressable memoires and cache hierarchies. In order to show the usability of global linearly addressable memory architectures, first, we need to simulate a distributed memory processor, validate it, and perform modifications. Results must be evaluated in order to know how changes impacts on usability and on performance.

**Hypothesis 4**: *Small changes on architecture can help to improve usability.* There is a trade of between usability and architecture performance. Some architectures have very good performance results with almost any code (like generic architectures), but some other architectures need deep knowledge of the architecture in order to achieve the maximum performance. It is possible to modify architecture in order to increase usability, but on the other hand, the architecture can decrease its maximum performance. We state that some changes on architecture can create a good balance between two possibilities: to make available good performance ratios with low knowledge of underlying architecture.

**Objective 4**: *Present changes in the architecture that increases usability on complex architectures, even if we loose partial hypothetical maximum performance.* In order to satisfy this objective we use a simulator and other architectures in order to prove candidate changes. Changes must show how concepts like global linearly addressable memory on distributed memory can help to increase usability with an acceptable cost.

# Section 2.5. Graph Matching Preprocessing And Streaming Applications

Streaming applications have perfect properties for heterogeneous distributed memory architectures: they have multiple independent kernels (functions) with explicit data flows. Graph matching preprocessing algorithms are in fact image acquisition programs. This kind of programs usually present streaming characteristics. Streaming applications have been used on multiple research and are deployed on multiple commercial system. If we stablish that they have common characteristics with graph matching preprocessing algorithms, we can use a well known algorithms in order to perform firsts steps with streaming architectures.

Objectives

As we stated above on section 2.1 we want to face a only problem at a time. There is a large research on some streaming applications on many kinds of architectures. There are also a large number of streaming programs deployed on commercial systems. On the other hand, there is not an annotated programming model to create streaming applications. So we stablish once again three-step research: select streaming applications comparable to graph matching preprocessing, use streaming applications to define a programming model for streaming applications, apply resulting knowledge to graph matching preprocessing.

Streaming applications are based on independent kernels with explicit communication data flows. A kernel is like a function, executed in its own thread, within a loop whose iterations are computed each time that a data set is received. Kernel memory is private, this memory is not accessed by other kernels. All communications between kernels are performed using synchronous data channels, or specialized asynchronous directives. Kernels computations are performed over incoming data from synchronous data channels. Their results are sent to other kernels through outgoing synchronous data channels.

Synchronous data channels communicates kernels, they represent a data flow. There are three main operations over synchronous data channels: push, peek, and pop. Data channels are flows of one single type of data. Push operation is applied to outgoing synchronous data channels, it adds one data element to the channel. Push operation is synchronous, it can stop its kernel execution if there are not enough available space to receive data. Pop operation reads and discards one element from a synchronous data channel. Pop reads elements in the same order that push adds elements. If a synchronous data channel is empty, pop blocks its kernel execution. Peek operation reads one arbitrary non discarded element from a synchronous data channel. If required element is not yet pushed, peek blocks its kernel execution. Peek operation is performed carefully because it decides the minimum number of elements of synchronous data channels buffers. Peek operation can induce dead-locks when there are loops or cycles in the data flow.

Some architectures do not allow kernels to block. For this reason, the number of consumed elements and produced elements for each kernel must be known by runtime.

#### 2.5. Graph Matching preprocessing and Streaming applications

Any streaming application is in fact a graph: each node is a kernel, and each edge is a synchronous communication data channel. This structure is very malleable: nodes and edges can be grouped in order to share affine resources. If a compiler knows the streaming application structure and properties, it can decide how map each node and edge to available architecture resources. If a graph matching preprocessing algorithm can be expressed as a streaming graph, it can be implemented as any streaming program and take advantage from streaming optimisations.