# Per-Task Energy Metering and Accounting in the Multicore Era

Qixiao Liu

#### Advisor

Miquel Moretó Planas

Co-Advisors

Jaume Abella Ferrer

Francisco J. Cazorla Almeida

Mateo Valero Cortés

Memòria del Projecte de Tesi Programa de Doctorat d'Arquitectura i Tecnologia de Computadors Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

March 2016

## **Abstract**

Chip multi-core processors (CMPs) are the preferred processing platform across different domains such as data centers, real-time systems and mobile devices. In all those domains, energy is arguably the most expensive resource in a computing system, in particular with fastest growth. Therefore, measuring the energy usage draws vast attention. Current studies mostly focus on obtaining finer-granularity energy measurement, such as measuring power in smaller time intervals, distributing energy to hardware components or software components. Such studies focus on scenarios where system energy is measured, and under the assumption that only one program is running in the system. So far, there is no hardware-level mechanism proposed to distribute the system energy to multiple running programs in a resource sharing multi-core system in an exact way.

In this thesis, for the first time, we formalize the need for per-task energy measurement in multicore by establishing a two-fold concept: per-task energy metering and sensible energy accounting. The former, for a task running in a multi-core system, provides estimates on the actual energy consumption corresponding to its resource usage. The latter provides estimates on the energy the task would have consumed running in isolation with a given fraction of the shared resources.

Accurately determining the energy consumed by each task in a system will become of prominent importance in future multi-core based systems as it offers several benefits including (i) better application energy/performance optimizations, (ii) improved energy-aware task scheduling and (iii) energy-aware billing in data centers.

We have shown how these two concepts can be applied to the main components of a computing system: the processor and the memory system. In each, we have proposed models to ideally meter and account the energy. And by trading off the hardware cost with the estimation accuracy, we have obtained implementable and affordable mechanisms with high accuracy. We have also shown how these techniques can be applied in different scenarios, such as, to detect significant energy usage variations for any particular task and to develop more energy efficient scheduling policy for the multi-core system.

# **Acknowledgment**

First and foremost, I want to thank my advisers, Dr. Miquel Moretó, Dr. Jaume Abella, Dr. Francisco J. Cazorla and Professor Mateo Valero. They have taught me how high-quality research in the computer architecture field is done. It has been a great honor to be supervised by them and I sincerely appreciate their contributions of time, ideas and guidance to make my Ph.D experience stimulating and enjoyable. Their joys and enthusiasms for the research are contagious and motivational for me, especially during the tough times of the study. They have also provided me with excellent examples as successful researchers and mentors.

The members of the Computer Architecture and Operating System interface (CAOS) group have contributed immensely to my research and life here at Barcelona. The group has been a source of friendships as well as good advices. I'm especially grateful for Dr. Carlos Luque, whose work is one of the cornerstone of my thesis: the performance accounting. He vigorously shared his visions and experiences with me, and helped me to get over difficulties. I would like to thank Dr. Petar Radojkovic, from whom I have learned the successful and encouraging researching experiences.

I want to thank Pradip Bose, Alper Buyuktosunoglu, Ramon Bertran and Victor Jimenez from IBM T.J Watson in New York, where I have spent five months for an internship, for their immense help in the research and life. It has been incentive to work with them with joy. They have taught me numerous knowledges and experiences on research with excellent mentoring skills. I am also grateful for Professor Daniel A. Jimenez from Texas A&M university. He has played an important role in the work we have collaborated together, I'm greatly influenced by his meticulous attitude and profound knowledge. In regards to the work here in Barcelona Supercomputing Center, I thank Francesc Subirada. With Mateo, they have spent numerous efforts in building this world class supercomputer and a fabulous workplace for researchers. It has been an great honor to stand by them exhibiting the MareNostrum, the stunning artifact to the visitors from my home country, China.

ACKNOWLEDGMENT

ii

In particular, this work has been partially supported by the Spanish Ministry of Science and Innovation under grant TIN2012-34557; the HiPEAC Network of Excellence, by the European Research Council under the European Union's 7th FP, ERC Grant Agreement n. 321253; and by a joint study agreement between IBM and BSC-CNS (number W1361154). I have also been funded by the Chinese Scholarship Council under grant 2010608015.

At last, I would like to thank my parents for all their love, encouragements and supports. With all of that, I can pursue this Ph.D.

Qixiao Liu March, 2016

# **Contents**

| A            | bstra | act                                                 | i  |

|--------------|-------|-----------------------------------------------------|----|

| A            | ckno  | wledgment                                           | i  |

| $\mathbf{C}$ | ontei | nts                                                 | i  |

| 1            | Inti  | roduction                                           | 1  |

|              | 1.1   | Thesis Contribution                                 | 6  |

|              | 1.2   | Thesis Structure                                    | 9  |

| <b>2</b>     | Rel   | ated Work                                           | 11 |

|              | 2.1   | Energy Consumption in Computing Systems, A Taxonomy | 12 |

|              | 2.2   | Computing System Power Measurement                  | 14 |

|              | 2.3   | Energy and Power Profiling                          | 16 |

|              | 2.4   | Summary                                             | 20 |

| 3            | Exp   | perimental Framework                                | 21 |

|              | 3.1   | Simulation Framework                                | 21 |

|              | 3.2   | Performance Simulators                              | 23 |

|              | 3.3   | Power Simulators                                    | 26 |

|              | 3.4   | Benchmarks                                          | 28 |

|              | 3.5   | Metrics                                             | 34 |

| 4            | Per   | -task Energy Metering for The Processor             | 37 |

|              | 4.1   | Introduction                                        | 37 |

|              | 4.2   | Ideal PTEM for the Multicore: LLC and Core          | 39 |

|              | 4.3   | An Implementable PTEM Approach                      | 43 |

|              | 4.4   | Evaluation                                          | 48 |

CONTENTS

| $\mathbf{B}$ | iblios     | graphy                                             | 149         |

|--------------|------------|----------------------------------------------------|-------------|

| 9            | Pul        | olications                                         | 147         |

|              | 8.2        | Future Works and Impact                            | . 144       |

|              | 8.1        | Thesis Conclusion                                  | . 141       |

| 8            | Cor        | nclusion and Future Directions                     | 141         |

|              | 7.6        | Summary                                            | . 139       |

|              | 7.5        |                                                    |             |

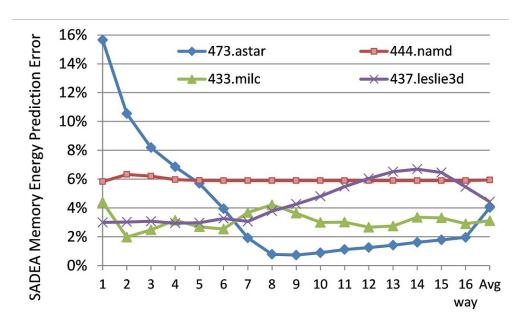

|              | 7.4        | SADEA, an Implementable Approach of SEA            |             |

|              | 7.3        | Ideal SEA for DRAM Memory System                   |             |

|              | 7.2        | Background                                         |             |

|              | 7.1        | Introduction                                       |             |

| 7            |            | sible Energy Accounting for the DRAM Memory System | <b>12</b> 1 |

|              | 0.1        |                                                    | . 120       |

|              | 6.7        | Summary                                            |             |

|              | 6.6        | Case Study                                         |             |

|              | 6.5        | Evaluation                                         |             |

|              | 6.3<br>6.4 | Theoretical SEA                                    |             |

|              | 6.2        | Background                                         |             |

|              | 6.1        | Introduction                                       |             |

| 6            |            | sible Energy Accounting for the Processor          | 93          |

| _            | <b>a</b>   |                                                    |             |

|              | 5.7        | Summary                                            | . 92        |

|              | 5.6        | Case Study                                         |             |

|              | 5.5        | Evaluation                                         |             |

|              | 5.4        | DReAM, an Implementable Approach                   |             |

|              | 5.3        | Idealized PTEM for DRAM Memory                     |             |

|              | 5.2        | DRAM Memory System Fundamentals                    |             |

| 0            | 5.1        | Introduction                                       |             |

| 5            | Per        | -task Energy Metering for the DRAM Memory System   | 65          |

|              | 4.6        | Summary                                            | . 62        |

|              | 4.5        | Case Study                                         | . 57        |

## Introduction

Energy is becoming one of the most, if not the most, expensive resource in computing systems. This trend will continue as the price of energy continues to rise, increasing in recent years by up to 70% in several European countries [28].

- In a large-scale computing facility (LSCF), energy for computing already accounts for 20% of the total cost of ownership [8,39]. In addition, the Power Usage Effectiveness (PUE) is still above 2.0 in most LSCFs in the year 2015 [24,38]. This metric compares the energy used on the computing facilities with the total energy consumed including other facilities such as power delivery and cooling system:  $PUE = \frac{total\ energy}{computing\ energy}$ . Thus, the energy cost doubles if we consider all the facilities in LSCFs, implying that the total energy-related cost is already in the same order of magnitude as the hardware-related cost (servers), which dominates the cost of ownership. Additionally, while server cost has remained almost constant over successive generations, energy cost is expected to rise [8]. In fact, in terms of power, current facilities consume several megawatts, enough to power small towns [6]. Meanwhile, in terms of energy, worldwide energy consumption attributable to servers and data centers is estimated to be above 200 billion kWh annually in 2010 [63].

- Energy demand is also an issue for home computers. A typical desktop computer may use in the order of 100–200 Watts (the particular figure depends on the type of computer and peripherals) whereas laptops fit in a lower range (60–100 Watts). The energy cost of running a computer can be computed as  $\frac{Watts \times Hours\ Of\ Use}{1000} \times Cost\ per\ kWh$ . Assuming that a computer runs for 15,000 hours during its lifetime

(around 28 months nonstop) with a cost of 22.1 cents per kWh (household), the energy cost of a 150W desktop is \$497. This figure already represents a significant fraction of the purchase cost of a computer.

• Energy is also critical for the mobile embedded systems, as the computing power of hardware keeps growing whereas the energy densities of the battery technology comparatively slowly grows. Estimating the battery duration of the device with a set of applications running, based on the energy delivered by the battery for a given size and weight is essential for device design.

The so called *power wall* and Instruction Level Parallelism (ILP) wall have been shown to be the major obstacles to maintain the historical rate of performance growth in computing systems [15, 41, 79, 85, 112]. In this line, multi-core and many-core design paradigms have enabled the growth of throughput performance despite the dramatic slowdown in clock speed growth. Multi-core designs offer improved performance per Watt – for similar single-core solutions – for workloads that can make use of multiple cores. However, its establishment as the *de facto* hardware paradigm across most computing domains, together with increasing core counts in each new generation, makes energy consumption in such complex system difficult to be measured at a fine granularity (e.g., per task). Thus, in the current energy-sensitive environment, accurate attribution of energy contribution needs more sensible understanding and study.

Take the scenario of LSCFs where energy already dominates the operational cost for example: In the age of non-virtualized systems, service providers normally charge users based on the time they have used the facility. In this case, as stated in [53], once a user instance received some physical resources, no other user would be able to share those resources. In such a situation, time is indeed money; so, even if the user instance isn't using the allocated resources, it would make sense to charge the user a flat, per-hour rental rate, because once a set of resources is tied up, the owner can't make rental income out of those resources from any other waiting customer.

Today's LSCFs providers, cloud-computing for example, serve the customers with services based on different models, such as the Infrastructure as a Service (IaaS), Platform as a Service (PaaS) and Software as a Service (SaaS). While in the basic IaaS model, the physical machines are still offered along with virtual machines (more often). The trend is to provide customers highly virtualized online service instead of direct hardware resources, such as PaaS and SaaS. Current cloud-computing providers such as ElasticHost [26] and CloudSigma [21] provide computing power in the form of IaaS. They use similar pricing models, which has been concluded in [74] as follows:

$$P_{vm} = P_{base} + P_{CPU} \left( \frac{f_{CPU} - f_{CPU_{base}}}{f_{CPU_{base}}} \right) + P_{RAM} \frac{RAM_{size}}{RAM_{size_{base}}}$$

(1.1)

In this model, customers are offered with the flexibility to choose a specific CPU frequency  $f_{CPU}$  which stands for the demanding computing power of the processor, and the memory size  $RAM_{size}$ . they are For other resources, they can be priced using the same methodology, but they are ignored in this formula to simplify the discussion. Based on the customer's selection, the corresponding price is calculated with fixed rates  $P_{base}$ ,  $P_{CPU}$  and  $P_{RAM}$ .  $P_{base}$  is the basic price when the minimum CPU capacity  $f_{base}$  and  $RAM_{size_{base}}$  are used. With the extra demand on computing capacity and memory size, the price  $P_{vm}$  that customer has to pay also rises.

Note that in this case, the boundary between the physical machine and the virtual machine is already unclear. For example, given that customer needs 10GHz CPU frequency, and the per-processor computing power in the infrastructure is 3GHz. We can either presume that the demanded 10GHz CPU frequency can be divided into 3 physical processors entirely, and the rest 1GHz falls into a virtual machine to be placed in any shared processor. Besides, the whole demanded CPU frequency is placed into several virtual machines that the operator can smartly schedule in the infrastructure to maximize the actual resource usage and optimize the overall power and energy consumption. In most cases, the latter one is clearly the preferable choice. Providers benefit from the virtualization of the hardware resources, since they can charge multiple users sharing the hardware resources. As claimed in [53], in this new scenario, the owner has no reason not to move to an energy-aware accounting system based on actual resource usage; [...] A built-in energy-accounting system could guide the workload management system to make scheduling decisions that result in safe, more efficient workload consolidation.

From the customer side, energy accounting is also beneficial. For example, if such a system is presented, it can help them to demand proper services to satisfy their need and budget. Most importantly, they will receive billing with higher fairness and accuracy for running their applications. Nevertheless, the benefit of being energy-aware is not limited to this LSCF case, and application can be easily found across all computing domains.

As energy already draws attention from the community, there have been abundant energy-oriented studies. In these works, researchers focus on refining the energy measurement in different perspectives, such as hardware and software based energy measurement in each small time interval, energy and power profiling for programs and systems, energy consumption breakdown in hardware components and program blocks, etc. [14, 27, 105].

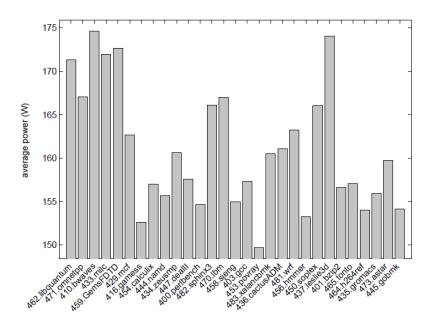

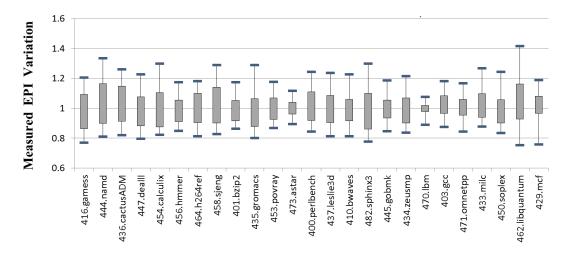

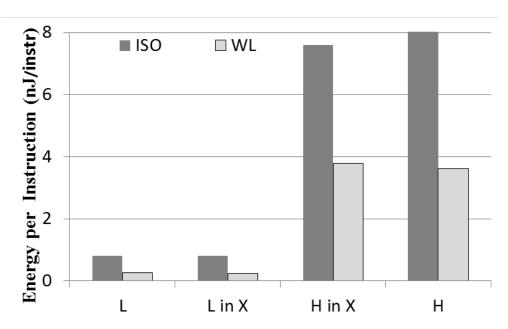

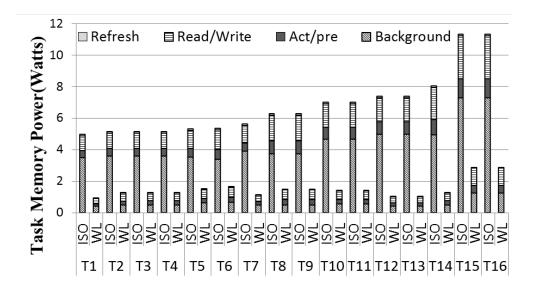

Figure 1.1: Power consumption of SPECCPU 2006 benchmarks on a PS701 system with an IBM POWER7 processor

However, despite the fact that multicore processors have been pervasively used in almost all computing domains in which multiple tasks<sup>1</sup> can simultaneously run, to the best of our knowledge, no mechanism has been proposed to accurately measure the energy consumed by each task in multicore architectures.

Current approaches to measure tasks' energy consumption assume computer system's energy is evenly distributed across all running tasks, as if all of them were using resources homogeneously. However, different applications may easily incur vastly different resource utilization in the shared resources. Such heterogeneous resource utilization translates into heterogeneous power dissipation per application, and therefore, simply dividing energy evenly across running tasks is neither fair nor accurate enough.

To elaborate on the need of accurate per-task energy measurement, Figure 1.1 shows the average power dissipation when executing all the SPEC CPU2006 benchmarks on a POWER7-based system [58]. As shown, different tasks incur different average power dissipation, with the maximum variation being 16%, between 453.povray and 410.bwaves. Hence, if a povray-like and a bwaves-like program execute undisturbed in a computing system for a period of time, they will incur significantly different energy consumptions. However, the same amount of energy would be attributed to each, which sum up to the total energy consumption of the system. Note that workloads in this example are fairly

<sup>&</sup>lt;sup>1</sup>In this thesis, we use the term task to refer to hardware threads belonging to a single-threaded application. And the term workload refers to a set of co-running tasks.

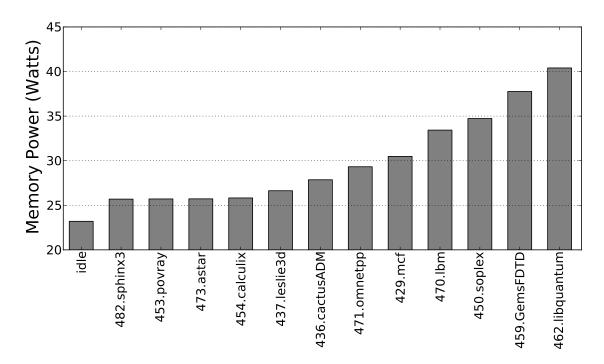

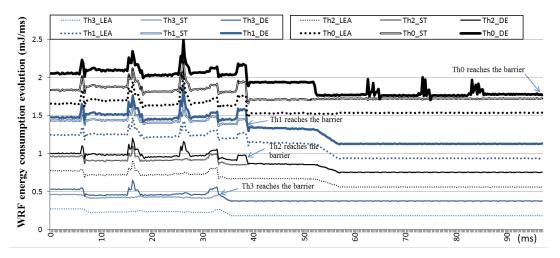

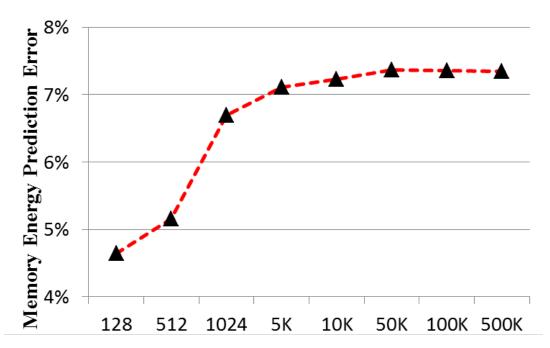

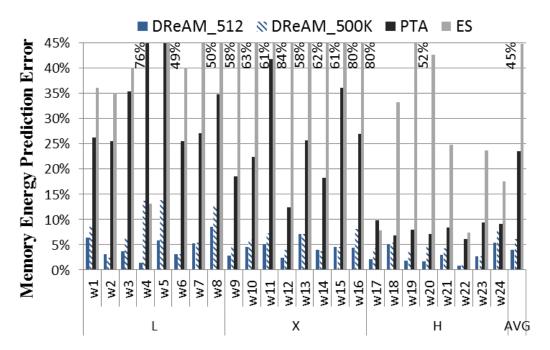

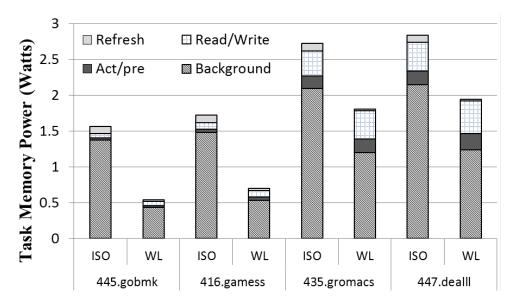

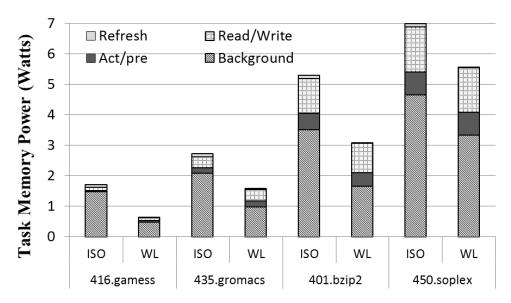

Figure 1.2: Memory power of some SPEC CPU 2006 benchmarks running alone on an Intel Sandy Bridge server, with 8 cores and a 64GB DDR3-1600 memory running at 0.8GHz. Power is obtained using the Running Average Power Limit (RAPL) interfaces [50]. FitPC external multimeter is used to measure wall power. We correlate wall power data with the data collected from the hardware energy counters using time stamps. Representative benchmarks were selected based on previous characterization studies [51,94].

homogeneous given that they correspond to a single benchmark suite in this case. More heterogeneous workloads including database processing, I/O-intensive applications as well as high-performance ones will exhibit even higher power variations.

Similar trends can be observed on different platforms. We have also performed an experiment with several representative SPEC CPU 2006 benchmarks running on an Intel Sandy Bridge server. In this experiment, we focus on the average memory power during their execution, which represents between 24.6% and 33.9% of the total systemrpower. It is comparable to the entire processor power: on average, the memory system only consumes 6.3% less power than the processor.

Figure 1.2 shows the average memory power consumption of each benchmark when executing in isolation on the system. Different tasks incur different power consumption, with the maximum variation being 54%, between 482.sphinx3 and 462.libquantum (from 25.7W to 40.4W). Hence, libquantum-like and sphinx3-like workloads executing for the same amount of time would incur significantly different energy consumption.

It is our position that accurately measuring the energy consumed by each task in a computer, instead of considering only the whole energy consumed by the computer, will have plenty of important applications. These applications will not only improve the energy usage attribution in the multicore system, but also enable optimizations on the design and management of computing systems. As a matter of example we list the following applications:

- In LSCF, the energy cost is already dominating the billing. For example, consider the cloud computing provider Cloudsigma [21]: the unit price is 2 cent per hour for a CPU running at 2.5GHz. Assuming an average 50W power consumption and 12.8 cent per kWH electricity price (industry), the energy cost is 30% of the bill without accounting the energy spent in other facilities (12.8·50/1000 = 0.6 cent per hour). With such figure, users' billing without considering energy cost cannot be fair. Especially in multicore systems, according to our study in Chapter 4, the energy that a task consumes when it co-runs with different tasks can vary in the range of [-25%, 40%]. Despite this variability, it is our position that when a customer requests the same computing power to run the same task using the same input, the same energy cost should be accounted. Based on that, the provider should consistently charge the customers with the same billing.

- During the design of multi-core and many-core architectures, the per-task performance and system throughput have been mainly taken into account. However, the impact on per-task energy has been somewhat ignore. If the energy consumption of per-task can be measured, the energy efficiency of using multicore processor can be quantified, and more energy efficient design can be devised.

- For computing systems in different domains that use multi-core and many-core processors, collocating tasks with different power needs in the nodes must be done in a way to maximize their performance while minimizing energy consumption. In a given node, allocating appropriate resources to tasks and regulating the frequency/voltage level to reach the optimal tradeoff between their performance and energy consumption has also prominent importance.

#### 1.1 Thesis Contribution

In pursuance of building energy-aware multi-/many-core systems, numerous efforts are needed in different perspectives. In this thesis, we focus on the per-task energy measure-

ment, as needed by fair energy accounting and system optimization.

In particular, we divide this topic into two distinct concepts: for a particular task, 1) measuring its actual energy consumption in a given workload; and 2) estimating its energy consumption with a given allocation of resources.

Since modern computer components are implemented with diverse techniques and designs, and thus have different structures and organizations, we propose techniques for the on-chip resources and off-chip memory subsystem separately in this thesis.

### 1.1.1 Per-Task Energy Metering (PTEM)

First, we propose *Per-Task Energy Metering (PTEM)*, which is a measurement of the actual energy consumption one task has during its execution in a multi-core architecture where the resources are shared with other tasks. We define this concept formally as follows:

Given a workload composed by n tasks  $T_i, T_2, ..., T_n$  running in a processor with m hardware threads (e.g., m single-threaded cores), Per-Task Energy Metering consists in tracking the energy that a given task,  $T_i$ , consumes during a given period of time. This requires metering the energy a task  $T_i$  consumes in private hardware components (i.e. components only used by the task at a given point in time) for instance, the single-threaded cores in a multi-core CPU, and shared resources, such as Simultaneous Multi-Threaded (SMT) core and shared L2 or Last Level Cache (LLC).

The difficulty with shared resources resides on the fact that they can serve requests from different tasks concurrently, and each request type may generate different internal activity in the resource with variable duration. This seriously challenges per-task energy metering. Current methods for energy metering focus mostly on time-shared resources (e.g. CPUs) and are based on usage time and allocated resources. This may be adequate if static power dominate the total power consumption. However, this is no longer true with the shift towards energy-proportional systems [5] where most of the energy consumed by an application – and hence, its cost – is due to its activity. Hence, in an energy proportional system two customers that incur different utilizations across similarly allocated resources for similar usage time, will be accounted the same energy consumption while in reality their energy consumption profiles can be quite different. In [53] authors run several homogeneous programs in isolation on the same platform for a fixed period of time. Results show that power dissipation across these homogeneous programs with similar resource and time allocation may vary more than 20%. More heterogeneous workloads including database processing, I/O-intensive applications as well as high-performance ones exhibit higher power variations.

Our view is that, the energy metered to a given task should be proportional to its resource usage. This includes the number and type of accesses to the different resources and, for stateful resources (e.g., Branch Target Buffer, caches and Translation Look aside Buffer (TLB)) the fraction of the space occupied by the task. The accuracy of per-task energy metering depends on the characteristics of the hardware resources used and the hardware support enabled for energy metering. Note that when we have per thread energy metering, energy for multi-threaded applications simply consists in adding up the energy consumed by each of its constituent threads.

## 1.1.2 Sensible Energy Accounting (SEA)

PTEM provides a way to measure the *real* energy a task consumes in the computer. However, the energy metered to a task in a given system, despite it has the same input set, varies depending on other tasks that are running at the same time (co-runners). Apart from being able to measure the energy consumed by a task, we also aim at maintaining the same *Principle of Accounting* that holds for execution time (a.k.a. CPU accounting) [76]: the energy accounted to a task should be independent from the workload in which this task runs. Several runs of the same task with the same input should – theoretically – result in the same energy consumption and hence the same charge in a data center.

Therefore, we propose Sensible Energy Accounting (SEA) to fairly account a task a constant amount of energy as if it has been assigned a fraction of resources to use in the computer, regardless of the concurrently running tasks. We define SEA formally as follows:

Let us assume a workload composed of n tasks  $T_1, T_2, \ldots, T_n$  running on a processor with m hardware threads (e.g., m single-threaded cores), SEA consists of estimating, for a given task  $T_i$ , the energy that it would have consumed if it had run in isolation with a given fraction of the hardware resources denoted fhr. Thus, SEA does not give the actual energy consumption of a task, but rather an abstraction of the energy consumption that the end-user can rely on to be fair and consistent.

The main challenge for SEA is how to compute the energy for any task and any valid fraction of the resources, despite the fact that a particular task may incur different activities in different workloads due to interactions with co-runners, and such variation makes its performance fluctuate. This effect makes energy consumption hard to account since it cannot be extracted directly from the energy measured. Our view is that, accurately accounting the energy to a task for a particular fraction of resources depends on precise estimation of activities and execution time this task should have incurred.

#### 1.1.3 Future Impact of PTEM and SEA

We consider both concepts are key to provide clarifications on the per-task energy usage, from the perspective of actual workloads and feasible allocations of resources. We consider that PTEM and SEA can be separately used or combined, but in any case they will have several important applications across different computing domains. We show some cases where PTEM and SEA can apply to:

- Selection of appropriate co-runners. Task interaction in hardware shared resources may negatively affect tasks hurting performance and increasing energy requirements. PTEM and SEA can help the OS scheduler or a runtime-based scheduler to decide which tasks must be run and when, thus reducing the total energy profile.

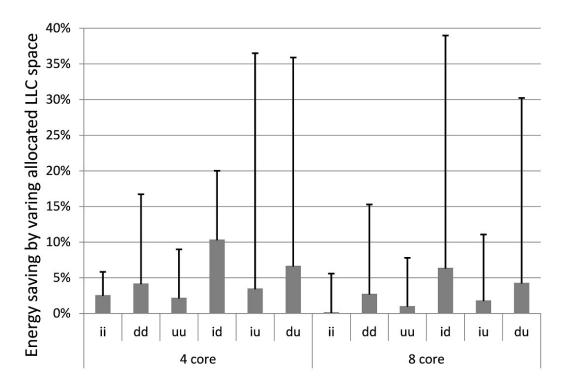

- Energy/Performance optimization. While allocating more resources to a program may make it runs faster, it could also increase its power consumption, and vice versa. Thus, the net effect on how the total energy profile relates to the resource allocation is unclear. Accurately measuring the energy consumed in different processor (e.g. number of cores) and software (e.g. scheduling) setups will justify their effectiveness in energy-saving. Sensibly accounting the energy consumed per task would allow finding the optimal setup that leads to the lowest per task energy consumption, and thus the lowest system energy consumption (shown in Section 6.6.2).

- Billing in data centers. Data centers charge users for the use of their resources. The fact that costs will be dominated by energy, makes billing systems more and more energy-centric, so that part of the bill is directly dependent on the energy consumed by users' running jobs. Measuring the energy each task consumes, rather than evenly dividing the cost of energy among running tasks, would allow data centers to accurately account the energy cost. Sensibly accounting the energy each task consumes under a given fraction of resources would give a fair billing upon their energy profile. Such methods can facilitate the energy cost integration in different service models, even with higher abstraction levels such as SaaS and PaaS. Since the execution of each virtual machine instance can be tracked, the energy in that physical node can be metered and accounted using PTEM and SEA.

#### 1.2 Thesis Structure

The structure of this thesis is organized as follows:

- Chapter 2 introduces the state of art of energy/power measuring and profiling techniques in computing systems. We abstract several important concepts to show how our work is different from them, and how we advance this topic from a new perspective.

- Chapter 3 introduces the simulation framework we used in this thesis. We give a detailed description of our architecture and power simulator. Also, we have also introduced the benchmark suite and metrics to evaluate our proposals.

- Chapter 4 has made a case of accurate PTEM for on-chip resources. We propose an idealized reference model to perform accurate PTEM based on the resource utilization of each task. A simple, yet accurate, implementation of such approach is also proposed. The focus is the main shared hardware resources in current multicore processors, including SMT core and LLC.

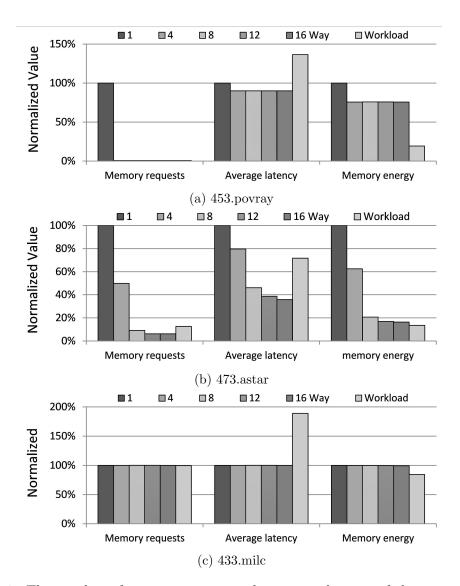

- Chapter 5 introduces the PTEM model in DRAM memory system and an efficient implementation of such method. A case study, in which the SPEC CPU 2006 benchmarks have been characterized using the proposals is also presented.

- Chapter 6 develops the concept of SEA from a theoretical point of view and discusses how it can contribute to different computing domains. Then, a low-overhead hardware mechanism to obtain SEA for on-chip resources in a multicore architecture is presented.

- Chapter 7 makes a case of SEA model in the DRAM memory system when one task

has been assigned different fraction of resources on the chip. The interactions of

memory requests in the memory controller and DRAM devices have been analyzed.

A practical and low-overhead implementation is also proposed.

- Chapter 8 concludes the work in this thesis and shows directions for future work.

- Chapter 9 lists the publication related to this thesis and during the PhD study.

## Related Work

Nowadays, modern microprocessors integrate in the order of billions of transistors on chip and operate at a frequency of several gigahertz. The power wall has already become a major obstacle in satisfying the growing computational needs. The multi-core/multi-threaded design paradigms have enabled the growth of throughput performance despite the slowdown in clock speed growth. Nevertheless, power dissipation and current delivery limitation make it hard to keep scaling indefinitely along the dimension of on-chip thread count. Therefore, accurate measurement and profiling of the energy/power consumption is needed so that future systems can optimize the power dissipation to better convert the electrical power into computing power.

In this chapter, we show the state of the art in the power/energy consumption measurement and profiling in computing systems. First of all, we introduce the energy consumption taxonomy, based on which, we elaborate the classification to better fit our needs. Then, we review several studies on how to abstract the energy of the devices using different means. In the fields of energy or power profiling, we illustrate works on different categories including: power characterization of computing systems, hardware components power consumption breakdown, and software component energy breakdown. In the context of these related works, we can see how our contributions advance the state of the art in this field.

# 2.1 Energy Consumption in Computing Systems, A Taxonomy

Within a given computing system, *energy* stands for the source which powers the hardware devices to operate. The standard measurement of *energy* is *Joules*, directly reflecting the electricity cost. And *power* is the rate at which the *energy* is consumed, and is measured in *Watts* which corresponds to *Joules* per second.

The distinction between energy and power is key to understand per-task energy measurement in multi-core architectures. For instance, when several tasks run concurrently in a multi-core system with abundant shared resources, the power dissipation of one task is most probably reduced compared with the case when it runs alone in the system. However, the energy consumption incurred by its execution is undetermined because of the – likely – prolonged execution time. In this thesis, we study the energy consumed by tasks when running in resource-sharing multi-core systems, by analyzing the power each task dissipated in time intervals during their execution.

In digital Complementary Metal-Oxide-Semiconductor (CMOS) technology, the energy consumption mainly comes from three resources: a) The logic transition that makes the current flow through the transistors. This occurs when the circuit transitions back and forth between the two logic levels. The electrical energy is consumed by the parasitic capacitances and resistance of transistors. b) The short circuit current that flows directly from supply to ground when the n-subnetwork and the p-subnetwork of a CMOS gate both conduct simultaneously. c) The leakage current between the source and drain of transistors. In former studies, they have been commonly categorized into dynamic power and static power [73, 113]. Specifically, dynamic power includes power dissipated by the logic transition and short circuit current, and static power refers to the power dissipated by leakage current. However, such classification, although has been conventionally used to study circuit and system power consumption, does not fit our need to attribute the energy consumption to tasks since we need more precise categories. Therefore, for the sake of clarity, we break down the energy consumed in a computing system into three main components: dynamic active energy, dynamic maintenance energy and leakage energy. These terms are consistently used in this thesis.

• Dynamic active energy corresponds to the energy consumed performing those actions needed by the instructions executed, such as the energy used to read a register or to issue an instruction. When considering the energy consumed during a given time interval, we can also express as the dynamic active power, which may vary along

time.

- Dynamic maintenance energy corresponds to the energy wasted in useless activities not triggered by any particular instruction, for instance, the significant clocking power that is consumed in idle blocks. Similarly, many SRAM arrays such as cache memories precharge some bitlines every cycle in order to speed up accesses. However, such activity is useless if no access occurs [16]. Note that the energy consumed due to an access corresponding to a useless instruction (e.g., a misspeculated instruction) is considered as dynamic active energy despite such activity is useless because the action has been triggered by the instruction under execution. Due to the fact that these useless activities constantly consume energy during the whole system active period, dynamic maintenance energy can also be expressed as dynamic maintenance power in most cases.

- Leakage energy corresponds to the energy wasted due to imperfections of the technology used to implement the circuit. Thus, it includes all energy wasted due to undesired leakage current and parasitic current from supply to ground. Leakage energy persists whether a computer is active or idle, since the leakage and parasitic current flow through transistors even when the transistors are turned off as long as they are powered up. Thus, leakage energy consumed in a given time interval can also be expressed as leakage power.

Bear in mind that dynamic active and maintenance power are both derived as a superset of logic transition and short circuit current in the CMOS circuit, and they can be summed up to dynamic power. In this sense, our study can be easily aligned with former studies. Breaking down dynamic active and maintenance energy is useful in our context since it avoids mixing the energy consumed due to the activity triggered by the instructions executed and the energy that cannot be attributed to any task, especially if several of them are running. Dynamic maintenance power has been recognized as platform power in some other works [102].

For the studies related to hardware analysis, the focus is mainly on power consumption since it is a direct reflection of the device computation power and sensitive to the thermal capacity. In contrast, for software related studies, the focus is instead on the total energy consumed by the piece of software that is executed. In the following sections, these terminologies are carefully distinguished.

## 2.2 Computing System Power Measurement

Obtaining power figures of complex, highly-threaded multi-core system is a difficult challenge. The effort invested on this task is large. The most common approaches can be classified as either direct power measurement or indirect power measurement, although some studies have considered a hybrid approach to obtain improved results [43,48].

#### 2.2.1 Direct Power Measurement

Direct hardware-based power measurement consists of measuring the current and supply voltage level on a particular component, for instance, the processor and the memory system. Then the measured values are used to compute the power. Such measurement requires different types of meters, some specifically designed circuits embedded in the platform, and power sensors inside the device.

Meters measure the power dissipation of the device in a straightforward way by connecting them between the power supply and the measured component. However, the widely used digital multimeter [55] or AC power meter [109], sample the measured device at a coarse granularity, normally at around 1 Hz.

Direct power measurement typically needs specialized device support, as explained in [105]. Nowadays, most of the servers have the service processor designed inside, which is a hardware and software integrated platform that works independently from the processor and the operating system. The service processor uses the power sensors to monitor the power, and voltage and temperature sensors to refine the measurements [43, 48]. The monitored results are read through an interface by the controller to provide the data to the operating system. The information can be used by the software to optimize the performance, power and energy efficiency. Furthermore, such hardware/software support also allows promoting the sampling frequency up to 3kHz [27].

#### 2.2.2 Indirect Power Measurement

Indirect power measurement can be performed on a simulation platform or at runtime inside the operating system. Thus, measurements are less accurate. However indirect power measurement does not need specific hardware support such as the service processor, and can better correlate the power with the performance of the device.

Hardware-level power model. In the case of microarchitecture simulation, normally a hardware-level power model is used [65, 91]. As described in section 2.1, the classical

breakdown of energy in CMOS circuits includes *dynamic power* and *static power*. For a particular hardware device, or a component in the processor, the power can be derived with the following two formulas:

$$P_{dynamic} = C \cdot V_{dd}^2 \cdot \alpha \cdot f \tag{2.1}$$

$$P_{static} = I_{leakage} \cdot V_{dd} \tag{2.2}$$

where C stands for the load capacitance,  $V_{dd}$  stands for the supply voltage,  $\alpha$  represents the activity ratio on the hardware device, f is the clock frequency and  $I_{leakage}$  stands for the leakage current of the circuit. Such low level models are arduous to use in architectural studies since the low level details are hard to derive for all components, thus making the estimation inefficient and costly. Wattch and CACTI tradeoff the estimation accuracy with simulation time by flexibly modeling the structure of each component with a general purpose model [16,87]. Such characteristic helps them being pervasively used in research studies. In many cases, these models are compared against approaches using circuit-based mechanisms.

Software-based power model. Although the hardware-level models can provide very accurate but time-consuming power information, the online power estimation often relies on the software-based models. Such models use performance statistics supplied by the operating system, where multiple indicators are used to reflect the hardware states and task execution. The selection of indicators is normally based on tuning the estimation by comparing with real system power and the result of hardware-level models [7,11,12,14,36]. In general, these models rely on collecting data from a set of events counters, voltage and temperature sensors, with coefficients derived from an empirical linear regression model. Depending on the system under study and the purpose of the power estimation (e.g., analyzing a hardware component, a process in the operating system or a program phase) different sets of events may be chosen. Note that in the software-based models, the term event may not directly map to the Performance Monitoring Counters (PMCs), but may also be a calculated metric, such as the Instruction Per Cycle (IPC).

Power model abstraction. In both cases, when estimating the runtime energy consumption, the power models can be generalized as analytic functions of a set of parameters, where the power consumption incurred by the execution of a program is derived based on their correlations. Therefore, in a system with J major components, each with I events count, the runtime power is computed as follows:

$$Power = \sum_{j=1}^{J} \beta_j \times \left( SP_j \times T_j + DP_j \times \sum_{i=1}^{I_j} \alpha_j^i \times e_j^i \right)$$

(2.3)

where  $SP_j$  and  $DP_j$  stand for the pre-calculated static power and dynamic power of component j.  $T_j$  is the activated time of component j and  $e_j^i$  is the event count obtained for j.  $\alpha_j^i$  and  $\beta_j$  stand for a set of coefficients derived through a linear regression model.

The same formula can be applied to software-based models, the difference is that, J refers to a set of selected indicators in any particular use case, each with I as event count.  $SP_j$ ,  $DP_j$  are derived through a linear regression model as well as  $\alpha_j^i$  and  $\beta_j$ .

Note that we have used the approach based on the hardware-level power model in our simulation framework.

## 2.3 Energy and Power Profiling

#### 2.3.1 Processor power consumption characterization

The power and thermal characteristics of a processor are essential for designing its power delivery system, packaging, cooling, and power/thermal management schemes. For such purposes, the maximum power and thermal profile of a processor need to be studied. In the following works, a set of micro-benchmarks – known as *power virus* – are designed to stress the processor to its peak power.

In [56], the concept of maximum power consumption has been refined into maximum sustainable power and maximum single cycle power. The maximum sustainable power is the maximum power of the processor that lasts for a time interval that is adequately long. Accurately characterizing it is important as it guides the design of the power delivery system and the packaging requirements for the microprocessor. Similarly, the maximum single-cycle power is the maximum power that can be consumed by the processor during one processor cycle. It holds an important key to estimate the maximum transient current that can be drawn by the microprocessor. By taking into account the information on instructions, input data and architecture details, this study generates micro-benchmarks and tests the above characteristics of a particular processor setup with simulation.

In [10], Bertran et al. present a tool to generate micro-benchmarks to explore the maximum power consumption of a real machine. With configurable low-level micro-architecture semantics knowledge of the machine, a taxonomy in terms of energy per instruction (EPI) and processor activity characteristics has been developed. Using such information, authors

use a compiler-like pass-based code generator to provide flexibility and full control of the micro-benchmarks generation.

Using the same methodology, Kestor et al. [61] characterize the on-chip memory hierarchy by designing a set of micro-benchmarks that move data through different levels of cache.

#### 2.3.2 Hardware component level power consumption breakdown

In recent years, there has been an increasing interest in breaking down the power consumption to different hardware component levels in different environments from data centers [9,59] to smartphones [17,20,90,92]. Those detailed power measurements improve the characterization of the hardware device, and thus the future designs and implementations can improve the power/performance characteristics of the system.

Many proposals [14,17,82,90,92,95] estimate the overall system energy consumption within the software using similar PMC-based approaches as introduced in 2.2.2, and then break it down across the different hardware components at a coarse-granularity, such as the processor, memory and screen. POWER7 processor uses power proxy [32,48] where the monitored power estimations divided among each core. Such model uses as a proxy around 50 dedicated hardware counters, along with voltage, frequency and temperature sensors. Similar firmware is also implemented in Intel Sandy Bridge architectures power management module to break down the power consumption of the system [99]. That firmware uses 100 PMCs for active power distribution, and voltage and temperature sensors for static power distribution.

#### 2.3.3 Software component energy consumption breakdown

From the software side, refining the runtime energy measurement during program's execution in a given platform is also a research hotspot. Several studies focus on attributing energy to the execution phases or blocks of a running program.

Performance and power vary through the execution of a program. To better analyze the program power behavior and optimize power usage, timing-based power behavior profile is required. Similar to Simpoint [103], techniques based on the basic block vector compare the similarities between different time intervals, to find the representative ones [44]. Based on this, Hu et al. [45] proposed a technique to find the representative phases in a given time interval by incorporating the control flow and runtime events profiles.

Systematic profiling tools characterize the program runtime behavior in different ways [54, 67, 70, 75, 97] (e.g., sampling events like stack traces, hardware events, etc.). By cross-

correlating this information with the executable binary, these tools can locate the hottest process, routine, code regions, library/kernel calls, and measure the performance across different compilations and/or platforms. By correlating with online power measurements, such tools can also enable fine-granularity distribution of the energy.

Shen et al. [102] proposed a request-level OS mechanism to meter power consumption to each server request based on PMCs [7]. The authors consider both active and maintenance power and attribute it to the responsible server requests. However, the per-task energy estimates obtained with this approach cannot be accurately obtained since, as stated by the authors, "Request executions in a concurrent, multi-stage server contain fine-grained activities with frequent context switches, and direct power measurements on such spatial and temporal granularities are not available in today's systems".

In a given time interval during the execution of a program, its power consumption is determined by the bunch of instructions that execute through the pipeline, which may be of different types, exhibit data dependencies, incurred different activities, etc. Tools like Linux perf [70] and oprofile [54] can identify an executed instruction periodically, and thus allow locating a coarse code region where this instruction resides. By correlating such techniques with the power consumption sampling, authors in [69] attribute power consumption of each sample period to the basic block where the sampled instruction resides in. Conversely, authors in [68] propose to estimate the instant power consumption at runtime by pre-characterizing the power that could be consumed by each basic block. Their estimation not only takes into account the instruction types and mixes, but also explores the inter-block effects to recalibrate their estimates, which is enabled by fine-granularity simulation. However, the power of the processor is determined by the activities of basic blocks executed together in a time window, denoted as superblock [40, 49]. Superblocks has diverse combinations of basic blocks, thus, for an application with complicated control flow, it is infeasible to pre-determine the power consumption in advance.

#### 2.3.4 Current per-task energy measurement models

The above studies have shown to be very accurate in profiling per-component and overall system's energy consumption. However, the hardware-level approaches focus on breaking down the energy to the main hardware components, in which only the activities in the hardware have been taken into account. The task-level interactions, either from the operating system or the Task-Level Parallelism (TLP) on the hardware, have been ignored. Therefore, these approaches do not fit for per-task energy measurements. In contrast, the software-component approaches can only be performed under an important assumption:

the application is the only one scheduled on the processor and it is accounted all the energy consumed in the system, which allows performing the component-level breakdown. In the scenarios where multiple tasks concurrently run, these approaches fail to abstract the task energy from the energy consumed in the system. In summary, the former introduced studies are denoted as Per-Component Energy Metering (PCEM).

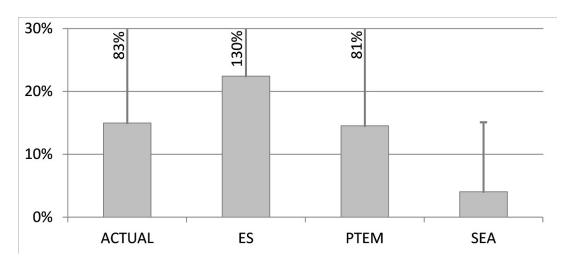

Next, we analyze the mechanisms for per-task energy measurement that can be derived from current multicore and multi-threaded systems. In modern multicores, the total energy consumption of the system and its main components can be monitored or accurately estimated during a long-enough time interval. In the scenarios where N tasks  $T_1, \ldots, T_N$  are concurrently running, the goal of per-task energy measurement is to distribute the energy among them. A simple and naive method is to evenly split the energy to the running tasks, which we denote Evenly Split (ES) model. Unfortunately, this is the most commonly used method nowadays as task-level hardware activities are not easy to identify in general and per-task energy measurement did not draw enough attention until recently. Thus, for a given task in ES model, the energy assigned to it is calculated as follows:

$$Energy_i = \sum_{j=1}^{J} \frac{e_j}{N} = \frac{Energy_{total}}{N}$$

(2.4)

where  $e_j$  stands for the energy consumed in each component, and the sum of all these values corresponds to the total energy consumption of the system  $Energy_{total}$ .

To take one step further, we can correlate some available task-level metrics with the energy attributed to the running tasks, e.g., the committed instruction count of each task and other PMC values. These task-level metrics roughly indicate the usage of the hardware resources done by each task. We denote this approach *Proportional To Access (PTA)*.

Note that we have to derive the PTA model separately in different hardware structures, mainly the core, LLC and memory system. In the case of the LLC and memory, PTA is a simple approach that distributes energy to tasks proportionally to the number of accesses to each structure. In current processors, per-task LLC and memory accesses can be monitored with performance counters [58]. In contrast, the core slices have many components that can incur diverse activities. Thus, from the set of available PMCs, an empirical linear regression model is used to correlate the energy consumption with tasks.

Thus, for the PTA model, the energy attributed to a task i, can be formalized as follows:

$$Energy_i = Energy_{total} \times \left( \sum_{j=1}^{J} \left( \beta_j \times \frac{a_j^i}{\sum_{i=1}^{N} a_j^i} \right) + \alpha \right)$$

(2.5)

where  $Energy_{total}$  stands for the energy consumed in the system,  $a_j^i$  stands for the activity count task i has in component j, and  $\sum_{i=1}^{N} a_j^i$  stands for the sum of activities in component j.  $\beta_j$  and  $\alpha$  are a set of coefficients derived from the linear regression model. Note that both ES and PTA models are closed-loop methods, since we perform the attribution of energy based on accurately monitored system energy.

It is our position that existing methods in current systems will not go beyond the scope of these two models. However, such models lack the capabilities to deliver accurate pertask energy estimates. In order to obtain more accurate estimates in multicores systems, we need support from the architecture level.

## 2.4 Summary

In this chapter, we have described the state of art on energy measurement in current computing systems. Directly measuring the power of the computing system demands external devices. This measurement represents the actual power consumption, but it does not provide enough information to estimate per-task energy measurement. To approximate this measurement, indirect approaches have been proposed based on performance monitoring counters. Such solutions have also inspired further studies on breaking down the energy to different components, both in the hardware and software level. However, as multicore processors have already become the reference platform in almost all computing domains, to the best of our knowledge, no model has been reported to accurately provide per-task energy measurement.

Per-task energy measurement can be easily distinguished from the former works, since all these studies are focused on the energy consumption of the whole system. The proposals on per-task energy measurement in this thesis aim at providing much more accurate information and concrete models to solve the ambiguities in distributing energy consumption of a computing system to its multiple running tasks. We will show in the following chapters that it is not trivial to achieve such goals. With simple and naive models that can be plainly derived, such as ES and PTA, none of them can estimate per-task energy consumption with satisfactory accuracy. In contrast, our proposals, PTEM and SEA, significantly advance the state of art in this field through hardware approaches.

# **Experimental Framework**

In this chapter, we describe the simulation framework we use to implement and validate our PTEM and SEA proposals. To this end we build on a set of cycle-accurate architecture performance simulators, power simulators, and benchmark suites. Combining those elements we build our own experimental methodology, which we complement with the appropriate metrics to evaluate PTEM and SEA.

#### 3.1 Simulation Framework

Simulation has shown to be a powerful and efficient tool for research in the computer architecture field. Simulation is used pervasively in both academic community and industry. In particular, microarchitecture simulation has been widely deployed in the computer architecture arena. The main advantages of microarchitecture simulation are as follows: a) those simulators are capable of modeling different levels of architecture details and setups; b) with reasonable tradeoffs between execution time and simulation detail, those simulators can achieve highly accurate results compared with executions on actual hardware or lower-level simulations (e.g. gate level or register transfer level [34,35]); c) those simulators are flexible and so convenient for applying hardware changes that are needed to evaluate novel ideas, such as PTEM and SEA. Such features make microarchitecture simulators – just simulators from now onwards – the most suitable platforms to perform the research of this thesis. Note that we have modeled a general-purpose processor and memory system, not a particular real system. On the one hand, this is because cycle-accurate simulation of a particular processor would require privileged access to its detailed design data. On the other hand, our study focuses on the methodologies to measure the energy for each

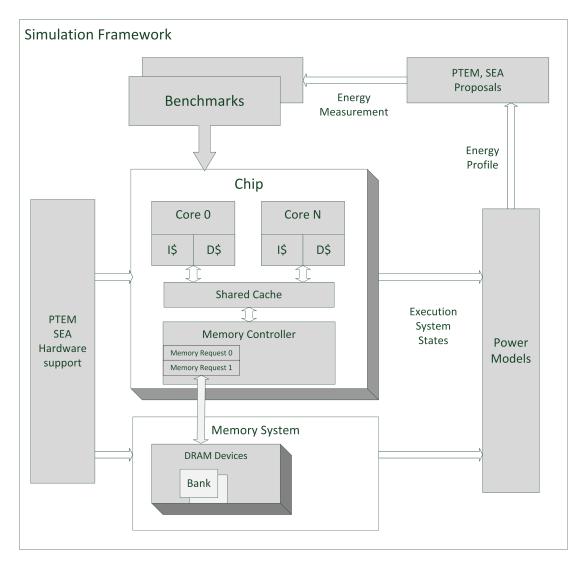

Figure 3.1: Diagram of the simulation framework

task in a generic way, which can be adapted to different processors and memory systems as we have modeled all the main components in modern processors.

The target of this thesis is to explore PTEM and SEA in two main components of a computer system: the processor (core slice<sup>1</sup>, shared caches, buses, etc.) and the memory subsystem. To this end, we need concrete information on the dynamic behavior and energy consumption of a program during its execution in a computing system. In addition, we need efficient simulation, yet accurate, to allow a large amount of experiments to be performed, so that we can come up with enough results to prove the advantages of our solutions.

<sup>&</sup>lt;sup>1</sup>In this thesis, we refer the processor pipeline units and the private caches as the core slice

Our simulation framework builds upon two pillars: performance and power simulators. A diagram of this framework is depicted in Figure 3.1. In this framework, we use the performance simulator to emulate the timing behavior of benchmarks, which are reflected into energy consumption by the power simulator. Based on the derived energy, our PTEM and SEA proposals attribute it to the running benchmarks. Since our proposal may need extra hardware support from the architecture, the feasible changes can be applied to the simulator, thus allowing us to explore the design space. In this thesis, we have used existing simulators instead of developing a brand new platform to avoid wasting efforts, and because using these already well-designed and validated simulators lets us have high confidence on the simulation efficiency and accuracy.

#### 3.2 Performance Simulators

Most current performance simulators focus on the on-chip components, while the highly complicated behaviors in memory system have been somewhat ignored. In such simulators, some naive memory models have been applied assuming either fixed memory request latency with infinite bandwidth or simply aggregating the latencies of consecutive memory requests. This is problematic since processor and memory systems are highly dependent on each other. As the processor in general operates at a higher clocking frequency than memory, sometimes it is forced to be stalled a significant number of cycles waiting for the memory requests to be served. Specially, consecutive memory requests could generate different levels of conflicts, e.g., when accessing the memory banks, buses, memory controller resources, etc. Instead, it can also be the case that the latency of these memory requests gets totally or partially overlapped due to the large capacity of the memory system. Analogously to the case of standalone processor simulation, standalone memory system simulation can neither reveal the whole picture. For this reason, we build our performance simulator by interactively integrating a processor and a memory system simulator.

On the processor side, we use MPsim [3], a trace-driven cycle-accurate simulator that supports CMP and SMT architectures, which is an enhanced version of SMTSim [110]. This simulator is developed at UPC, and has been used in a large number of prior works [18, 77, 78, 86, 114]. MPsim emulates the processor with a model of the processor pipeline, on-chip cache hierarchy and buses. The simulated pipeline stages are as follows: fetch, branch predict, decode, register rename, register read/write, cache read/write, execute until commit. Since trace-driven simulation uses instruction traces that are recorded during a previous execution of a program, MPsim is adapted to emulate the impact from

| Parameter | Description                                                  | Cycles |

|-----------|--------------------------------------------------------------|--------|

| $t_{RAS}$ | Time interval between a row access command and data          | 24     |

|           | restoration in a DRAM array                                  |        |

| $t_{CAS}$ | Time interval between a column access command and the        | 10     |

|           | start of data return from the DRAM devices                   |        |

| $t_{RCD}$ | Time interval between row access and data ready in the sense | 10     |

|           | amplifiers                                                   |        |

| $t_{RTP}$ | Time interval between a read and a precharge command         | 5      |

| $t_{RP}$  | Time interval that it takes for a DRAM array to be prepared  | 18     |

|           | for another row access                                       |        |

| $t_{RRD}$ | Minimum time interval between two row-activation com-        | 4      |

|           | mands to the same DRAM device                                |        |

| $t_{RC}$  | Time interval between accesses to different rows in a bank   | 34     |

| $t_{WR}$  | Minimum time interval between the end of a write data burst  | 10     |

|           | and the start of a precharge command                         |        |

| $t_{WTR}$ | Minimum time interval between the end of a write data burst  | 5      |

|           | and the start of a column read command                       |        |

| $t_{RFC}$ | Time interval between refresh and activation commands        | 107    |

Table 3.1: Summary of some DRAM device timing parameters used in DRAMSim2

wrong path instructions by using a separated dictionary to provide information on all static instructions to avoid compromising the accuracy of the simulation results. In addition, we add several enhancements to it in this work to make it better fit with the memory system simulator and power models. For instance, we have added an exact read/write port model for each components to ensure the activities incurred on each component in every cycle can be simulated precisely and power can be accounted conveniently.

For the memory system, we use DRAMSim2 [98], also a cycle-accurate simulator to emulate the DDR2/3 memory system with a set of DRAM devices, a memory controller and a standard memory bus. This simulator is either driven by a trace of memory requests with their timing information, or connected to a processor simulator through a robust interface. On the arrival of a memory request, the memory controller decomposes it into the corresponding DRAM device internal commands and schedules them to perform operations in the DRAM devices. And after the memory request finishes, DRAMSim2 returns the data to the processor. These internal procedures are modeled with circuit-level details, such as memory bank activating, data read/write and precharge, etc. The latency of each command follows a strict timing model, which is a generic abstraction of modern DDR2/3 memory systems. It enables convenient configuration in the simulator, since parameters from different technologies and designs of DRAM devices are largely different. A brief description of some parameters used in this model is shown in Table 3.1, along with example values obtained from the specification on DDR3\_64B\_SG15 with  $0.68\mathrm{nm}$ technology. A more detailed description of how DDR2/3 DRAM memory works can be found in Section 5.2.1.

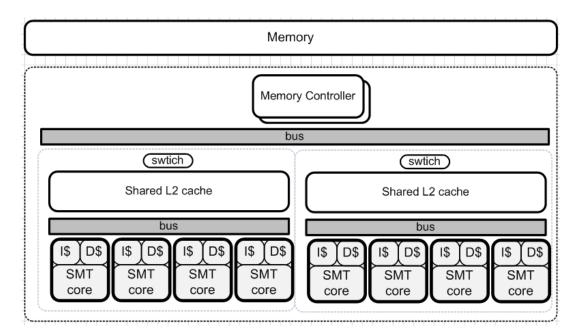

Table 3.2: Configuration Summary

| Parameter              | Description                                           |  |  |  |

|------------------------|-------------------------------------------------------|--|--|--|

| Chip details           |                                                       |  |  |  |

| Cluster count          | 1, 2, 4 and 8                                         |  |  |  |

| Core count             | 4 cores per cluster; 1-, 2-thread SMT                 |  |  |  |

| Supply voltage         | 1.0V                                                  |  |  |  |

| Technology             | 65nm                                                  |  |  |  |

|                        | Core details                                          |  |  |  |

| Core type              | out-of-order                                          |  |  |  |

| Fetch, decode, issue,  | 2/4 instr/cycle                                       |  |  |  |

| commit bandwidth       |                                                       |  |  |  |

| Branch Predictor       | Hybrid 256B Gshare                                    |  |  |  |

| Branch target buffer   | 32 entries, 4-way                                     |  |  |  |

| Return address stack   | 32 entries                                            |  |  |  |

| Reorder buffer size    | 96 entries                                            |  |  |  |

| Issue queues size      | 48/48/48 entries for INT/FP/Load-store queues         |  |  |  |

| Register file          | 164 INT, 164 FP                                       |  |  |  |

| Functional Units       | 2 INT ALU (1 cyc), 1 mult (4 cyc), 1 div (7 cyc)      |  |  |  |

|                        | 1 FP ALU (6 cyc), 1 mult (6 cyc), 1 div (17 cyc)      |  |  |  |

| Instruction L1         | 32KB, 4-way, 32B/line (2 cycles hit)                  |  |  |  |

| Data L1                | 32KB, 4-way, 32B/line (2 cycles hit)                  |  |  |  |

| Instruction TLB        | 256 entries fully-associative (1 cycle hit)           |  |  |  |

| Data TLB               | 256 entries fully-associative (1 cycle hit)           |  |  |  |

|                        | Shared L2 Cache                                       |  |  |  |

| Unified L2             | 2MB, 16-way, 64B/line (3 cycles hit, 300 cycles miss) |  |  |  |

| Main Memory            |                                                       |  |  |  |

| Size                   | 8GB                                                   |  |  |  |

| Frequency              | 1000MHz                                               |  |  |  |

| Row-buffer policy      | Close-page or open-page                               |  |  |  |

| Address mapping scheme | Shared bank                                           |  |  |  |

| Power-down mode        | Fast                                                  |  |  |  |

| Supply voltage         | 1.35V                                                 |  |  |  |

| Technology             | 65nm                                                  |  |  |  |

During the integration of two simulators, the synchronization was relatively straightforward since both simulators are cycle-based. In modern computers, processors normally work at a higher clock frequency than memory, commonly ranging from 1.5 GHz to 3 GHz. The frequency of DRAM DDR2/3 memory normally ranges from 667 MHz to 1666 MHz. In this thesis, as we assume a general purpose architecture, the processor frequency has been set to 2 GHz, and the memory frequency to 1000 MHz, although our findings are not specific to any particular clock frequencies. This particular setup has been chosen to avoid extra synchronization complexity. Although the memory requests generated from the processor in 2 cycles are dispatched together to the memory system, their order is maintained by the memory controller.

Keeping track of instructions in the two simulators is also trivial. As for a load/store

instruction, its memory address is used to search through the on-chip cache-hierarchy in MPsim. If it incurs a Last Level Cache (LLC) miss, the same address is used for addressing in the memory system after its execution stalls in the pipeline. Also, the information of this LLC miss is stored in a Last Level Miss Status Handling Register (LLMSHR) to allow other concurrent misses. DRAMSim2 memory controller also preserves the information of each memory request. When one request completes its operations, the memory controller uses a callback mechanism to notify the processor of the returning data and the information related to the memory request. After receiving the information and data, the LLMSHR is iterated to find the matched entry. This entry points to the stalled instruction which generated the memory request, and upon the reception of the memory answer, such instruction is resumed to complete its execution. Note that from the memory side, there is no hard limitation on the number of co-running tasks in the system, which simplifies the integration process to connect DRAMSim2 with a regular multi-core architecture. Instead, the only limit is the number of pending memory requests that can be processed in parallel, which in turn is limited by the number of commands that can be stored in the memory controller command queue (128 entries in our case).

An overview of the configuration of the performance simulator used across this thesis can be found in Table 3.2.

#### 3.3 Power Simulators

To simulate the energy consumption of a program during its execution, with the runtime information provided by the performance simulators, an infrastructure is needed to analyze and quantify the power dissipation of the program on the hardware components. In this thesis, we have used parameterized power modeling infrastructures on the processor and memory system components of different hardware structures. A tradeoff is needed between the low-level details of the hardware designs, the model accuracy and the simulation speed, so that diverse configuration setups and workloads can be experimented efficiently.

The power models for the processor we used in this thesis are analogous to those of Wattch [16]. Wattch-like power models provide a framework where the activity- and time-based power consumption of the major units in the processor are parameterized and quantified, which makes it suitable to be integrated into our performance simulator of the processor. As the technology and configuration continuously change, the power of cache and SRAM-based components in our setup are modeled on top of CACTI 6.5 simulation tool [87]. CACTI is a flexible tool to model delay, energy (dynamic and leakage) and area of cache memories and SRAM-based arrays. Power models for functional units have been

| Unit            | Parameters E |           | Energy Co | Energy Consumption |                 |              |

|-----------------|--------------|-----------|-----------|--------------------|-----------------|--------------|

| Ome             | Size (B)     | R/W Ports | Block (B) | Type               | Per Access (nJ) | Leakage (mW) |

| IALU            |              |           |           |                    | 0.024           | 1.92         |

| FALU            |              |           |           |                    | 0.05            | 4.02         |

| BTB             | 8192         | 2         | 8         | cache              | 0.033           | 20.94        |

| RAS             | 2048         | 2         | 8         | cache              | 0.019           | 6.33         |

| DCache          | 32768        | 2         | 64        | cache              | 0.072           | 59.77        |

| ICache          | 32768        | 2         | 64        | cache              | 0.072           | 59.77        |

| DTLB            | 2048         | 2         | 8         | cache              | 0.013           | 5.74         |

| ITLB            | 2048         | 2         | 8         | cache              | 0.013           | 5.74         |

| INT Register    | 1312         | 10/6      | 8         | SRAM               | 0.016           | 5.06         |

| FP Register     | 1312         | 6/4       | 8         | SRAM               | 0.012           | 2.66         |

| INT Issue queue | 384          | 4/2       | 8         | cache              | 0.013           | 1.01         |

| FP Issue queue  | 384          | 2/2       | 8         | cache              | 0.012           | 0.71         |

| LS Issue queue  | 384          | 2/2       | 8         | cache              | 0.012           | 0.71         |

| Bus             |              |           |           |                    | 0.004           | 0.21         |

| ROB             | 2048         | 2/2       | 8         | cache              | 0.021           | 8.35         |

| LLC             | 2097152      | 1         | 64        | cache              | 1.76            | 224.75       |

Table 3.3: Summary of the power models on Major On-chip Components

updated to use modern designs. Although in recent studies the power estimations made from McPAT, a CACTI based power model, show a big gap with the real computer [117], we still use it as our platform. On the one hand, McPAT/CACTI power models are the current de facto standard in the computer architecture community, being extensively used in research works for design space exploration. On the other hand, this thesis is neither improving nor covering the gap of such models, but exploring the per-task energy distribution mechanisms based on the estimates made by such models. Therefore, even if power estimates cannot perfectly match with the real system, such analytical model helps us to reveal the interaction between hardware resources and tasks in an analyzable way. In this perspective, McPAT/CACTI power models provide the capabilities for analysis and fast simulation speed to make our research feasible. In Table 3.3, we show an example of the CACTI configurations and output that we have used for some major components on-chip.

Unlike on-chip resources, the memory power is more sensitive to the timing and addresses of memory requests. Although CACTi can provide accurate estimation on the memory power based on a given activity factor, which requires deep understanding of the memory structure, the estimation is rather static and so misses important details. Micron has published a set of *data sheet specifications* for system designers to estimate the power consumption of DDR2/3 DRAM memory. We derive the power model from the data sheet and integrate it to DRAMSim2 seamlessly since they come from the same source. The power model provides the current profiles, which correspond to the state of the DRAM

| Current    | Description                                    | Value (mA) |

|------------|------------------------------------------------|------------|

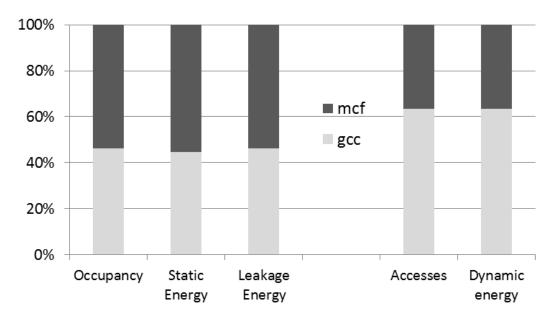

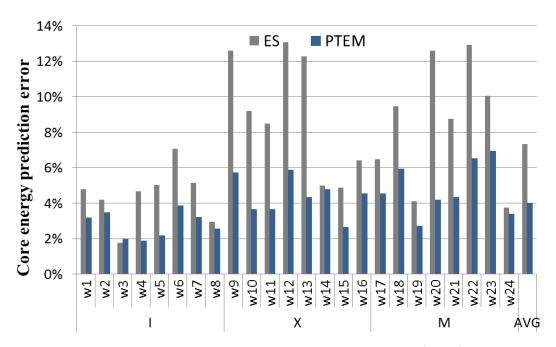

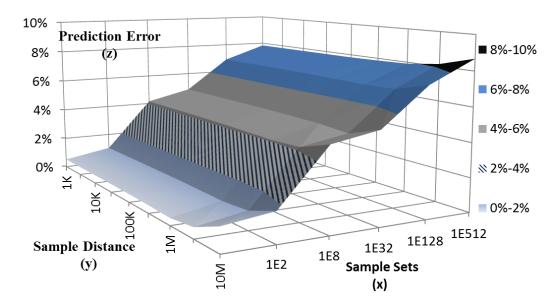

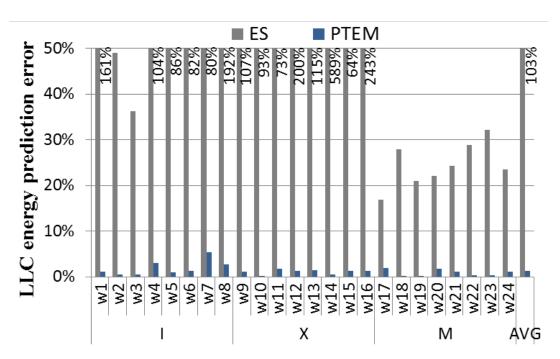

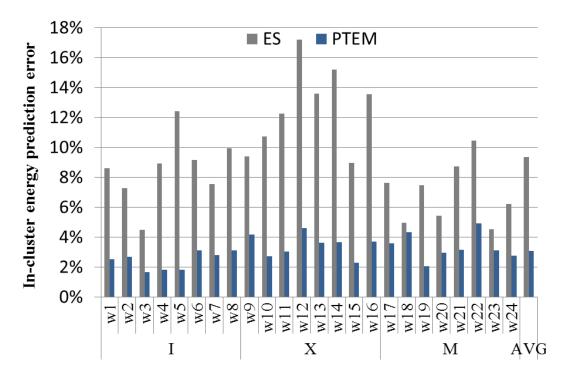

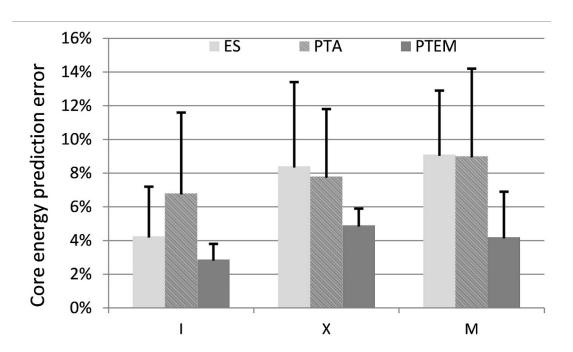

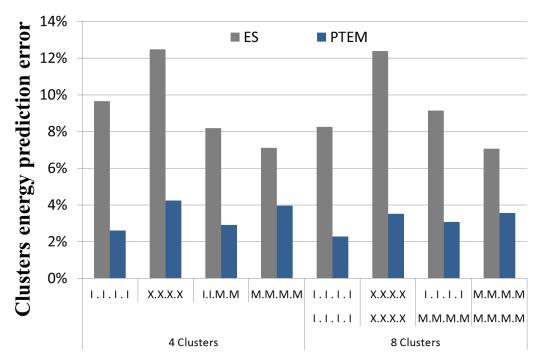

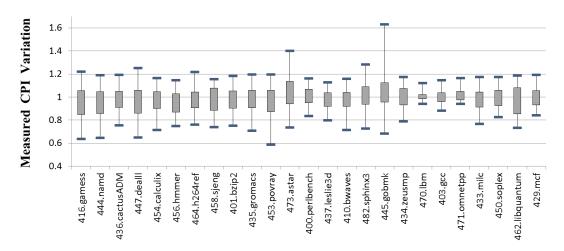

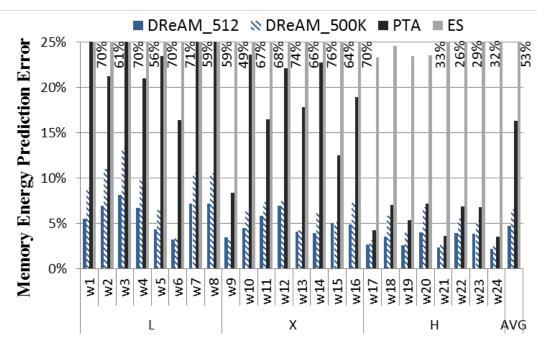

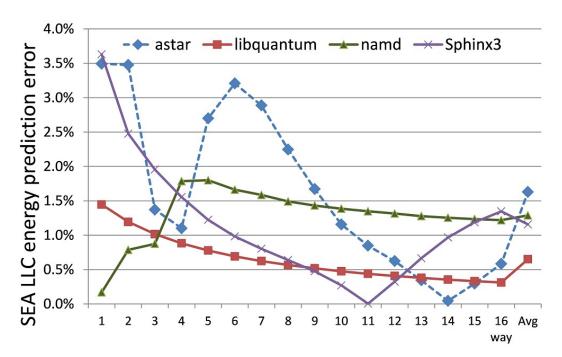

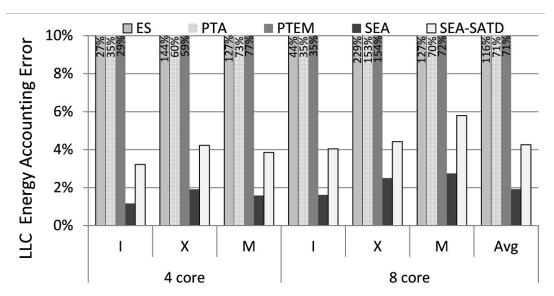

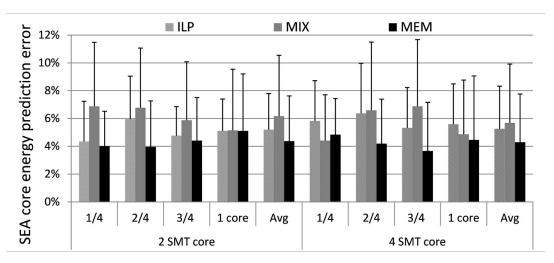

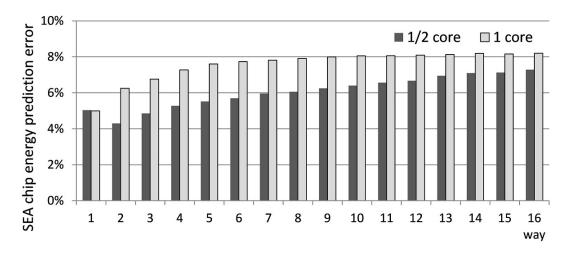

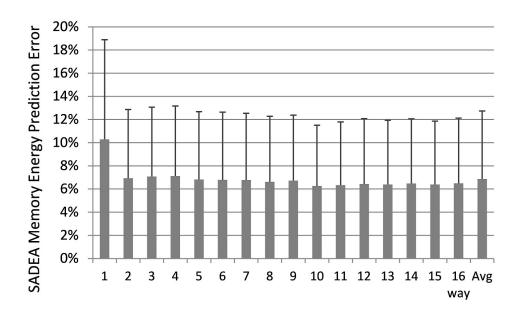

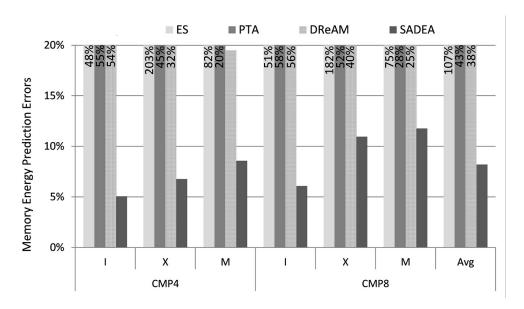

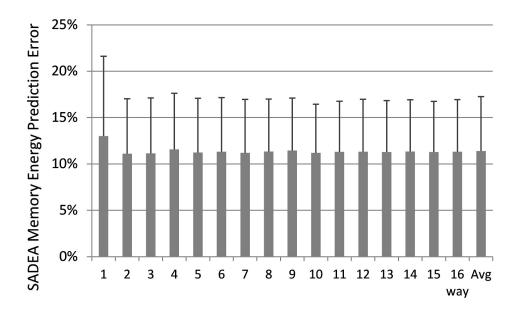

| $IDD_0$    | Operate one bank active-precharge current      | 100        |