## POWER-CONSTRAINED AWARE AND LATENCY-AWARE MICROARCHITECTURAL OPTIMIZATIONS IN MANY-CORE PROCESSORS

### by Sudhanshu Shekhar Jha

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) le repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX.No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (<a href="framing">framing</a>). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="framing">framing</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis the institutional repository **UPCommons** by (http://upcommons.upc.edu/tesis) and the cooperative repository TDX (http://www.tdx.cat/?localeattribute=en) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

## Improving the Efficiency of Multicore Systems Through Software and Hardware Cooperation

A DISSERTATION PRESENTED

BY

Víctor Javier Jiménez Pérez

TC

THE DEPARTMENT OF COMPUTER ARCHITECTURE

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN THE SUBJECT OF

Computer Science

Universitat Politècnica de Catalunya – Barcelona Tech Barcelona September 2016 ©2016 – Víctor Javier Jiménez Pérez all rights reserved. Thesis advisor: Dr. Francisco Cazorla Thesis advisor: Dr. Mateo Valero

### Improving the Efficiency of Multicore Systems Through Software and Hardware Cooperation

### **ABSTRACT**

Increasing processors' clock frequency has traditionally been one of the largest drivers of performance improvements for computing systems. In the first half of the 2000s, however, it became clear that continuing to increase frequency was not a viable solution anymore. Power consumption and power density became prohibitely costly, and processor manufacturers moved to multicore designs. This new paradigm introduced multiple challenges not present in single-threaded processors. Applications running on multicore systems share different resources such as the cache hierarchy and the memory bus. Resource sharing occurs at much finer degree when cores support multithreading as well. In this case, applications share the processor's pipeline too. Running multiple applications on the same processor allows for better utilization of its resources—which otherwise may just lie idle if an application does not use them. But sharing resources may create interferences between applications running on the system. While the degree of these interferences depends on the nature of the applications, it is typically desirable to reduce them in order to improve efficiency.

Most currently available processors expose a set of sensors and actuators that software can use to monitor and control resource sharing among the applications running on a system. But it is typically up to end users to analyze their workloads of interest and to manually use the actuators provided by the processor. Because of this, in many cases the different mechanisms for controlling resource sharing are simply left unused. In this thesis we present different techniques that rely on software/hardware interaction to monitor and improve application interference—and thus improve system efficiency. First we conduct a quantitative study showing the benefits of hardware/software cooperation on system efficiency. Then we narrow our focus on a given hardware knob: data prefetching. Specifically we develop and evaluate several adaptive solutions for improving the efficiency of hardware data prefetching on multicore systems. The impact of the solutions presented in this thesis, however, goes beyond the particular case of data prefetching. They serve as illustrative examples for developing software/hardware cooperation schemes that enable the efficient sharing of resources in multicore systems.

Resource sharing in a processor is a critical factor that significantly affects system efficiency. But resource sharing also occurs at other levels in a computing system. In large-scale computing facilities applications might also share storage and networking resources for instance. As a case study we consider the design of an energy accounting system relying on hardware/software cooperation for large-scale computing facilities. We explore multiple alternatives for the required sensors and actuators, as well as the inherent trade-offs in the design of such a system.

## Contents

| Ι | Introduction                               |                                                                 |          |  |

|---|--------------------------------------------|-----------------------------------------------------------------|----------|--|

|   | I.I                                        | Sensors and Actuators                                           | 3        |  |

|   | 1.2                                        | Problem Statement                                               | 4        |  |

|   | 1.3                                        | Using Hardware Data Prefetching as an Actuator                  | 6        |  |

|   | 1.4                                        | Contributions                                                   | 8        |  |

|   | 1.5                                        | List of Publications                                            | 9        |  |

|   | 1.6                                        | Dissertation Organization                                       | I        |  |

| 2 | Related Work                               |                                                                 |          |  |

|   | 2.I                                        | Hardware Solutions for Resource Management                      | 12       |  |

|   | 2.2                                        | Sampling-Based Online Adaptive Systems                          | 13       |  |

|   | 2.3                                        | Solutions Exposing Custom Sensors and Actuators to the Software | 14       |  |

|   | 2.4                                        | Thread Mapping                                                  | I        |  |

|   | 2.5                                        | General Prefetching                                             | 16       |  |

|   | 2.6                                        | Local Adaptive Prefetching                                      | 17       |  |

|   | 2.7                                        | CMP-Aware Adaptive Prefetching                                  | 17       |  |

|   | 2.8                                        | Adaptive Prefetching Solutions for Real Systems                 | 18       |  |

|   | 2.9                                        | Per-Task Energy Accounting                                      | 18       |  |

| 3 | MOTIVATION: IMPACT OF HARDWARE ACTUATORS 2 |                                                                 |          |  |

| , | 3.I                                        | The IBM POWER6 Processor                                        | 2.2      |  |

|   | 3.2                                        | Effect of Workload Characteristics                              | 25       |  |

|   | 3.3                                        | Effect of Core Usage                                            | 29       |  |

|   | 3.4                                        | PMC-Based Power Model                                           | 3:       |  |

|   | 3.5                                        | Improving Efficiency Through Hardware Knobs                     | 37       |  |

|   | 3.6                                        | Conclusions                                                     | 5C       |  |

| 4 | Platform Characterization and Methodology  |                                                                 |          |  |

|   | 4.I                                        | The IBM POWER7 Processor                                        | 5:<br>5: |  |

|   | 4.2                                        | Methodology                                                     | 66       |  |

|   |                                            |                                                                 |          |  |

| 5 | ADA                                        | APTIVE PREFETCHING: IMPROVING PER-APPLICATION PERFORMANCE       | 68       |  |

|   | 5.1                                        | Introduction                                                    | 68       |  |

|   | 5.2                                        | Adaptive Prefetching                                            | 69       |  |

|   | 5.3                                        | Results                                                         | 70       |  |

|    | 5.4                                                   | OS-Based Implementation                              | 89  |

|----|-------------------------------------------------------|------------------------------------------------------|-----|

|    | 5.5                                                   | Conclusions                                          | 91  |

| 6  | Bandwidth Shifting: Improving System-Wide Performance |                                                      |     |

|    | 6.I                                                   | Introduction                                         | 92  |

|    | 6.2                                                   | Effect of Prefetching on Performance and Bandwidth   | 94  |

|    | 6.3                                                   | Intelligent Bandwidth Shifting                       | 97  |

|    | 6.4                                                   | Results                                              | 103 |

|    | 6.5                                                   | Comparing Bandwidth Shifting to Adaptive Prefetching | II4 |

|    | 6.6                                                   | Conclusions                                          | 117 |

| 7  | Per-Task Energy Accounting                            |                                                      | 118 |

|    | 7 <b>.</b> I                                          | Introduction                                         | 118 |

|    | 7.2                                                   | Benefits of Energy-Aware Accounting/Billing          | 123 |

|    | 7.3                                                   | Target Facilities                                    | 127 |

|    | 7.4                                                   | Energy Accounting Design and Trade-Offs              | 128 |

|    | 7.5                                                   | Conclusions                                          | 134 |

| 8  | Conclusions and Future Work                           |                                                      | 135 |

|    | 8.1                                                   | Conclusions                                          | 135 |

|    | 8.2                                                   | Future Work                                          | 138 |

| RE | FERE                                                  | NCES                                                 | 151 |

## Listing of Figures

| I.I | Examples of sensors and actuators exposed by hardware to software                                                                                                     | 2        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 | Design overview for the proposed adaptive resource management system                                                                                                  | 5        |

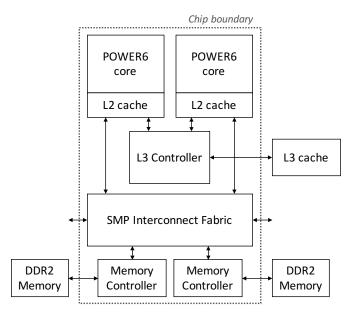

| 3.I | POWER6 microarchitecture overview                                                                                                                                     | 23       |

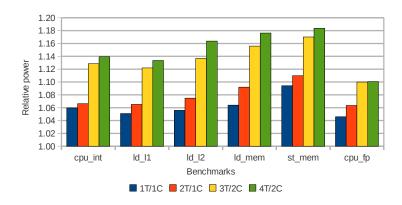

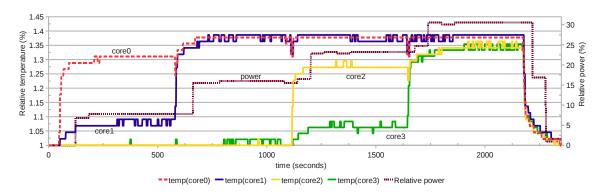

| 3.2 | METbench power consumption for different number of threads (T) and cores (C).                                                                                         | 26       |

| 3.3 | Several copies of cpu_int are used to create an incremental execution (2, 4, 6 and 8 hardware threads). The values are relative to the power and temperature measure- |          |

|     | ments when the system is idle.                                                                                                                                        | 29       |

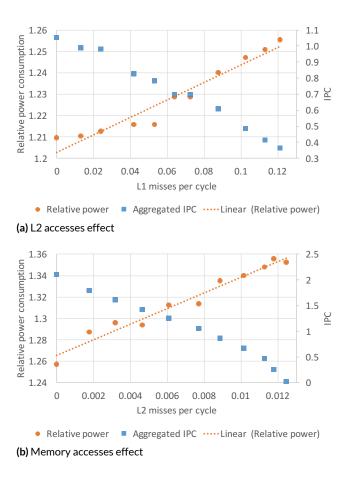

| 3.4 | Effect of accesses to L2 cache and main memory on system power consumption.                                                                                           |          |

|     | Power values are relative to the idle system consumption. Several instances of the same benchmark are executed to create a higher power delta. The regression line is |          |

|     | just an approximation to show the increasing trend                                                                                                                    | 33       |

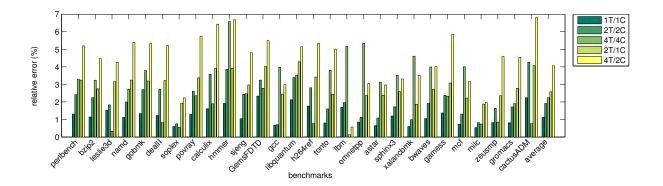

| 3.5 | Estimation accuracy for the power model trained with METbench data only, for dif-                                                                                     |          |

|     | ferent number of threads (T) and cores (C). For instance, $4T/2C$ means $4$ threads are                                                                               |          |

|     | run on 2 cores (using SMT capabilities). The error is computed as: $\frac{ measured-predicted }{measured} \times$                                                     |          |

|     | IOO                                                                                                                                                                   | 35       |

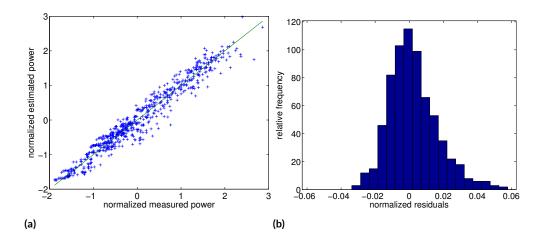

| 3.6 | Model validation using all the available data (METbench and SPEC CPU2006). (a)                                                                                        |          |

|     | shows the normalized measured vs. estimated power. The values are normalized                                                                                          |          |

|     | by subtracting the mean of the error and dividing by the standard deviation of the                                                                                    |          |

|     | error. (b) shows the residue error distribution with the cross-validation process. The                                                                                | 26       |

| 2.7 | residuals are normalized by dividing to the actual measure value                                                                                                      | 36<br>40 |

| 3.7 | Tower spikes due to tick time events                                                                                                                                  | 40       |

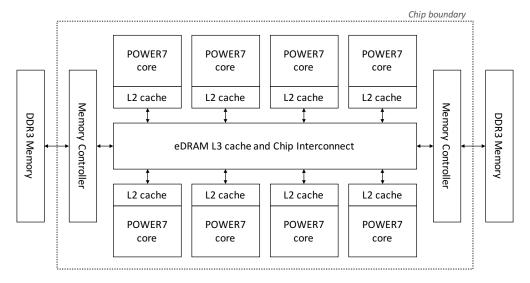

| 4.I | POWER7 microarchitecture overview                                                                                                                                     | 52       |

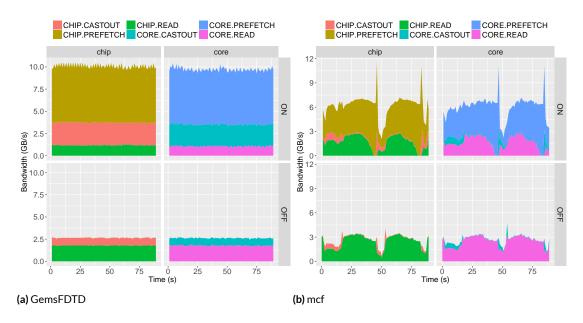

| 4.2 | Measured bandwidth for two SPEC CPU2006 benchmarks                                                                                                                    | 57       |

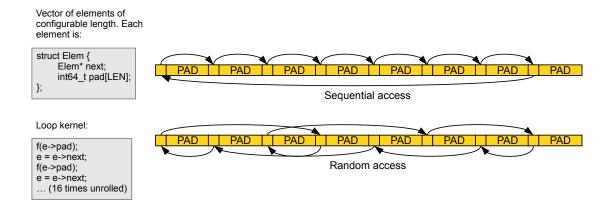

| 4.3 | Microbenchmarks description. The microbenchmarks perform an array traversal                                                                                           |          |

|     | either in sequential or random order. The distance between accesses is a configurable                                                                                 |          |

|     | parameter. Depending on function f, the accesses to every array element can be loads,                                                                                 | 0        |

|     | stores or both                                                                                                                                                        | 58       |

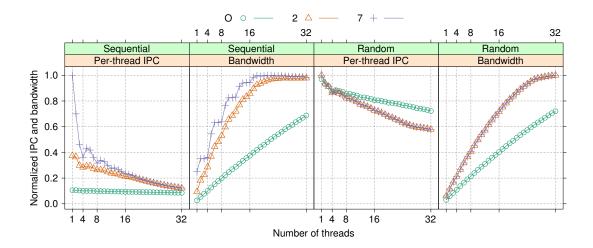

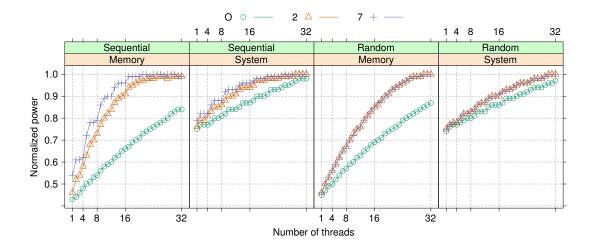

| 4.4 | marks are used to show the effect of prefetch depth on performance and memory                                                                                         |          |

|     | bandwidth. Threads are bound to contexts in an increasing order (the first four                                                                                       |          |

|     | threads go to the first core, the next four ones go to the second core, and so on).                                                                                   |          |

|     | Values are normalized to the maximum value observed in each plot                                                                                                      | 60       |

| 4.5         | Stride-N and prefetch depth effect characterization. A sequential strided microbenchmark is used to show the effect of stride-N and prefetch depth on performance and memory bandwidth. Threads are bound to contexts in an increasing order (the first four threads go to the first core, the next four ones go to the second core, and so on).                                                            |          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.6         | Values are normalized to the maximum value observed in each plot                                                                                                                                                                                                                                                                                                                                            | 61       |

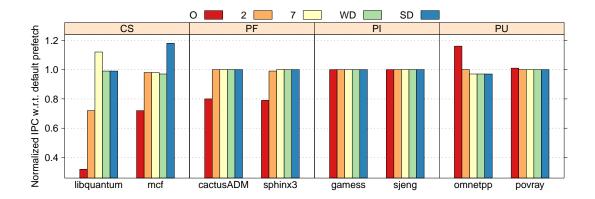

| 4.7         | threads go to the first core, the next four ones go to the second core, and so on). Values are normalized to the maximum value observed in each plot Effect of prefetching on performance for single-threaded runs. Multiple prefetch configurations are used in order to show the effect of each prefetch knob: depth (2-7), prefetch on stores (WD), and stride-N (SD)—refer to Table 4.1 for notation on | 62       |

| 4.8         | prefetch configurations                                                                                                                                                                                                                                                                                                                                                                                     | 64<br>66 |

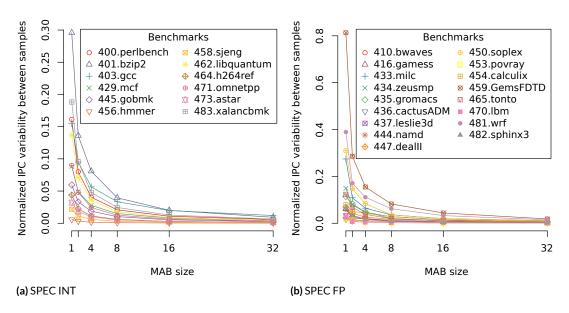

| <b>5.</b> I | Effect of changing the buffer size on inter-sample IPC variability. IPC variability (see                                                                                                                                                                                                                                                                                                                    |          |

| )·-         | Equation 5.1) is normalized to the average IPC for each benchmark                                                                                                                                                                                                                                                                                                                                           | 71       |

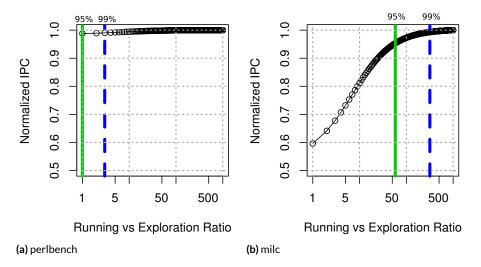

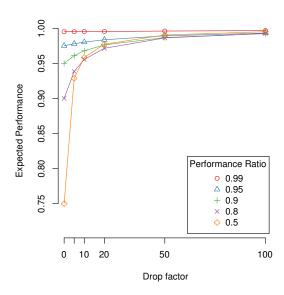

| 5.2         | Effect of exploration/running ratio on expected performance. Values are normalized to the maximum values observed for each workload.                                                                                                                                                                                                                                                                        | 74       |

| 5.3         | Effect of drop factor on expected performance. Values are normalized to the best possible performance.                                                                                                                                                                                                                                                                                                      | 76       |

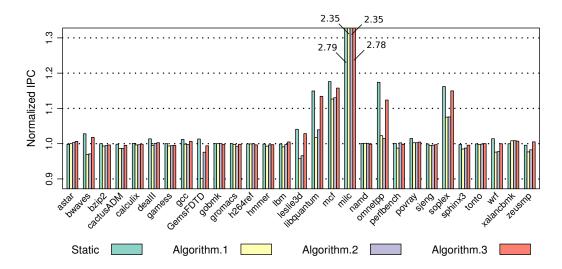

| 5.4         | Performance results for single-threaded workloads normalized to the ones obtained with the default prefetch configuration.                                                                                                                                                                                                                                                                                  | 79       |

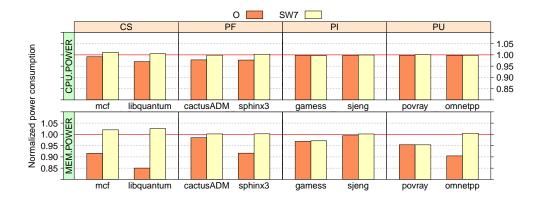

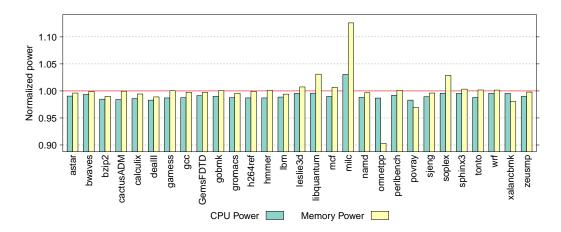

| 5-5         | CPU and memory power consumption results for single-threaded workloads using Algorithm 3. The values are normalized to the ones obtained with the default                                                                                                                                                                                                                                                   | ,,       |

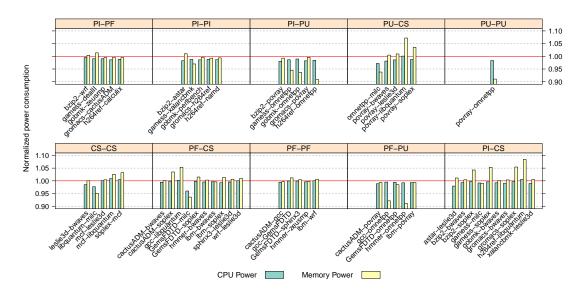

|             | prefetch configuration                                                                                                                                                                                                                                                                                                                                                                                      | 81       |

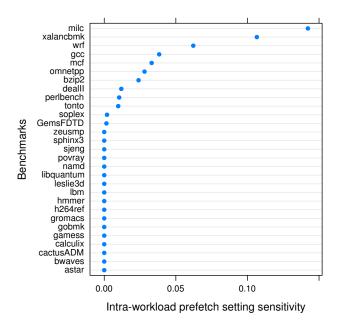

| 5.6         | Intra-workload prefetch setting sensitivity for all the SPEC CPU2006 benchmarks.                                                                                                                                                                                                                                                                                                                            | 83       |

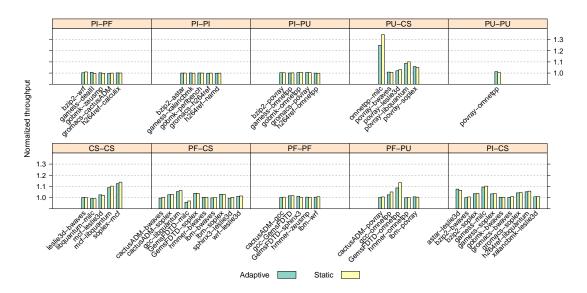

| 5.7         | Performance results for both the static and adaptive approaches for mixed-workloads. Each workload is composed of two different benchmarks from different classes (PI=prefinsensitive, PF=prefetch-friendly, PU=prefetch-unfriendly, CS=config-sensitive). Four copies of each benchmark are run at the same time. Results are normalized to the                                                            |          |

| _           | ones obtained with default prefetching.                                                                                                                                                                                                                                                                                                                                                                     | 84       |

| 5.8         | CPU and memory power consumption results for the adaptive approach for mixed-workloads (same pairs as in Figure 5.7). Values are normalized to the ones obtained                                                                                                                                                                                                                                            |          |

|             | with the default prefetch configuration.                                                                                                                                                                                                                                                                                                                                                                    | 86       |

| 5.9         | Performance and power characterization for SPECjbb2005 along its execution for eight warehouses (i.e., threads). Individual thread values are first aggregated, and                                                                                                                                                                                                                                         |          |

|             | then they are normalized, dividing them by the mean of all the samples. In this way                                                                                                                                                                                                                                                                                                                         |          |

|             | we keep the same ratio between both prefetch configurations as in the original values.                                                                                                                                                                                                                                                                                                                      | 88       |

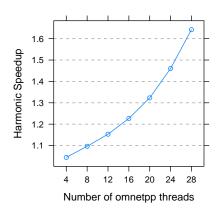

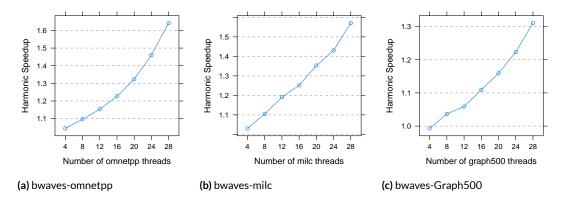

| 6.1          | Effect of bandwidth shifting on system performance when a prefetch-efficient benchmark (bwaves) and a prefetch-inefficient one (omnetpp) run together. The X axis                                                                                                                                                                            |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

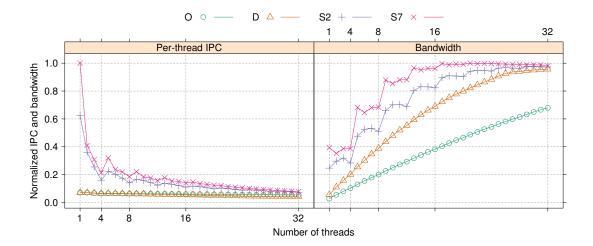

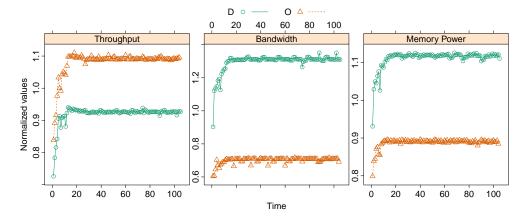

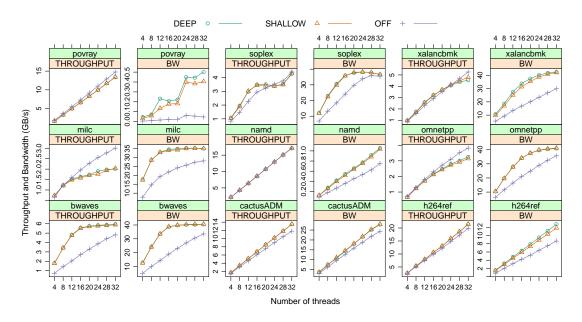

| 6.2          | shows the number of omnetpp threads $(x)$ . The number of bwaves threads is $32 - x$ . Throughput and memory bandwidth consumption characterization for a subset of the benchmarks. This subset is representative of all the benchmarks used in this chapter (i.e., the curves for the benchmarks not shown here match one of the benchmarks | 93  |

|              | marks shown in the figure)                                                                                                                                                                                                                                                                                                                   | 95  |

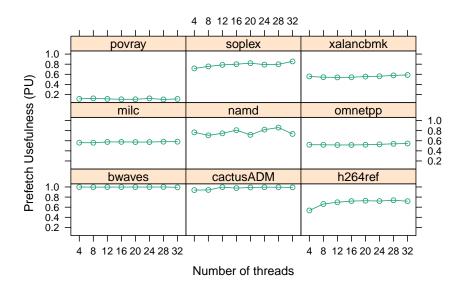

| 6.3          | Prefetch usefulness characterization for the benchmarks shown in Figure 6.2                                                                                                                                                                                                                                                                  | 99  |

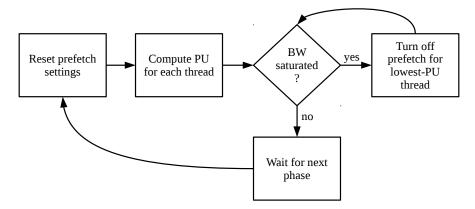

| 6.4          | Base bandwidth shifting algorithm                                                                                                                                                                                                                                                                                                            | 100 |

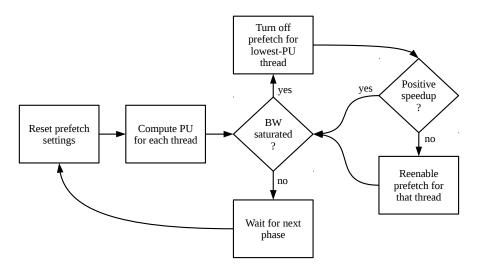

| 6.5          | Enhanced bandwidth shifting algorithm with a guard mechanism                                                                                                                                                                                                                                                                                 | IO2 |

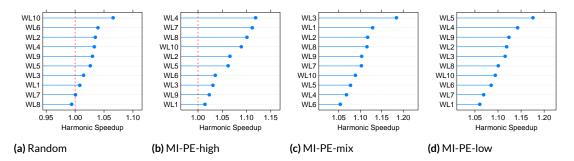

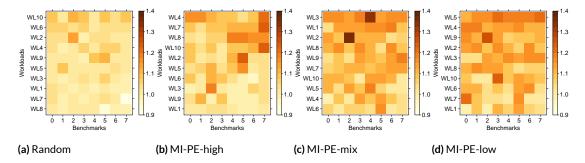

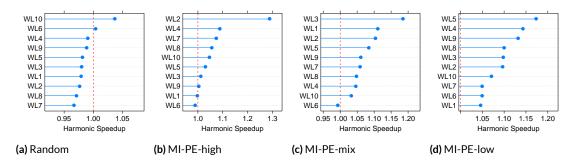

| 6.6          | Performance results for randomly-constructed workloads                                                                                                                                                                                                                                                                                       | 105 |

| 6.7          | Individual speedups for results in Figure 6.6. Each square in a plot displays the indi-                                                                                                                                                                                                                                                      |     |

|              | vidual speedup for a benchmark within a workload. The speedup degree is shown                                                                                                                                                                                                                                                                |     |

|              | with a color scale, going from light colors—lower speedup—to dark colors—higher                                                                                                                                                                                                                                                              |     |

|              | speedup                                                                                                                                                                                                                                                                                                                                      | 108 |

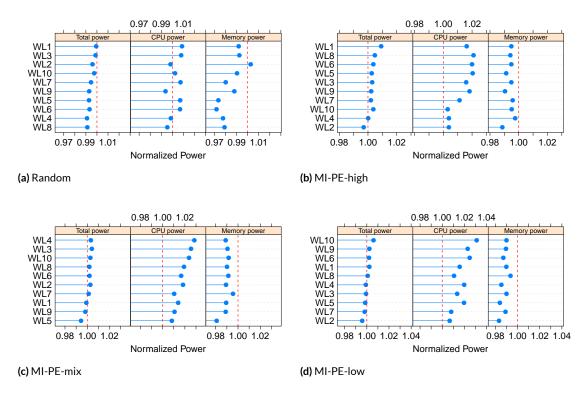

| 6.8          | Power consumption results for random workloads. Values are normalized to the                                                                                                                                                                                                                                                                 |     |

|              | case where the most aggressive prefetch setting is used for all the benchmarks                                                                                                                                                                                                                                                               | IIO |

| 6.9          | Performance results for an increasing number of copies of prefetch-inefficient bench-                                                                                                                                                                                                                                                        |     |

|              | marks.                                                                                                                                                                                                                                                                                                                                       | III |

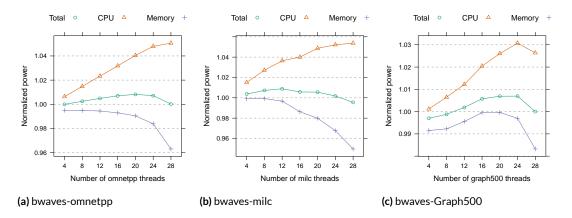

| 6.10         | Power consumption results for an increasing number of copies of prefetch-inefficient                                                                                                                                                                                                                                                         |     |

|              | benchmarks. Figure 6.9 shows the performance results for the same set of experiments.                                                                                                                                                                                                                                                        | II2 |

| 6.11         | Performance speedup resulting from using bandwidth shifting over adaptive prefetch-                                                                                                                                                                                                                                                          |     |

|              | ing                                                                                                                                                                                                                                                                                                                                          | 116 |

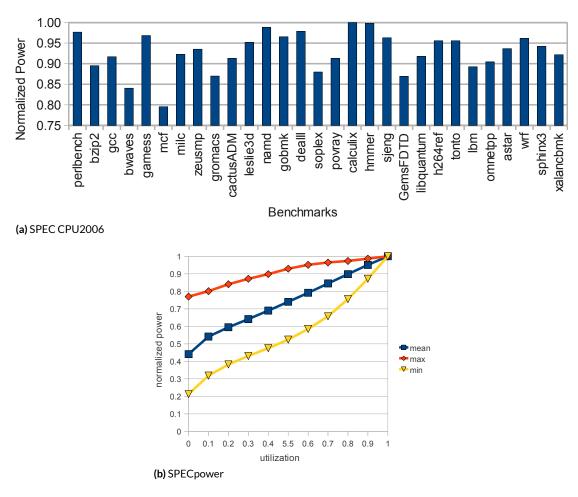

| 7 <b>.</b> I | Power consumption for SPEC CPU2006 benchmarks measured on an Intel quad-                                                                                                                                                                                                                                                                     |     |

|              | core system (a) and for the available results for SPECpower at several CPU utilization                                                                                                                                                                                                                                                       |     |

|              | levels (b). Max and min refer to the most- and least-consuming systems. Mean is                                                                                                                                                                                                                                                              |     |

|              | the average for all the submitted results                                                                                                                                                                                                                                                                                                    | I2I |

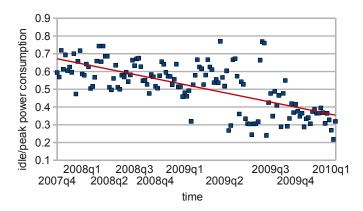

| 7.2          | Comparison of idle and peak power consumption for SPECpower submitted results.                                                                                                                                                                                                                                                               | 122 |

| 7.3          | Power consumption as a function of usage for a system submitted to the SPECpower                                                                                                                                                                                                                                                             |     |

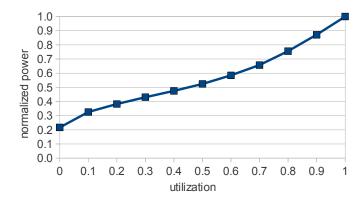

|              | webpage. The values are normalized to the consumption when the system is fully                                                                                                                                                                                                                                                               |     |

|              | utilized. The actual system is a Fujitsu PRIMERGY TX150 S7 server, based on a                                                                                                                                                                                                                                                                |     |

|              | quad-core Intel Xeon X3470 with 4GB of RAM. Its maximum power consump-                                                                                                                                                                                                                                                                       |     |

|              | tion is 112 watts when utilization is 100 percent.                                                                                                                                                                                                                                                                                           | 124 |

Dedicated to my wife and parents, for their constant support.

## Acknowledgments

Ever since I was a child, my parents strove to give me a good education. When I became interested in computers, they did not hesitate to buy me one—even if at that time computers were not precisely affordable. Later, they always encouraged me to continue studying, and supported me and my decisions. For all this, I am very grateful to them. Thanks to my brother for bringing joy and fun to my family, and for enduring my (failed) attempts to spark his interest in computers. Amusingly, he is now professionally dealing with computers.

I met my wife soon after starting my PhD. It was supposed to take just a few years, but it ended up taking quite a bit longer. I am thankful for her endless support and for cheering me up during difficult times. My son was born when I was close to finishing this thesis. His needs certainly delayed its end, but the joy he brought to my life simply outshines everything else. I want to thank him for not complaining too much when I needed to devote some time to complete this thesis.

I am indebted to my advisor, Francisco Cazorla, for his direction and encouragement since day one. His constructive criticism had a large influence on my development as a researcher. I am grateful for his trust and the freedom he allowed me to have during my studies. Roberto Gioiosa provided lots of insights and contributed to lively discussions that significantly helped my research. I thank him for his teachings. I want to show my gratitude to Mateo Valero for all his support and for being always there when difficulties appeared on the path.

During the internships I did at the IBM T. J. Watson Research Center, Pradip Bose and Alper Buyuktosunoglu guided my research as well. In a way, they became de facto advisors of my PhD studies. Pradip was always eager to help me no matter what the problem was. Beyond invaluable Alper's mentoring, my friendship with him certainly made my time there more enjoyable. It was great to watch together Barça winning so many titles. I thank Pradip and Alper for all their teachings and all the opportunities that they provided me. I also want to thank Francis P. O'Connell, Canturk Isci, Chen-yong Cher and Eren Kursun for their help while I was at IBM. During my stays at IBM, some friends made me feel closer to home. I am thankful to Ramon, Augusto, Valentin and Alex for it.

The path that led to my PhD studies started when I decided to enrol in the master program at the Computer Architecture Department at UPC. I am grateful to Marisa Gil, Nacho Navarro and Xavi Martorell for their support during that time. During my master studies I was a visitor student at INRIA. I thank Grigori Fursin for the opportunity. I also want to thank Isaac Gelado for all his help with my master thesis.

The C6 building is a special place for me. There, I met many people who made the process towards obtaining my PhD a much better experience. Many of them continue to be my friends to this day. I want to thank Zoraida, Carlos González, Àlex, Jordi, Abhishek, Carlos Boneti, Ramon, Lluís, Javi, Carlos and Isaac. I specially want to thank Carlos Boneti for all his help during the first stages of my

PhD in the CAOS group at Barcelona Supercomputing Center (BSC). I am grateful to all the other members of the CAOS team for their friendship.

Even if they do not really understand very much what my research is about, I am grateful to my friends Cesc and Sergi for being part of my life before, during and (hopefully) after my PhD. Soon, they will not be able to continue to make fun of my eternal student condition. I also want to thank my undergraduate friends: Alex, Juanan, Marc, Bea, Lou, Lucas and many more. The list is simply too long. During all these years I met other people who in one way or another helped me to finish my PhD. I am thankful to all of them.

Last but not the least, I thank all the institutions that supported me during my PhD studies: the Computer Architecture Department at the UPC, the HiPEAC Network of Excellence, the Barcelona Supercomputing Center and IBM Corporation. Specifically, this work has been partially sponsored by Defense Advanced Research Projects Agency (DARPA), Microsystems Technology Office (MTO), under contract no. HRooti-13-C-0022. The views expressed are those of the authors and do not reflect the official policy or position of the Department of Defense or the U.S. Government. This document is: Approved for Public Release, Distribution Unlimited. This work has also been partially supported by: the Spanish Ministry of Economy and Competitiveness (MINECO) under contracts TIN2012-3455 and TIN2015-65316-P; the Spanish Ministry of Science and Technology of Spain under contracts TIN-2007-60625 and JCI-2008-3688, and grants AP-2005-3776 and AP-2005-3318; and the HiPEAC Network of Excellence (IST-004408).

# 1

## Introduction

In the last two decades of the past century computer scientists relied on the scaling laws for CMOS devices to improve processor performance. Increases in clock speed drove processor performance during that time—processor clock frequency doubled approximately every 18 months. In the first half of the past decade, however, the slowdown of Dennard scaling made processor manufacturers to embrace the multicore design (Haensch et al. <sup>45</sup>, Horowitz et al. <sup>49</sup>). That move allowed processor performance to continue to increase by scaling up the number of cores instead of the clock rate. But it also introduced multiple challenges not present in single-threaded processors. Suddenly, traditional problems in the parallel computation realm such as thread coscheduling or resource sharing appeared in the context of a single multicore processor.

Multicore processors allow multiple applications to concurrently run on a single processor. This

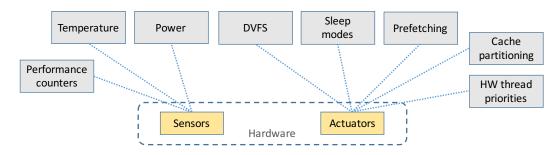

Figure 1.1: Examples of sensors and actuators exposed by hardware to software.

typically increases the utilization of the different units in the processor such as caches and functional units (assuming the processor supports multithreading too). But it also creates interferences between applications running on the system as they compete for the usage of shared resources. In order to alleviate these interferences—and therefore increase performance—several hardware techniques to adaptively manage resource sharing were developed over time (e.g., Tullsen et al. <sup>124</sup> studied several SMT fetch policies and Qureshi & Patt <sup>101</sup> presented a runtime mechanism to partition shared caches). Hardware-based adaptive policies are widely used in modern processors and they have proved successful at increasing performance or improving energy efficiency. Yet, in this thesis we show that there is room for improvement: adaptive policies can be further enhanced by relying on software and hardware cooperation. In this approach, hardware exposes sensors and actuators to software. A software layer uses the sensors to gather all the required information to implement smart adaptive resource-management policies. Such policies then use the actuators to adapt hardware resource sharing to the running workloads based on a certain metric of interest (e.g., performance, power consumption or quality of service).

#### I.I SENSORS AND ACTUATORS

Current processors contain multiple sensors that users can use for different purposes (Bowhill et al. <sup>18</sup>, Sinharoy et al. <sup>11</sup>). Some examples of such sensors can be seen in Figure 1.1. Performance counters (PMCs) are a set of special-purpose registers built into the performance monitoring unit (PMU) in a processor. The PMU can be programmed to measure a broad selection of microarchitectural events such as the number of instructions completed, cache misses or cycles that the processor was stalled because of different reasons. Measures obtained from PMCs can help performance monitoring, workload characterization and application tuning (Anderson et al. <sup>5</sup>, Zagha et al. <sup>132</sup>). They can also be helpful during the verification of a processor design to validate the exepcted system performance (Srinivas et al. <sup>117</sup>). Typically the OS exposes these special-purpose registers through some interface so that users can use them to measure system performance. Eranian <sup>37</sup> implemented such an interface in the form of a patch for the Linux kernel. Later, native support for PMCs was added to the Linux kernel (Carvalho de Melo <sup>22</sup>).

In addition to performance measurement, modern systems also allow users to obtain power consumption measurements. This information can then be used—potentially together with performance measurements—to build adaptive power management techniques. For instance, AMESTER (IBM Automated Measurements of Systems for Temperature and Energy Reporting software) is an in-house solution to monitor IBM POWER systems (Floyd et al. <sup>38</sup>). This software operates in an out-of-band manner, thus avoiding any performance overhead on the system being measured. Power consumption can be measured for different components (e.g., processor and memory). Other metrics such as temperature, voltage and frequency can also be obtained by reading the sensors in POWER systems.

The IBM POWER7 also includes a power proxy that estimates power consumption for each core based on PMC data (Floyd et al. <sup>38</sup>). Empirical results show that estimations obtained from the power proxy are close to the actual power consumption measurements. Some of the advantages of this ap-

proach are a finer sampling granularity—the interval can be as small as a few microseconds—as well as the ability to independently estimate power consumption for each core.

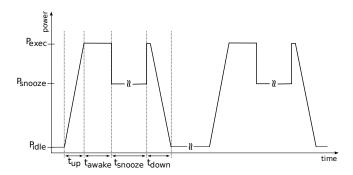

Processor designers also expose multiple actuators (or knobs) so that software can program and control the behavior of the processor (see Figure 1.1 for examples of such actuators). Dynamic frequency and voltage scaling (DVFS) (see Chandrakasan et al. <sup>24</sup>), core sleep modes (Floyd et al. <sup>38</sup>), hardware thread priorities (Boneti et al. <sup>16</sup>) or programmable prefetching engines (Sinharoy et al. <sup>11</sup>) are some examples of such knobs. Processors typically expose these actuators to the OS through special-purpose registers or privileged instructions.

### 1.2 Problem Statement

Support for controlling some of these actuators is built into current operating systems. For instance, Linux contains a mechanism to control processor frequency and voltage based on workload demands (Pallipadi & Starikovskiy <sup>97</sup>). In many cases, however, it is left to the end users to manually program these actuators. Because of that, quite often these actuators end up not being used. The reason is typically the costly workload characterization and optimization process necessary to select the optimal setting for a particular actuator. That process further complicates when users are not just running a small set of workloads, but their systems run a broad mix of workloads with different characteristics.

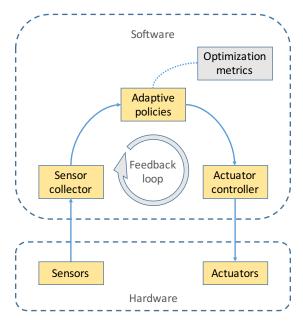

An adaptive mechanism that tunes hardware settings based on workload characteristics has the potential to increase system efficiency—either from a pure performance perspective or from an energy point of view. A block diagram of such a mechanism is depicted in Figure 1.2: the hardware exposes sensors and actuators to the software—typically to the OS or some firmware. The sensor collector reads the hardware sensors to obtain workload resource usage. Based on that information, a set of adaptive policies take resource allocation decisions. The specific decisions depend on the optimization metric of interest (e.g., performance, power consumption or quality-of-service). The actuator controller

Figure 1.2: Design overview for the proposed adaptive resource management system.

enforces such decisions by configuring the actuators accordingly.

The design of such an adaptive mechanism follows the principle of hardware-software codesign (Shalf et al. <sup>109</sup>), which proposes deeper collaboration between the hardware design and the application teams. At the core of this approach lies an iterative optimization loop where application design influences hardware design decisions, and vice versa. It also encourages workload autotuning to optimize applications for the specific platforms they run on. An adaptive resource management mechanism has the potential to optimize a system well beyond the time while the system is being designed—further optimizing the system once it has been delivered to its users.

In this thesis we explore the potential of leveraging hardware actuators to improve system efficiency. First we conduct a quantitative study that shows the benefits of a hardware/software cooperation approach. Then we narrow our focus to a given knob: hardware data prefetching. This choice is based on its potential performance impact—caches continue to be critical to system performance—and the

lack of adaptive solutions that tailor this knob. We present and evaluate different adaptive techniques that rely on hardware/software cooperation in order to intelligently control prefetching on a multicore system. The results show that our policies significantly increase performance and might reduce memory bandwidth and power consumption too—effectively making the system more efficient. Resource sharing occurs as well at other levels in a computing system. For instance, in large-scale computing facilities applications—and their users—might share a wide variety of resources, ranging from processor and memory to storage and networking. In this context we describe the design of an energy accounting system for large-scale computing facilities, and we analyze different forms of hardware/software cooperation required to build such a system.

### 1.3 Using Hardware Data Prefetching as an Actuator

Hardware data prefetching is a well-known technique to help alleviate the so-called *memory wall* problem (Wulf & McKee <sup>129</sup>) and hide memory latency. The technique relies on the fact that many applications exhibit spatial locality (i.e., once a given memory address is accessed, it is very likely that surrounding addresses will be accessed in the near future). Upon a data cache miss for a given address, the prefetcher may speculatively bring consecutive blocks corresponding to the addresses that the application is likely to access in the future. More complex prefetch implementations may detect access patterns to non-consecutive data (e.g., pointer-based list traversal).

Many general purpose server-class microprocessors in the field today rely on data prefetch engines to improve performance for memory-intensive workloads. Some prefetch engines allow users to change some of their parameters. In current commercial systems, however, the hardware prefetcher is typically enabled in a default configuration during system bring-up, and dynamic reconfiguration of the prefetch engine is not an autonomic feature. Nonetheless, commonly used prefetch algorithms—when applied in a fixed, non-adaptive mode—will not help performance in many cases. In fact, they

may actually degrade it due to useless bus bandwidth consumption and cache pollution. These problems exacerbate with current chip multiprocessors (CMP) and simultaneous multithreading (SMT) processors, which contain a significant number of cores (e.g., IBM POWER7 has 8 cores). And given the current trends future processors will have larger core counts. Executing many threads concurrently can potentially stress the bandwidth between processor and memory (Rogers et al. <sup>104</sup>). In this scenario, bandwidth can easily be saturated even without the presence of data prefetching. Enabling data prefetch may degrade system performance, since prefetches will fight with demand loads for the scarce available bandwidth.

In this thesis, we present multiple adaptive solutions that dynamically adapt the prefetching configuration to the running workloads. We first present a scheme that optimizes the prefetching setting for every thread running on a system. Then, we describe a system-wide solution that tackles the problem of managing global memory bandwidth by intelligently shifting prefetching bandwidth resources among applications. Our mechanisms successfully achieve significant performance improvements. In some cases they are also capable of reducing power consumption.

We use the IBM POWER7 (Sinharoy et al. <sup>III</sup>) as the vehicle for this study, since: (i) it represents a state-of-the-art high-end processor, with a mature data prefetch engine that has evolved significantly since the POWER3 time-frame; and (ii) it provides facilities for accurate measurement of performance and power metrics. POWER7 contains a programmable prefetch engine that is able to prefetch consecutive data blocks as well as those separated by a non-unit, constant stride. The processor system is provided to customers with a default prefetch setting that targets to improve performance for most applications. But users can manually override the default setting via the operating system, if needed. Users can specify some parameters such as the prefetch depth and whether strided prefetch and prefetch for store operations should be enabled or not. Changing the prefetch configuration affects workloads in different ways depending on the workload nature. This is the case even within the class of scientificengineering applications, which are generally amenable to data prefetch. While the optimal prefetch

setting—if known—can lead to a significant performance improvement, the corollary to this, as we show in this thesis, is that blindly setting a configuration may reduce performance and waste power consumption.

### 1.4 CONTRIBUTIONS

This dissertation makes the following contributions:

- I. We characterize the impact of multiple actuators on a real CMP/SMT platform. We also assess the potential of adaptive resource-management techniques that leverage hardware actuators.

- 2. We conduct an extensive characterization of the hardware data prefetching unit included in the IBM POWER7 processor. We analyze the impact of multiple configurations on both performance and power consumption. To that end, we use a combination of well-known benchmarks as well as microbenchmarks.

- 3. We present and evaluate a runtime-based adaptive prefetching mechanism capable of improving performance via dynamically setting the optimal prefetching configuration, without the need for a priori profile information. Our adaptive scheme increases performance up to 2.7X and 1.3X compared to the default prefetching configuration for single-threaded and multiprogrammed workloads, respectively. Our mechanism is able to reduce memory power consumption in some cases. We also study the implementation of such an adaptive prefetching scheme within the OS kernel. After implementing our adaptive mechanism into the Linux kernel, we have observed similar performance improvements to those obtained by the userspace implementation.

- 4. We provide a motivation for prefetch-based bandwidth shifting and a characterization of the performance-bandwidth trade-off for multiple benchmarks. We introduce a metric that esti-

mates prefetch usefulness for a given thread based solely on performance counters commonly available in current processors. A novel bandwidth shifting mechanism is capable of significantly improving system performance by taking bandwidth away from benchmarks that do not use prefetching in an efficient way, and giving it to prefetch-efficient benchmarks. The mechanism does not require any hardware support, and it is able to obtain up to 18.5% speedup (10-11% on average). We also study the impact of bandwidth shifting in extreme cases where one benchmark is highly prefetch-efficient and the other uses prefetching inefficiently. Our results show that bandwidth shifting achieves much larger speedups (>1.6X). We also evaluate the impact of the bandwidth shifting mechanism on power consumption.

5. In the last chapter we look beyond the single-system case. We explore how sensors and actuators can be used to accurately track per-task energy consumption in large-scale computing facilities.

We study the different trade-offs inherent in the design of an energy accounting solution. We also show how such approach can be beneficial for both users and owners of the facility.

During this thesis we ported AMESTER—an internal power measurement tool at IBM (see Floyd et al. <sup>38</sup>, Lefurgy et al. <sup>70</sup>)—to C++. By doing so, we could extend the framework where our adaptive policies are implemented with support for power measurement. In addition to that, members of the System and Technology Group (STG) at IBM collaborated in the research conducted during this thesis. We believe the results from our research have provided valuable feedback to IBM's product group.

### 1.5 List of Publications

The different parts in this thesis have been published in international conferences or technical journals. The following list contains the details for the publications that spawned from this thesis.

• Jiménez, V., Cazorla, F. J., Gioiosa, R., Valero, M., Boneti, C., Kursun, E., Cher, C., Isci, C., Buyuktosunoglu, A., & Bose, P. (2010). Power and thermal characterization of POWER6

- system. In Proceedings of the 19th International Conference on Parallel Architectures and Compilation Techniques, PACT (pp. 7–18)

- Jiménez, V., Cazorla, F. J., Gioiosa, R., Valero, M., Boneti, C., Kursun, E., Cher, C., Isci, C., Buyuktosunoglu, A., & Bose, P. (2011b). Characterizing power and temperature behavior of power6-based system. *IEEE Journal Emerging and Selected Topics in Circuits and Systems, JETCAS*, 1(3), 228–241

- Jiménez, V., Gioiosa, R., Cazorla, F. J., Buyuktosunoglu, A., Bose, P., & O'Connell, F. P. (2012).

Making Data Prefetch Smarter: Adaptive Prefetching on POWER7. In *Proceedings of the 21st International Conference on Parallel Architectures and Compilation Techniques*, PACT (pp. 137–146).: ACM. Best Paper Award Nominee.

- Jiménez, V., Cazorla, F. J., Gioiosa, R., Buyuktosunoglu, A., Bose, P., O'Connell, F. P., & Mealey, B. G. (2014). Adaptive prefetching on POWER7: improving performance and power consumption. ACM Transactions on Parallel Computing, TOPC, I(I), 4

- Jiménez, V., Buyuktosunoglu, A., Bose, P., O'Connell, F. P., Cazorla, F. J., & Valero, M. (2015). Increasing multicore system efficiency through intelligent bandwidth shifting. In *Proceedings* of the 21st International Symposium on High Performance Computer Architecture, HPCA (pp. 39–50).: IEEE

- Jiménez, V., Cazorla, F. J., Gioiosa, R., Kursun, E., Isci, C., Buyuktosunoglu, A., Bose, P., & Valero, M. (2011a). Energy-Aware Accounting and Billing in Large-Scale Computing Facilities.

IEEE Micro, 31(3), 60-71

Chapter 7 in this thesis orginated a new line of research. The following two publications expand some of contents in this thesis.

- Liu, Q., Moretó, M., Jiménez, V., Abella, J., Cazorla, F. J., & Valero, M. (2013). Hardware support for accurate per-task energy metering in multicore systems. ACM Transactions on Architecture and Code Optimization, TACO, 10(4), 34

- Liu, Q., Jiménez, V., Moretó, M., Abella, J., Cazorla, F. J., & Valero, M. (2014a). Per-task energy accounting in computing systems. Computer Architecture Letters, 13(2), 85–88

### 1.6 Dissertation Organization

This dissertation is divided into eight different chapters. Chapter 2 describes the related work relevant to this thesis. Chapter 3 provides a motivation showing the impact of hardware actuators. Chapter 4 describes and characterizes the platforms used in this thesis. It also contains the experimental methodology. Chapter 5 presents an adaptive prefetching mechanism to improve single-threaded performance. Chapter 6 shows a system-wide solution that shifts prefetching bandwidth across workloads. Chapter 7 focuses on resource sharing for large-scale computing facilities. It describes the tradeoffs in the design of such a system, and analyzes different sensors and actuators that can be used. Finally, Chapter 8 provides the main conclusions of this thesis and directions for future work.

## 2 Related Work

A significant amount of research on adaptive solutions for resource management has been conducted over the years. As computing systems continue to share resources at finer granularities, more opportunities for such solutions appeared. Adaptive resource management can be entirely implemented in hardware or they might rely on hardware/software cooperation. We provide a detailed overview of the related work in the field of adaptive resource management. Moreover, as this thesis presents two adaptive solutions for controlling the prefetching engine, we also include a list of relevant prior work on data prefetching.

### 2.1 HARDWARE SOLUTIONS FOR RESOURCE MANAGEMENT

Multicore processors typically share the last level cache among the different cores. Therefore, applications running on such processors compete for space in the last level cache. Suh et al. <sup>121</sup> present a dynamic cache partitioning scheme. Their solution adds extra hardware but the control algorithm is actually implemented at the operating system level. Qureshi & Patt <sup>101</sup> enhance the previous work by eliminating any effect on the partitioning algorithm due to interferences between the actual applications sharing the cache. Moreto et al. <sup>87</sup> present a cache partitioning technique but they focus on achieving QoS for the co-running applications. Parallel applications running on a multicore processor need to maintain cache coherency among the different cores. Cache coherency traffic competes for the available bandwidth in the interconnection bus. Martin et al. <sup>82</sup> use an adaptive bandwidth snooping protocol. Depending on the number of processors and the running workloads, the protocol selects a different policy to keep cache coherency, effectively optimizing the usage of the interconnection bus.

If a processor supports multithreading, resource sharing occurs in the processor's pipeline too. Threads running on a particular core will share multiple resources such as the instruction fetch buffers, issue queues or reorder buffer. Tullsen et al. <sup>124</sup> present different instruction fetch policies that try to maximize the usage of resources in the pipeline. Cazorla et al. <sup>23</sup>, Choi & Yeung <sup>26</sup> show fetch policies aiming to increase throughput or provide quality of service (QoS).

### 2.2 Sampling-Based Online Adaptive Systems

Offline adaptive systems typically rely on application profiling to optimize future executions of a particular application. This approach allows for the usage of computationally expensive optimization schemes, but its utility is limited when different inputs are used or when the application mix running on a system changes over time. Online adaptive systems, on the other hand, monitor running applications and make optimization decisions while the applications are running. Many online adaptive

systems use a two-step approach. During the first step sensors are read to obtain measurements for the metric of interest (e.g., performance, power consumption or temperature). Then, in the second step an optimization decision is made based on the information obtained in the first step.

Isci et al. <sup>55</sup>, Sarikaya et al. <sup>106</sup> present solutions that uses performance monitoring counters (PMCs) to predict application phases. These solutions then use phase information to guide dynamic power management schemes. Tikir & Hollingsworth <sup>123</sup> develop an online page migration scheme that characterizes the memory access pattern of an application, and then moves pages to memory local to the processor that accesses them most frequently. Petrica et al. <sup>98</sup> present a runtime that optimizes system's efficiency by enabling and disabling parts of the processor's pipeline in a fine-grain approach.

Lu et al. <sup>79</sup> relies on performance monitoring counters and dynamic instrumentation to insert prefetching instructions in a running application. Adl-Tabatabai et al. <sup>3</sup> present a similar system for JIT-based runtimes. Schneider et al. <sup>108</sup> use PMCs to optimize object spatial locality in a generational garbage collector.

### 2.3 Solutions Exposing Custom Sensors and Actuators to the Software

Most current, general-purpose processors expose different sensors (or counters) to the operating system or userspace. For instance, performance monitoring counters allow software to obtain a significant amount of information related to applications' usage of the different subunits in the processor. This information can be used to analyze the behavior of the applications or find their performance bottlenecks. Processors and other components in a computer system may expose power consumption and temperature sensors too. Processors can also expose actuators so that the operating system or the end user are able to alter the behavior of the processor. Two commonly used actuators let the processor's frequency and sleep states to be controlled.

Prior research on resource management has proposed exposing new sensors or actuators that enable

the implementation of more complex adaptive schemes. Zhou et al. 133 present a memory allocation adaptive solution that uses the page miss ratio curve to guide its decisions. Their proposal adds extra hardware to collect the page miss ratio curve and it exposes that information through a new sensor that the operating system has access to. Suh et al. 120 utilizes a set of novel hardware counters that expose information about the isolated miss-ratio for each process running on the system. This information can be used to guide scheduling decisions or to dynamically partition the cache. Merten et al. 84 propose sensors that expose applications' hot spots to the operating system. An adaptive scheme could use these sensors to optimize the performance in the hot spots. Yasin 131 adds extra events to the performance monitoring unit of a processor to accurately find the bottlenecks of an application running on that processor. Nagarajan & Gupta 91 expose interprocessor dependence information and build a software solution that efficiently detects mispeculation and improves application reliability. Boneti et al. 16 implement and characterize a kernel module to access the hardware thread prioritization mechanism present in the IBM POWER5 processor. A follow-up work, presents an adaptive solution to balance parallel applications using the thread prioritization mechanism. <sup>17</sup> Bhattacharjee & Martonosi <sup>14</sup> present a sensor that exposes thread criticality predictions to the operating system. Using the measurements obtained from that sensor they present an adaptive scheme to reduce thread imbalance as well as another scheme to improve energy efficiency in barrier-based parallel applications.

### 2.4 THREAD MAPPING

Although thread mapping might apparently not look like a traditional actuator—in the sense of a knob that can be tweaked—the way threads are mapped to cores or hardware contexts has a large impact on the exact resource sharing among these threads. For instance, the interference level between threads sharing a last-level cache might be very different depending on the particular mapping that the operating system chooses. Also, threads running on multithreaded processors such as the IBM

POWER7 may have different access to pipeline's resources depending on the multithreading level being used. III Therefore, thread mapping might affect performance in this case too.

Radojković et al. <sup>102</sup> use a statistical approach based on extreme value theory to optimally assign tasks in multithreaded processors. Tang et al. <sup>122</sup> study the impact of thread-to-core mappings in terms of cache and bus bandwidth sharing. They also present an adaptive approach to thread mapping in a data center, resulting in significant performance gains. Lo et al. <sup>78</sup> show an adaptive solution to safely colocate latency-sensitive applications on a data center.

### 2.5 GENERAL PREFETCHING

There is a significant record of past research in data prefetch (e.g., Baer & Chen <sup>7</sup>, Fu et al. <sup>41</sup>, Jouppi <sup>63</sup>, Palacharla & Kessler <sup>95</sup>, Smith <sup>113</sup>). Most of the initial proposals were based on sequential prefetchers, which rely on applications exhibiting spatial locality. Although sequential prefetchers work effectively in many cases, there are applications with non-sequential data access patterns that do not benefit from sequential prefetching. This has motivated the research on more complex prefetchers that try to capture the non-sequential nature of these applications. Cooksey et al. <sup>27</sup>, Ebrahimi et al. <sup>34</sup>, Roth et al. <sup>105</sup>, Wang et al. <sup>127</sup>, Yang & Lebeck <sup>130</sup> study prefetch techniques targeting pointer-based applications. Joseph & Grunwald <sup>62</sup> study Markov-based prefetchers and present solutions to limit the bandwidth devoted to prefetching. Solihin et al. <sup>114</sup> use a user-level memory thread in order to prefetch data, delivering significant speedups even for applications with irregular accesses. Emma et al. <sup>35</sup>, Srinivasan et al. <sup>18</sup> present limit studies and prefetch analytical models.

Most general-purpose processors contain a prefetch engine based on some of these works. Our solution is orthogonal to them since their objective is to improve the accuracy of the algorithms implemented in a single prefetcher.

### 2.5.1 FILTERING USELESS PREFETCHES

Several works that attempt to reduce the number of useless prefetches sent to memory have been presented in the past (Charney & Puzak <sup>25</sup>, Lee et al. <sup>69</sup>, Lin et al. <sup>73</sup>, Mowry et al. <sup>88</sup>, Mutlu et al. <sup>90</sup>, Zhuang & Lee <sup>134</sup>). Even when these filtering techniques are used, applications still have different prefetchefficiency degrees. Therefore, our bandwidth shifting mechanism can be complementary used to further improve performance.

### 2.6 Local Adaptive Prefetching

Using a prefetch engine that implements a fixed algorithm is suboptimal since the prefetch-efficiency of applications may change during the different phases of execution. Several adaptive solutions that attempt to dynamically change the prefetch configuration exist in prior research (Dahlgren et al. <sup>28</sup>, <sup>29</sup>, Nesbit et al. <sup>94</sup>, Srinath et al. <sup>116</sup>). The objective of these solutions, however, is not to maximize global system performance. They are either designed for single-threaded processors or they only attempt to locally increase performance of individual cores. Therefore, while they may improve performance for a particular core, system performance may decrease. On the contrary, in this thesis we present a solution that maintains a global system view and increases performance for the whole system.

### 2.7 CMP-Aware Adaptive Prefetching

With the advent of CMP processors, interaction between threads must be taken into account when designing a prefetch system. Ebrahimi et al. <sup>33,32</sup> study the effect of thread-interaction on prefetch, and propose techniques to design prefetch systems that improve throughput or fairness. Despite the similarities to the solutions presented in this thesis, their solution requires costly extra hardware—amounting to multiple kilobytes—whereas ours work with most modern general-purpose processors.

Liu & Solihin <sup>74</sup> study the impact of prefetching and bandwidth partitioning in CMPs. But their work only presents an analytical model and no mechanism to exploit their observations is included.

### 2.8 Adaptive Prefetching Solutions for Real Systems

Although there is a significant number of studies on prefetching based on simulators, there are very few works that deal with hardware-based measurement and characterization. Wu & Martonosi <sup>128</sup> characterize the prefetcher of an Intel Nehalem processor and provide a simple algorithm to dynamically control whether to turn the prefetcher on or off. Their study, however, is solely oriented towards reducing intra-application cache interference without taking actual system performance into consideration. Liao et al. <sup>72</sup> construct a machine learning model that dynamically modifies the prefetch configuration of the machines in a data center (based on Intel Core2 processors). Although they improve performance for some applications by enabling/disabling prefetch, their work only focuses on how to improve the performance for a single application without taking into account the performance/bandwidth trade-offs that appear when multiple applications are executed concurrently.

### 2.9 Per-Task Energy Accounting

Large-scale computing facilities are vast infrastructures with high operation costs. Any possible optimization that improves their efficiency can translate into a considerable cost reduction. Several proposals focus on improving data centers' energy efficiency (Moreira & Karidis 86, Karidis et al. 66, Meisner et al. 83). Many of these proposals advocate for energy-proportional systems, in which the benefits of energy accounting are higher than in current systems.

Several of these works focus on either reducing power consumption when the system is idle or improving efficiency by consolidating more virtual machines in the same hardware. To this end, Moreira & Karidis <sup>86</sup> leverage workload heterogeneity to better schedule the workloads onto the computing

resources, thus increasing resource usage. Nathuji & Schwan <sup>92</sup> propose a mechanism to connect the low-power mechanisms available in the hardware with the power management requests and hints made by an operating system running within a virtual machine.

Accounting users, tasks and virtual machines for the energy they actually consume is orthogonal to the aforementioned proposals. On the one hand, the potential to adapt to the workloads' heterogeneity increases with per-task energy accounting. On the other hand, energy accounting brings benefits by itself as shown earlier.

Kansal et al. <sup>65</sup> present initial steps for an accurate energy-accounting mechanism. Their goal is to develop a better power-capping mechanism in the presence of multiple virtual machines on one node. However, more research is necessary to obtain a more accurate mechanism for use not only for power consumption estimation, but for billing users according to their energy consumption as well. For instance, their proposal uses simple ways to split static power consumption and power consumption caused by virtual machine interferences, among virtual machines.

To obtain better accuracy, hardware and operating system support is necessary. Bertran et al. <sup>13</sup> present an energy-accounting system for small-sized systems. Our work focus on large-scale computing facilities, where other types of solutions are likely needed.

# 3

## Motivation: Impact of Hardware Actuators

Workloads running on a multicore processor compete for different shared resources. Due to workload variability, the usage of these resources might be significantly unbalanced. This fact has important implications on performance, power consumption and energy efficieny. In this chapter we characterize these implications and we analyze the potential to improve system efficiency of solutions based on hardware/software cooperation.

As process technologies advance, the trend is to have more cores per chip, where each core can further increase the amount of concurrent threads via SMT. This has been the case for processors such as the IBM pSeries (POWER6 68, POWER7 III, POWER8 II2) and the Intel Xeon. I8 While CMP processors provide better performance per watt ratios than monolithic architectures, the power dissipation continues to be a key performance limiter also for multithreaded architectures. Consequently, power

and thermal characteristics of processors are one of the primary design constraints, and motivate an active research area.