ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# Analysis of the Resistive Switching phenomenon in MOS devices for memory and logic applications

Ph. D. Thesis written by Marcos Maestro Izquierdo

> Under the supervision of Rosana Rodríguez Martínez

Reliability of Electron device and Circuits

The undersigned, Dra, **Rosana Rodríguez Martínez**, professor of the Electronic Engineering Department (Engineering School) of the *Universitat Autònoma de Barcelona*,

### **CERTIFY:**

That the thesis entitled "Analysis of the Resistive Switching phenomenon in MOS devices for memory and logic applications" has been written by the Ph. D. candidate Marcos Maestro Izquierdo under her supervision, in fulfillment of the requirements for the PhD degree of Electrical and Telecommunication Engineering.

And hereby to acknowledge the above, sign the present.

Rosana Rodríguez Martínez

Marcos Maestro Izquierdo

"... The show must go on Inside my heart is breaking My make-up may be flaking But my smile still stays on..."

The show must go on, Queen

## *ACKNOWLEDGEMENTS*

During last years, there have been many people that have made possible this thesis has been performed thanks to their support, help and encouragement. Thus, I would like to show my gratitude to all of them.

First of all, I would like to thank my supervisor *Rosana Rodríguez* for guiding me during these years, for being always accessible for all the issues and doubts I may have had.

I would also like to express my gratitude to Javier Martín for his very helpful advices during the large hours of laboratory and his patience on understanding my doubts and to Montserrat Nafría for giving me the opportunity of developing all the thesis work within the research group she heads. I also extend my acknowledgments to rest of the colleagues and friends from the REDEC group (Carlos Couso, Miquel Moras, Albert Crespo, Javi Díaz, Quian Wu, Sergi Claramunt, Marc Porti and Xavier Aymerich), from the office (Fran, Oscar, Alberto and Cristian) and from the whole Electronic Engineering Department for these wonderful four years. Thanks to all them, my background of knowledge, experience and, besides, great moments has growth hugely.

I want to extend my gratitude to *Daniele Ielmini* who gave me the opportunity to work within his research group. During that period, I learnt a lot from his knowledge and from the experience of their whole group. Particular thanks to *Alessandro*, *Elia*, *Giacomo*, *Mario and Roberto* for the large sessions of "measuring" and for make me the stay so pleasant. In this particular thanks, I would like to include to *Erika* and *Lorenzo*, two friends, who embrace me from the first moment and let me take part in their very special moments.

Obviously, I cannot forget all my family because this work is also their merit. Specially, *Nemesio*, *Mariangeles* and *Eva* because despite the hundreds of kilometers that separate us, you are always close to me with your support, your advices, your love, your confidences... in a few words, thanks for the luck I have of you being part of my life. I do not want forget my "enanos" (*Vega y Esteban*) who are like siblings to me and all the members of my family that are by my side all the time.

Eventually, and despite all, thanks *Rebeca* for all the support during last years, a part of this work is also merit of her.

# A GRADECIMIENTOS

Durante estos últimos años, ha sido mucha la gente que ha hecho posible la consecución de esta tesis gracias a su apoyo, ayuda y ánimos. Por ello, me gustaría mostrar mi gratitud a todos ellos.

En primer lugar, me gustaría dar las gracias a mi tutora, *Rosana Rodríguez*, por guiarme durante estos años, por estar siempre disponible para solucionar cada uno de los problemas y dudas que he podido tener.

También me gustaría expresar mi gratitud a Javier Martín por sus útiles consejos durante las largas horas de laboratorio y por su paciencia a la hora de resolver mis dudas. Extender mi gratitud, a Montserrat Nafría por darme la oportunidad de poder desarrollar todo el trabajo de la tesis dentro del grupo de investigación que ella coordina. Por supuesto, quiero agradecer enormemente a todos mis compañeros y amigos del grupo REDEC (Carlos Couso, Miquel Moras, Albert Crespo, Javi Díaz, Quian Wu, Sergi Claramunt, Marc Porti and Xavier Aymerich), del despacho (Fran, Oscar, Alberto and Cristian) y del departamento de ingeniería electrónica al completo por estos maravillosos cuatro años. Gracias a todos ellos por hacer que mi conocimiento, mi experiencia y sobre todo mi mochila de grandes momentos hayan crecido de esta manera. Espero que, de una manera u otra, sigáis brindándome todo ello.

Vorrei estendere la mia gratitudine a Daniele Ielmini che mi ha dato l'opportunità di lavorare nel suo gruppo di ricerca. Durante questo periodo, ho imparato molto della sua conoscenza e dell'esperienza di tutto il gruppo. Grazie in particolare a Alessandro, Elia, Giacomo, Mario e Roberto per lungue ore di "measuring" e per rendermi il soggiorno così piacevole. In questo particolare ringraziamento, vorrei includere a Erika e Lorenzo, due amici che mi hanno abbracciato dal primo momento e mi hanno permesso di partecipare ai loro momenti più speciali.

Obviamente no puedo olvidarme de toda mi familia porque todo este trabajo también es mérito suyo. En especial mi familia más cercana, Nemesio, Mariangeles y Eva porque a pesar de la distancia que nos separa siempre estáis cerca de mí dándome vuestro apoyo, consejos, amor, compartiendo confidencias... en pocas palabras mil gracias por la suerte que tengo de que seáis parte de mi vida. No olvidarme de mis "enanos" (Vega y Esteban) a lo que considero como mis hermanos y todos los miembros de mi familia que están ahí para todo.

Finalmente, y a pesar de todo lo ocurrido, agradecer a *Rebeca* todo su apoyo durante estos últimos años ya que parte de este trabajo también es mérito suyo.

# CONTENTS

| CONTEN    | TTS                                               |    |

|-----------|---------------------------------------------------|----|

| ACRONY    | VMS                                               | 5  |

| PREFAC    | $E \ldots \ldots E$                               | 7  |

| 1. INTRO  | ODUCTION                                          | 19 |

| 1.1. Resi | STIVE SWITCHING PHENOMENON                        | 20 |

| 1.1.1.    | What is Resistive Switching?                      | 20 |

| 1.1.2.    | Operation modes                                   | 24 |

| 1.1.2     | 2.1. Bipolar resistive switching                  | 25 |

| 1.1.3.    | Physical RS mechanisms                            | 27 |

| 1.1.3     | 3.1. Valence change                               | 29 |

| 1.2. Reli | ABILITY ISSUES IN RESISTIVE SWITCHING             | 32 |

| 1.2.1.    | Variability                                       | 32 |

| 1.2.2.    | Retention                                         | 34 |

| 1.2.3.    | Endurance                                         | 35 |

| 1.2.4.    | Random Telegraph Noise                            | 36 |

| 1.3. App  | LICATIONS OF RESISTIVE SWITCHING PHENOMENON       | 41 |

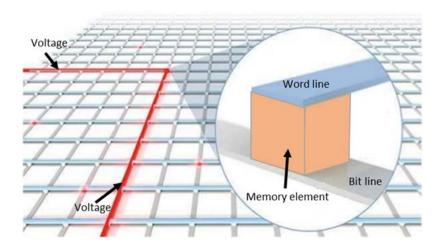

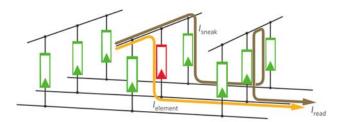

| 1.3.1.    | Memory applications                               | 41 |

| 1.3.2.    | Digital applications                              | 44 |

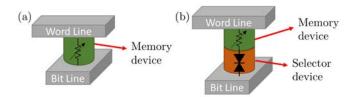

| 1.3.3.    | As selector element                               | 46 |

| 1.3.4.    | Neuromorphic applications                         | 49 |

| 1.3.5.    | Stochastic computing and security                 | 51 |

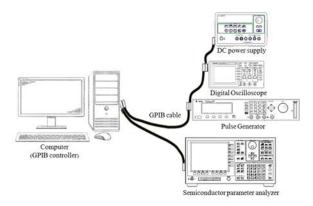

| 1.4. Expi | ERIMENTAL AND ANALYSIS EQUIPMENT                  | 52 |

| 1.4.1.    | Experimental equipment                            | 52 |

| 1.4.2.    | Instrument control by GPIB communication          | 53 |

| 1.4.3.    | Software for instrument control and data analysis | 54 |

| 2. ANAL      | YSIS OF RESISTIVE SWITCHING IN MOSFET                                  | 57  |

|--------------|------------------------------------------------------------------------|-----|

| 2.1. MC      | SFET SAMPLES DESCRIPTION                                               | 58  |

| 2.2. RES     | SISTIVE SWITCHING CHARACTERIZATION                                     | 58  |

| 2.2.1.       | Device operation under bipolar RS                                      | 59  |

| 2.2.2.       | Device operation under unipolar RS                                     | 61  |

| 2.3. FIL.    | AMENT LOCATION IN MOSFET                                               | 63  |

| 2.3.1.       | Control of filament location                                           | 64  |

| 2.4. ME      | THOD TO DISCRIMINATE GATE CURRENT CONTRIBUTIONS                        | 67  |

| 2.4.1.       | Experimental Procedure                                                 | 68  |

| 2.4.2.       | Methods to separate gate current components based on filament location | 69  |

| •            | 2.1. Filament located close to the source                              |     |

| 2.5. Con     | CLUSIONS                                                               | 75  |

| 3. ANAL      | YSIS OF RESISTIVE SWITCHING IN MEMRISTORS                              | 77  |

| 3.1. Mem     | RISTORS SAMPLES AND MEASUREMENT SETUP DESCRIPTION                      | 78  |

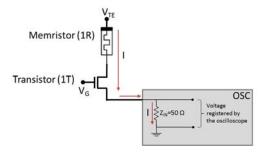

| 3.2. Ana     | LYSIS OF SET AND RESET MECHANISMS UNDER FAST VOLTAGE RAMPS             | 81  |

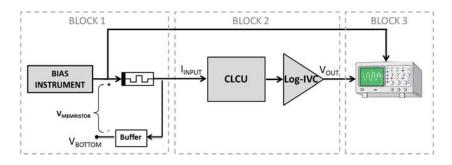

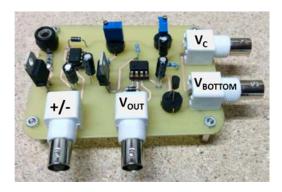

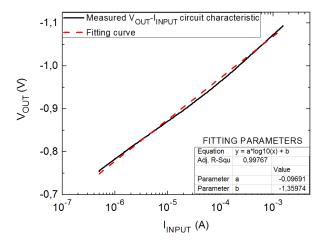

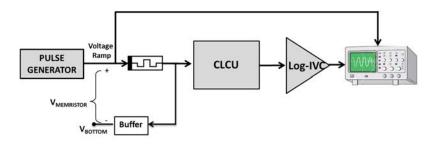

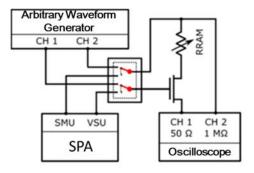

| 3.2.1.       | Experimental setup                                                     | 82  |

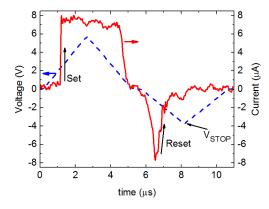

| 3.2.2.       | Measurement procedure                                                  | 84  |

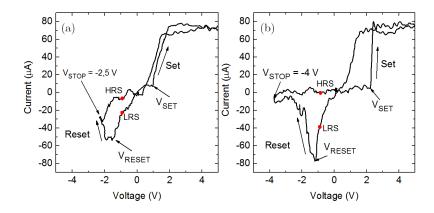

| 3.2.3.       | RS parameters analysis                                                 | 85  |

| 3.3. High    | RESOLUTION RTN CHARACTERIZATION PROCEDURE                              | 88  |

| 3.3.1.       | Measurement and data analysis procedure                                | 88  |

| 3.3.2.       | Applicability of the high-resolution method                            | 90  |

| 3.4. Con     | CLUSIONS                                                               | 94  |

| $4. SIO_X-E$ | SASED MEMRISTORS AS MEMORY/SELECTOR DEVICES                            | 97  |

| 4.1. Mem     | ORY AND SELECTOR DEVICES                                               | 98  |

| 4.2. TI/S    | $IO_X$ MEMORY CHARACTERISTICS                                          | 100 |

| 4.2.1.       | DC characteristics                                                     | 101 |

| 100          | Pulsed characteristics                                                 | 101 |

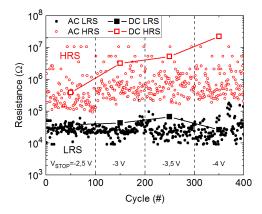

| 4.2.3.    | Endurance characteristics                                                    | 108     |

|-----------|------------------------------------------------------------------------------|---------|

| 4.2.4.    | Retention characteristics                                                    | 110     |

| 4.3. AG/S | $SiO_X$ selector device characteristics                                      | 111     |

| 4.3.1.    | DC characteristics                                                           | 111     |

| 4.3.2.    | Pulsed characteristics and retention time                                    | 114     |

| 4.4. Mem  | ORY-SELECTOR ONE DEVICE                                                      | 117     |

| 4.5. CON  | CLUSIONS                                                                     | 118     |

| 5. MEMR   | RISTORS IN LOGIC CIRCUIT APPLICATIONS                                        | 121     |

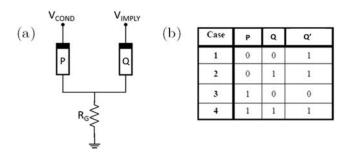

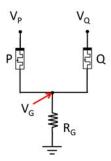

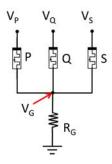

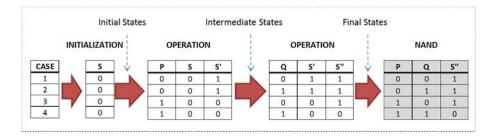

| 5.1. Desc | CRIPTION OF IMPLY AND IMPLY-BASED NAND GATES                                 | 122     |

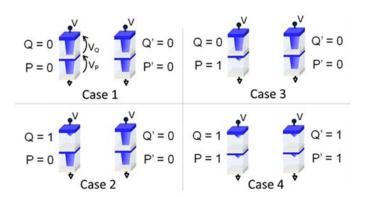

| 5.1.1.    | IMPLY gate                                                                   | 122     |

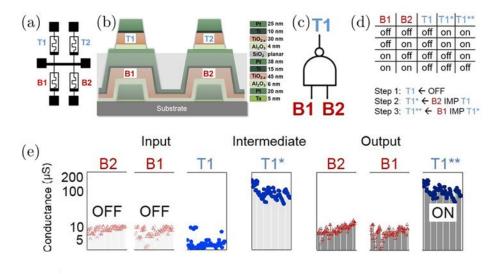

| 5.1.2.    | IMPLY-based NAND gate                                                        | 123     |

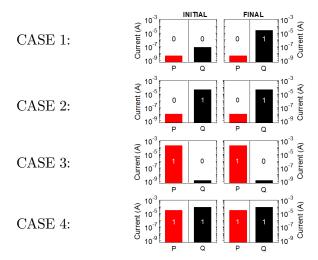

| 5.2. Mem  | RISTOR AS DIGITAL ELEMENT                                                    | 125     |

| 5.3. Expe | ERIMENTAL VERIFICATION OF THE IMPLY AND NAND GATES BASED ON E                | $IFO_2$ |

| 5.3.1.    | Experimental procedure conditions                                            |         |

| 5.3.2.    | IMPLY gate                                                                   | 127     |

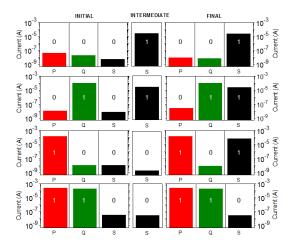

| 5.3.3.    | IMPLY-based NAND gate                                                        | 128     |

| 5.4. A MC | DDIFIED NAND PROCEDURE OPERATION                                             | 130     |

| 5.4.1.    | Circuit analysis and feasibility                                             | 131     |

| 5.4.2.    | Experimental verification                                                    | 133     |

|           | LYSIS OF THE TRANSIENT RESPONSE OF THE MEMRISTORS DURING $IMPLY$ RATION STEP | 135     |

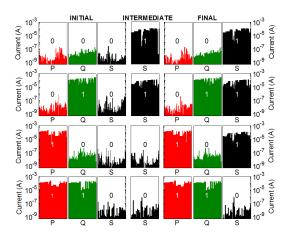

| 5.5.1.    | Experimental procedure conditions                                            | 135     |

| 5.5.2.    | Memristors behaviour for each IMPLY case                                     | 136     |

| 5.5.3.    | The effect of the series resistor on IMPLY operation                         | 144     |

| 5.6. Cond | CLUSIONS                                                                     | 147     |

| 6. CONC   | LUSIONS                                                                      | 149     |

| PUBLICA   | ATIONS                                                                       | 153     |

| o nano ni | NCDC                                                                         | 1 5 77  |

# **ACRONYMS**

| Abbreviation        | Explanation                           |

|---------------------|---------------------------------------|

| CDF                 | Cumulative Distribution Function      |

| $\operatorname{CF}$ | Conductive Filament                   |

| CLCU                | Current Limit Control Unit            |

| ECM                 | Electro-Chemical Mechanism            |

| HRS                 | High Resistance State                 |

| IMPLY               | Material Implication                  |

| Log IVC             | Logarithmic current-Voltage Converter |

| LRS                 | Low Resistance State                  |

| MIM                 | Metal-Insulator-Metal                 |

| MIS                 | Metal-Insulator-Semiconductor         |

| RRAM                | Resistive Random Access Memory        |

| RS                  | Resistive Switching                   |

| RTN                 | Random Telegraph Noise                |

| SD                  | Selector Device                       |

| SMU                 | Source Measurement Unit               |

| SPA                 | Semiconductor Parameter Analyzer      |

| TCM                 | Thermochemical Mechanism              |

| TLP                 | Time Lag Plot                         |

| TS                  | Threshold Switching                   |

| VCM                 | Valence Change Mechanisms             |

| VRS                 | Voltage Ramp Speed                    |

| W-TLP               | Weighted-Time Lag Plot                |

| NVM                 | Non Volatile Memory                   |

# PREFACE

In general, the continuous evolution, and improvement, of the technology has led to face new emerging challenges. Regarding the electronic field, one of the most relevant has been the Moore's law which postulates "the number of transistors in a dense integrated circuit doubles approximately every two years". To accomplish this postulate, the solution has been reducing the device dimensions. However, in last decades, physical limitations have been reached since device dimensions are in the atomic range. Moreover, problems originated from the device scaling such as short channel effects in MOSFETs have been observed. Consequently, the focus of the scientific community has turned into the exploration of alternative device materials and structures or different phenomena that would overcome the different issues owing to the scaling.

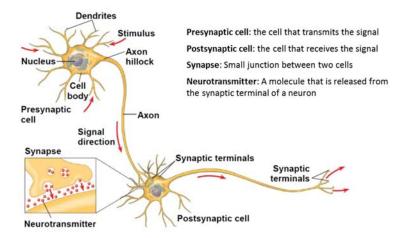

Concerning alternative phenomena, one of the most relevant has been the **Resistive** Switching (RS) phenomenon which has shown promising features to be implemented in many applications. This phenomenon is based on the capability of a dielectric layer to change its resistance (or conductivity) between two or more values, which show a non-volatile behavior, under the action of an electric field. Overall, these characteristics makes this phenomenon very suitable and promising for its application in digital logic where a new paradigm of computation based on this phenomenon is emerging, in the development of artificial neural networks emulating the behavior of the neuron part known as synapse, and in memory like the next generation of non-volatile memories.

Resistive switching (RS) was firstly reported by T. W. Hickmott (1962) and later by J. G. Simmons and R. R. Verderber (1967) where such a phenomenon was observed in different metal-oxide-metal sandwiches whose dielectric layer was based on silicon, aluminum, titanium, tantalum, or zirconium. Initially, the phenomenon was not defined like resistive switching, authors talked about changes in the resistance of the dielectric layer by observing large current densities inside of that layer. During the 1960s and 1970s, multiples studies about RS were performed due to the great interest the phenomenon caused. Many dielectric materials were observed exhibiting those resistance changes and different physical mechanisms were proposed to explain the origin of that resistance change. However, one of the most important contribution was in the applicability of the phenomenon. Devices exhibiting resistance changes were originally proposed to be implemented like non-volatile memories.

The interest in RS phenomenon decreased significantly in the 1980s and 1990s. The most likely reasons were the slow progress in the physical understanding of the

phenomenon, the difficulty in controlling it for a specific application and the enormous prosperity of silicon-based electronics. However, in the very beginning of 2000s, the interest in RS phenomenon suffered a revival. Zhuang, et al. in 2002 reported a fabricated resistive switching-based device to act like non-volatile memory element and Baek, et al. in 2004 showed the first RS behavior in binary transition metal oxides (TMO). From these years to date, a vast number of works about RS have been published extending the materials showing RS characteristics (binary and ternary oxides, nitrides or even organics materials); proposing new physical mechanisms or completing the existing ones to better describe RS phenomenon in the different dielectric materials (based on ion migration, thermochemical reaction or changes in the dielectric morphology). Additionally, much more works have been released where the applicability of RS-based devices as non-volatile memories, in the implementation of logic gates or in unconventional computing has been verified.

Despite the great efforts of the scientific community in last half a century, there are several hot topics, such as the deeper RS understanding, the analysis of reliability issues affecting RS behavior or the thorough investigation on new applications of RS-based devices in which much more work must be done. In this way, the goal of this thesis is focused on increasing the RS phenomenon knowledge and studying its feasibility for different applications. Hence, RS phenomenon has been study both at device level, to analyze the phenomenon itself, and at circuit level, to analyze its application in memory and digital fields. The results have been presented in relevant publications and conferences related to this subject. All these results are thoroughly explained in this thesis which is structured as follow:

Initially, in the first chapter, resistive switching phenomenon is widely defined, describing the main parameters that characterize it. The different modes in which the phenomenon can operate and the physical mechanisms explaining the origin of the resistance changes are described. Furthermore, the main applications where RS phenomenon can be implemented are numbered as well as the typical devices structures in which the phenomenon is observed. Eventually, a brief description of the principal reliability issues affecting the phenomenon performance is included.

In the second chapter, the RS phenomenon is experimentally studied on MOSFET transistors analyzing the effect on the dielectric resistance change of the voltage polarity applied to provoke RS. Furthermore, due to the localized character of the phenomenon, the different current contributions involved in the conduction through the dielectric and the control of those current contributions are analyzed.

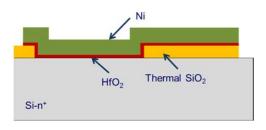

In the third chapter, RS is studied on memristors with a dielectric layer based on HfO<sub>2</sub>. Here, the phenomenon is studied applying fast voltage ramps to provoke the resistance changes in order to analyze the influence of the voltage ramp speed on the

RS parameters. In addition, in this chapter, enhanced experimental setups and characterization methods are proposed to analyze the RTN associated to RS.

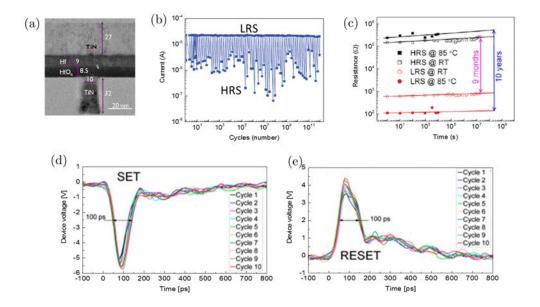

In the fourth chapter, memristors with a SiO-based dielectric layer are investigated as memory and selector devices. Different DC and pulsed analysis are included to corroborate the feasibility of such devices for these applications.

Finally, the fifth chapter is dedicated to the application of memristors in the digital field. Memristors are used as the main element to design logic gates, specifically, to implement material implication-based (IMPLY) and NAND gates. In this chapter, the experimental working demonstration of both memristor-based logic gates (IMPLY and NAND) is presented. In addition, the transient behaviors of memristors involved in the IMPLY gate are experimentally studied in order to analyze what happens to memristors during IMPLY operation.

# **PREFACIO**

La continua evolución de la tecnología ha llevado a afrontar nuevos retos. Concretamente en el campo de la electrónica, uno de los más relevantes ha sido la Ley de Moore que postula que "el número de transistores in un circuito integrado se duplicará aproximadamente cada dos años". Por ello, para cumplir con dicho ley, la solución ha sido reducir las dimensiones de los dispositivos. Sin embargo, en las últimas décadas, la reducción de estas dimensiones ha alcanzado limitaciones físicas ya que actualmente se está llegando al rango atómico. Además, se han observado diversos problemas, como por ejemplo efectos de canal corto en MOSFETs, originados por el escalado de los dispositivos. Como consecuencia, la comunidad científica se ha focalizado en la exploración de nuevos materiales, en el desarrollo de estructuras alternativas o en el estudio de diferentes fenómenos para solucionar los problemas derivados del escalado.

Con respecto a fenómenos físicos alternativos, uno de los más relevantes ha sido el fenómeno de **Resistive Switching** (RS) el cuál ha mostrado prometedoras características para ser implementado en diversas aplicaciones. Este fenómeno se basa en la capacidad de una capa de dieléctrico para cambiar su resistencia (o conductividad) entre dos o más valores que muestran un comportamiento no volátil bajo la acción de un campo eléctrico. En general, estas características permiten que este fenómeno sea muy apropiado y prometedor para su aplicación en lógica digital, donde un nuevo paradigma de computación basado en este fenómeno está surgiendo, en el desarrollo de redes neuronales artificiales, emulando el comportamiento de una parte de la neurona conocida como sinapsis, y en memorias como la siguiente generación de memorias no volátiles.

Resistive switching fue citado por primera vez por T. W. Hickmott (1962) y más tarde por J. G. Simmons and R. R. Verderber (1967) donde dicho fenómeno fue observado en diferentes estructuras metal-óxido-metal cuya capa dieléctrica estaba basada en silicio, aluminio, titanio, tantalo o zirconio. Inicialmente, el fenómeno no fue definido como RS, los autores hablaban simplemente de cambios en la resistencia de la capa de dieléctrico observando grandes densidades de corriente a través de dicha capa. Durante los años 60 y los 70, se llevaron a cabo multiples estudios sobre RS debido al gran interés que suscitó el fenómeno. Se observaron muchos materiales dieléctricos mostrando los sucesivos cambios de resistencia y se proposieron diferentes mecanismos físicos que pretendían explicar el origen de esos cambios resistivos. Sin embargo, una de las contribuciones más importantes fue en la aplicabilidad del

fenómeno. Dispositivos exhibiendo cambios resistivos fueron originalmente propuestos para ser implementados como memorias no volátiles.

El interés sobre el fenómeno RS disminuyó significativamente en las decadas de los 80 y 90. La razón más probable fue el lento progreso en el entendimiento físico del fenómeno, en la dificultad de controlarlo para aplicaciones más especificas y a la enorme prosperidad de la electrónica basada en silicio. Sin embargo, al comienzo de los 2000, el interés sobre el fenómeno RS sufrio un nuevo auge, principalmente debido a que. Zhuang, et al. en 2002 reportaron un dispositivo experimental basado en resistive switching que podía actuar como un elemento de memoria no volátil y Baek, et al. en 2004 mostraron el primer comportamiento de RS en óxidos metálicos binarios de transición (TMO). Desde aquellos años hasta la fecha, se han publicado un vasto número de trabajos sobre RS donde se ha aumentado el número de materiales que experimentan características RS (óxidos binarios y ternarios, nitruroso incluso material orgánicos); se han propuesto nuevos mecanismos físicos o se han completado los ya existentes para describir mejor el fenómeno RS en los diferentes materiales dieléctricos (basados en migración de iones, reacciones termoquímicas o en cambios en la morfología del dieléctrico). Adicionalmente, se han publicado numerosos trabajos donde se ha demonstrado la aplicabilidad de dispositivos basados en RS como memorias no volatiles, in la implemtación de puestas lógicas o en computación no convencional.

A pesar de los grandes esfuerzos por parte de la comunidad científica en la última mitad de siglo, hay varios temas candentes en los que aún queda mucho trabajo por hacer. Algunos de estos temas son entender más profundamente el fenómeno RS, analizar los problemas de fiabilidad que afectan al comportamiento RS o la investigación minuciosa de nuevas aplicaciones de dispositivos basados en RS. Por tanto, el fenómeno RS ha sido estudiado tanto a nivel de dispositivo, para analizar el fenómeno en sí mismo, como a nivel de circuito, para analizar sus aplicaciones en memorias y en lógica digital. Los resultados han sido presentados en publicaciones y conferencias relevantes en el tema donde la tesis está enmarcada. Todos estos resultados son detalladamente explicados en esta tesis que se ha estructurado como sigue:

Inicialmente, en el primer capítulo se explica ampliamente el fenómeno de RS, describiendo los principales parámetros que lo caracterizan. Se definen los diferentes modos en los que el fenómeno puede operar así como los mecanismos físicos que explican el origen de los cambios resistivos. También, se listan las principales aplicaciones donde el fenómeno RS puede ser implementado además de las estructuras típicas en las cuales el fenómeno es observado. Finalmente, se incluye una breve descripción de los problemas de fiabilidad más relevantes que afectan al rendimiento del fenómeno.

En el segundo capítulo, el fenómeno RS se estudia experimentalmente en transistores MOSFETs analizando el efecto de la polaridad del voltaje aplicado para provocar RS sobre el cambio resistivo del dieléctrico. Además, debido al carácter localizado del fenómeno, se analizan las diferentes contribuciones de corriente involucradas en la conducción a través del dieléctrico y el control de dichas contribuciones.

En el tercer capítulo, RS se estudia en memristores con una capa de dieléctrico basada en HfO<sub>2</sub>. Aquí, el fenómeno se estudia aplicando rampas de voltajes más rápidas para provocar los cambios resistivos con el fin de analizar la influencia de la velocidad de la rampa sobre los parámetros RS. También, en este capítulo, se proponen montajes experimentales y métodos de caracterización mejorados para analizar el random telegraph noise (RTN) asociado al RS.

En el cuarto capítulo, se investigan memristores con una capa de dieléctrico basada en SiO para su aplicación como dispositivos de memoria y selección. Se han incluido diferentes análisis tanto en DC como AC para corroborar la viabilidad de dichos dispositivos en esas aplicaciones.

Finalmente, el quinto capítulo está dedicado a la aplicación de memristores en el campo de la lógica digital. Se han usado memristores como el elemento principal para diseñar puertas lógicas, específicamente para implementar puertas IMPLY y NAND. En este capítulo, se presenta la demostración experimental del funcionamiento de dichas puertas basadas en memristores así como el estudio experimental de la evolución temporal de los memristores involucrados en la puerta IMPLY con el fin de analizar que ocurre durante la operación lógica.

# **Prefact**

La contínua evolució de la tecnologia ha portat a afrontar nous reptes. Concretament en el camp de l'electrònica, un dels més rellevants ha estat la Llei de Moore que postula que "el nombre de transistors en un circuit integrat es duplicarà aproximadament cada dos anys". Per això, per complir aquest raonament, la solució ha estat reduir les dimensions dels dispositius. No obstant això, en les últimes dècades, la reducció d'aquestes dimensions ha arribat a limitacions físiques ja que actualment s'està arribant al rang atòmic. A més, s'han observat diversos problemes, com ara efectes de canal curt en MOSFETs, originats per l'escalat dels dispositius. Com a conseqüència, la comunitat científica s'ha focalitzat en l'exploració de materials i estructures de dispositius alternatives o en diferents fenòmens que ajudarien a solucionar els problemes derivats de l'escalat.

Pel que fa a fenòmens físics alternatius, un dels més rellevants ha estat el fenomen de Resistive Switching (RS) el quin ha mostrat prometedores característiques per ser implementat en diverses aplicacions. Aquest fenomen es basa en la capacitat d'una capa de dielèctric per canviar la seva resistència (o conductivitat) entre dos o més valors que mostren un comportament no volàtil sota l'acció d'un camp elèctric. En general, aquestes característiques permeten que aquest fenomen sigui molt apropiat i prometedor per a la seva aplicació en lògica digital, on un nou paradigma de computació basat en aquest fenomen està sorgint, en el desenvolupament de xarxes neuronals artificials, emulant el comportament d'una part de la neurona coneguda com sinapsis, i en memòries com la següent generació de memòries no volàtils.

Resistive switching va ser citat per primera vegada per T. W. Hickmott (1962) i més tard per J. G. Simmons and R. R. Verderber (1967) on aquest fenomen va ser observat en diferents estructures metall-òxid-metall la capa dielèctrica estava basat en silici, alumini, titani, tantalo o zirconi. Inicialment, el fenomen no va ser definit com RS, els autors parlaven simplement de canvis en la resistència de la capa de dielèctric observant grans densitats de corrent a través d'aquesta capa. Durant els anys 60 i els 70, es van dur múltiples estudis sobre RS a causa del gran interès que va suscitar el fenomen. Molts materials dielèctrics van ser observats mostrant aquells canvis de la seva resistència i diferents mecanismes físics van ser proposats per explicar l'origen d'aquest fenomen. No obstant això, una de les contribucions més importants va ser l'aplicabilitat del fenomen. Dispositius exhibint canvis resistius van ser originalment proposats per a ser implementats com memòries no volàtils.

L'interès sobre el fenomen RS va disminuir significativament en les dècades dels 80 i 90. La raó més probable va ser el lent progrés en l'enteniment físic del fenomen, en la dificultat de controlar-lo per a aplicacions més específiques i l'enorme prosperitat de l'electrònica basada en silici. No obstant això, a començaments dels anys 2000, l'interès sobre el fenomen RS va patir un ressorgiment. Zhuang, et al. al 2002 van reportar un dispositiu experimental basat en Resistive switching que podia actuar com un element de memòria no volàtil i Baek, et al. al 2004 van mostrar el primer comportament de RS en òxids metàl·lics binaris de transició (TMO). Des d'aquests anys fins a la data, s'han publicat un vast nombre de treballs sobre RS on s'ha augmentat el nombre de materials que experimenten característiques RS (òxids binaris i ternaris, nitrurs fins i tot materials orgànics); s'han proposat nous mecanismes físics o s'han completat els ja existents per descriure millor el fenomen RS en els diferents materials dielèctrics (basats en migració d'ions, reaccions termoquímiques o en canvis en la morfologia del dielèctric). Addicionalment, s'han publicat molts més treballs on s'ha demostrat l'aplicabilitat de dispositius basats en RS com memòries no volàtils, en la implantació de postes lògiques o en computació no convencional han estat publicats.

Malgrat els grans esforços per part de la comunitat científica en l'última meitat de segle, hi ha diversos temes candents en què encara queda molta feina per fer. Alguns d'aquests temes són entendre més profundament el fenomen RS, analitzar els problemes de fiabilitat que afecten al comportament RS o la investigació minuciosa de noves aplicacions de dispositius basats en RS. Per tant, el fenomen RS ha estat estudiat tant a nivell de dispositiu, per analitzar el fenomen en si mateix, com a nivell de circuit, per analitzar les seves aplicacions en memòries i en lògica digital. Els resultats han estat presentats en publicacions i conferències rellevants en el tema on la tesi està emmarcada. Tots aquests resultats són detalladament explicats en aquesta tesi que s'ha estructurat com segueix:

Inicialment, en el primer capítol, el fenomen de RS és àmpliament definit, descrivint els principals paràmetres que el caracteritzen. Els diferents maneres en què el fenomen pot operar així com els mecanismes físics que expliquen l'origen dels canvis resistius són descrits. També, es llisten les principals aplicacions on el fenomen RS pot ser implementat a més de les estructures típiques en les quals el fenomen és observat. Finalment, s'inclou una breu descripció dels problemes de fiabilitat més rellevants que afecten el rendiment del fenomen.

En el segon capítol, el fenomen RS s'estudia experimentalment en transistors MOSFETs analitzant l'efecte de la polaritat del voltatge aplicat per provocar RS sobre el canvi resistiu del dielèctric. A més, a causa del caràcter localitzat del fenomen, s'analitzen les diferents contribucions de corrent involucrades en la conducció a través del dielèctric i el control d'aquestes contribucions.

En el tercer capítol, RS s'estudia en memristors amb una capa de dielèctric basada en HfO2. Aquí, el fenomen s'estudia aplicant rampes de voltatges més ràpides per provocar els canvis resistius per tal d'analitzar la influència de la velocitat de la rampa sobre els paràmetres RS. També, en aquest capítol, es proposen muntatges experimentals i mètodes de caracterització millorats per analitzar el random telegraph noise (RTN) associat a l'RS

En el quart capítol, s'investiguen memristors amb una capa de dielèctric basada en SiO per a la seva aplicació com a dispositius de memòria i selecció. Diferents anàlisis tant en DC com AC s'han inclòs per corroborar la viabilitat d'aquesta dispositius en aquestes aplicacions.

Finalment, el cinquè capítol està dedicat a l'aplicació de memristors en el camp digital. Els memristors són usats com l'element principal per dissenyar portes lògiques, específicament per implementar portes IMPLY i NAND. En aquest capítol, es presenta la demostració experimental del funcionament d'aquestes portes basades en memristors. A més, s'ha estudiat experimentalment l'evolució temporal dels memristors involucrats en la porta IMPLY per tal d'analitzar com es comporten aquests memristors durant l'operació lògica.

# 1. Introduction

any alternatives have been proposed along the years in order to improve technology and make it more competitive particularly in the electronic field. As indicated in the preface, the scaling of device dimensions, was one of those alternatives which successfully allowed accomplishing Moore's law. However, as the scaling increased, different issues related to physical limitations or the wrong-operations of devices have been appearing. In order to solve them, different device materials and structures and other physical phenomena have been studied. In this latter regard, a new phenomenon, known as *Resistive Switching* (RS), has emerged as an alternative physical mechanism to be implemented in many different applications like logic, memory, artificial neural networks and computing.

Due to Resistive Switching is the focus of this thesis, an overview of the phenomenon is presented in this introductory chapter. First, the description of the phenomenon is detailed, explaining the basis of RS operation, the different modes in which the phenomenon can operate regarding the polarity of the applied electric field and the main physical mechanisms that explain the behavior of RS. Second, the foremost reliability issues related to the phenomenon are also introduced indicating how they affect to RS functionality, the different studies performed about them and, if possible, the proposed solutions to overcome them. Third, relevant applications where RS has been implemented are presented explaining their performance and including some examples that demonstrate the functionality of RS phenomenon in the application. Eventually, a description of the equipment used along the thesis as well as measurement and data analysis procedures is included at the end of the chapter.

### 1.1. Resistive switching phenomenon

In this section, resistive switching phenomenon will be described. Initially, a detailed phenomenon definition, indicating its characteristic processes and parameters, will be presented as well as the devices where such a phenomenon has been observed. Then, the different operation modes in addition with the most relevant physical mechanisms that describe the phenomenon will be explained.

### 1.1.1. What is Resistive Switching?

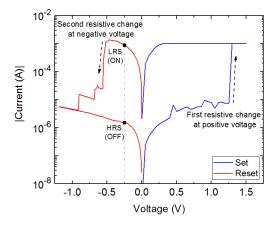

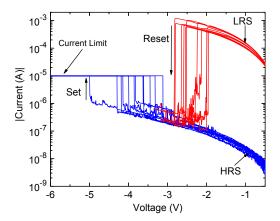

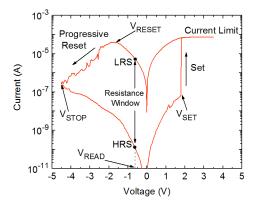

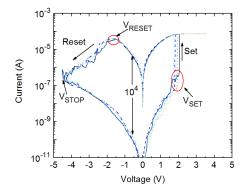

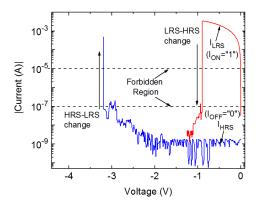

Resistive switching consists in successive resistance changes of a thin dielectric layer by applying an external electric field. Figure 1-1 shows two typical experimental current-voltage (IV) curves of the phenomenon. One IV-curve corresponds to the first resistive change for positive applied voltages whereas the subsequent resistive change is depicted for negative voltages, although other combinations of voltage polarities can take place. The resistance changes of the dielectric layer commonly occur between two well-differentiated states, which are usually separated by several orders of magnitude, although dielectrics with more than two resistance values are also possible allowing multistate RS. Those two dielectric resistance states are extensively recognized as high resistance state, HRS, and low resistance state, LRS, which show a non-volatile behavior, i.e. they are remained for a retention time after the electric field has been removed. Due to the relation between resistance and current (Ohm's law), at LRS state the current flowing through the dielectric is quite large; however, at HRS the flow of the current is almost suppressed (in Figure 1-1

Figure 1-1: Typical experimental IV-curves of a memristive device showing resistive switching phenomenon.

indicated LRS and HRS show a current difference of approximately three decades). LRS and HRS resistance states can be also identified as ON (current flowing) and OFF (not current flowing) states, respectively. Moreover, following digital nomenclature, they can be considered as the "1" and "0" Boolean values for memory and digital applications.

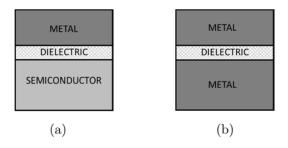

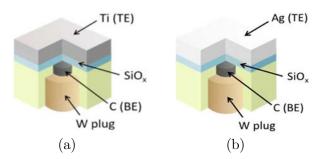

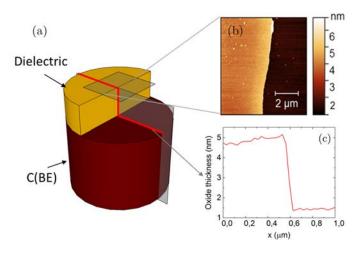

Those devices where RS phenomenon takes place are frequently known as memristive devices. The most used and important memristive device is the memristor (contraction of memory and resistor). Firstly predicted by Leon Chua in 1971 as one of the four fundamental two-terminal circuit elements [1], and later experimentally demonstrated by D. Strukov and et al. in 2008 [2], memristors have become in a reality during the last decades. Structurally, a memristor consists in a three-layer structure formed by a top electrode, a bottom electrode and a dielectric layer sandwiched in between those electrodes. Two different memristor structures are mainly found: metal-insulator-metal (MIM) and metal-insulator-semiconductor (MIS) which are schematically presented in Figure 1-2(a) and (b), respectively. The dielectric layer corresponds to that layer whose resistance can be successively changed and, therefore, where the RS phenomenon takes places. However, the observation of such a phenomenon strongly depends on the electrodes and dielectric materials, not all the materials can experience RS phenomenon. Both, MIS and MISstructured memristors have been used along this thesis to study different applications of the RS phenomenon.

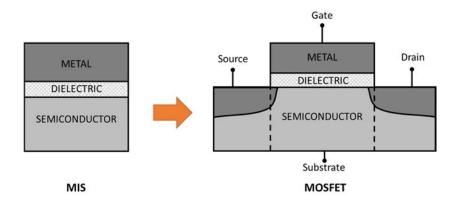

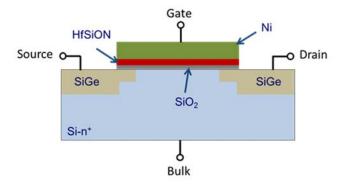

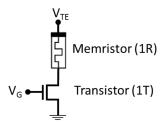

From memristive point of view, a MOSFET transistor can be considered as a memristor because it is based on a MIS structure where two additional regions (drain and source) have been added, as shown in Figure 1-3. Essentially, MOSFET can act as a memristive device when a voltage difference is applied between gate and substrate electrodes, while drain and source terminals are grounded. Consequently, a resistance state change takes place in the dielectric (or oxide) layer. Such description of MOSFET operation could suggest that drain and source regions are

gure 1-2: Schematic of (a) a metal-insulator-semiconductor (MIS) and (b) a metal-insulator-metal (MI structures.

Figure 1-3: Schematic of a MOSFET where all the electrodes are indicated: gate, substrate, drain and source. RS phenomenon takes place in the dielectric layer located between the gate and substrate electrodes. Hence, a MOSFET can be considered as a memristive device.

useless since they are grounded all the time. Contrarily, these two terminals have allowed characterizing more deeply the resistance change behavior and postulating and demonstrating the existence of a kind of MOSFETs where resistive switching phenomenon and typical transistor operations can alternatively occur in the same device. This multifunction transistor has been called memFET (memory field effect transistor), [3]–[6], due to its functionality like memory, by provoking RS phenomenon, and like a typical transistor by modulating the current flowing between source and drain through the electric field applied between gate and substrate. More studies in the literature have also devoted to the analysis of the resistive switching in transistors [7].

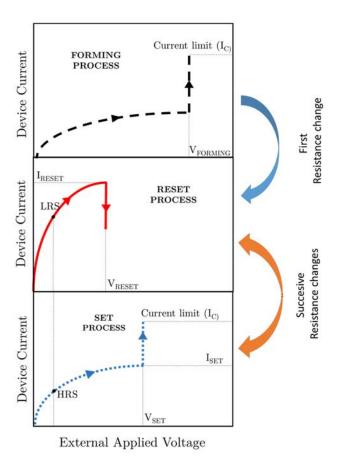

Successive dielectric resistance changes in memristors are accomplished by performing different electrical processes that are mainly known like forming, set and reset. In Figure 1-4, very schematic representations of the three processes involved in RS operation as well as its characteristic parameters are depicted.

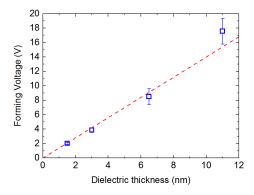

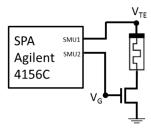

Forming process is usually the very first process occurring in a device where RS phenomenon is observed. Although it is not necessary in all the devices, in most of dielectric materials in which RS is observed, this process is required to observe subsequently the RS behavior. The forming process provokes the change of the dielectric resistance value from a pristine state to a LRS (top in Figure 1-4) by applying an external voltage. The exact voltage value at which this resistance change takes place is usually known as forming voltage,  $V_{FORMING}$ . An important condition to take into account during the forming process, although not mandatory depending on the dielectric material, is the use of a limit in the current flowing through the dielectric to avoid a complete dielectric breakdown which is an irreversible phenomenon. This parameter is commonly named compliance or current limit ( $I_{\rm C}$ ).

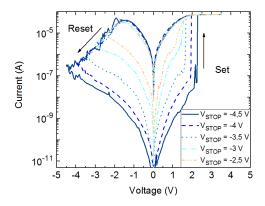

After forming, the device can be switched from LRS to HRS and vice versa successively by applying external voltages again. The first resistance change (from LRS to HRS) where dielectric resistance value increases is identified as reset process and the voltage at which the change occurs is defined as reset voltage, V<sub>RESET</sub> (center in Figure 1-4). On the other hand, the process to perform the decrease of the dielectric resistance (from HRS to LRS) is called set process whose characteristic voltage, i.e. the voltage at which resistance change occurs, is labeled as set voltage, V<sub>SET</sub> (bottom in Figure 1-4). Like in the forming process, during set process it is usually necessary to establish a current limit to avert an irreversible damage in the dielectric and to observe successive dielectric resistance changes.

Regarding the polarity of the applied voltage to provoke the different processes, RS phenomenon can be classified into different operation-mode categories depending on the polarity combination of voltages applied to perform set and reset processes.

Figure 1-4: Schematic of forming (top), reset (center) and set (bottom) processes. Characteristic voltages ( $V_{FORMING}$ ,  $V_{RESET}$  and  $V_{SET}$ ), resistance states (LRS and HRS) and characteristic currents ( $I_{SET}$  and  $I_{RESET}$ ) are also indicated in each process.

### 1.1.2. Operation modes

The main operation modes of the phenomenon are: bipolar and unipolar resistive switching. There is a third operation mode, not related to voltage polarity actually, known as threshold switching. This last operation mode differs from the previous ones in the volatile behavior or the LRS, because when the applied voltage is removed memristive device comes back to HRS.

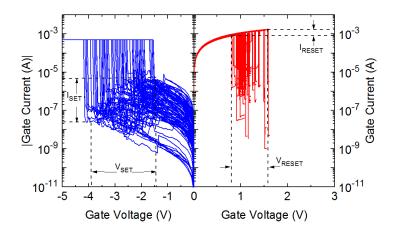

### 1.1.2.1. Bipolar resistive switching

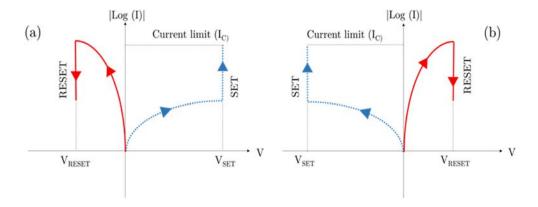

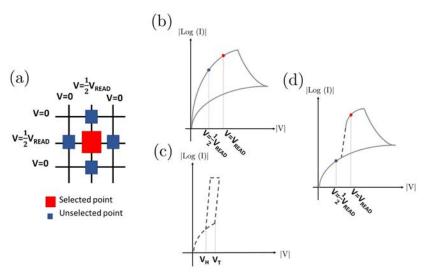

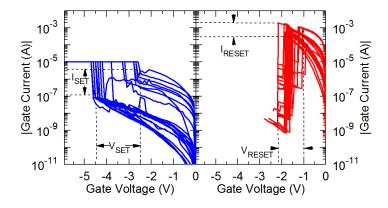

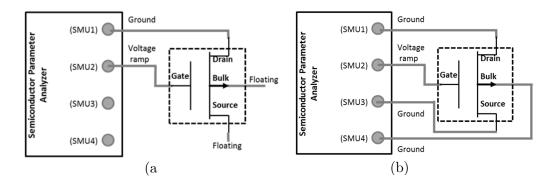

Bipolar RS takes place when the voltages applied to perform set and reset processes have opposite polarities. This is the most common voltage polarity combination used to observe the RS phenomenon. Schematic I-V curves for both possible bipolar switching modes are sketched in Figure 1-5(a) and (b), where the absolute value of the current is plotted in a logarithmic scale. In both figures, dotted blue curve corresponds to the change from HRS to LRS, i.e. the set process (the current limit, Ic, usually needed to avoid the whole dielectric breakdown is also indicated) whereas solid red curve shows the transition from LRS to HRS, i.e. when reset process takes place. First bipolar switching mode (Figure 1-5(a)) is called, in some works, as "figure-of-eight" bipolar switching due to 8-shape of the curves when they are plotted in linear scales. In this case, set process takes place when positive voltages are applied while reset process occurs for negative voltages. On the contrary, owing to the inversion of polarities, the second bipolar switching mode, where set and reset processes are provoked when negative and positive voltages are applied respectively (Figure 1-5(b)), is called "counter-figure-of-eight" bipolar switching.

Figure 1-5: Sketch of typical I-V characteristics for (a) bipolar RS, where applied voltages to set and reset the device are positive and negative respectively, and (b) bipolar RS where set and reset processes are provoked applying negative and positive voltages, respectively.

Many materials have been reported in the literature showing bipolar RS such as TiO<sub>2</sub>, TaO<sub>x</sub>, HfO<sub>x</sub>, Al<sub>2</sub>O<sub>3</sub>, Cr<sub>2</sub>O<sub>3</sub>, SiN, BaTiO<sub>3</sub> or graphene oxide amongst many others [8], [9]. Majority of the materials show only one kind of the bipolar voltage polarity combination (the one presented in Figure 1-5(a) or (b)). However, in some dielectric materials as for example WO<sub>x</sub> [10], [11] both bipolar RS modes have been observed.

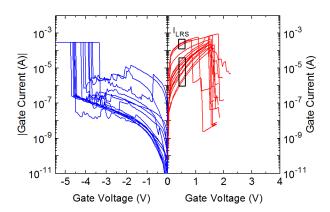

### 1.1.2.2. Unipolar resistive switching

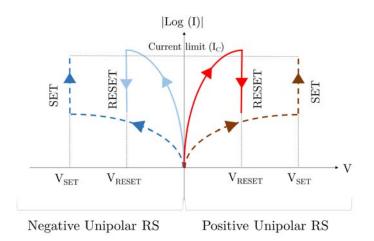

Contrarily to the previous switching mode, unipolar resistive switching occurs when the voltage polarities applied to provoke set and reset processes are the same. Because of the two different voltage polarities, unipolar switching can be sub-classified into two types: negative and positive. In Figure 1-6, both negative (left hand side) and positive (right hand side) unipolar resistive switching are schematically shown (y-axis corresponds to absolute value of the current in logarithmic scale). Here, dashed line corresponds to the resistance transition from HRS to LRS, the set process. On the contrary, solid line represents the LRS-HRS transition, where reset process occurs. Current limit (I<sub>C</sub>), although not always necessary, is also included during set process.

Many works have demonstrated the existence of many different dielectric materials showing negative, TiO<sub>2</sub> [12], positive, SiO<sub>X</sub> [13], Nb<sub>2</sub>O<sub>5</sub> [14] or even both unipolar RS modes HfO<sub>2</sub> [15], NiO [16], [17]. On the other hand, not only unipolar or bipolar operation modes can be observed in the same material, some other works have shown

Figure 1-6: Sketch of typical I-V characteristics for both unipolar RS modes, (left) negative unipolar RS and (right) positive unipolar RS. In each mode, the applied voltages to provoke set and reset processes have the same polarity.

the coexistence of both resistive switching modes (bipolar and unipolar) occurring in the same device with a dielectric layer based on  $TiO_2$  [18], NiO [19] or  $HfO_2$  [20].

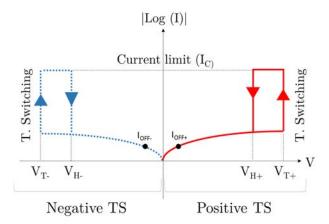

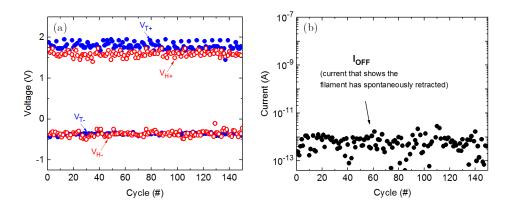

#### 1.1.2.3. Threshold switching

Although it is also based on RS phenomenon, threshold switching (TS) is not strictly a resistive switching mode as far as voltage polarity and state volatility is concerned. However, as some results of this thesis are related to this type of switching, a brief introduction about TS is included.

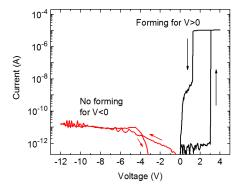

Figure 1-7 shows a sketch of I-V curves for positive (solid red line) and negative (dotted blue line) threshold switching behavior. Initially, by applying a voltage ramp, TS consists in a set-like switching process which occurs at a certain voltage called threshold voltage,  $V_T$ . During the process, a current limit is also necessary to avoid a complete dielectric breakdown and reach the low resistance state as in the case of the set process. Contrarily to RS, the reached resistance state shows a volatile behavior; therefore, when voltage is removed back to zero an inverse switching takes place at a voltage named holding voltage,  $V_H$ . Then, a device showing TS only has one stable resistance state which is related with a HRS state in RS and whose current, measured to identify such a state, is labeled  $I_{OFF}$  as it is shown in Figure 1-7. The other resistance state reached after threshold switching, related to LRS state, is only stable in a short voltage range (between  $V_T$  and  $V_H$ ). Due to the volatile behavior, threshold switching lacked of interest in memory or digital applications where two stable states are required. However, TS mode has been very attractive to develop select devices in crossbar memories [21], [22] as will be shown in section 1.3.

Figure 1-7: Sketch of typical I-V curves of positive (solid red lines) and negative (dotted blue lines) threshold switching behavior when positive and negative voltages are respectively applied. A current limit ( $I_{\rm C}$ ), needed in TS, is also indicated.

Once the different RS operation modes have been introduced, another important matter related to the RS phenomenon is the explanation of how set and reset processes physically occur. Different physical mechanisms explaining the nature of the resistance change behavior in a dielectric material have been proposed in the literature. In the following subsection, those physical mechanisms related to the RS phenomenon observed in this thesis are briefly presented.

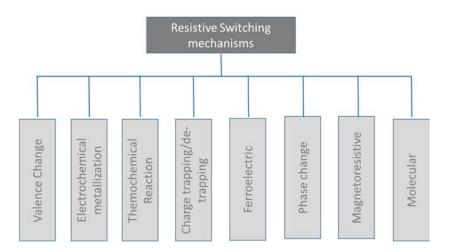

## 1.1.3. Physical RS mechanisms

Numerous research groups have focused their efforts on finding the physical mechanisms that governs the set and reset processes to explain the RS behavior. [23]–[32]. Furthermore, those physical mechanisms specifically allow explaining the different operation modes of RS. Figure 1-8 shows a classification of different mechanisms according to how the resistance change physically occurs [24]. From all of them, only the three mechanisms occurring in the devices used along this thesis will be described. These three mechanisms (valence change, electromechanical metallization and thermochemical reaction) are very similar since the resistance changes of the dielectric are owing to the creation/dissolution of a conductive filament (CF) along the dielectric that connects top and bottom electrodes. The difference between these three mechanisms is in the physical process performed to create and disrupt the conductive filament. These processes depend on the materials of dielectric layer and the electrodes as well as the polarity of applied voltages to provoke the RS.

Figure 1-8: Classification of different physical mechanisms explaining the dielectric resistance change depending on how the resistance change physically occurs [24].

## 1.1.3.1. Valence change

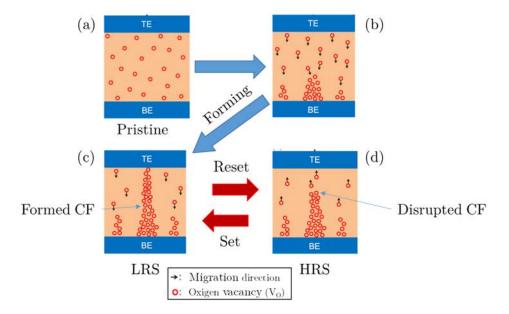

Valence change mechanism (VCM) typically occurs in metal oxides such as HfO<sub>x</sub> [33],  $NiO_X$  [34],  $TaO_X$ [35], or  $TiO_X$  [25], where a migration of ions takes place, specifically, a migration of anions. Actually, the mechanism is described by the "migration" of the positively charged counterparts, known as oxygen vacancies  $(V_{OS})$ , of those anions. The accumulation/depletion of  $V_{OS}$  causes changes in the resistance of the oxide. The accumulation of vacancies can be associated to the creation of a conductive filament formed of such vacancies. On the other hand, the depletion can be related to the dissolution or disruption of the conductive filament. In Figure 1-9, a schematic of valence change process is depicted. Initially, (a) the device in a pristine state has a uniform distribution of oxygen vacancies. Then, when a positive voltage bias is applied to the top electrode (TE), with the bottom electrode (BE) grounded, an accumulation of oxygen vacancies is induced at the interface between BE and oxide layer (b). If enough positive voltage is applied, the forming process is finally provoked creating a V<sub>o</sub>s-based conductive filament connecting TE and BE (c) and reaching the LRS. After the forming, the device has reached the LRS state. Owing to the nature of the mechanism, Vos-based filaments are typically considered conical shaped whose thinnest part is located at the interface between TE and oxide.

Figure 1-9: Schematic of VCM mechanism. (a) Initial state with a uniform distribution of oxygen vacancies. (b) Accumulation of oxygen vacancies starting at the interface between BE and the oxide layer. (c) Device at LRS when set (or forming) process has been performed by applying positive voltage bias. (d) HRS state of the device reached after a negative voltage bias was applied provoking reset process. Readapted from [8].

Once conductive filament is created, the device can be switched to HRS by means of the reset process. To do so, a negative voltage bias is applied provoking the totally or partially disruption of the filament (d) what is caused mainly by the  $V_{os-}$  migration-induced redox reaction. Applying a positive voltage bias again, the device can be switched to LRS state performing the set process and a re-creation of the filament is done (c). Applying successively positive and negative voltage biases, subsequent set and reset processes are performed originating the re-creation and disruption of the  $V_{os-}$  based conductive filament.

Regarding operation modes, VCM is closely related to bipolar RS. However, it is not clear which polarity of bipolar mode predominates. In general, the polarity of the voltages at which bipolar RS is observed depends on many factors related to the material used for the electrodes, such as the work function or the formation of interface layers [24].

#### 1.1.3.2. Electrochemical metallization

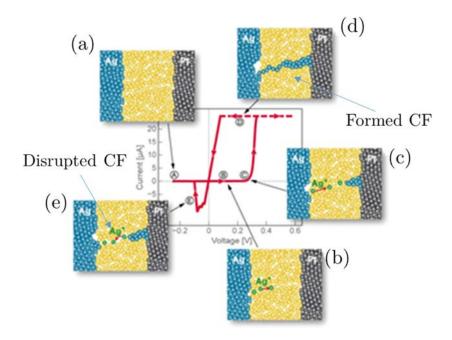

As the valence change mechanism, electrochemical metallization (ECM) is based on ion migration. In this case, metal cations migrate back and forth between an electrochemically active metal (AM) and an electrochemically inert counter electrode (CE) creating and dissolving the metallic conductive filament along a dielectric layer located between both electrodes. Figure 1-10 shows an I-V characteristic of a structure with Ag as active metal, Pt as inert metal and Ge-Se as the dielectric [36]. Some sketches ((a)-(d)) of the structure at important curve points are included.

Initially, when no voltage bias is applied the device is at a pristine (or HRS) state (sketch (a)) and no metal ions migrate from the AM electrode into the dielectric layer. Later, by applying a positive voltage bias to Ag-electrode, metal ions are electrochemically dissolved (sketch (b)) to migrate subsequently through the dielectric being, then, deposited on the surface of CE (sketch (c)) due to reduction and electro-crystallization processes. When a sufficient positive voltage is applied and an adequate number of metal ions have been migrated and deposited, the metal-ionbased conductive filament is created (sketch (d)), forming process has been accomplished at the first step and the device has been switched to LRS state. Now, a negative voltage bias is applied to the device to switch it to HRS state and, therefore, performing the reset process. The resistance change occurs due to an electrochemical dissolution of the metal CF (sketch (e)) helped by Joule heating at the thinnest parts of the filament. When CF has been dissolved completely, the device comes back to LRS state by applying positive voltages again what performs the set process. Applying successively positive and negative voltages, the device can be switched to HRS and LRS, and vice versa, thanks to the creation and dissolution of a metallic filament.

Figure 1-10: Typical I-V characteristic of a Ag/Ge-Se/Pt structure and a complete RS process. (a) Device in pristine state, (b)-(d) creation of the metallic CF by forming process (or set process for subsequent cycles) and (e) dissolution of the CF by reset process [36].

Many works have demonstrated the existence of a metallic CF created and dissolved by ECM mechanism in different materials such as TiO<sub>2</sub>, SiO<sub>2</sub> or ZrO<sub>2</sub> [9]. Likewise, metals like Ag, Cu, Ni or Au have been used as AM [8]. In all of them, repeating the process of applying subsequently positive and negative voltage bias, the device can be switched successively from HRS to LRS (set) and from LRS to HRS (reset) performing a RS cycling. This polarity combination to perform set/reset cycles suggest that the predominant operation mode is the figure-of-eight bipolar mode shown in Figure 1-5(a). A positive voltage is needed to be applied to AM while CE is grounded to provoke the electromigration of the metal cations during set. On the contrary, a negative voltage applied to AM is necessary to provoke the dissolution of the cations during reset process. Therefore, bipolar resistive switching can be explained by VCM and ECM mechanisms. Depending on the dielectric materials and electrodes material either vacancy-based or metallic-based mechanism can illustrate set and reset processes under bipolar RS.

#### 1.1.3.3. Thermochemical reaction

From the works presented by Wun-Cheng Luo et al. in [37] and Xing Wu et al. in [38], thermochemical mechanism (TCM) might be considered as a combination of ECM and VCM. Depending on the polarity of the applied voltage during forming

process the filament can be based on metal ions (ECM) or  $V_{\rm OS}$  (VCM). Consequently, the set process is governed by the diffusion of metal ions or by the migration of  $V_{\rm OS}$ . However, for the reset process, the rupture of the conductive filament is considered to be governed by thermally diffusion instead of ion dissolution.

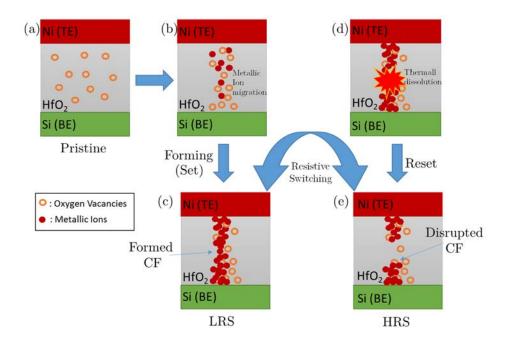

In Figure 1-11, a schematic of a complete RS cycle is depicted for a Ni/NfO<sub>2</sub>/Si MIS-structure. Initially, the device at a pristine state has a random distribution of oxygen vacancies and no metal ions have migrated yet (a). By applying a positive voltage to TE, the migration of metal (Ni) ions and V<sub>o</sub>s begins due to the ECM and VCM mechanisms, respectively. Initially, oxygen vacancies are forced to reorganize as explained in VCM. However, when the applied voltage increases sufficiently, metal ions from TE are able to migrate through the oxide (b) and to be deposited in BE-oxide interface as voltage, and consequently the metal-ion migration, increases [38], [39]. When enough positive voltage is applied, the device reaches the LRS state (c) due to the formation of a conductive filament constituted by V<sub>o</sub>s and metal cations where metallic conduction predominates. Once the CF is created, the forming process

Figure 1-11: Schematic of metallic filament formation and rupture in a TCM device. (a) Initial state of the device before none voltage is applied yet. (b) Metallic ion and vacancies migration when positive voltage is applied to the TE. (c) Device at LRS state when filament is completely formed. (d) Rupture of the filament due to joule heating when positive voltage is applied. (e) Device at HRS state when filament is partially disrupted.

has been performed. With device at LRS state, if a positive voltage bias is applied again to the TE, contrarily to ECM and VCM, conductive filament can be ruptured switching the device to HRS state. As voltage increases, more metal ions (and also oxygen vacancies) migrate increasing the current through the filament. A self-accelerated mechanism occurs producing the increase of temperature, controlled by the applied voltage and current, by Joule heating [40], [41], in the narrowest parts of the filament. At a certain temperature, CF is ruptured by thermal dissolution of the ions that was forming the CF (d). After that, the device reaches the HRS state (e). Applying positive voltages successively over the top electrode, set/reset cycles can be performed.

Therefore, TCM mainly allows explaining the unipolar RS operation mode. However, in a device showing unipolar RS, the bipolar operation mode can be also observed due to the coexistence of  $V_{OS}$  and metallic ions in the CF.

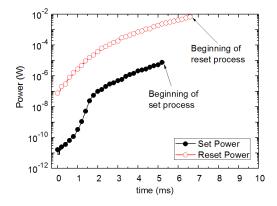

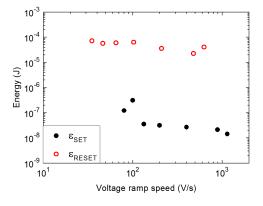

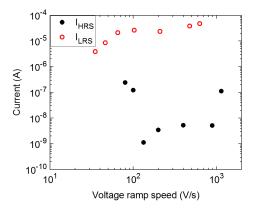

Unlike the mechanism governing set process, which seems well known in all the cases introduced so far, there are still some unsolved questions about the mechanism governing reset process in TCM, such as: does the rupture of the filament occur over the entire CF or just at a certain point? How does the CF shape affect to the process? Or how much amount of power is needed to trigger the process? Some of these questions are partially answered in [42] or [43]. Regarding the latter question related to the power, the work done during this thesis contributes with the analysis of the energies needed to trigger set and reset processes which have been observed to be critical RS parameters (chapter 3).

# 1.2. Reliability issues in resistive switching

As pointed out in the introduction, there are reliability issues affecting the RS functionality. The most concerning are state retention, endurance, variability and random telegraph noise. In this section, a brief overview of them will be included focusing more on the impact of random telegraph noise on RS devices because it has been covered in this thesis.

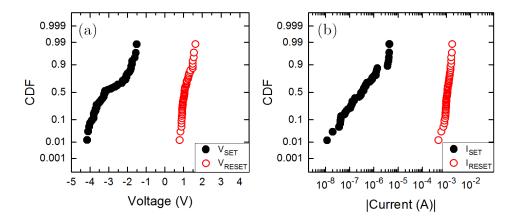

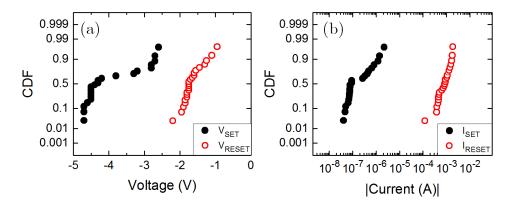

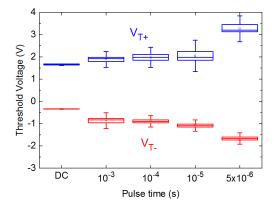

# 1.2.1. Variability

Variability is understood as those fluctuations of RS operation parameters such as forming, set and reset voltages or resistance states (or related currents). Fluctuations refer to any change in the value of a parameter appearing due to the stochasticity of the RS operations mechanisms. They can be observed between different devices (device-to-device), known as spatial variability, or in a single device between the

subsequent set/reset cycles (cycle-to-cycle), known as temporal variability. Another reason for the RS parameters variability is the impact of fixed parameters such as current limit ( $I_C$ ) which can provoke fluctuations in operation parameters when its value is varied. For memristive devices, two kind of variability are differentiated: intrinsic (that variability due to the device itself) and extrinsic (related to the effects originated because of the combination of the memristor with external current limiter devices like a transistor, selector or resistor).

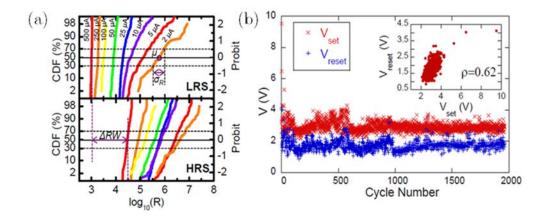

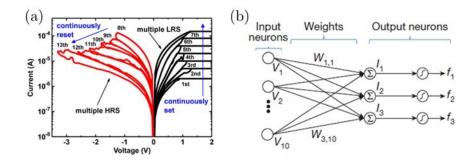

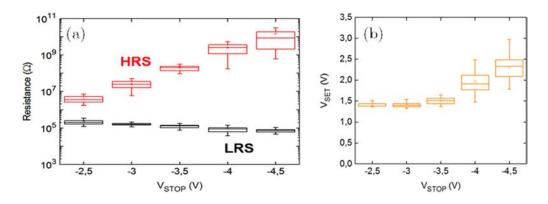

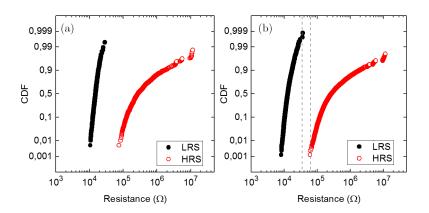

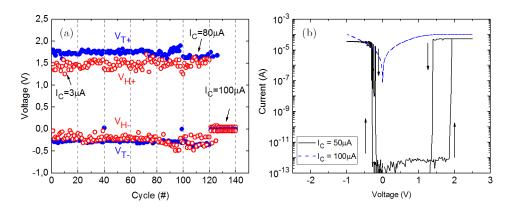

Some examples about RS variability are shown in Figure 1-12(a), where LRS and HRS resistance cumulative distributions of MIM memristors are depicted for different current limits (from 500  $\mu A$  to 2  $\mu A$ ) [44]. A resistance variability increase is observed as current limit decreases. In LRS, for  $I_C=500~\mu A$  the median value,  $\mu$ , of the resistance is  $10^3~\Omega$  while for  $I_C=2~\mu A$ , the median value has suffered a shift to  $\sim 10^6~\Omega$ . In addition, a cycle-to-cycle variability is observed when current limit decreases. When  $I_C$  varies from 500  $\mu A$  to 2  $\mu A$ , cycle-to-cycle variability, identified as the deviation ( $\sigma_R$ ) of the distribution, increases from practically zero to a half of a decade. Similar behavior is observed for HRS resistance.

On the other hand, in Figure 1-12(b) set and reset voltages, extracted from cycling measurements in a MIS-structure memristor, are depicted as a function of the number of cycles [45]. Cycle-to-cycle variability is observed in both set and reset voltages, which authors in [45] attribute to the random creation and dissolution of the metallic conductive filament. Furthermore, they have found that both voltages are statistically correlated by means of the Pearson coefficient as the inset in

Figure 1-12: (a) LRS and HRS resistances cumulative distribution for different current limits. Mean value ( $\mu$ ); deviation value ( $\sigma_R$ ) and resistance window ( $\Delta RW$ ) are indicated [44]. (b) Set and Reset voltages evolution along RS cycling. Inset shows the relation between both set and reset voltages which are correlated by the Pearson coefficiente ( $\rho$ ) [45].

Figure 1-12(b) shows. Regarding dispersion, set voltage shows a range of values between  $\sim 3$  V and  $\sim 4$  V whereas for reset voltage the range is comprised between  $\sim 1$  V and  $\sim 3$  V. Such a set/reset voltage variability provokes an overlap in the operations voltages what can cause malfunction of the device when it is used, for instance, in memory or logic applications.

#### 1.2.2. Retention

Memristive devices are mainly characterized by the non-volatile behavior of their states. However, the retention of those states is not boundless. The increase of the temperature, the operation time or simply the aging can provoke variations on HRS and LRS resistances which originates the retention failure.

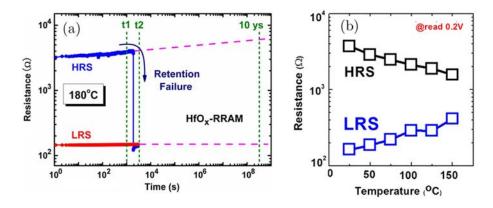

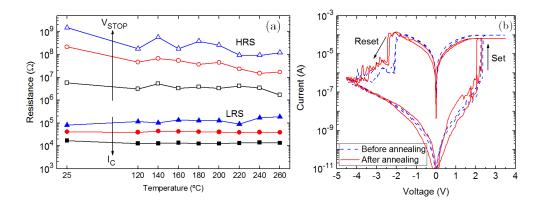

Diverse experimental and simulation studies have been carried out to analyze the behavior of HRS and LRS resistances under different unfavorable conditions. For instance, in [48]–[50], authors have observed a retention failure of HRS state with time. Moreover, they have observed that the resistance at LRS tends to increase with temperature whereas HRS resistance decreases when increasing temperature. A time retention failure example is shown in Figure 1-13(a), where HRS and LRS resistances of devices are measured every 1s under a constant temperature of 180 °C [46]. Until time t<sub>1</sub> both states follow the projected device lifetime of ten years. However, between that time and time t<sub>2</sub>, a retention failure is observed due to a sudden decrease of the HRS resistance. On the other hand, in Figure 1-13(b), a state retention test increasing the temperature is shown. Here, HRS and LRS memristor resistances are

Figure 1-13: (a) HRS and LRS resistances measured every 1 s at 180 °C. After time  $t_1$  the failure of HRS state is observed while LRS state is kept. Modified from [46]. (b) Temperature dependence of HRS and LRS resistances as temperature increases [47] where a resistance window decrease takes place as temperature increases.

measured at different temperatures [47]. Instead of the abrupt retention failure of any resistance state, a progressive degradation of memristor resistance at LRS (increasing) and HRS (decreasing) states is observed.

## 1.2.3. Endurance

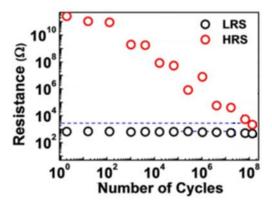

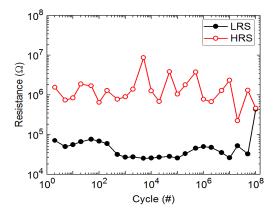

Conceptually, endurance refers to the maximum number of switching cycles performed by a device until the decrease of the resistance window to an inacceptable value or to its complete closure, mostly related to the final failure of the device. Figure 1-14 shows an example of an endurance test of the resistance window for a HfO<sub>2</sub>-based device [51]. As cycling increases, the resistance window decreases and it is completely closed after 10<sup>8</sup> cycles due to the decrease of HRS resistance while LRS remains almost constant. In other studies, the closure of the resistance window has been also observed because of LRS resistance degradation while HRS stays barely unchanged [52] or because of the degradation of both HRS and LRS states [53].

Along the years, endurance has been highly enhanced achieving up to  $10^{12}$  cycles in bipolar RS operation mode [28], [54]. However, that large endurance is difficult to reproduce due to the lack of an absolute control on the stochastic resistance changes. In this way, RS research works have been focused on understanding what provokes the endurance failure in the different devices. For example in [55], authors found that the cause of the endurance failure in  $HfO_X$ -based devices is due to an irreversible set which occurs during the procedure to provoke the reset process.

Endurance and retention failures seems to be a very important reliability issues that are closely related due to their effect on resistance states. Due to that relation, optimizing one might have consequences on the other, so many times a trade-off

Figure 1-14: Resistance window evolution along RS cycling. After  $10^8$  cycles, a complete closure of the window is observed due to the degradation of HRS resistance, modified from [51].

between both reliability issues is necessary. The works performed in [56], [57], show studies on the endurance/retention trade-off on  $HfO_2$ -based and  $Ta_2O_5$ -based memristors, where authors demonstrate relevant improvements in endurance or retention at the cost of slightly getting worse other performance features such as resistance window.

## 1.2.4. Random Telegraph Noise

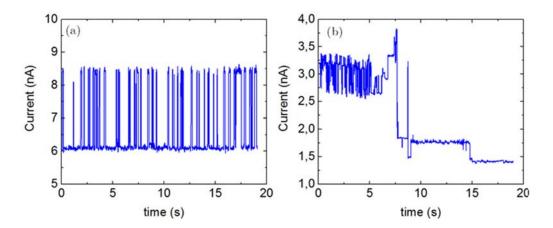

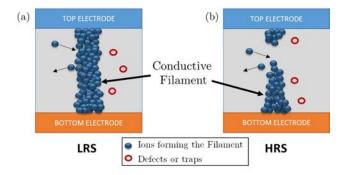

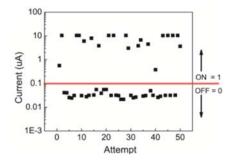

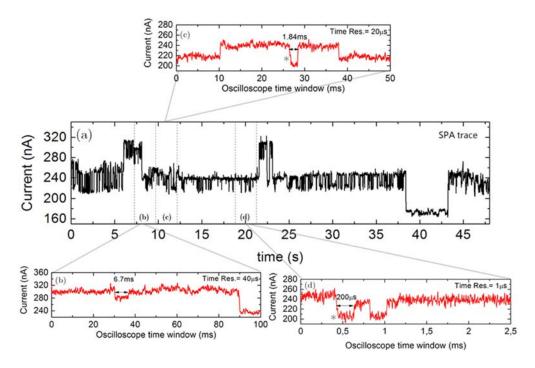

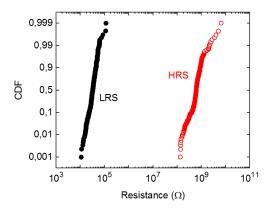

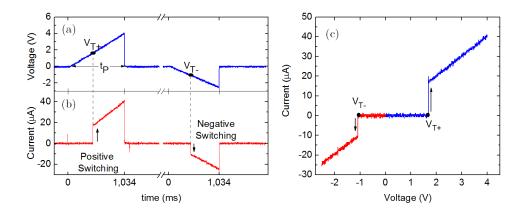

Random Telegraph Noise (RTN) observed in memristive devices consists in random dielectric current fluctuations between two or more discrete states when a constant voltage is applied to the memristor Figure 1-15. Those current fluctuations occur because the electrons flowing through the dielectric (mainly through the conductive filament) can be captured and emitted by existing defects (traps) in the dielectric (Figure 1-15(a)). Furthermore, higher current fluctuations can be observed in RTN signals originated by disturbances in the CF since ions (oxygen vacancies, metal ions), whose nature depends on the RS switching mechanism (VCM, ECM), are added or removed [58], [59] (Figure 1-15(b)). However, these higher fluctuations provoke morphological changes in the CF being more difficult to analyze with standard RTN characterization methods. In Figure 1-16, the two possible scenarios where RTN can appear are depicted for a memristive device (a) at LRS, (CF is completely formed with large current flowing through it) and (b) at HRS (when CF is partially disrupted and the current is typically several orders of magnitude smaller than at LRS state). Considering that most of the current through the dielectric is owing to CF contribution, current contributions can be produced by defects (empty

Figure 1-15: (a) RTN signal where stable current fluctuations between two current levels are observed due to one trap. (b) RTN signal with higher current fluctuations caused by addition or removal of ions to the filament [58].

Figure 1-16: Metal-insulator-semiconductor structure at both (a) HRS and (b) LRS resistances states of RS phenomenon. In both scenarios, defects or traps responsible of RTN fluctuations are placed around conductive filament (red empty circles). Moreover, the addition and removal of ions (solid blue circles) causing higher current fluctuations are indicated by arrows.

red circles) located near the filament (where electrons can be captured or emitted) or by the addition or removal of ions (solid blue circles, the addition or removal is indicated by the arrows) to the filament. As extracted from the previous figure, the RTN impact on filament current is slightly different at LRS than at HRS. In the first one, considering a well-formed filament, current fluctuations are hardly observed since the current is quite large. On the contrary, at HRS the current is much lower and current jumps are easier of being observed. This is the reason why most of the works study RTN at HRS state, although the observation of RTN at LRS has also been reported [59], [60]. Overall, in memristive devices, the presence of RTN can cause a large spread in the distribution of the HRS and LRS resistances and induce errors, for instance, reading the wrong memory state stored in the memristor if the memory window is relatively small.

#### RTN characterization

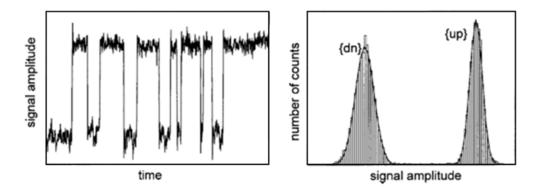

Just regarding current fluctuations due to traps, detection of RTN signals can also serves as a tool to determine the number of traps, the characteristic times of the trap (as the emission  $(\tau_e)$  and capture  $(\tau_C)$  times), the spatial trap location from dielectric-electrode interface and the trap energy depth below conduction band of dielectric [61], [62]. Nevertheless, before identifying trap properties, RTN signal must be properly characterized. The simplest way to analyze those signals is plotting every point of the current of a RTN trace in a histogram which is quite feasible when the fluctuations are only between two levels as shown in Figure 1-17. However, as the complexity of the RTN signal increases either due to the enlargement of the background noise or the rising of number of traps, analysis methods must be enhanced. Different methods to analyze and characterize RTN have been developed [63] but those based on that proposed in [62] have become the most common. In [62]

Figure 1-17: An experimental random telegraph signal showing two current levels. The histogram plot of the previous RTN signal. Two amplitude histograms (dn and up) corresponding to the current levels appear well differentiate without overlapping [64].

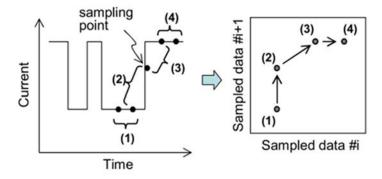

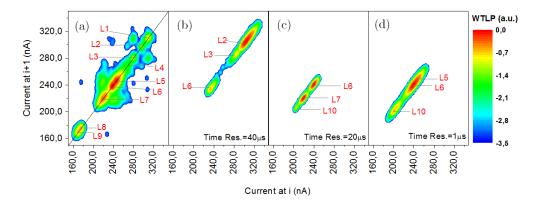

authors presented a method to study RTN signals which uses a Time Lag Plot (TLP). Figure 1-18 shows an explanation to get such a plot. The (i+1)-th current points of a RTN signal (left) are plotted against i-th current points of the same RTN signal to obtain the individual points shown in Figure 1-18 (right). In this plot, points located along the diagonal of the plot correspond to the current levels (points 1 and 4) whereas points outside the diagonal indicate the transitions occurred between those levels (points 2 and 3).

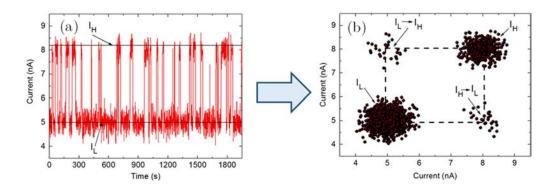

As an example, Figure 1-19(a) shows a current trace corresponding to a simulated one-defect RTN signal, what means that only two current levels exist. Applying the previous method, the TLP depicted in Figure 1-19(b) is obtained revealing four point clusters. Those located at the diagonal of the plot indicate the current levels of the RTN signal, identified as high ( $I_H$ ) and small ( $I_L$ ) current. On the contrary, the other two point clusters outside of the diagonal reflect the transitions between currents

Figure 1-18: Explanation of how to create a time lag plot (TLP) from a current trace [62].

Figure 1-19: (a) Simulated RTN signal caused by a single defect. (b) The corresponding time-lag plot: two populated clusters on the main diagonal indicate the two levels. Other clusters of points outside the diagonal correspond to transition between levels.

levels (from  $I_L$  to  $I_H$  and from  $I_H$  to  $I_L$ ). Note that a one-defect RTN signal creates a square in whose vertexes those clusters are located. Based on the number of clusters placed along the diagonal, that is, the number of RTN current levels, authors in [62] proposed a way to determine the number of detectable traps. Considering that  $2^{(n-1)}$  < (current levels)  $\leq 2^n$ , then the number of detectable traps originating current fluctuations corresponds to n.

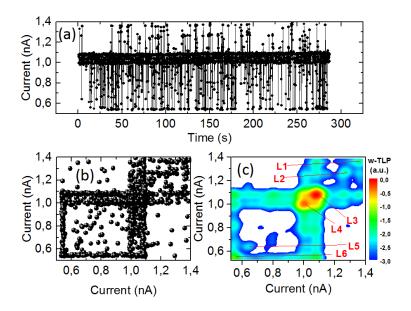

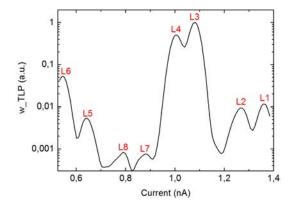

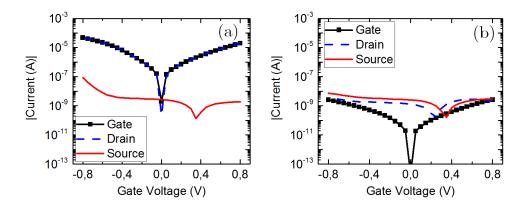

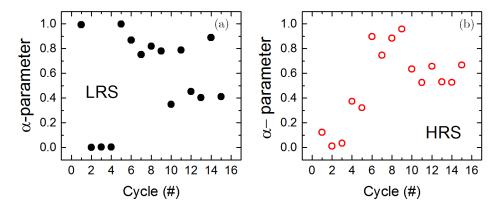

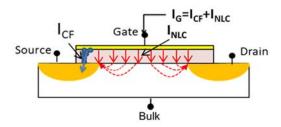

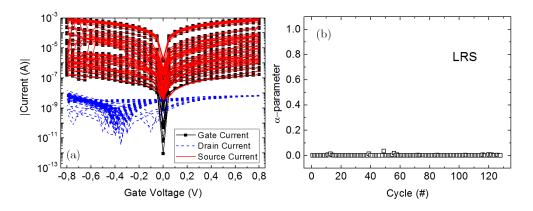

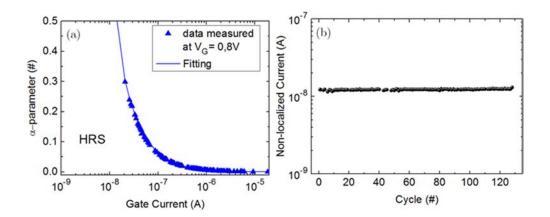

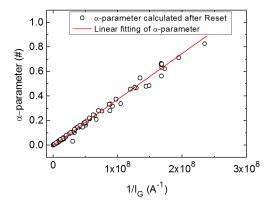

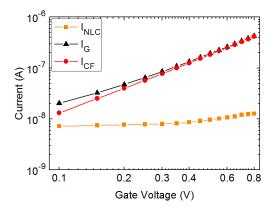

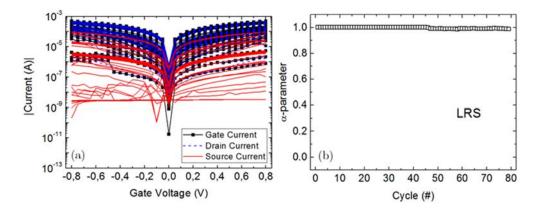

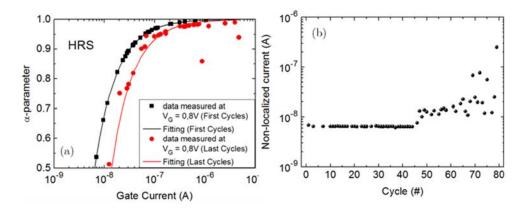

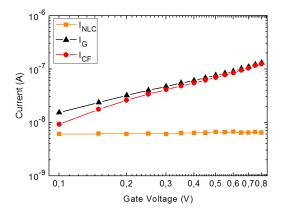

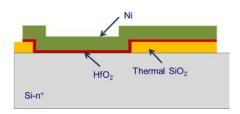

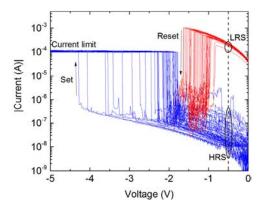

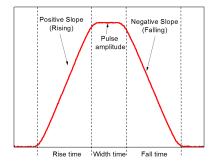

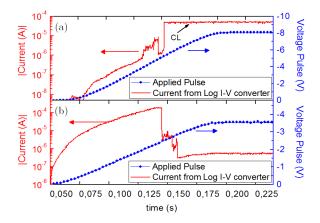

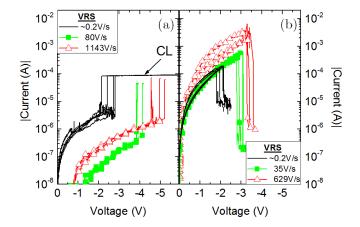

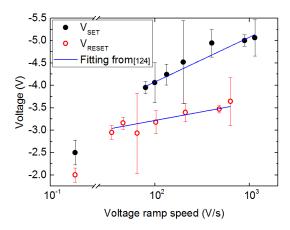

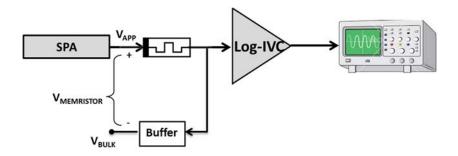

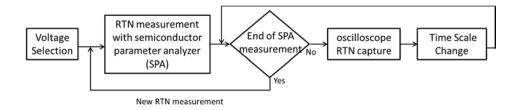

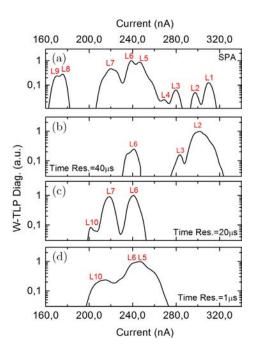

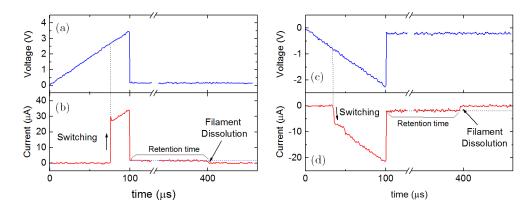

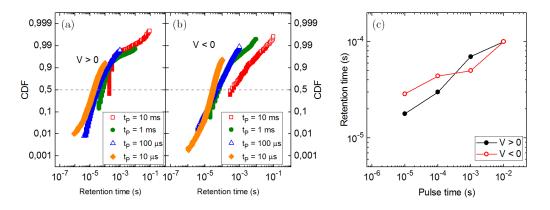

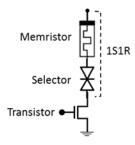

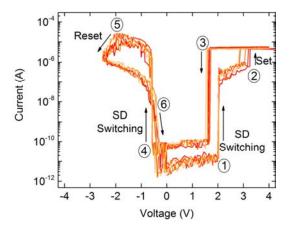

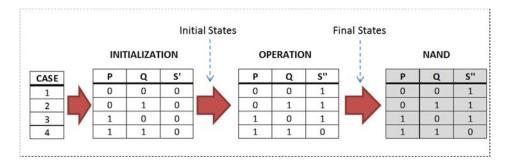

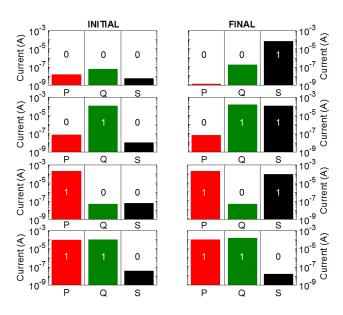

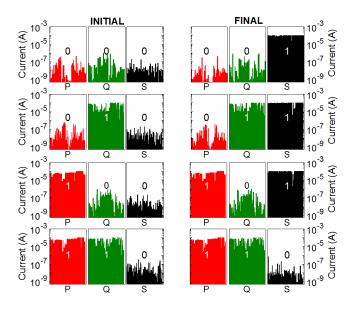

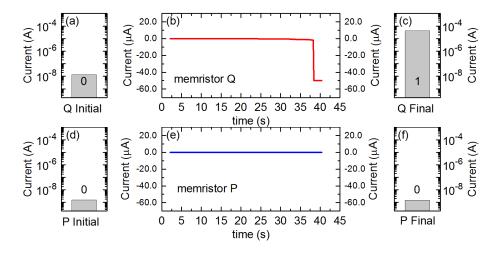

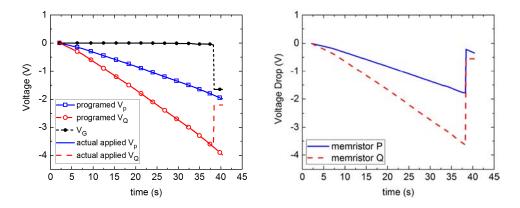

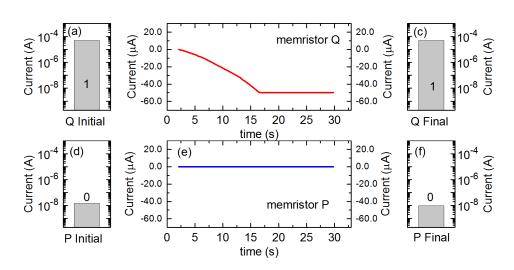

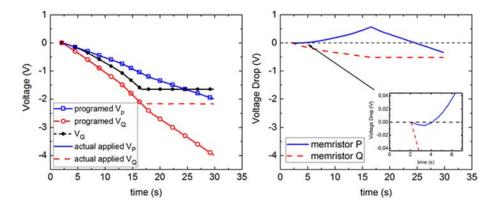

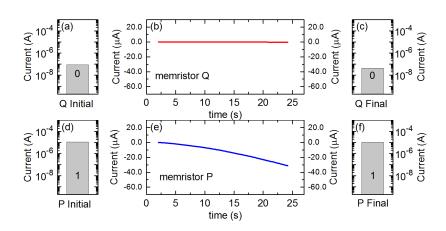

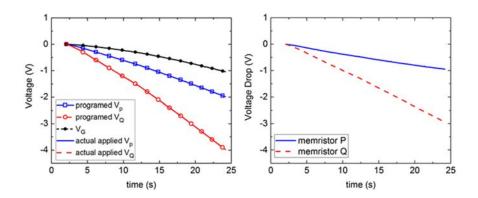

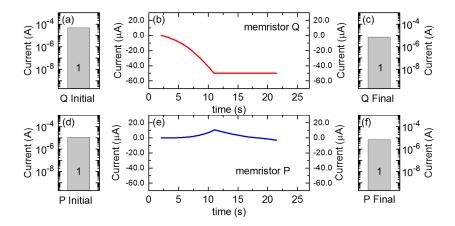

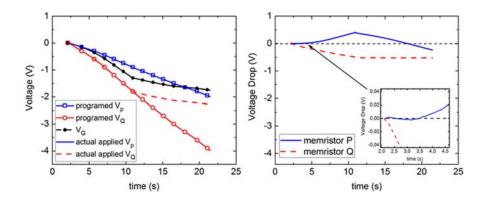

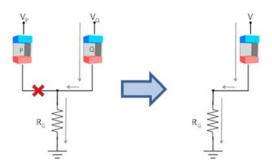

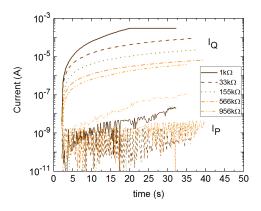

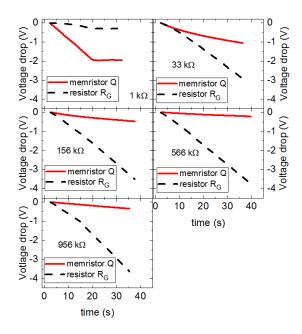

Despite the fact that TLP method is very useful when the RTN current fluctuations are well defined, it becomes limited when the background noise is more relevant or when multilevel RTN signals are measured since different clusters can overlap each other. To overcome those limitations, in [65], an enhanced RTN characterization method named Weighted Time Lag (W-TL) is proposed. The method mainly improves TLP-based method minimizing the effect of the background noise in a RTN signal. The W-TLP method calculates a weighted function, which is based on a normal bivariate distribution of i-th point and (i+1)-th point, on each dot in TLP. Then, the weighted function is plotted as a contour plot where x and y-axes correspond to the current of i-th and (i+1)-th points, respectively (Figure 1-20(c)). On the other hand, the color map of the figure represents the weighted function (in arbitrary units) being 0 (red) the value of most populated region of the plot and -3 (blue) the value of empty region.