# Improving Heterogeneous System Efficiency: Architecture, Scheduling, and Machine Learning

Daniel A Nemirovsky Department of Computer Architecture Universitat Politècnica de Catalunya

A thesis submitted for the degree of Doctor of Philosophy in Computer Architecture

October, 2017

**Director:** Dr. Adrian Cristal **Codirector:** Prof. Mateo Valero

For Kim

## Abstract

Computer architects are beginning to embrace heterogeneous systems as an effective method to utilize increases in transistor densities for executing a diverse range of workloads under varying performance and energy constraints. As heterogeneous systems become more ubiquitous, architects will need to develop novel CPU scheduling techniques capable of exploiting the diversity of computational resources. In recognizing hardware diversity, state-of-the-art heterogeneous schedulers are able to produce significant performance improvements over their predecessors and enable more flexible system designs. Nearly all of these, however, are unable to efficiently identify the mapping schemes which will result in the highest system performance.

Accurately estimating the performance of applications on different heterogeneous resources can provide a significant advantage to heterogeneous schedulers for identifying a performance maximizing mapping scheme to improve system performance. Recent advances in machine learning techniques including artificial neural networks have led to the development of powerful and practical prediction models for a variety of fields. As of yet, however, no significant leaps have been taken towards employing machine learning for heterogeneous scheduling in order to maximize system throughput.

The core issue we approach is how to understand and utilize the rise of heterogeneous architectures, benefits of heterogeneous scheduling, and the promise of machine learning techniques with respect to maximizing system performance. We present studies that promote a future computing model capable of supporting massive hardware diversity, discuss the constraints faced by heterogeneous designers, explore the advantages and shortcomings of conventional heterogeneous schedulers, and pioneer applying machine learning to optimize mapping and system throughput. The goal of this thesis is to highlight the importance of efficiently exploiting heterogeneity and to validate the opportunities that machine learning can offer for various areas in computer architecture.

**Keywords:** Computer Architecture, Multi Core, Heterogeneous Systems, Scheduling, Machine Learning, Deep Learning

# Acknowledgements

Working to achieve a PhD is a unique adventure to experience. It is unlike anything I have ever experienced. An era that has been altogether marvelous in its own right, both its soaring peaks and excruciating valleys, surely to be warmly rekindled as a collection of moments frozen in memory that one is fond to call their own. It is a remarkable journey that navigates one to explore and understand, to create and withstand. Above all else, it is a trial of one's very own perseverance and dedication. An impassable mountain were it not for the mentorship, camaraderie, and tireless support of one's advisors, colleagues, friends, and family.

So here, on these two humble pages, I shall try and undoubtedly fail to express my sincerest gratitude to all those who have been a part of this expedition at one time or another.

I would first like to thank my advisors Dr. Adrian Cristal and Professor Mateo Valero for accepting me into their research group and guiding my work. Mateo is a tremendously capable professional, highly intelligent and motivational. His leadership has fostered an outstanding academic atmosphere that I was fortunate to be a part of. I greatly appreciate the opportunity that you have given me.

There are few individuals that I have had the pleasure of working alongside that I consider geniuses in their respective fields but Dr. Adrian Cristal is certainly one. He has provided a guiding hand in all aspects of my research and has continually inspired me with his ability to clarify any technical barriers with the utmost ease. I would also like to thank Dr. Osman Unsal who was the co-director of our research group and has been a wonderful unofficial advisor. Technically adept, Osman is responsible for shaping a great deal of my research and has always provided me with excellent advice for turning my abstract ideas into practical approaches.

I would like to also extend my gratitude to the members of my defense committee and reviewers of my thesis for your time and detailed as well as constructive critiques. They include: Dr. Adria Armejach, Dr. Vasilis Karakostas, Dr. Oscar Palomar, Dr. Gulay Yalcin, Dr. Antonio Cortes, and Dr. Petar Radojković.

The outstanding and friendly staff at the Barcelona Supercomputing Center and UPC's Departament d'Arquitectura de Computadores, especially Joana Munuera, deserve much recognition for their support over the years from dealing with all of us eccentric engineers.

I was fortunate to have brilliant colleagues which turned into great friends including Nikola Marković, Nehir Sonmez, Oriol Arcas, Ivan Ratković, Milan Stanić, Tugberk Arkose, Mladen Slijepcević, Behzad Salami, Damian Roca, Francesco Ciaccia, Josue Esparza, Javier Arias, and Vladimir Gajinov.

I would like to also thank my friends and family for their support over these years, especially my loving parents Laura and Mario and sister Michelle for their boundless dedication and encouragement. And to my other and better half, Kim, you're enduring patience and love I could not imagine living without.

# Contents

| 1 | Intr | Introduction |                                         |    |  |  |

|---|------|--------------|-----------------------------------------|----|--|--|

|   | 1.1  | Proble       | em statement and objectives             | 3  |  |  |

|   | 1.2  | Scope        | of the thesis                           | 3  |  |  |

|   |      | 1.2.1        | Machine learning                        | 4  |  |  |

|   |      | 1.2.2        | CMPs                                    | 4  |  |  |

|   |      | 1.2.3        | Scheduling                              | 5  |  |  |

|   |      | 1.2.4        | Workloads                               | 5  |  |  |

|   | 1.3  | Key cł       | hallenges                               | 5  |  |  |

|   | 1.4  | Thesis       | s contributions                         | 7  |  |  |

|   |      | 1.4.1        | Reimagining heterogeneous computing     | 7  |  |  |

|   |      | 1.4.2        | Preliminary studies                     | 8  |  |  |

|   |      | 1.4.3        | Applying ML to heterogeneous scheduling | 9  |  |  |

|   | 1.5  | Thesis       | soutline                                | 10 |  |  |

| 2 | Mot  | tivation     | l                                       | 13 |  |  |

|   | 2.1  | Backg        | round                                   | 13 |  |  |

|   |      | 2.1.1        | Chip Multi-processors (CMPs)            | 13 |  |  |

|   |      | 2.1.2        | Caches                                  | 15 |  |  |

|   |      | 2.1.3        | Program structures and behaviors        | 17 |  |  |

|   |      | 2.1.4        | CMP scheduling                          | 22 |  |  |

|   |      | 2.1.5        | Machine learning                        | 27 |  |  |

|   | 2.2 | Reimagining Heterogeneous Computing | 0 |

|---|-----|-------------------------------------|---|

|   |     | 2.2.1 Conceptual discussion         | 2 |

|   |     | 2.2.2 Functional ISA                | 4 |

|   |     | 2.2.3 Example case                  | 6 |

|   |     | 2.2.4 Conclusion                    | 0 |

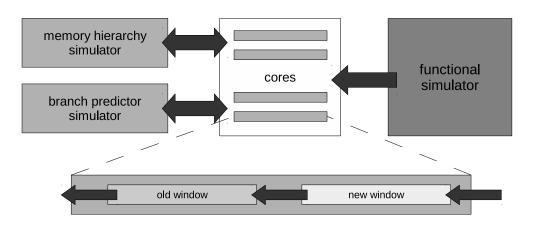

| 3 | Met | nodology 4                          | 1 |

|   | 3.1 | Simulator                           | 1 |

|   | 3.2 | CMP architecture                    | 5 |

|   | 3.3 | Benchmarks                          | 6 |

|   |     | 3.3.1 SPEC2006                      | 6 |

|   |     | 3.3.2 SPLASH-2                      | 7 |

|   | 3.4 | Schedulers                          | 0 |

|   | 3.5 | Artificial neural networks (ANNs)   | 2 |

|   | 3.6 | Measuring Error and Results         | 3 |

# I Preliminary Studies on the Potential of Heterogeneous Architectures 55

| 4 | Exte | Extending the flexibility of ACMPs for mobile devices using alternative |                            |    |  |

|---|------|-------------------------------------------------------------------------|----------------------------|----|--|

|   | cach | e config                                                                | gurations                  | 59 |  |

|   | 4.1  | Motiva                                                                  | ation                      | 60 |  |

|   |      | 4.1.1                                                                   | Cache footprint            | 61 |  |

|   | 4.2  | Altern                                                                  | ative cache configurations | 63 |  |

|   | 4.3  | Metho                                                                   | odology                    | 65 |  |

|   |      | 4.3.1                                                                   | Processor configuration    | 65 |  |

|   |      | 4.3.2                                                                   | Benchmark execution        | 65 |  |

|   | 4.4  | Experi                                                                  | iments and evaluation      | 66 |  |

|   | 4.5  | Future                                                                  | e work                     | 71 |  |

|   | 4.6  | Conclu                                                                  | usion                      | 71 |  |

| 5              | Performance and energy efficient hardware-based scheduler for symmet-  |        |                                                             |           |

|----------------|------------------------------------------------------------------------|--------|-------------------------------------------------------------|-----------|

|                | ric/asymmetric CMPs                                                    |        |                                                             |           |

|                | 5.1                                                                    | Threa  | d lock section-aware scheduling (TLSS)                      | 74        |

|                |                                                                        | 5.1.1  | TLSS algorithm                                              | 74        |

|                |                                                                        | 5.1.2  | Hardware implementation discussion                          | 76        |

|                |                                                                        | 5.1.3  | Hardware versus Software implementation                     | 78        |

| 5.2 Evaluation |                                                                        |        |                                                             | 78        |

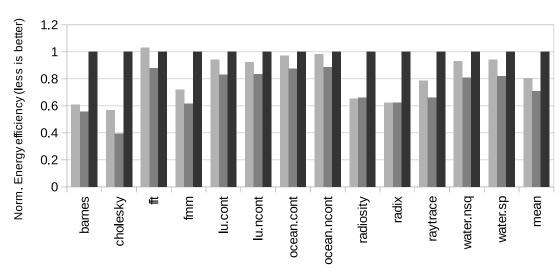

|                |                                                                        | 5.2.1  | Performance per Watt Evaluation                             | 79        |

|                |                                                                        | 5.2.2  | Performance evaluation of TLSS on a many core ACMP          | 82        |

|                |                                                                        | 5.2.3  | Energy efficiency comparison of the different schedulers on |           |

|                |                                                                        |        | an ACMP over an SCMP                                        | 84        |

|                | 5.3                                                                    | Concl  | usion                                                       | 87        |

|                |                                                                        |        |                                                             |           |

| Π              | Aj                                                                     | pplyir | ng ML to Heterogeneous Scheduling                           | <b>89</b> |

| 6              | 6 A Machine Learning Approach for Performance Prediction and Heteroge- |        |                                                             |           |

|                | neo                                                                    | us CPU | Scheduling                                                  | 95        |

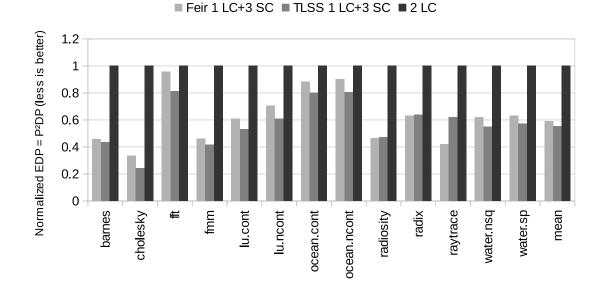

|                | 6.1                                                                    | ML ba  | ased heterogeneous scheduling                               | 96        |

|                |                                                                        | 6.1.1  | Parameter engineering                                       | 98        |

|                |                                                                        | 6.1.2  | Next quantum thread-behavior predictor (NQP)                | 99        |

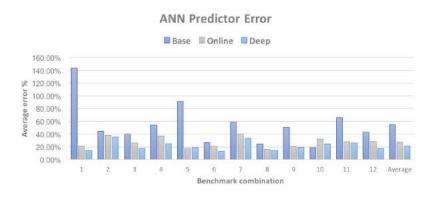

|                |                                                                        | 6.1.3  | ANN performance predictors                                  | 101       |

|                |                                                                        | 6.1.4  | Mapping                                                     | 108       |

|                | 6.2                                                                    | Evalua | ation                                                       | 109       |

|                |                                                                        | 6.2.1  | Methodology                                                 | 109       |

|                |                                                                        | 6.2.2  | Results                                                     | 111       |

|                | 6.3                                                                    | Future | e work and conclusion                                       | 114       |

| 7              | A D                                                                    | eep Le | arning Mapper (DLM) for Heterogeneous Scheduling            | 117       |

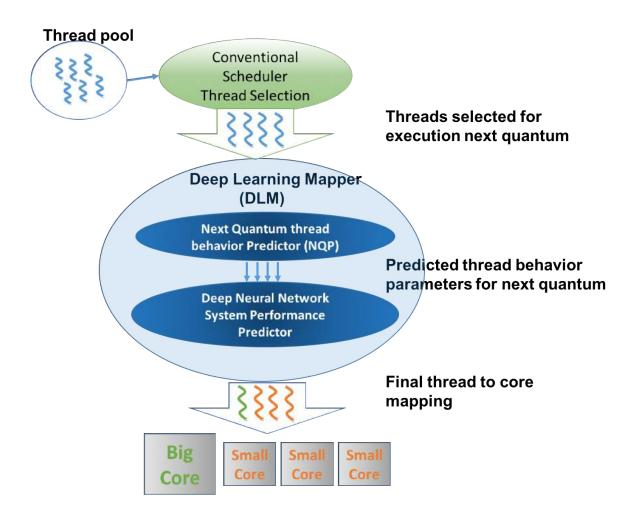

|                | 7.1                                                                    | Sched  | uling model                                                 | 118       |

|                |                                                                        | 7.1.1  | Deep learning mapper (DLM)                                  | 120       |

|                |                                                                        | 7.1.2  | Overheads                                                   | 126       |

|                | 7.2                                                                    | Evalua | ation                                                       | 127       |

|                |                                                                        | 7.2.1  | Methodology                                                 | 127       |

|     | 7.3             | Future Work and Conclusion                                       | 129 |  |

|-----|-----------------|------------------------------------------------------------------|-----|--|

| 8   | Rela            | ted Work                                                         | 131 |  |

|     | 8.1             | Heterogeneous architectures                                      | 131 |  |

|     | 8.2             | Scheduling                                                       | 132 |  |

|     | 8.3             | Machine learning for systems                                     | 134 |  |

|     | 8.4             | Programming/analytical models and unconventional architectures . | 135 |  |

| 9   | Con             | clusion                                                          | 139 |  |

| 10  | Pub             | lications                                                        | 143 |  |

|     | 10.1            | Publications from the thesis                                     | 143 |  |

|     | 10.2            | Publications not included in the thesis                          | 144 |  |

| Lis | List of Figures |                                                                  |     |  |

| Lis | List of Tables  |                                                                  |     |  |

| Bil | bliog           | raphy                                                            | 155 |  |

## Introduction

The field of computer architecture has been evolving over the last decade to embrace multi and many core (i.e., chip multi-processors or CMP) designs and more than ever, resource heterogeneity in terms of CPU and accelerator diversity found within systems on a chip (SoC). CMPs have become so readily utilized that they can be found in severs, desktops, laptops, mobile devices, and automated devices making part of the Internet of Things (IoT). Each of these devices may be used for running different workloads under specific circumstances, and within certain constraints. With processor fabrication technology currently at 7nm [25] and expected to reach 5nm by 2020, the advances in transistor densities have provided substantial opportunities for architects to combine even more general purpose cores, GPUs, accelerators, and cache memory onto a single system on a chip (SoC). Exploring heterogeneous solutions, however, requires studying microarchitecture as well as novel tools and approaches for optimization within the context of performance, energy consumption, and physical size or environment requirements.

Diversity is also found within the workloads that a CMP may need to execute. Applications may behave in very different manners from one another depending upon their program structure, computational, memory, I/O requirements, and parallelism. The rich heterogeneity of applications and system requirements is nicely complemented by the heterogeneity found in state-of-the-art CMPs such as ARM's big.LITTLE [38] and Nvidia's Tegra3 [74]. Extrapolating the trend of exploiting transistor density increases using heterogeneity, systems of the future may include

### **1. INTRODUCTION**

hundreds or thousands of accelerators specialized for executing common libraries, kernels, or even whole programs.

In order to effectively support current and future heterogeneous architectures, single and multi-threaded applications must be properly managed by a heterogeneous scheduler. An effective scheduler should be aware of a system's diverse computational resources and how threads perform and interfere with one another on different cores. Heterogeneous scheduling uses its knowledge to periodically determine which threads to assign to specific cores. This process, otherwise known as mapping, is critical to perform efficiently in order to exploit hardware diversity and maximize system performance. An efficient heterogeneous scheduler can provide significant performance and energy benefits to heterogeneous CMPs compared with typical schedulers targeted for homogeneous systems. As a result, heterogeneous scheduling can provide architects with added flexibility in their design choices including the number of and types of cores as well as the cache configuration.

The design opportunities provided by heterogeneous schedulers are significant and provide insightful studies. There is, however, still room for improvement over state-of-the-art heterogeneous schedulers regarding the mapping scheme. Current schedulers, which make use of a priority [54] or round-robin [72] based heuristic to determine the mapping scheme, are not capable of predicting a mapping scheme to maximize system performance. To do so, a scheduler must know or at least be able to predict what the system performance would be for different mapping options and then select the one that results in the highest value. The correct approach and set of tools to use in order to predict system performance for different mapping options could require identifying behavioral statistics for an executing thread and finding relationships between these statistics and the thread's resulting performance on the different core types.

Managing and mapping threads is a problem that shares similarities with recommendation and navigation systems both of which have benefitted using machine learning (ML) techniques [62, 60, 16]. Though heterogeneous scheduling is a popular area of research, there has yet been no work exploring the use of ML for mapping optimization. In fact, using ML techniques to optimize computer systems has been as a whole seldom explored (see Chapter 8.3). The work in this thesis serves to demonstrate the practicality and improvements that can result by applying ML towards optimizing computer systems.

Artificial neural networks (ANNs) in particular are beginning to be utilized in a wide variety of fields due to their great promise in learning relationships between input data and numerical or categorical outputs [42]. The relationships are often hard to identify and program for manually, but using ANNs can result in excellent prediction accuracies. ANN based predictors have been shown to be useful in accurately predicting target categories and values for a wider variety of fields such as predicting network traffic [12] and stock market prices [39]. Moreover, feedforward ANNs such as those used in this work are lightweight in both computation and memory overheads and can be easily accelerated using GPUs or specialized hardware [103].

## **1.1 Problem statement and objectives**

Given the contextual descriptions mentioned above, the problem statement of this thesis is how can we understand and utilize the rise of heterogeneous architectures, the benefits of heterogeneous scheduling, and the promise of machine learning techniques with respect to maximizing system performance. The purpose of this thesis is to highlight the importance of effectively exploiting heterogeneous systems, demonstrate the usefulness that ML can provide to heterogeneous scheduling, and in doing so, highlight the potential that ML can offer for various areas in computer architecture. To our knowledge, this work is the first to apply artificial neural network machine/deep learning techniques to heterogeneous scheduling.

The rest of this chapter describes an overview of the scope of the thesis, key challenges, contributions, and thesis outline.

## **1.2** Scope of the thesis

This thesis touches upon the fields of machine/deep learning, heterogeneous architectures, CPU scheduling, and multitasking. Described in this section is the scope

### **1. INTRODUCTION**

of which this thesis goes into depth in each of these areas. More details about each of these topics is provided in section 2.1.

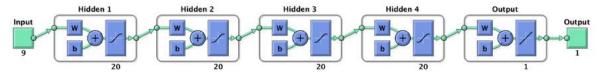

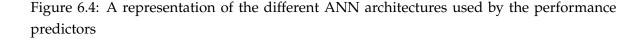

## 1.2.1 Machine learning

This work examines ML centered around artificial neural networks (ANNs) and deep ANNs (DNNs). These models are used for predicting performances of threads or of a whole system and are composed of layers of artificial neurons that are trained to develop relationships between the input parameters and the output target. The architectures of the specific ANNs used in this work is described in detail in Part II entitled "Applying ML to Heterogeneous Scheduling."

## 1.2.2 CMPs

Heterogeneous architectures can include various general purpose as well as accelerator computational cores within a system on a chip (SoC). There are two main types of heterogeneity that are explored within the scope of this thesis. The first is based on the hardware resource diversity of all hardware elements found within a SoC such as a CPU, a graphical processing unit (GPU), digital signal processor (DSP), and other accelerators. This can be considered more of a macro type of heterogeneity since the diversity is found between the different resources each of which serves a different purpose.

In contrast, the second type of heterogeneity that is explored in depth in this thesis is what can be referred to as micro heterogeneity or in other words, diversity between resources dedicated to a similar purpose. This can include diversity between different cores in a CPU related to microarchitectural differences. Conventional CMPs either rely on homogeneous cores (known as symmetric CMPs or SCMPs) or on cores which share an Instruction Set Architecture (ISA) but differ in terms of performance or functionality (referred to as asymmetric CMPs or ACMPs). ACMPs have been shown to be able to outperform SCMPs for a fixed area or power budget [81], [83] and are attractive candidates to exploit diverse workloads and performance requirements. In this thesis, we explore the reaches of

heterogeneous diversity but our contributions are primarily applied to ACMP architectures since they are currently the most popular conventional implementations of heterogeneous systems.

## 1.2.3 Scheduling

The growth of heterogeneous architectures has led to a reexamination of scheduling mechanisms to exploit the resource diversity. Schedulers are typically responsible for CPU resource allocation for executing processes aimed at maximizing overall CPU utilization. This work focuses on exploring different practical techniques to optimize the scheduling mechanisms which are responsible for (i) selecting threads to execute and (ii) mapping those threads onto the hardware cores. The selection process is important in order to guarantee fairness in terms of execution time provided to all available threads, and the mapping process is critical for exploiting the system resources given different workload characteristics. The scheduler is called periodically (i.e., after every scheduling quantum which is typically within the range of 1ms-4ms) to reassess the selection and mapping schemes.

## 1.2.4 Workloads

Scheduling is critical in CMP systems when performing multitasking and executing parallel applications. Different applications and individual threads behave differently on the distinct hardware cores and may affect the performance of other neighboring threads (for example by causing interference in the shared resources). In this thesis, we evaluate various computational and memory intensive single and multi-threaded benchmarks. We explore how their diverse behaviors affect the abilities of our performance predictors and heterogeneous schedulers.

## 1.3 Key challenges

Each of the areas considered within the scope of this thesis consists of particular constraints and challenges.

### **1. INTRODUCTION**

For heterogeneous architectures, this involves identifying the performance, energy, and size requirements as well as what types of hardware resource diversity can be practically implemented. It is important to examine the advantages and disadvantages that result from composing CMPs using different core types, memory structures, and accelerators for executing diverse workloads under specific constraints. Crafting an analytical framework is a powerful method that can help with analyzing different heterogeneous implementations.

For scheduling, the challenges include identifying the mechanisms and shortcomings of current techniques, heuristics and tools that could improve these mechanisms, and the feasibility of proposed implementations. Judging the practicality of the proposed implementations combines balancing the performance benefits that arise from the proposal with the overhead costs imposed which can include quantifying the scheduling or algorithm computation cost, context swaps, and the runtime statistics needed to be gathered.

A similar set of challenges can be found when applying ML techniques to the mapping mechanism of a scheduler. Though numerous ML models could be useful in predicting system performance, each model may result in different accuracies, implementation practicality, and overhead costs. After a certain level of complexity, the gains in performance from using ANNs may be outweighed by the overhead costs owing to the amount of calculations needed to be performed and/or the parameters needed to be gathered and stored.

Finally there is the challenge of determining the experimental framework including simulators and benchmark suites with which to conduct our studies and validate our proposals. The simulator should be hardware validated, accepted by the community, and be able to accurately model numerous heterogeneous cores and scheduling mechanisms. The benchmarks should be representative of the environments that are targeted by the proposals and include computational, memory, and I/O intensive single and multi-threaded workloads. It is necessary for the chosen simulator to present performance, energy, and physical area results of the different experiments. The scalability of the proposals is also a challenge pertinent to design practicality and should be tested using a simulator that can accommodate increasing the number and diversity of cores and benchmarks.

## 1.4 Thesis contributions

Our main contributions can be divided into two parts. Part I consists of a motivating contribution highlighting a long term vision for massively heterogeneous systems and two preliminary studies which explore the benefits that heterogeneous schedulers can provide for energy savings and architecture flexibility. Part II is composed of studies which justify and validate applying ML models to heterogeneous scheduling, resulting in significant performance improvements and implications for computer architecture as a whole. Specifically, we describe a pioneering proposal to decouple a scheduler's thread selection and mapping function, and apply machine/deep learning to predict thread and system performance at the quantum granularity. Below we provide a brief overview of each of the main contributions in this work.

## 1.4.1 Reimagining heterogeneous computing

A semantic gap seems to be emerging between the advances in hardware and software in terms of resource and program diversity and the use of high abstraction levels. This is due to the physical and compatibility constraints that hardware developers face, which are far more flexible at the software level. However, given the current state of the industry, architects need to consider radical paradigmshifting computing-model proposals. Such proposals will not necessarily offer clear roadmaps or practical short-term solutions, but they could contain the hints and alternate ideas needed to rethink the long-term vision that computer architects hope to achieve.

In this motivating work, we address an emerging hardware-software semantic gap by considering an unconventional computing model that merges current heterogeneous state-of-the-art hardware with the concept of abstraction that has been very useful and ubiquitous in software. To do so, we use the concept of abstraction to reinterpret the notion of the ISA. Most ISAs in use today remain (for compatibility reasons) based on designs developed several decades ago to solve that era's physical and software constraints. The current CMP model's scalability is inherently constrained because of the current ISA's functional granularity, which intro-

## **1. INTRODUCTION**

duces high memory footprint and energy consumption. As a remedy, we propose a functional ISA (F-ISA) that increases the functional abstraction level of the machine instructions. Consequently, this extra level of functional abstraction enables a dramatic increase in the heterogeneous diversity of a processor's computational units, resulting in greater specialized execution particular to the needs of the software algorithms. We hope that this alternative computational model can significantly improve and fine-tune system performance relative to latency, memory footprint, and power.

## 1.4.2 Preliminary studies

Drawing inspiration from how heterogeneous system may look like in the future from the subsection mentioned above, the objective of the preliminary studies is to examine the opportunities and limitations present in current CMP and scheduling designs. We believe this discussion presents a realistic starting point in order to acquire several key insights instrumental for advancing towards the future of heterogeneous architectures. Each of the following two contributions provides separate investigations into analyzing CMP design tradeoffs, and improving performance and energy efficiency.

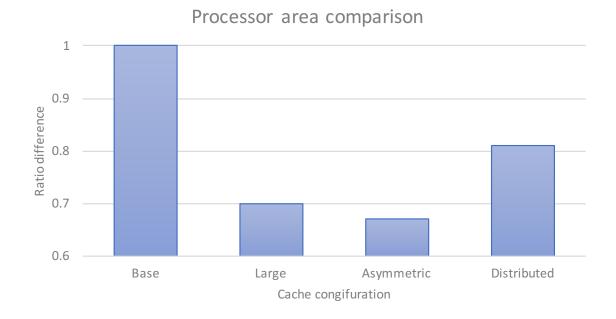

# Extending the flexibility of ACMPs for mobile devices through alternative cache organizations

The focus of this work is to highlight how architects can optimize the energy efficiency and size of ACMP systems by using novel memory configurations. This approach offers a method to tailor an ACMP system to provide suitable performance, energy efficiency, and area for very demanding mobile devices. We propose three alternative cache configurations and examine their effects on system performance and processor size when executing applications concurrently. Our results show that adopting an alternative cache hierarchy in conjunction with a scheduler targeting asymmetrical systems can lead to substantial energy savings of over 17%, power reductions of over 5%, and over 19% reductions in physical size while still outperforming execution times achieved with conventional operating system schedulers on a CMP with larger caches by over 10%.

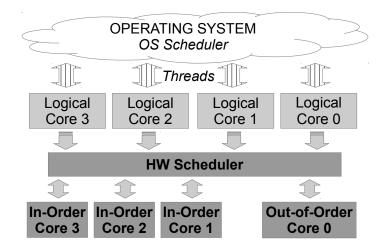

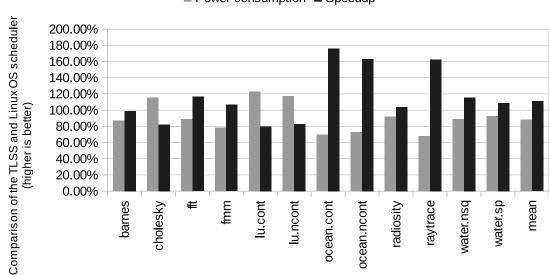

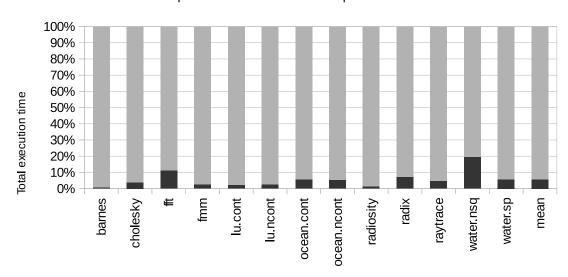

# Performance and energy efficient hardware-based scheduler for Symmetric/Asymmetric CMPs

Since more and more applications become multi-threaded we expect to find a growing number of threads executing on a machine. Consequently, the operating system will require increasingly larger amounts of CPU time to schedule these threads efficiently. Instead of perpetuating the trend of performing more complex thread scheduling in the operating system, we propose a hardware implementation of the Thread Lock Section-aware Scheduling (TLSS) scheduling mechanism [71]. This lightweight mechanism helps to identify multi-threaded application bottlenecks such as thread synchronization sections and complements state-of-the-art heterogeneous schedulers. It is, to our knowledge, the first hardware based lock sectionaware scheduling that is energy attentive and can be applied to both asymmetric and symmetric CMPs. It achieves average performance gains of 10.9% compared to the state-of-the-art Linux OS Scheduler when applied on an SCMP. At the same time, it is 81% more EDP (energy-delay product) efficient when applied on an ACMP and compared to the Linux OS Scheduler on an SCMP, where ACMP and SCMP take relatively the same chip area.

## 1.4.3 Applying ML to heterogeneous scheduling

Accurately estimating the performance of applications on different heterogeneous resources can provide a significant advantage to heterogeneous schedulers seeking to improve system performance. Having demonstrated the opportunities and limits available using current CMP and scheduling designs, the contributions of this part of the thesis examine applying machine learning techniques to conventional heterogeneous schedulers in order to predict the system performance for different mapping schemes.

# A machine learning approach for performance prediction and heterogeneous CPU scheduling

In this study we propose a unique throughput maximizing heterogeneous CPU scheduling model that uses ML to predict the performance of multiple threads on

### 1. INTRODUCTION

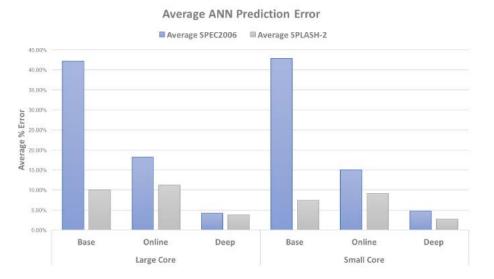

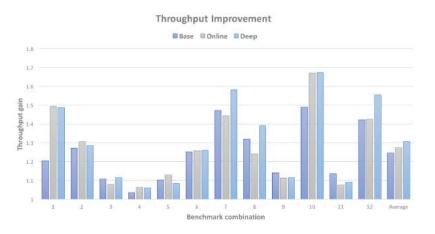

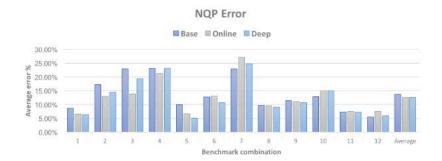

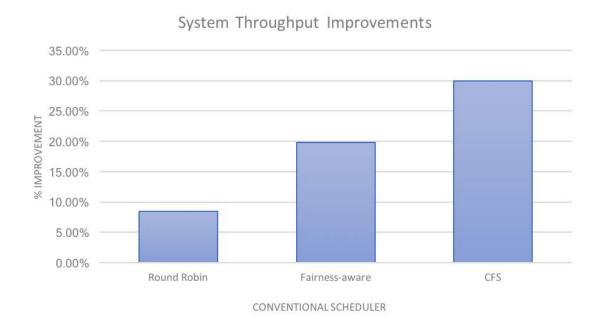

diverse system resources at the scheduling quantum granularity. We demonstrate how lightweight ANNs can provide highly accurate performance predictions for a diverse set of applications thereby helping to improve heterogeneous scheduling efficiency. We show that online training is capable of increasing prediction accuracy but deepening the complexity of the ANNs can result in diminishing returns. Notably, our approach yields 25% to 31% throughput improvements over conventional heterogeneous schedulers for CPU and memory intensive applications on an ACMP.

### A deep learning mapper (DLM) for heterogeneous scheduling

This work pioneers applying a deep learning mapper to a scheduling model that decouples thread selection and mapping routines. We use a conventional scheduler to select threads for execution and a deep learning mapper to map the threads onto a heterogeneous hardware. The validation of our preliminary study shows how a simple deep learning based mapper can effectively improve system performance for state-of-the-art schedulers by 8%-30% for CPU and memory intensive applications.

## 1.5 Thesis outline

The subsequent sections of this thesis are structured as follows. Chapter 2 presents the necessary background on heterogeneous systems, application behaviors, CMP scheduling, and machine learning models. It elaborates on the motivating factors of this thesis and concludes by providing an inspirational vision of what a reimagined massively heterogeneous computing model for the future can look like. Chapter 3 describes the experimental frameworks and metrics that were used in testing and evaluating the contributions presented in this thesis. This includes descriptions of the system simulator, processor models, and benchmark suites.

The thesis is then divided into two parts composed of preliminary investigations followed by a study on applying ML to heterogeneous scheduling:

Part I presents two preliminary studies on the increased architectural flexibility and energy efficiency benefits provided by heterogeneous scheduling in Chapters 4 and 5.

Part II presents two pioneering studies on applying ML to heterogeneous scheduling. Chapter 6 defines a scheduling model based upon a thread behavior predictor, ANN based thread performance predictors for each core type, and a scheduling heuristic. Chapter 7 presents an extension of the machine learning based heterogeneous scheduler which expands the scope of the predictors to cover thread interference effects and extends their applicability to be compatible with nearly all conventional schedulers as an add-on module.

Chapter 8 discusses the related work regarding all of the studies presented in this thesis and Chapter 9 details our conclusions. A list of publications and references is provided at the end.

# Motivation

This chapter presents the necessary background on homogeneous and heterogeneous CMPs, application behaviors, multi-core scheduling, and ML techniques. We identify the potential of heterogeneous CMPs, scheduling mapping shortcomings, and ML tools as the motivating factors for this thesis. The chapter concludes by providing a compelling vision of what a reimagined massively heterogeneous computing model for the future can look like and why designing efficient heterogeneous scheduling is at the core of scaling heterogeneity.

# 2.1 Background

## 2.1.1 Chip Multi-processors (CMPs)

Computer architects have been greatly benefiting from the steady progress of chip fabrication techniques which have vastly expanded the number of available transistors to make use of in their designs. Previously, architects made use of the added transistors by designing larger and more complex single core CPUs until the trend fell out of favor due to power constraints and limits to parallel execution among others. Current trends exploit these extra transistor densities by implementing several identical (i.e., homogeneous) computational cores on a single chip, thereby improving the performance when running several applications concurrently or parallelized workloads. These types of homogeneous CMPs are known as symmetric or SCMPs.

#### 2. MOTIVATION

As long as only a single core type is used, SCMPs can includes either complex and powerful cores, such as those found in the Intel Xeon [52] or AMD Opteron [17] processors, or simple and lower-power cores as in Sun's Niagara [59]. A drawback of SCMPs, however, is that all cores will have to be implemented with the same complexity as the most powerful core required to meet certain constraints. This is a disadvantage since not all applications nor environments will have similar constraints. Hence, the hardware is essentially limited by the weakest link of all applications which requires higher core performance. This disadvantage is apparent in conventional SCMP designs which are becoming more limited by power dissipation and efficiency concerns. The power dissipation issues, which are also highlighted in the study termed Dark Silicon [33], have served to highlight the bounds of current design practices. Thermal dissipation constraints limits the total amount of transistors that may be powered concurrently at nominal voltage, thereby leaving large areas of a transistor rich chip to be off at any given time. The need to develop faster, smaller, and less power hungry CPUs has motivated research related to heterogeneous or asymmetric CMPs (ACMPs).

Several studies [81, 83] have been conducted that highlight the ability of ACMPs to outperform SCMPs for a fixed area or power budget. A wide range companies have also conducted research on ACMP systems including Intel [64, 106], and HP [81]. Commercial ACMP implementations such as ARM's big.LITTLE [38] and Nvidia's Tegra3 [74] have also been popularly used.

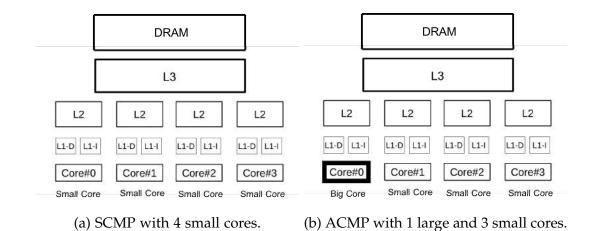

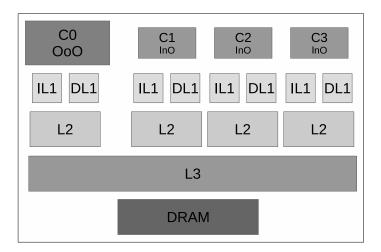

Compared to SCMPs, ACMPs employ cores that execute the same instruction set architecture (ISA) but differ in terms of microarchitecture. These differences can include issue width, whether the core supports out-of-order (OoO) or in-order execution, brach predictors, cache configuration, and also voltage and clock frequency. An advantage of using cores that share the ISA as opposed to specialized accelerators is that the application code does not need to be compiled separately for each core type that has a different ISA. Figure 2.1 illustrates the differences between an SCMP and an ACMP design.

Determining which combination of different types of cores to include in a CMP design is a non-trivial task and depends heavily upon the performance, power, and size requirements. These requirements are based upon the workloads, environments, and devices that a CMP is targeted towards. Relying only on homogeneous

Figure 2.1: An example of SCMP and ACMP CPU designs. Note that the cores must be all of the same ISA (e.g., ARM, x86) but may be more of different complexities for the ACMP system. The designs both have private L1 and L2 caches and a shared L3 cache.

CMP approaches is a simple approach but may result in sub-optimal performance compared with a heterogeneous CMP. Part of the motivation and proposed solutions of this work is what criteria is needed to evaluate potential CMP designs and how to determine the optimal CMP configuration (either SCMP or ACMP) given certain performance requirements. Though employing hardware specialization can be useful for determining which core type yields the most effective performance/energy trade-off for a specific type of program behavior, it is up to the scheduler to determine a thread mapping scheme with which to effectively exploit system diversity.

## 2.1.2 Caches

CMPs include a cache hierarchy which consists of a set of private and shared cache structures to keep data that will be reused close to the cores that need them. A typical cache hierarchy configuration for a CMP may include separate but private instruction and data level 1 caches (L1), combined but private L2 caches, and a last level cache (LLC) shared amongst all the cores. In addition to private or shared, caches can also take on a distributed nature similar to non-uniform cache accesses (NUCA). A distributed cache is logically a single shared structure but physically composed of separate cache structures located in different areas of the chip. Load

### 2. MOTIVATION

and store accesses to this cache may end up resulting in different latencies depending on how far the data physically resides from the core requesting it.

The L1 cache typically include tens of kilobytes (KB), the L2 contains up to a few megabytes (MB), and the L3 or LLC with at least an order of magnitude more cache (e.g., tens of MB). Architectural trends have also been to use the increases in transistor densities to enlarge the sizes of the caches on chip. The levels of the caches, whether private, shared, or distributed, size of each cache, associativity of the caches, and replacement policies are various of the properties that may differ greatly between CMP designs and might affect the system's and application's performance.

In order to ensure that no two threads are simultaneously modifying and using the same data, a coherency mechanism is utilized by the caches. Various protocols which change the state (e.g., modified, shared) of a data line or directory based schemes can be used to enforce coherency between different cores' private cache structures. Since the coherency overheads rise as the amount of shared data accesses from different cores increase, selecting which threads to run and where (i.e., which physical core to map the threads to) can directly impact performance.

### Cache footprint

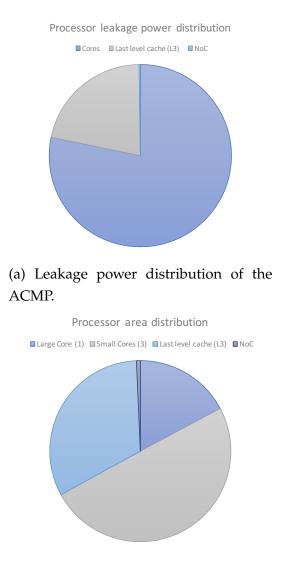

This section considers the cache footprint in terms of energy consumption, power budget, and physical size for an example case of an ACMP with one large and three small cores with private L1 (32KB) and L2 (256KB) cache per core and a single L3 (8MB) as the shared LLC (this ACMP is detailed comprehensively in Section 3.2). Modifying or reorganizing the cache hierarchy in order to mitigate the cache footprint may be a promising endeavor depending upon the performance/energy requirements of a CMP design.

The cache hierarchy of the example ACMP system when running both SPEC and SPLASH-2 benchmark suites consumes on average about 30% of the total energy and power budget of the processor. The last level L3 cache (LLC) alone consumes a significant chunk of the processor's energy, power, and size budget. Using measurements taken with McPAT [89] when running the 4 core ACMP, the LLC is responsible for on average about 10% of the total execution energy.

experimental simulations of a four core ACMP, the LLC has been shown to be responsible for around 21% of the processor's subthreshold leakage power (note that the total processor leakage power was upwards of 25% of the total peak power). In terms of physical size that it takes up on the die, the four cores, which include the L1 and L2 cache structures, take up about 67% of the total chip size while the LLC takes up a substantial 32%, and the interconnection network (NoC) a mere 1%.

### 2.1.3 Program structures and behaviors

A CMP system is regularly used to run programs which were designed for different purposes. Additionally, each of these applications may utilize multiple software threads to divide their work. Voice over IP programs, web browsers, media players and editors, and even daemons which seek to perform background optimizations and updates are just a small example of the diverse range of applications that a CMP will be required to execute concurrently.

Program structure refers to the algorithms, variables/objects, methods/functions, and dataflow used in the code itself. In contrast, a program's or thread's behavior is characterized by periodic patterns related to the instructions per cycle (IPC), instruction mix, branch prediction, cache and memory accesses and hit/miss rates, and other statistics related to its performance on a particular hardware. Variations in program structure can result in different behaviors in terms of computational, memory, and I/O intensity, all of which may vary significantly. Consequentially, program behavior is directly related to its structure and the physical hardware which it is executed on. Even applications targeted to solve similar problems may be coded so differently from one another that they may behave differently when executed on identical hardware. The memory access patterns are of particular interest in this case since applications may interfere with one another either by polluting shared memory structures such as the last level cache, or by accessing shared data structures which can be the case for multi-threaded programs.

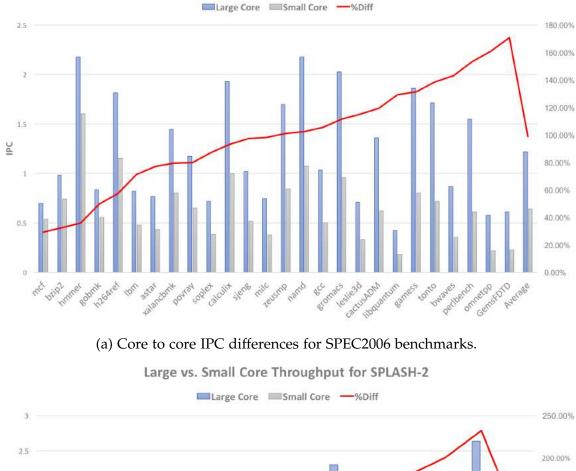

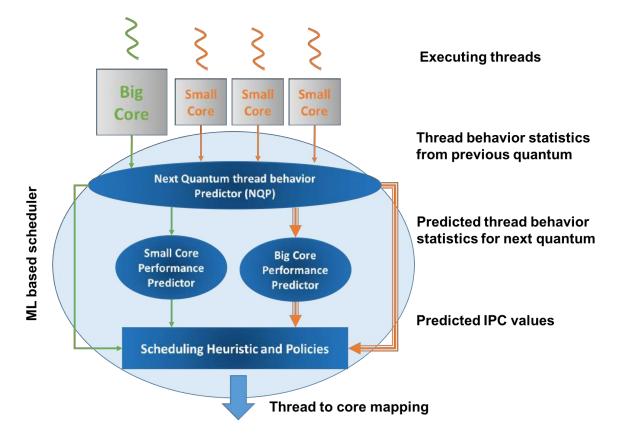

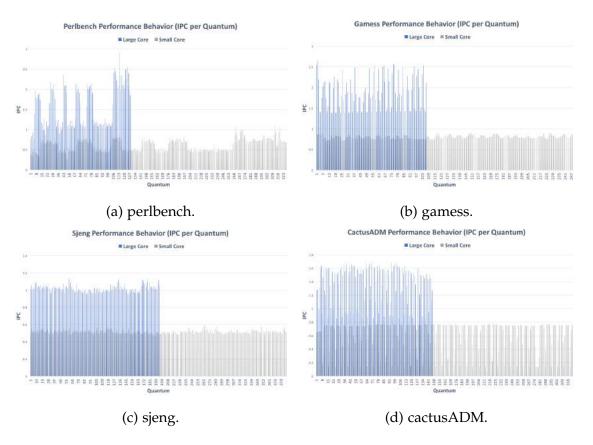

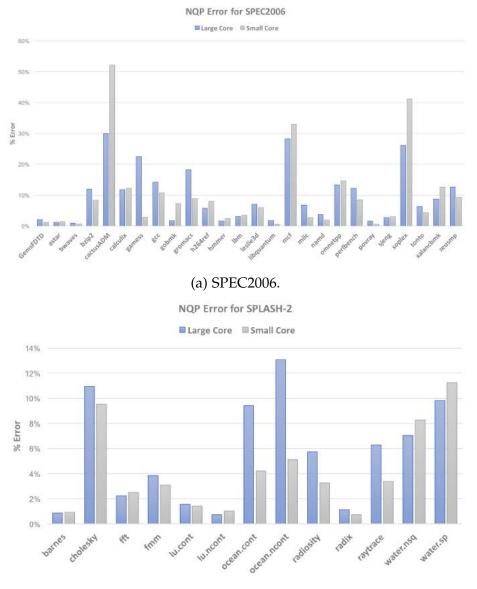

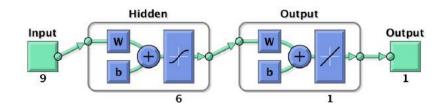

Figure 2.2 illustrates the performance differences that result from executing SPEC2006 and SPLASH-2 applications on a large core compared to a small core (for core details see Section 6.2.1). On average, the applications achieve nearly 2-2.3x better performance (instructions per cycle or IPC) when executing on the large core

### 2. MOTIVATION

compared with the small core. Variations in IPC differences can also be observed between applications. For some applications, these IPC differences can be either very minor (mcf 29%, barnes 6%, and radix 1%) or very sizable (gemsFDTD 171%, omnetpp 161%, and water.nsq 200%). These variations can be partially explained by the code's structure and algorithms, including loops, data dependencies, I/O and system calls, and memory access patterns among others.

These discrepancies between the performance gains of each benchmark when running on the large core vs. the small core clearly demonstrates the potential for system throughput optimization if an effective scheduling mapping scheme is chosen. For instance, if a combination of these benchmarks is run in parallel on an ACMP, then a scheduler with knowledge of performance behaviors of each application for all core types may be able to find an optimal mapping scheme that results in significantly better system performance than a random mapping scheme.

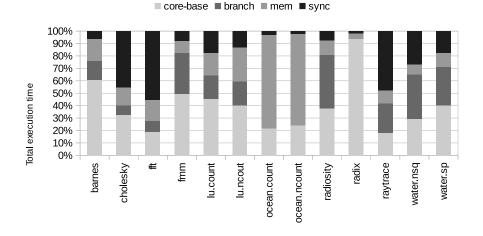

When investigating whether a program is computational, memory, or I/O intensive, it is often useful to break down their execution in terms of a CPI (cycles per instruction) stack. This stack separates the amount of total execution time an application spent on each type of instruction. Depending on the CPI stack, it is therefore possible to diagnose the application as being computational, memory, or I/O intensive.

Understanding program structures and behavioral characteristics is crucial when executing diverse programs on heterogeneous systems since each program may behave differently on distinct core types. For example, applications containing large quantities of instruction or memory level parallelism (ILP and MLP) could be more suited for execution on out-of-order (OoO) cores. On the other hand, applications with high amounts of thread level parallelism (TLP) or explicit instruction level parallelism may be ideal candidates for execution on lightweight in order cores. By identifying the behaviors of applications on the different cores, it is possible to better exploit the heterogeneous hardware. For instance, consider a two core system composed of a large OoO core and small in order core is used to run computationally intensive workloads while the larger OoO core is used to execute memory intensive workloads, that would otherwise suffer from substantial performance degradation due to memory request stalls if run on an in order core.

Large vs. Small Core Throughput for SPEC2006

(b) Core to core IPC differences for SPLASH-2 benchmarks.

Figure 2.2: The performance differences that result from executing each benchmark on a large vs. small core. Higher IPC numbers represent faster performance.

### 2. MOTIVATION

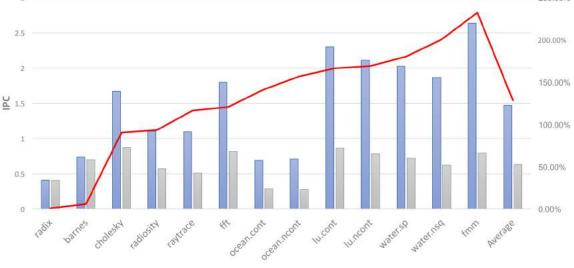

Figure 2.3: The IPC per quantum behavior of four SPEC benchmarks when running on the big core compared to the small core.

While not all programs exhibit the same behavior, studies [29, 94] have shown that the behavioral periodicity in different applications is typically consistent. In fact, the behavioral periodicity has been shown to be roughly on the order of several millions of instructions and is present in various different and even non correlated metrics stemming from looping structures inside of applications. Heterogeneous architectures such as ACMPs provide excellent environments for exploiting the behavioral diversity of concurrently executing programs.

Figure 2.3 helps to visualize this behavioral periodicity. It shows the IPC variability of the perlbench, cactusADM, gamess, and sjeng SPEC benchmarks throughout their simulated execution on an Intel Nehalem using a 1ms execution quantum. Though there are clearly periodic behavioral phases that span tens and sometimes hundreds of quanta, it is also possible to observe that for finer granularities, the IPC variation from quantum to quantum is quite minimal, and more so on the small core.

CMPs typically employ a shared memory model which may result in cooperative or interference effects when running applications and threads in parallel that access shared resources using a common address space. Parallel programs, in specific, may consist of several threads which need to synchronize or share locked data structures, commonly resulting in data races due to data dependencies. Accessing and modifying shared data from different cores may cause cache lines to be transferred between private caches which penalizes application performance and total system throughput. These effects are lower for work stealing workloads, however, since they allow idle cores to steal work from busy cores. As described in [48], inter-thread synchronization bottlenecks such as contended critical sections may cause thread imbalances at runtime leading to adverse performance effects. However, parallelized applications can be effectively exploited by CMPs since they can execute the different parallel sections of code using the various hardware resources available. Distinct thread and memory management/sharing approaches can also result in significant effects on system performance and utilization.

## 2.1.4 CMP scheduling

In order to properly manage threads and system resources, CMPs rely upon a scheduler that can be implemented either in software, for example in the operating system (OS), or hardware.

CMP schedulers rely chiefly upon two mechanisms to fulfill their policy objectives: 1) thread selection and 2) thread to core mapping (from here on referred to simply as mapping).

The thread selection mechanism is responsible for selecting a subset of threads to run from a larger pool of available threads. It does so by using heuristics which order the threads using priorities or scores related to how critical the threads are (e.g., time constrained or system level tasks may be given a higher priority than background tasks which search for application updates) or how much execution time or progress the threads have made so far. To identify all available threads, the scheduler keeps track of the current state of all the different threads (e.g., whether a thread is ready for execution, paused, or stalled on a disk access). Thread selection generally ensures that no threads are continually starved of system resources thereby guaranteeing a certain level of fairness and load balancing.

The scheduler may be triggered periodically via a specified scheduling quantum to preempt the current execution of the running thread(s) or also be called asynchronously as in the case of a thread stall. For the rest of this work, we will utilize the terms scheduling quantum and execution quantum interchangably.

Different CPU schedulers may have different thread to core optimization objectives. Some may try to maximize system throughput (IPC), others may want to finish the shortest thread or longest thread in the shortest time, and others may try to optimize for energy efficiency. Deciding on the correct scheduling policy to apply depends upon the target systems, programs, and applicability to different environments.

### Mapping

Finding the optimal thread to core mapping on a heterogeneous system is no simple endeavor. This is especially the case when executing diverse workloads since the performance of each application is likely to vary from quantum to quantum

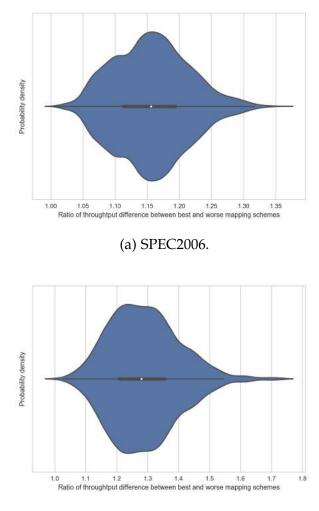

Figure 2.4: The importance of how different mapping schemes for a given set of applications can result in significantly different system throughputs. The y-axis represents the probability of a given ratio of throughput differences (x-axis) between the best and worst mapping schemes for all possible combinations of four applications from SPEC2006 and SPLASH-2 when running on a 1-large and 3-small core system. X-axis values should be read as the factor of system throughput improvement of selecting the best mapping scheme compared to the worst mapping scheme for a given four application combination. The white dot in the middle of the x-axis represents the mean and the black dots represent observed values which occur more frequently near the mean.

### 2. MOTIVATION

| Benchmark | Min | Max | Mean |

|-----------|-----|-----|------|

| SPEC2006  | 1%  | 36% | 16%  |

| SPLASH-2  | 3%  | 71% | 29%  |

Table 2.1: The minimum, maximum, and average differences (in percentage terms) between the best and worst mapping schemes for all possible combinations of SPEC2006 and SPLASH-2 benchmarks on a 1-large and 3-small core system.

and from core to core. The specific performance differences that result from executing an application on different core types can be measured by distance or as a ratio. These differences can vary from application to application (inter-application) as well as from phase to phase within an application (intra-application).

The inter-application variations in core to core IPC differences shown in Figure 2.2 also exist at the quantum level within each application (i.e., intra-application) as shown in Figure 2.3. It is important to highlight that these differences can vary as the application enters and exits different phases of execution. The more inter and intra application variations of core to core IPC differences there are, the harder it is for a scheduler to identify the optimal mapping scheme, but the more opportunities for improvement there are. A scheduler that needs to produce a new mapping scheme every quantum can further take advantage of these fine granularity performance discrepancies between applications and threads. Exploiting these variances may lead to identifying a mapping scheme every quantum which maximizes system performance.

To showcase how identifying these core to core IPC differences can translate into mapping benefits, consider the case where four applications (e.g., A, B, C, and D) are selected to run on an ACMP with one large core and three small cores. Four mapping schemes which assign one application to the large core and the other three to the small cores can be A-BCD, B-CDA, C-DAB, D-ABC. Each mapping scheme will produce a different resulting system IPC. The overall benefits of an effective mapper will be based upon the difference between the best and worst mapping schemes. For instance if A-BCD is the best mapping scheme resulting in a system IPC of 4 and C-DAB is the worst with a system IPC of 2, then the difference in percentage terms would be 100% (i.e., (4 - 2)/2).

To demonstrate this in practical terms, we found the differences between the best and worst mapping schemes for all possible combinations of four applications from both the SPEC and SPLASH suites. Figure 2.4 exposes the more detailed distribution these results for both SPEC and SPLASH. Both subfigures plot the probability density distribution of the best vs worst mapping schemes which highlights the importance of how different mapping schemes for a given set of applications can result in significantly different system throughputs. While both distributions are fairly similar, SPEC does appear to suffer from slightly more variation and less overall throughput differences although it is still very significant. Table 2.1 presents the average, minimum, and maximum differences (in percentage terms) between the best and worst mapping schemes for all possible combinations. The minimum differences range from 1%-3%, average differences from 16%-29%, and maximum differences from 36%-71% for all possible mapping schemes for SPEC and SPLASH respectively. These results expose the theoretical benefits that may be gained from an effective scheduler at the application level granularity. Practical schedulers, however, work at the quantum level granularity and may additionally take advantage of intra-application core to core performance differences which could expose greater opportunities for mapping optimization.

In order to identify an optimal mapping scheme, a heterogeneous scheduler should be able to estimate the system performance that each individual mapping scheme would produce. Conventional schedulers, however, typically do not make use of the mechanisms needed to exploit this potential. As we shall see, machine learning can be an effective tool for schedulers to utilize in order to help estimate system performance. In the studies presented in Part II we use the powerful prediction capabilities of artificial neural networks (ANNs) to greatly increase the benefits that CPU schedulers can provide for maximizing heterogeneous multi core performance.

## CMP schedulers in practice

The vast majority of conventional CMP schedulers are designed for SCMP system configurations and therefore cannot take advantage of differences between computational cores. The Completely Fair Scheduler (CFS) [54], which was integrated

with the Linux 2.6 kernel, is an example of a homogeneous scheduler. The stateof-the-art CFS selection scheme combines priorities with execution time metrics in order to select the threads to run next; however, the mapping scheme is relatively simplistic. When mapping, the CFS evenly distributes the threads onto the cores such that all cores have approximately the same number of threads to run. These threads are effectively pinned to the core because they are only swapped with threads on their assigned core and not with those of another core (i.e., threads do not move from the core they were initially assigned to).

In order to fully utilize heterogeneous systems, however, schedulers should be aware of and make use of a system's diverse resources. Several heterogeneous schedulers targeting ACMP systems have been proposed that show significant improvements over conventional SCMP schedulers. Some of these make use of online or offline profiling as well as sampling or estimation techniques to determine the optimum thread to core mapping (in relation to performance and/or power) whenever a specific event is detected or scheduling time quantum is completed [66], [20], [55] among others.

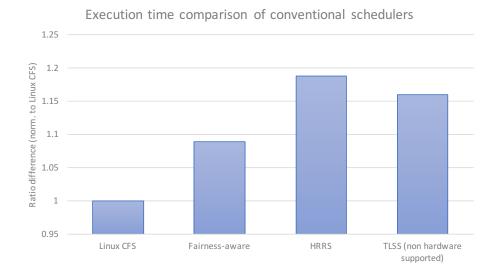

The fairness-aware scheduler by V. Craeynest et al. [56] is a heterogeneous scheduler which works similarly to the CFS but instead of mapping all threads evenly on all cores and pinning them there, it maps the highest priority thread (i.e., the one that has made the fewest progress) to the most powerful core. For example, in a four core system with one powerful core and three smaller energy efficient cores, this scheduler will send the thread with the highest priority to the large core and the next three highest priority threads to the other 3 small cores. This is similar to the Global Task Scheduler [51] used by ARM in its big.LITTLE heterogeneous systems which modifies the Linux kernel to send ready threads who have spent the most time waiting for a core to the large cores and the subsequent threads to the small cores. Thread lock section-aware scheduling [71] expands upon the fairness-aware scheduler by prioritizing threads who have recently switched back from system level to user level code to run on the powerful cores. This is done in an attempt to catch and accelerate the critical sections of a thread.

Another scheduler targeted at heterogeneous systems is the hardware roundrobin scheduler by Markovic et al. [72]. Instead of using priorities for thread selection, this approach chooses which threads to run next in a round-robin manner (thereby guaranteeing fairness) and then maps the selected threads to the cores. Using the same 4 core system as described above, this scheduler will rotate the threads in a manner similar to a first in first out queue, from small core to small core to small core to big core and then back into the thread waiting pool until all threads have had a chance to execute.

Schedulers produce overheads which may mitigate efficiency gains due to the cost of managing and selecting threads, calculating optimal thread to core mapping, and context switch penalties. It is therefore imperative for effective schedulers to balance finding an optimal mapping without triggering unnecessary context swaps and being as lightweight as possible.

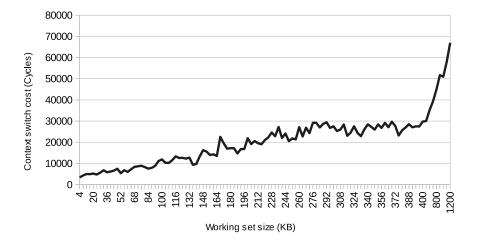

## **Context switches**

Implementing dynamic scheduling requires switching of the context of the cores including swapping the architectural state (register file), flushing the pipeline, and reloading the working-set into the private caches. A context switch incurs a fixed cost for storing and restoring the architecture state (at most a few kilobytes) [88] with most of the overheads being due to reloading the caches. Figure 2.5 presents the context switch overheads costs when executing different working set sizes on an Intel i7-4600U core[18]. The overheads grow gradually with the size of the working set until an excessively large working set causes additional page faults which increase the overheads significantly. The study [55] has shown the migration overhead to be less than 1.5% across different types of single-threaded workloads, ranging from memory to compute intensive, for a 4 MB shared LLC using a 1ms quantum.

## 2.1.5 Machine learning

Part of the attraction of machine/deep learning is the flexibility that its algorithms provide to be useful in a variety of distinct scenarios and contexts. For instance, advances in computer vision and natural language processing using convolutional neural network techniques [62, 60, 16] have led to high levels of prediction accuracy enabling the creation of remarkably capable autonomous vehicles and virtual assistants. Generally speaking, machine/deep learning techniques can be used to build

Figure 2.5: Context switch cost on a dual core Intel(R) Core(TM) i7-4600U CMP [18]. The overhead includes costs related to swapping architectural state, flushing the cores' pipelines, and reloading data into the private caches.

highly accurate predictors, pattern recognition systems, and also systems for data generation. Though ML techniques have been gaining traction over the last few years, its application toward improving hardware performance remains in its earliest stages. As of yet, there has been no seminal work applying machine learning for predicting thread performance on heterogeneous cores and maximizing system throughput.

Artificial neural networks (ANNs) in particular, are beginning to be utilized in a wide variety of fields due to their great promise in learning relationships between input data and both numerical or categorical outputs. The relationships learned by the ANNs are often hard to identify and program manually but can provide excellent prediction accuracies. Moreover, ANNs and deep ANNs (DNNs) are readily utilized for prediction purposes and can be relatively lightweight and flexible to implement. They consist of a set of input parameters (considered to be the first layer) connected to a hidden layer of artificial neurons which are then connected to other hidden layers before connecting to one or more output neurons. The inputs to the hidden and to the output neurons are each assigned a numerical weight that is multiplied with its corresponding input parameter and then added together with the result of the neuron's other incoming connections. The sum is then fed into an activation function (usually a rectified linear, sigmoid, or similar). The output of these neurons is then fed as input to the next layer of neurons or to the the output neuron(s). The result of the output neuron(s) is the prediction that the ANN makes which may be either a numerical value estimate or a classification estimate using one-hot bit encoding.

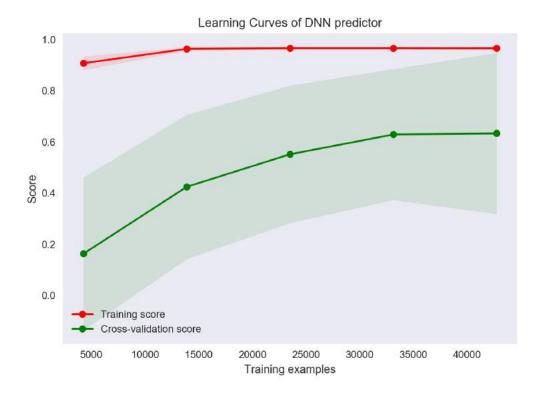

An ANN can learn to produce accurate predictions by adjusting its weights using a supervised learning method and training data. Other unsupervised methods of learning such as clustering also exist but fall outside the scope of this work. Supervised learning is performed via a learning algorithm such as backpropagation that adjusts the weights in order to find an optimal minima which reduces the prediction error based on an estimated output, the target output, and an error function. The more hidden layers and hidden units there are, the more intricate relationships that may be learned, however having too deep of an ANN can also lead to overfitting. Overfitting is when the model achieves very low error for data it has seen but produces high error when predicting for previously unseen data. Generalizing the ANN to be able to consistently predict at similar accuracies for seen (i.e., training) and unseen (i.e., testing) data is a central issue in ANN design and many different types of approaches are used.

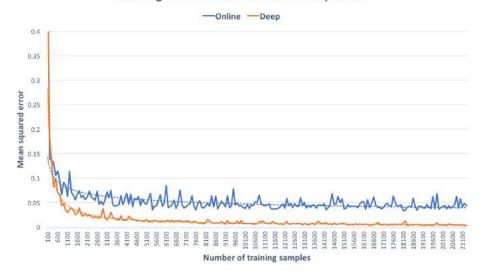

One such common practice in machine learning is to divide the data into training (70%), validation (15%), and test (15%) sets in order to not overfit the model. Evaluating how a model performs on the validation and test sets allows to modify the ANN to improve its generalization when predicting for unseen data. Other approaches include using regularization techniques to regulate the importance of parameters within the learning algorithm and more intricate methods such as dropout which trains the ANNs in phases excluding certain hidden units to ensure all neurons are able to contribute to a prediction. A way in which to evaluate the error of a model and how many data samples are needed to provide a consistent accuracy is in the use of learning curves. The learning curves show how the training and validation errors of the ANNs changes as the amount of training data increases. After a certain amount of training data, the curves level off so that increasing the amount of training data will not impact the ANN's accuracy.

Another approach for providing prediction flexibility and generalization to new data is the use of online learning. While ANNs can be trained statically before being ever used, they can also keep learning dynamically by periodically training as new data samples are provided. This method improves the accuracy and generalizability of the ANNs when predicting for applications that are run more than once. Learning dynamically is an area of active research since there are tradeoffs between how much to adapt the ANN for newer data and how that will impact the ANNs generalizability to past data as well as heavier computational costs. Online learning can also be extremely important in scenarios where the applications and behaviors of the workloads being run change over time.

Advances in learning algorithms have enabled faster training times and allowed for the practical use of intricate ANN architectures. The training calculations themselves may also be executed in parallel for the neurons within the same layer. The latency of these calculations can be further mitigated through the use of hardware support including GPUs, FPGAs, or specialized neural network accelerators. Deep learning methods expand on more simplistic machine learning techniques by adding depth and complexities to existing models. Using DNNs or ensembles of different machine learning models is a typical example of deep learning.

We believe the predictive power of ML techniques such as artificial neural networks (ANNs) will be of significant use to computer architects for optimizing system performance for example by estimating system performance, branch predictions, and cache/memory accesses.

## 2.2 Reimagining Heterogeneous Computing

This section proposes a motivating long-term vision to support the expansion of massively heterogeneous architectures which support and complement the diversity and functionality found in software applications, tasks, and kernels.

In an innovative step forward, the hardware community has started to tackle the power wall and the memory wall by diversifying the computational cores. Whereas initial chip multiprocessors (CMPs) integrated several identical computation cores per chip, we now see an increasing tendency to explore the reaches of integrating an expansive range of diverse computational cores. On the software front, the standardization of programming practices has promoted the development of vast amounts of commonly utilized libraries, tools, and frameworks. This has marked an unprecedented growth in the level of abstraction available to the average programmer. Emphasis on code optimization and portability has also led to the development of programming models and runtime systems that let programmers define and extract substantial amounts of parallelism in their code, such as OpenCL [102] Cilk Plus [86] and OpenMP [24].

Used effectively, these programming models allow significant gains in application performance and resource utilization. Yet, while these software models have been useful and complementary to advances on the hardware front, their considerable runtime overheads, implementation complexity, and limited adoption have hindered their appeal and applicability. Conversely, parallel applications have been shown to share similar characteristics, which increase their appeal for standardized libraries and hardware practices.

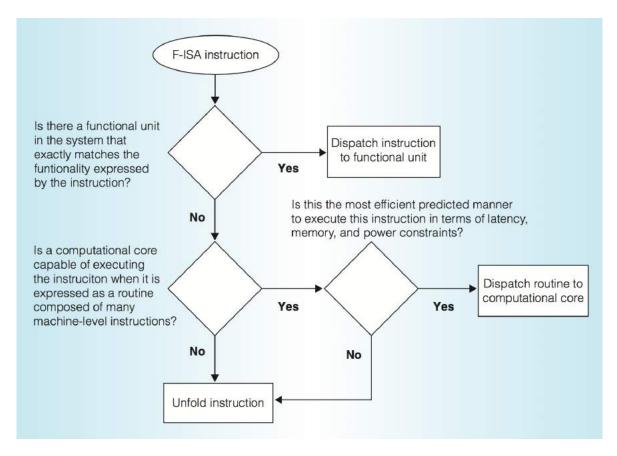

For now, a semantic gap seems to be emerging between the advances in hardware and software. The scope and potential of new technologies have started to lead to heterogeneous many-core systems, but hardware architects have not similarly embraced, as of yet, the use of high abstraction levels. This is because of the physical and compatibility constraints that hardware developers face, which are far more flexible at the software level. However, given the current state of the industry, architects need to consider radical paradigm-shifting computing-model proposals. Such proposals will not necessarily offer clear roadmaps or short-term pragmatic solutions, but they could contain the hints and alternate ideas needed to rethink the long-term vision that computer architects hope to achieve. In this section, we address this hardware-software semantic gap by considering an unconventional computing model that merges current heterogeneous state-of-the-art hardware with the concept of abstraction that has been so useful and ubiquitous in software, but not present in hardware. To do so, we use the concept of abstraction to reinterpret the notion of the ISA.

Most ISAs in use today remain (for compatibility reasons) based on designs developed several decades ago to solve that era's physical and software constraints. The current CMP model's scalability is inherently constrained because of the current ISA's functional granularity, which generally results in a large memory foot-

print and high energy consumption. As a remedy, we propose a functional ISA (F-ISA) that increases the functional abstraction level of the machine instructions. Consequently, this extra level of functional abstraction enables a dramatic increase in the heterogeneous diversity of a processor's computational units, resulting in greater specialized execution particular to the needs of the software algorithms. We hope that this alternative computational model can significantly improve and fine-tune system performance relative to latency, memory footprint, and power.

## 2.2.1 Conceptual discussion

Computation as we know it today is grounded on the interaction and communication between two key elements: data (to be used, manipulated, and/or produced) and functions (specifying what is done with the data). We identify three datafunction computational models: (i) data to function, (ii) function to data, and (iii) data and function.

## Data to function

This model is embodied in a system that comprises separate memory (instruction and data) and computational structures in which, via one or more machine-level instructions, data is sent from the memory (such as DRAM) to be executed in a functional unit (such as an integer adder). This method is the standard approach used by current CPUs, and both Von Neumann and Harvard architectures fall within its scope. This model's limiting factor is that a functional unit's complexity is determined by the ISA's functional abstraction level. An add instruction corresponds to an adder functional unit, a branch instruction to a branch unit, and so on. Because nearly all conventional ISAs rely on low-level functional instructions, the physical characteristics of the data and functional units are intrinsically bound by the exposed level of functionality.

The limited diversity and complexity of the functional units mean that they can understand only primitive data objects (e.g., integers, doubles, and branches). Consequently, this produces a homogenizing effect on the executable data objects and furthers the need for repetitive executions to perform higher-complexity functions (such as list sort and matrix multiplication). If the data is homogenized into primitive data objects, then more accesses to memory are required to load the necessary data into the cores to perform the desired (higher abstraction level) functions. These factors can significantly contribute to a system's overall memory footprint and power usage, a problem that is further exacerbated by the fact that conventional CPUs consolidate the available functional units into a handful of computational cores. Compared with a futuristic heterogeneous core configuration, in which each core contains specialized functional units suited to specific data structures, memory contention is greater when all cores are equally capable of executing the same functions on the same data. This is due to having larger number of simultaneous accesses to primitive data objects which are typically stored in shared memory structures.

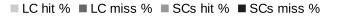

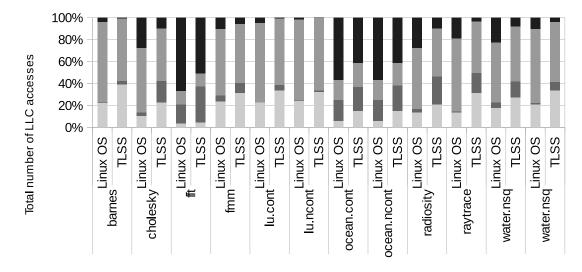

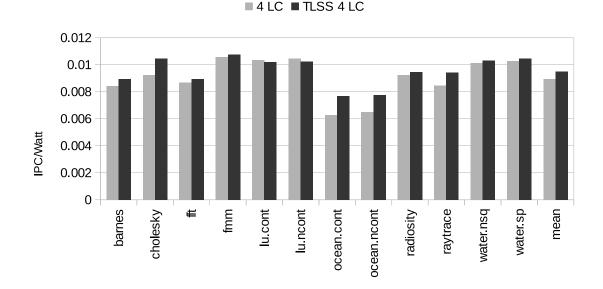

### Function to data