# Direct current control for grid connected multilevel inverters

### **Markus Schaefer**

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) les repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (\*framing\*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="https://raming/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) and the cooperative repository TDX (<a href="http://www.tdx.cat/?locale-attribute=en">http://www.tdx.cat/?locale-attribute=en</a>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Universitat Politècnica de Catalunya Departament d'Enginyeria Elèctrica

#### PhD thesis

# Direct Current Control for Grid Connected Multilevel Inverters

Autor: Markus Schaefer

Directors: Daniel Montesinos i Miracle

Ansgar Ackva

Barcelona, September 2017

Universitat Politècnica de Catalunya Departament d'Enginyeria Elèctrica Centre d'Innovació Tecnològica en Convertidors Estàtics i Accionament Av. Diagonal, 647. Pl. 2 08028 Barcelona

Copyright © Markus Schaefer, 2017

| Assessment results for the doctoral thesis                                     |                           |                                                            | Academic year:                           |  |

|--------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------|------------------------------------------|--|

| Full name                                                                      |                           |                                                            |                                          |  |

| Doctoral programme                                                             |                           |                                                            |                                          |  |

| Structural unit in charge of the programme                                     |                           |                                                            |                                          |  |

|                                                                                |                           |                                                            |                                          |  |

| Decision of the committee                                                      | !                         |                                                            |                                          |  |

| In a meeting with the examination contopic of his/her doctoral thesis entitled |                           | or this purpose, th                                        | e doctoral candidate presented the       |  |

| Once the candidate had defended the to award a mark of:                        | e thesis and answe        | ered the questions                                         | put to him/her, the examiners decided    |  |

| FAIL PASS                                                                      | s 🔲 g                     | GOOD                                                       | EXCELLENT                                |  |

| (Full name and signature)                                                      |                           | (Full name and signature                                   | )                                        |  |

| Chairperson                                                                    |                           | Secretary                                                  |                                          |  |

| (Full name and signature)                                                      | (Full name and signature) |                                                            | (Full name and signature)                |  |

| Manakas                                                                        | Manahan                   |                                                            | Marshar                                  |  |

| Member                                                                         | Member                    |                                                            | Member                                   |  |

|                                                                                |                           |                                                            |                                          |  |

| The votes of the members of the example School, and the result is to award the |                           | -                                                          | the Standing Committee of the Doctoral   |  |

| YES NO                                                                         |                           |                                                            |                                          |  |

| (Full name and signature)                                                      |                           | (Full name and signature                                   | )                                        |  |

|                                                                                |                           |                                                            |                                          |  |

| Chair of the Standing Committee of the Doct                                    | oral School               | Secretary of the Standing Committee of the Doctoral School |                                          |  |

| Barcelona,                                                                     |                           |                                                            |                                          |  |

| International doctorate me                                                     | ention                    |                                                            |                                          |  |

| As the secretary of the examination                                            | on committee. I hen       | ehy state that the                                         | thesis was partly (at least the summary  |  |

| <u>=</u>                                                                       |                           | -                                                          | monly used in scientific communication   |  |

| in the relevant field of knowledge                                             | which must not be         | an official langua                                         | ge of Spain. This rule does not apply to |  |

| stays, reports and experts from a                                              | Spanish-speaking of       | country.                                                   |                                          |  |

| (Full name and signature)                                                      |                           |                                                            |                                          |  |

|                                                                                |                           |                                                            |                                          |  |

| Socratary of the Evamination Comm                                              | sittee                    |                                                            |                                          |  |

I would like to dedicate this thesis to my loving wife, my wonderful children and my parents

#### Acknowledgements

I would like to express my gratitude to my advisors, Ansgar Ackva and Daniel Montesinos-Miracle, for their support, patience, and encouragement throughout the last years. It is not often that one finds advisors and colleagues who always find the time for listening to the little problems and roadblocks that unavoidably crop up in the course of performing research. Their technical and editorial advice was essential to the completion of this dissertation and has taught me innumerable lessons and insights on the workings of academic research in general.

I would also like to thank all external reviewers for reading and providing valuable comments that improved the thesis. Furthermore, I would like to thank the examination panel members for your support and willingness to be part of the panel. Personally I would like to thank Professor Arndt, Dr. Diaz Gonzalez and Professor Müller.

I am also grateful, especially to my colleagues, Martin Hofmann and Wolf Goetze, who have supported me with countless discussions on the subject of this dissertation. This discussion contributed significantly to the content and they were therefore indispensable for the success of the dissertation. I would also like to thank the other colleagues and master students who worked together with me during the thesis.

Last, but not least, I would like to thank my wife Janine and my wonderful children for their understanding and love during the past few years. Their support and encouragement was in the end what made this dissertation possible. My parents, Traudl and Jürgen, receive my deepest gratitude and love for their dedication and the many years of support during my undergraduate studies that provided the basis for this work.

#### Abstract

Control schemes for inverters of different topologies and various numbers of voltage levels are of great interest for many standard as well as special applications. This thesis describes a novel, robust and high-dynamic direct current control scheme for multilevel voltage source inverters. It is highly independent from load parameters and universally applicable. The new control method is examined and validated with real measurements.

The aim of the thesis is to establish and prove a new concept of a direct current control algorithm for multilevel inverter topologies for grid connected systems. This application is characterized by unknown grid conditions including failure modes and other distortions, complex inverter topologies and a large variety and complexity of current control algorithms for multilevel inverters. Therefore the complexity of the system needs to be reduced. Additionally, the advantages of multilevel inverters and the dynamic performance and robustness of direct current control techniques shall be combined. Starting from a detailed literature study on inverter topologies and direct as well as indirect current control methods, the thesis includes three chapters containing relevant contributions to the achievement of the objectives.

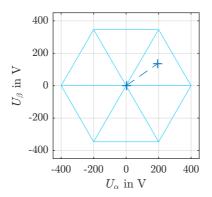

A method reducing the control-complexity of multilevel converters has been developed. The simplification method is based on a transformation that converts any three-phase voltage (or current) into a non-orthogonal coordinate system. This choice minimizes the complexity and effort to determine the location of those discrete voltage space vectors directly surrounding the required reference voltage vector. A further improvement is achieved by scaling all coordinates to integer values. This is advantageous for further calculations on microprocessors or FPGA based control systems.

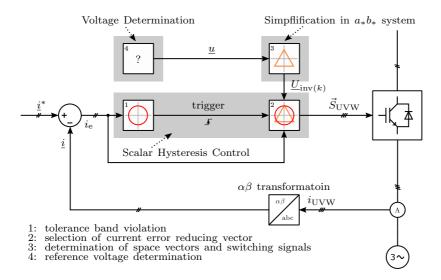

The main contribution of this thesis is a new direct current control method minimizing the disadvantages of existing direct methods. At the same time advantages of other control algorithms shall be applied. The new method is based on a simple mathematical equation, that is, the solution of a scalar product, to always select the one inverter output voltage vector best reducing the actual current error. This results in the designation "Scalar Hysteresis Control - SHC". An advanced seeking algorithm ensures robust current control capability even in case of unknown, unsymmetrical or changing loads, in case of rapid set-point changes or in cases of unknown phase voltages.

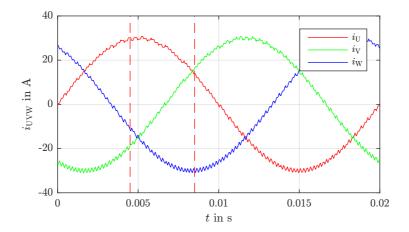

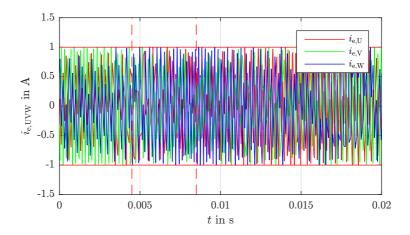

The new method therefore shows excellent properties in terms of simplicity, robustness, dynamics and independence from the inverter level count and the hardware topology. The properties of the control method are verified by means of simulations and real measurements on two-, three- and five-level inverters over the complete voltage operating range.

Finally, all contributions are collected together and assessed with regard to the objectives. From the proposed control method new opportunities for future work, further developments and extensions are evolving for continuing scientific research.

#### Resum

Els sistemes de control d'inversors de diferents topologies i diferent varis nivells de tensió són de gran interès per moltes aplicacions estàndard i també per aplicacions especials. Aquesta tesi investiga sobre un mètode de control directe de corrent per convertidors multinivell en font de tensió que es mostra robust i presenta una elevada dinàmica en el control de corrent. El mètode és molt robust davant de canvies als paràmetres de la càrrega i aplicable a qualsevol tipus de convertidor. En aquesta tesi s'analitza el mètode i es valida mitjançant resultats experimentals.

L'objectiu d'aquesta tesi és establir i demostrar un nou de mètode i algorisme de control directe de corrent aplicat especialment a inversors connectats a la xarxa. L'aplicació es caracteritza per la desconeixença dels paràmetres de la xarxa, incloent diferents modes de falla i distorsions en la seva tensió i una varietat de tipologies de convertidors multinivell. El mètode de control busca simplificar l'algorisme i que pugui ser aplicat en aquest entorn de forma robusta, de forma que es pugui estendre l'ús dels convertidors multinivell sense afegir més complexitat als algorismes de control i modulació.

La tesi aborda el problema iniciant amb un anàlisi de la literatura existent en aquest tipus de mètodes de control directe i indirecte del corrent i els convertidors multinivell, per continuar amb l'anàlisi del mètode proposat i la seva demostració mitjançant resultats de simulacions i experimentals.

El mètode de simplificació està basat en una transformació que transforma qualsevol sistema trifàsic a un sistema de coordenades no-ortogonal. Escollir aquest sistema de coordenades redueix la complexitat i l'esforç per determinar la ubicació d'aquells vectors espacials que directament envolten el vector de referencia. A més, totes les coordenades s'escalen a valors enters, que permet la programació de l'algorisme en sistemes de control basats en microprocessadors o FPGAs.

La principal contribució d'aquesta tesi és un nou mètode de control de corrent que intenta minimitzar els desavantatges dels mètodes indirectes existents a l'actualitat, al mateix moment que s'intenta incorporar els avantatges dels mètodes indirectes. El mètode proposat es basa en una equació matemàtica simple, la solució d'un producte escalar, per trobar el vector de tensió espacial que minimitza l'error de corrent, en el que s'anomena ?Scalar Hysteresis Control? o SHC. L'algorisme assegura un control robust del corrent

sense la necessitat de conèixer la tensió de fase, o les càrregues, tant si són desequilibrades o canviants. També presenta una dinàmica molt elevada en cas de canvies en la referència. El nou mètode mostra unes propietats excel·lents en termes de simplicitat, robustesa, dinàmica i independència de la tipologia del convertidor i, en el cas de convertidors multinivell, del nombre de nivells. Les propietats del mètode de control són verificades mitjançant simulacions i resultats experimentals en convertidors de dos, tres i fins a cinc nivells de tensió en tot el rang d'operació, fins i tot en la zona de sobremo-dulació.

A partir del mètode de control proposat, s'estan desenvolupant noves aplicacions i extensions, continuant també la contribució a la recerca científica.

# **Contents**

| List of Figures |       |                                                         | xii |

|-----------------|-------|---------------------------------------------------------|-----|

| Li              | st of | Tables                                                  | xix |

| 1               | Intr  | oduction                                                | 1   |

|                 | 1.1   | Background                                              | 1   |

|                 | 1.2   | Motivations for Research                                | 3   |

|                 | 1.3   | Objectives of Research                                  | 4   |

|                 | 1.4   | Contributions of Research                               | Ę   |

|                 | 1.5   | Thesis Outline                                          | (   |

| 2               | Con   | version of Electrical Energy                            | 7   |

|                 | 2.1   | Introduction                                            | 7   |

|                 | 2.2   | Grid Connected Voltage Source Inverters                 | 8   |

|                 |       | 2.2.1 AC Source/Sink                                    | (   |

|                 |       | 2.2.2 Filter Components                                 | 12  |

|                 |       | 2.2.3 DC Source/Sink                                    | 15  |

|                 |       | 2.2.4 Voltage Source Inverters                          | 15  |

|                 |       | 2.2.5 VSI System Architecture                           | 16  |

|                 | 2.3   | Topologies                                              | 17  |

|                 |       | 2.3.1 Two-level VSI                                     | 1   |

|                 |       | 2.3.2 Multilevel Voltage Source Inverters               | 18  |

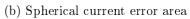

|                 | 2.4   | Diode Clamped Multilevel Inverters                      | 26  |

|                 | 2.5   | Summary of Electrical Energy Conversion                 | 28  |

| 3               | Con   | trol of Voltage Source Inverters                        | 29  |

|                 | 3.1   | Space Vector Representation of Three-Phase Systems      | 3(  |

|                 | 3.2   | Current/Voltage Relationship                            | 33  |

|                 | 3.3   | System Definitions for Space Vector Based Control Algo- |     |

|                 |       | rithms                                                  | 3   |

|                 | 3.4   | Indirect Current Control Techniques                     | 3!  |

|                 |       | 3.4.1 Space Vector Based PWM                            | 36  |

#### Contents

|   | 3.5 | Direct Current Control Techniques                        |

|---|-----|----------------------------------------------------------|

|   |     | 3.5.1 Three-phase Hysteresis Current Controller          |

|   |     | 3.5.2 $\alpha\beta$ Direct Current Control               |

|   |     | 3.5.3 Switched Diamond Hysteresis Direct Current Control |

|   | 0.0 | 3.5.4 Predictive Current Control                         |

|   | 3.6 | Comparison of Control Techniques                         |

|   | 3.7 | Summary of Control Techniques                            |

| 4 | Sim | plified Space Vector Modulation Techniques               |

|   | 4.1 | Problem Statement                                        |

|   | 4.2 | Existing Simplification Methods                          |

|   | 4.3 | The Idea - Hexagonal Bravais Lattice                     |

|   | 4.4 | Derivation of $a_*b_*$ -Transformation                   |

|   |     | $4.4.1$ Multilevel $a_*b_*$ -Transformation              |

|   | 4.5 | Determination of Space Vectors and Switching Signals     |

|   |     | 4.5.1 Determination of space vectors                     |

|   |     | 4.5.2 Determination of switching signals                 |

|   | 4.6 | Redundant Space Vectors                                  |

|   | 4.7 | Summary of Chapter 4                                     |

| 5 | Sca | lar Hysteresis Control                                   |

| _ | 5.1 | Introduction                                             |

|   | 5.2 | Basic Considerations                                     |

|   | _   | 5.2.1 System Description                                 |

|   | 5.3 | Sector and Tolerance Band Geometry                       |

|   | 0.0 | 5.3.1 Sector Geometry                                    |

|   |     | 5.3.2 Tolerance Band Geometry                            |

|   |     | 5.3.3 Tolerance Area                                     |

|   | 5.4 | Principle of the SHC Method                              |

|   | 0.1 | 5.4.1 Selection of Current Error Reducing Output Vector  |

|   | 5.5 | Summary of the SHC Concept                               |

|   | 5.6 | Simulations, Characteristics and Evaluation Criteria     |

|   | 5.7 | Higher Level Consideration                               |

|   | J., | 5.7.1 Three-Level Inverter System                        |

|   |     | 5.7.2 Five-Level Inverter System                         |

|   | 5.8 | Reference Seeking Algorithm                              |

|   | 0.0 | 5.8.1 Seeking Cases                                      |

|   |     | 5.8.2 Additional Hysteresis Limit                        |

|   |     | 5.8.3 Selection of Next Sector                           |

|   |     | 5.8.4 Negligibility of the Ohmic Component               |

|   |     | o.o. + regustomety of the Online Component               |

|    |       | 5.8.5   | Summary of the SHC Concept with Reference Se-        |

|----|-------|---------|------------------------------------------------------|

|    |       | 5.8.6   | eking Algorithm                                      |

|    |       | 5.8.7   | Advanced Seeking Algorithm                           |

|    | 5.9   | Summ    | nary of Scalar Hysteresis Control                    |

| 6  | Sim   |         | s and Experimental Verification                      |

|    | 6.1   |         | ation Results                                        |

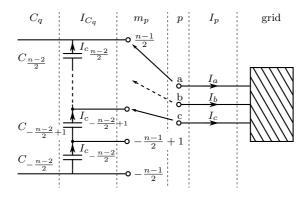

|    |       | 6.1.1   | Dead-Time Generation                                 |

|    |       | 6.1.2   | Block-Time                                           |

|    |       | 6.1.3   | DC-Link Balancing                                    |

|    |       | 6.1.4   | FPGA Delay Times                                     |

|    |       | 6.1.5   | Simulations, Characteristics and Evaluation Criteria |

|    |       | 6.1.6   | Seeking Cases                                        |

|    | 6.2   | Exper   | imental Verification                                 |

|    |       | 6.2.1   | Experimental Setup                                   |

|    |       | 6.2.2   | Measurements                                         |

|    |       | 6.2.3   | Seeking Cases                                        |

|    |       | 6.2.4   | Additional Measurements                              |

|    | 6.3   | Summ    | nary of Simulation and Experimental Verification     |

| 7  | Con   | clusion | and Future Work                                      |

|    | 7.1   | Concl   | usions and Contributions                             |

|    | 7.2   | Future  | e Work                                               |

|    | 7.3   | Public  | cations and Patent Applications of the Author        |

|    |       | 7.3.1   | Results Related to Current Control Techniques for    |

|    |       |         | Multilevel Systems                                   |

|    |       | 7.3.2   | Results Related to Applications for Current Con-     |

|    |       |         | trol Techniques                                      |

|    |       | 7.3.3   | Patent Applications                                  |

| Bi | bliog | raphy   |                                                      |

| Α  | Gan   | aric Dú | C-link balancing                                     |

|    |       |         |                                                      |

| В  | Stat  | te Mac  | hine                                                 |

| C  | Exp   | erimen  | tal Platform                                         |

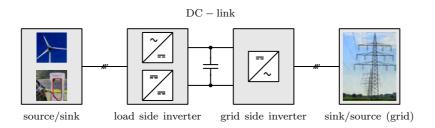

| Typical example of a frequency inverter system                 |

|----------------------------------------------------------------|

| General structure of a grid connected Voltage Source In-       |

| verter (VSI)                                                   |

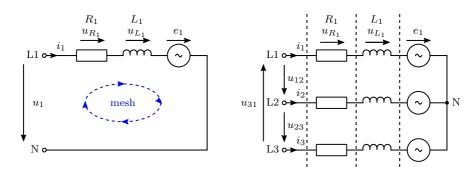

| Equivalent circuit of single-phase and three-phase AC sour-    |

| ce or sink                                                     |

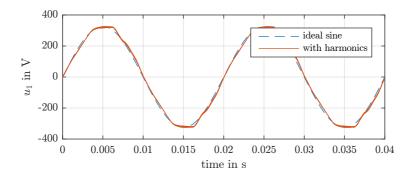

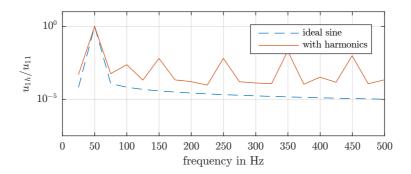

| Ideal voltage (dashed) and measured voltage of phase L1 .      |

| Ideal (dashed) and measured real voltage spectrum of phase L1  |

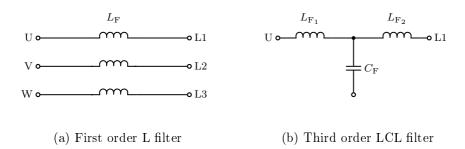

| Typical three phase filter structures                          |

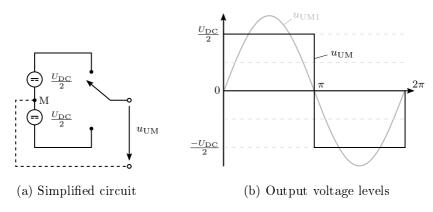

| Circuit and output voltage of a single phase two-level VSI     |

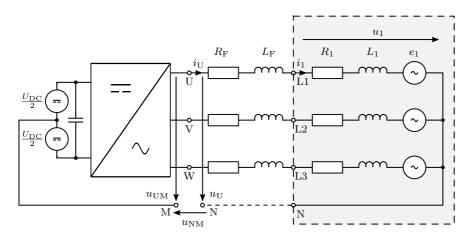

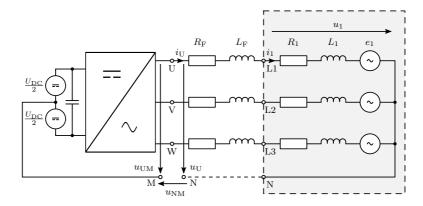

| VSI system architecture and labels for all components, vol-    |

| tages and currents                                             |

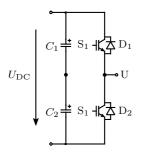

| Two-level inverter structure                                   |

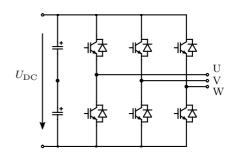

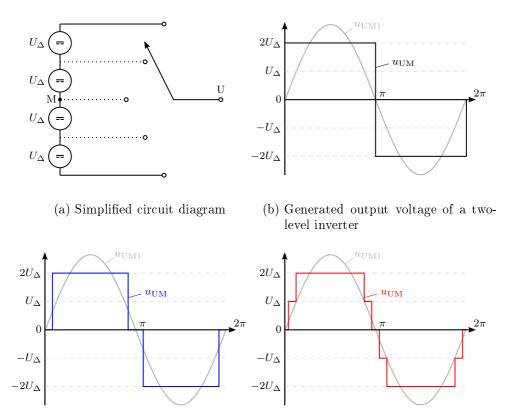

| Simplified circuit diagram and examples of the generated       |

| output voltages of a two-, three- and five-level inverter and  |

| their respective fundamental components                        |

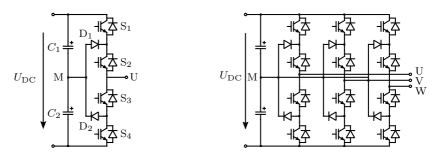

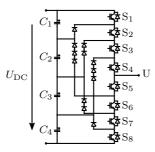

| NPC inverter                                                   |

| Single-phase five-level inverter                               |

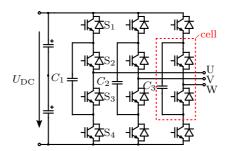

| Three-phase flying capacitor inverter                          |

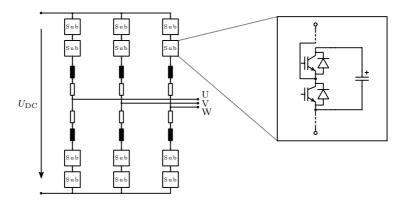

| Three phase three-level MMC inverter with a sub-module circuit |

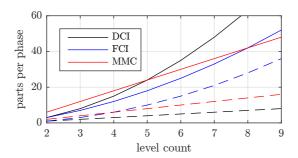

| Total number of parts per phase / Number of parts to be        |

| monitored (dashed)                                             |

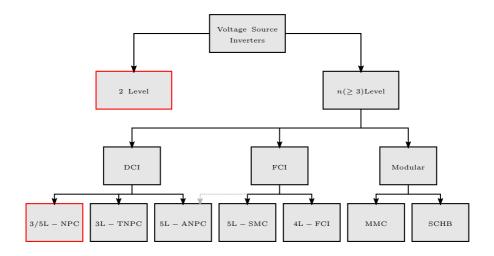

| Multilevel Inverter Topologies                                 |

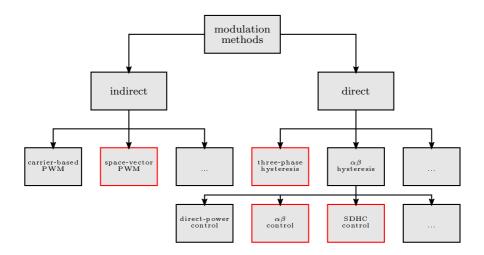

| Direct and indirect current control methods                    |

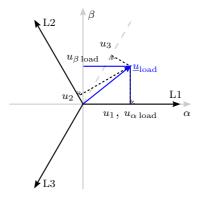

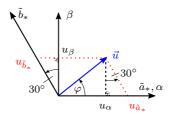

| Geometrical representation of Clarke transformation            |

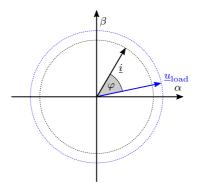

| Relationship between current and voltage                       |

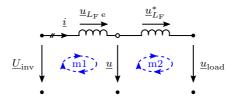

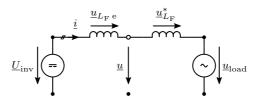

| Simplified circuit of a VSI system with currents and volta-    |

| ges used for space vector based control algorithms             |

| Simplified circuit of a VSI system set-point and error rela-   |

| ted inductive component                                        |

|                                                                |

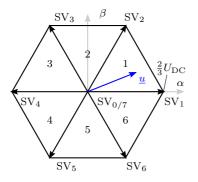

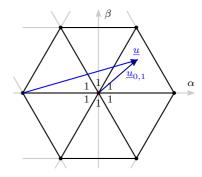

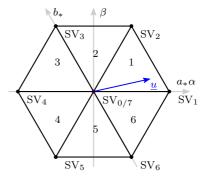

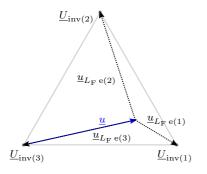

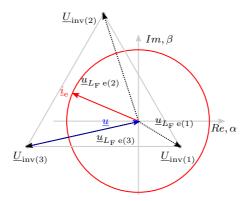

| 3.6  | Space vector representation of averaged inverter output voltage $\underline{u}$ |

|------|---------------------------------------------------------------------------------|

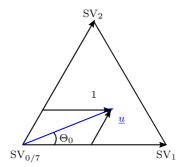

| 3.7  | Space vector diagram and sector used for SVPWM                                  |

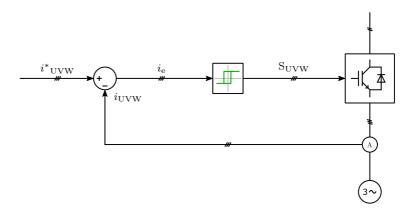

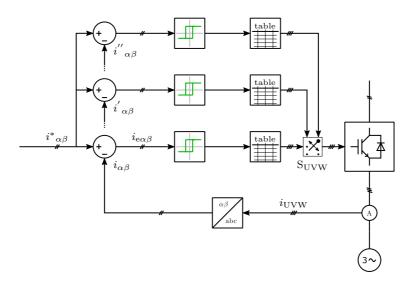

| 3.8  | Simplified diagram of a three-phase hysteresis controller .                     |

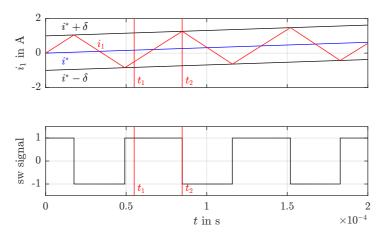

| 3.9  | Time segment of hysteresis based controlled current with                        |

| 0.0  | corresponding switching signal                                                  |

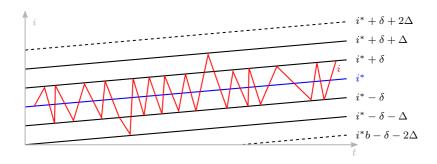

| 3.10 | Tolerance bands of $n$ level hysteresis controller                              |

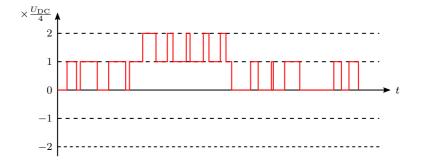

|      | Output voltage levels of a single phase five level inverter .                   |

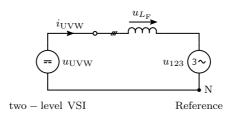

|      | Simplified circuit of two-level inverter system                                 |

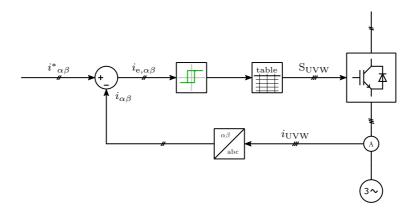

|      | Working principle diagram of an $\alpha\beta$ controller                        |

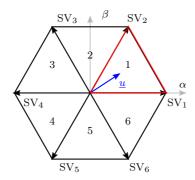

|      | Two-level space vector diagram with $\alpha\beta$ voltage                       |

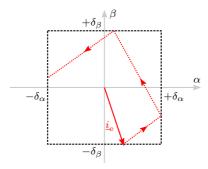

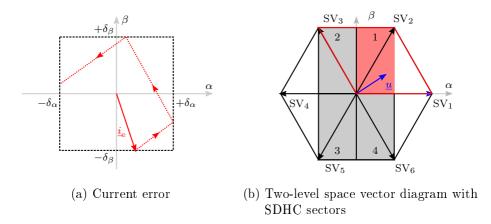

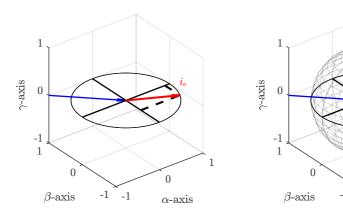

|      | Current error and tolerance area                                                |

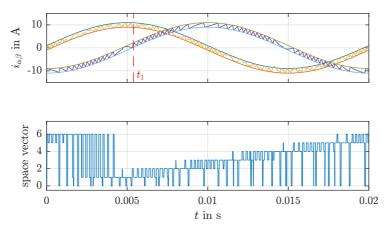

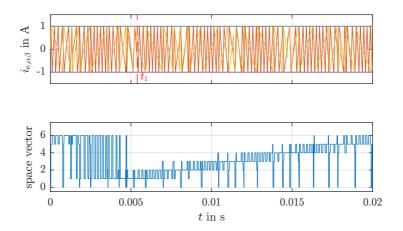

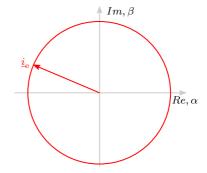

|      | $\alpha\beta$ -currents and corresponding space vectors                         |

|      | Tolerance band violation during $\alpha\beta$ hysteresis control                |

|      | Principle diagram of a Switched Diamond Hysteresis Con-                         |

| 0.10 | trol (SDHC) controller                                                          |

| 3 19 | Current error and two-level SDHC space vector diagram .                         |

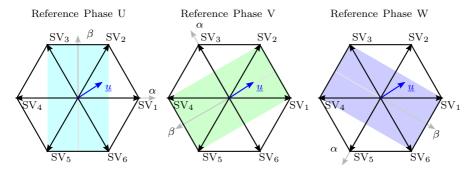

|      | Two-level space vector diagram with rotated sectors                             |

|      | $\alpha\beta$ -currents and corresponding space vectors                         |

|      | Time interval where tolerance band violation during $\alpha\beta$               |

| J    | hysteresis control occurred                                                     |

| 3.23 | Two-level and three-level space vector diagram with refe-                       |

|      | rence voltage and corresponding rectangular sector                              |

| 3.24 | Predictive current control                                                      |

|      |                                                                                 |

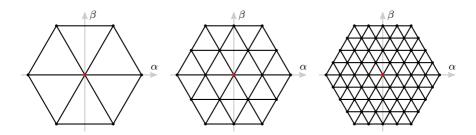

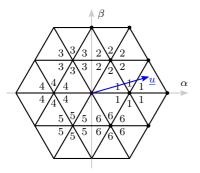

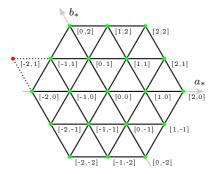

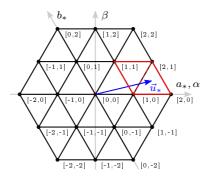

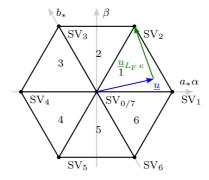

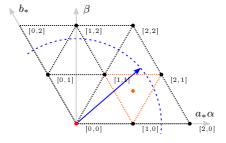

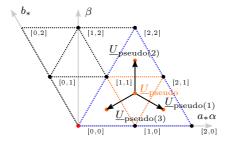

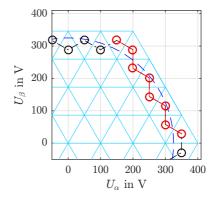

| 4.1  | Space vector diagram for a two-, three- and five-level inverter                 |

| 4.2  | Basic principle of simplification method I                                      |

| 4.3  | Basic principle of simplification method II                                     |

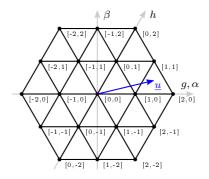

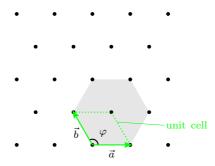

| 4.4  | Two dimensional hexagonal bravais lattice                                       |

| 4.5  | Geometric representation of the proposed transformation                         |

|      | and relationship to $\alpha\beta$ transformation                                |

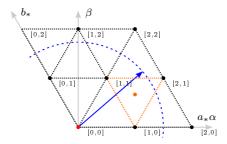

| 4.6  | Example of a three-level space vector diagram with $a_*b_*$                     |

|      | coordinates                                                                     |

| 4.7  | Three-level space vector diagram with unit cell (red) and                       |

|      | its base vector $[1,0]$                                                         |

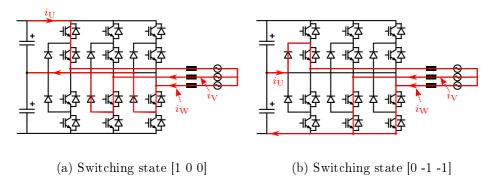

| 4.8  | Current flow for redundant switching states                                     |

| 5.1  | Simplified equivalent circuit of grid connected inverter sys-                   |

|      | tems                                                                            |

| 5.2  | Two level space vector diagram with reference voltage                           |

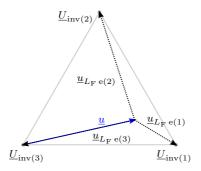

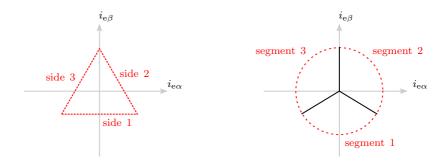

| 5.3  | Sector geometry and resulting voltages                                                 |

|------|----------------------------------------------------------------------------------------|

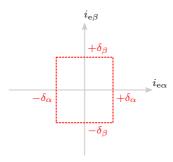

| 5.4  | Rectangular current error tolerance area                                               |

| 5.5  | Triangular and circular tolerance areas for the current error                          |

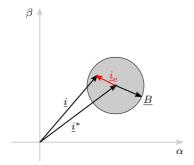

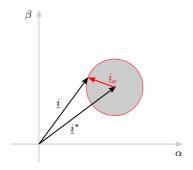

| 5.6  | Current vectors, error current and tolerance band                                      |

| 5.7  | Current error and space vector diagram                                                 |

| 5.8  | Triangular sector and current error in $\alpha\beta$ -plane                            |

| 5.9  | Combined representation of triangular sector and current                               |

|      | error                                                                                  |

| 5.10 | Voltage vectors and current error vector resulting from the                            |

|      | triangular sector                                                                      |

|      | Basic concept and overview of the SHC controller                                       |

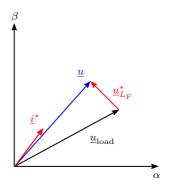

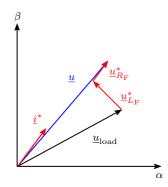

| 5.12 | Two-level space vector diagram with stationary voltage $\underline{u}_{\mathrm{load}}$ |

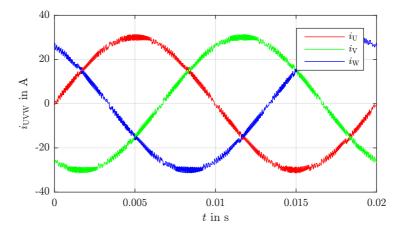

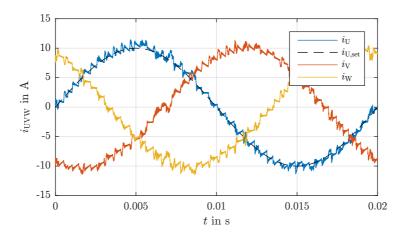

| 5.13 | Inverter output current                                                                |

| 5.14 | Three phase error current                                                              |

| 5.15 | Specific time section of stationary operating point                                    |

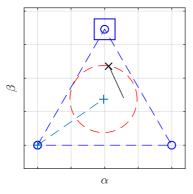

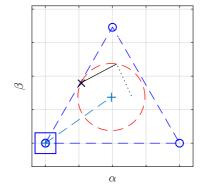

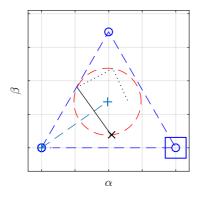

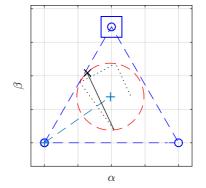

| 5.16 | Exemplary trigger positions for stationary operating point                             |

| 5.17 | Two-level space vector diagram with grid voltage $\underline{u}_{\mathrm{load}}$       |

| 5.18 | Inverter output current for nominal operating point                                    |

| 5.19 | Space vectors for one period of nominal operating point .                              |

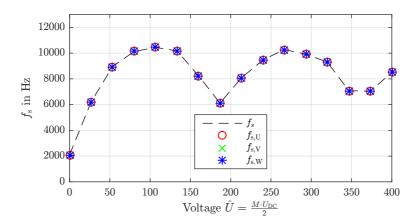

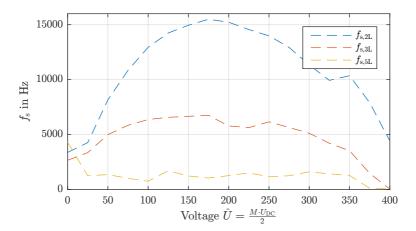

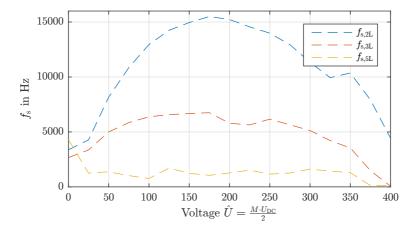

| 5.20 | Average witching frequency per phase and total versus mo-                              |

|      | dulation index                                                                         |

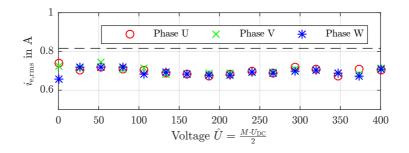

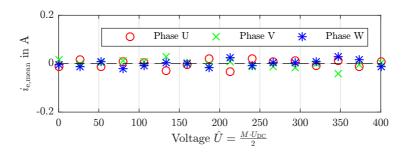

| 5.21 | Mean value of current error versus modulation index                                    |

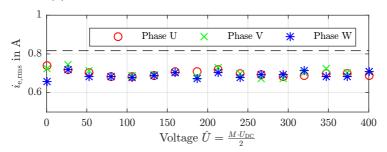

| 5.22 | RMS value of current error versus modulation index                                     |

| 5.23 | Time interval where a set-point change from 30 A to -30                                |

|      | A occurs                                                                               |

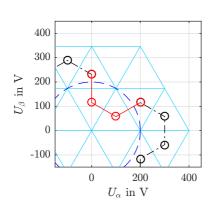

| 5.24 | Three- and Five-level space vector diagram                                             |

| 5.25 | Three-level inverter output current                                                    |

| 5.26 | Switching frequency versus modulation index                                            |

| 5.27 | Mean and RMS value of the current error of a three-level                               |

|      | inverter versus modulation index                                                       |

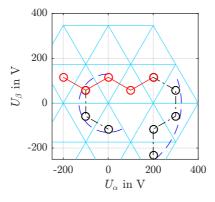

| 5.28 | Five-level inverter output current                                                     |

| 5.29 | Switching frequency versus modulation index                                            |

| 5.30 | Mean and RMS value of the current error of a five-level                                |

|      | inverter versus modulation index                                                       |

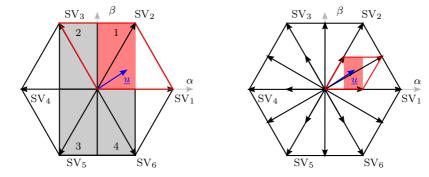

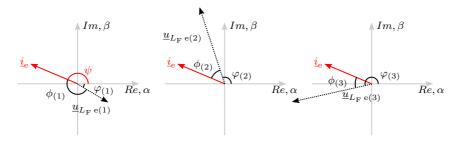

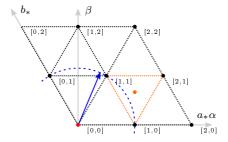

| 5.31 | Seeking Case 1                                                                         |

| 5.32 | Seeking Case 2                                                                         |

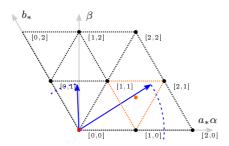

|      | Seeking Case 3                                                                         |

|      | Current vectors, error current and tolerance bands                                     |

|      | Extract of three-level space vector diagram                                            |

| 5.36         | Geometrical representation of all voltage and current vec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | tors needed for the selection of the next sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

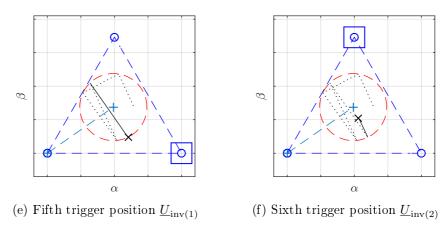

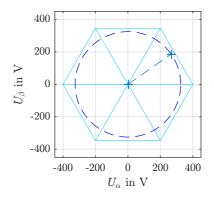

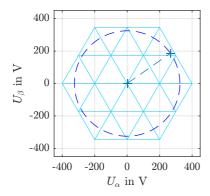

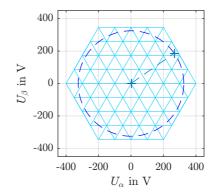

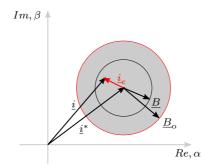

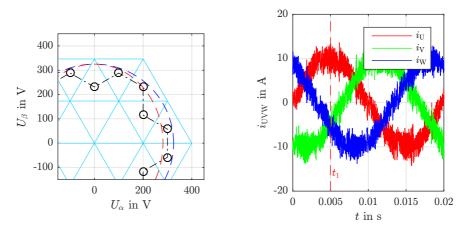

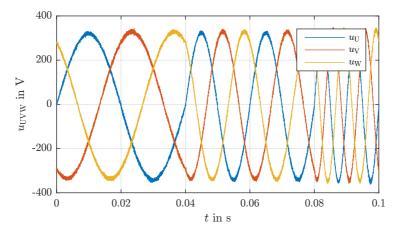

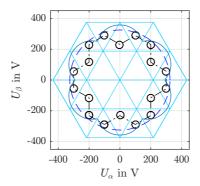

| 5.37         | Averaged inverter output voltage $\underline{u}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

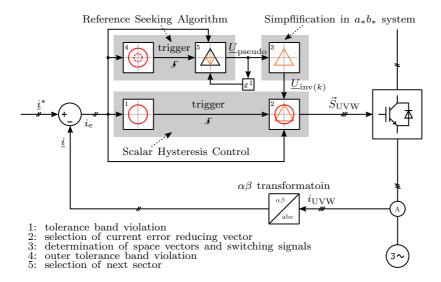

| 5.38         | Basic concept and overview of the SHC controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

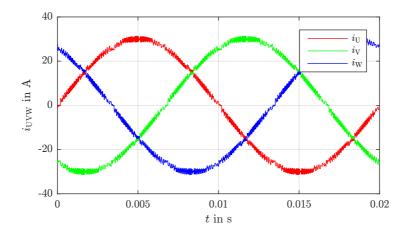

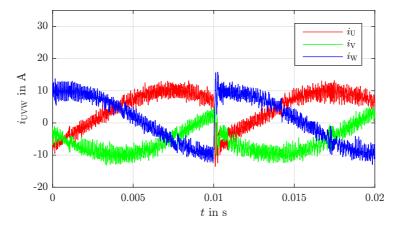

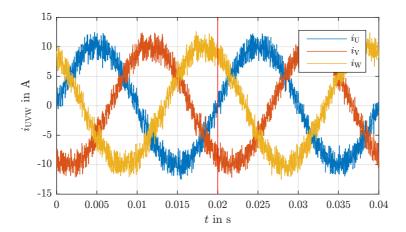

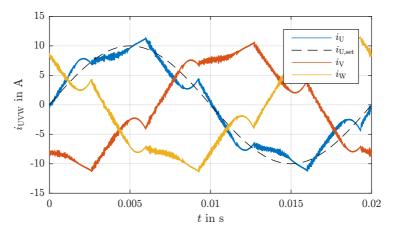

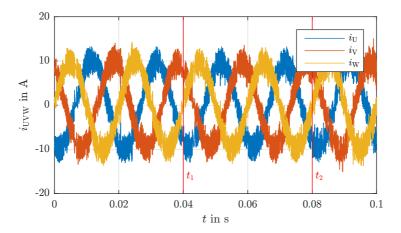

|              | Inverter output current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

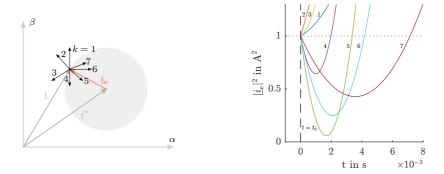

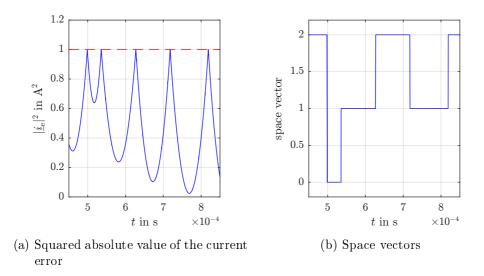

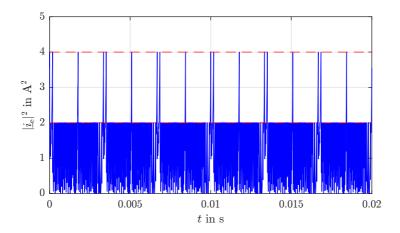

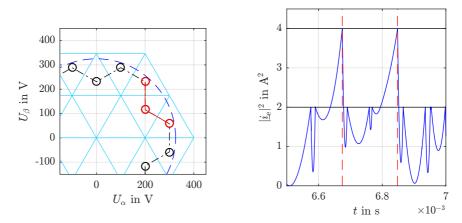

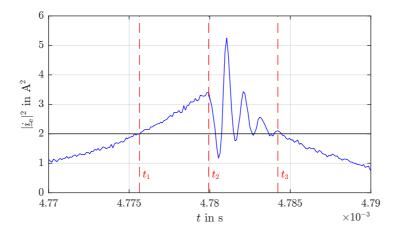

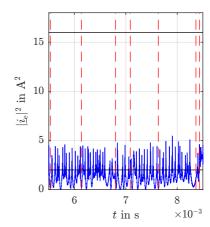

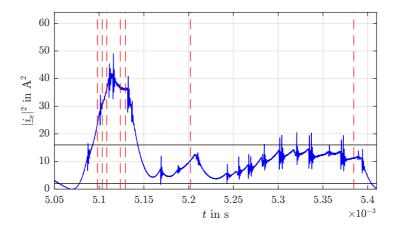

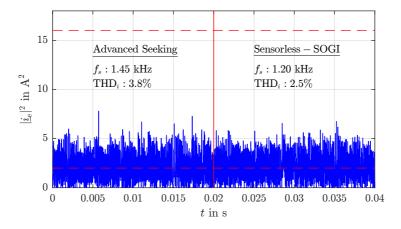

| 5.40         | Squared absolute value of the current error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

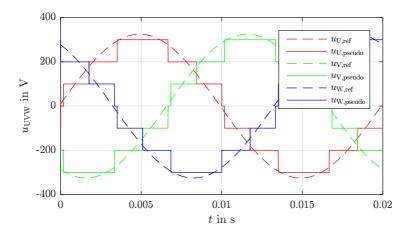

| 5.41         | Three-phase pseudo reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

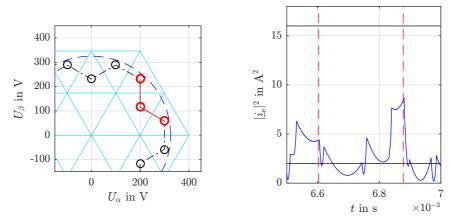

| 5.42         | Time segment with the three sectors (red) and two sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | changes caused by the violation of the outer tolerance band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | for seeking case 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

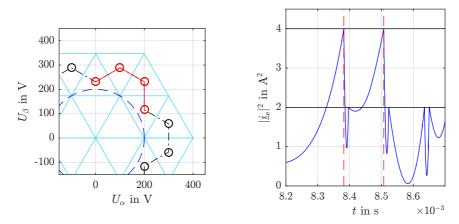

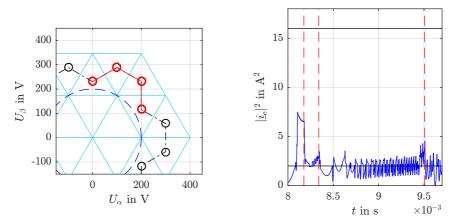

| 5.43         | Time segment for seeking case 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

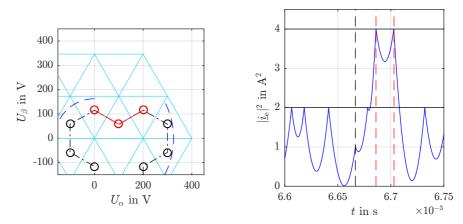

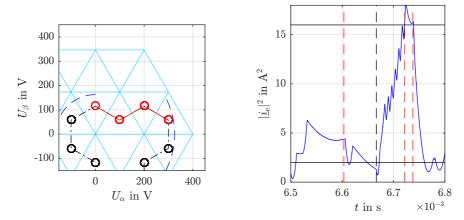

| 5.44         | Time segment for seeking case 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

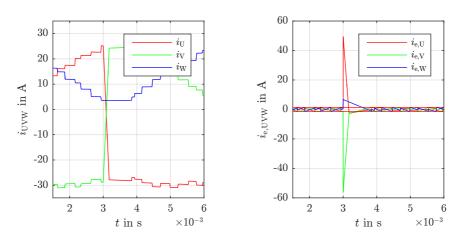

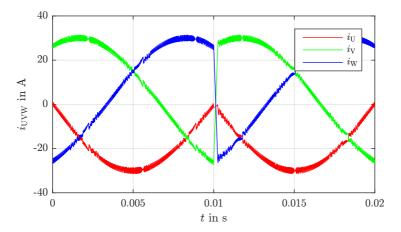

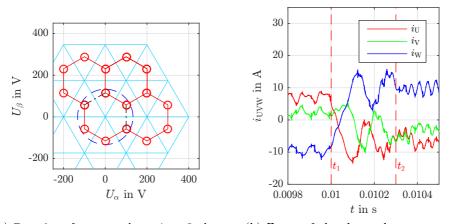

| 5.45         | Three phase current with set-point change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

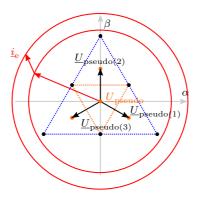

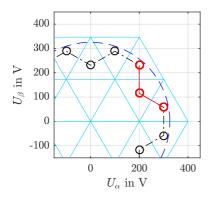

| 5.46         | Pseudo reference voltage in $\alpha\beta$ plane for seeking case 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.47         | Time segment with sector change of standard (black) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | advanced (blue) seeking algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <i>C</i> 1   | The maintain and a second of the second of t |

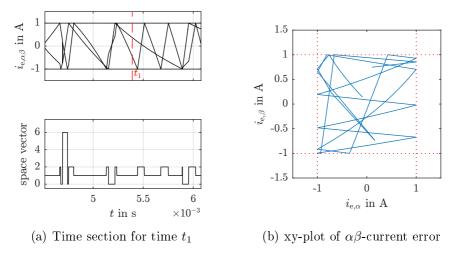

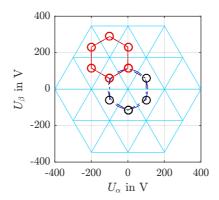

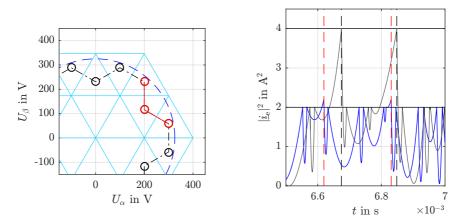

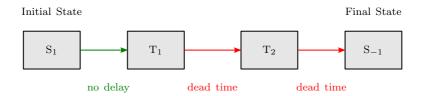

| $6.1 \\ 6.2$ | Transition example from initial State $S_1$ to final $S_{-1}$ Oscillation of the current error and time comment in which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

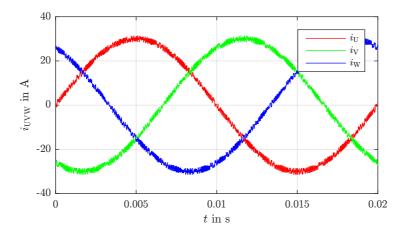

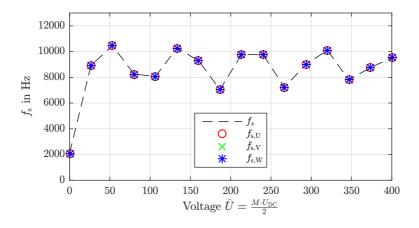

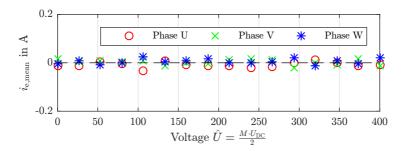

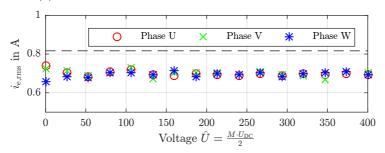

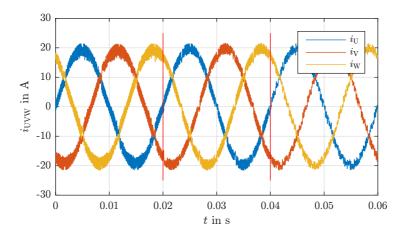

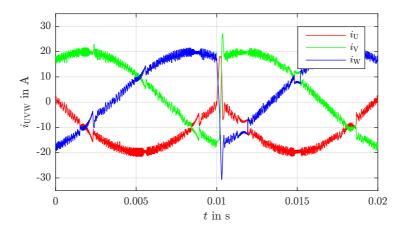

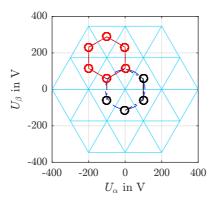

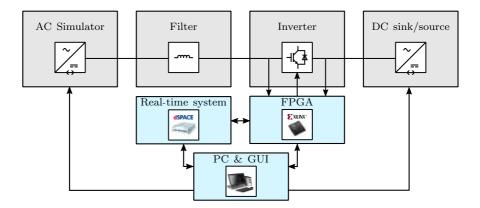

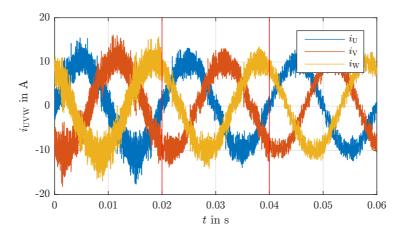

| 0.2          | Oscillation of the current error and time segment in which the current controller should be de-activated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |