# MICROARCHITECTURAL TECHNIQUES TO EXPLOIT REPETITIVE COMPUTATIONS AND VALUES

**Carlos Molina Clemente**

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya Barcelona (SPAIN)

**Advisors:**

Antonio Gonzalez Colás Universitat Politècnica de Catalunya

Jordi Tubella Murgadas Universitat Politècnica de Catalunya

## A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor en Informática

July 2005

"Once upon a time there was..." Classical Fairy Tales Beginning.

# PREFACE

Data dependences are some of the most important hurdles that limit the performance of current microprocessors. Some studies have shown that some applications cannot achieve more than a few tens of instructions per cycle in an ideal processor with the sole limitation of data dependences. This suggests that techniques for avoiding the serialization caused by them are important for boosting the instruction-level parallelism and will be crucial for future microprocessors.

Moreover, innovation and technological improvements in processor design have outpaced advances in memory design in the last ten years. Therefore, the increasing gap between processor and memory speeds has motivated that current high performance processors focus on cache memory organizations to tolerate growing memory latencies. Caches attempt to bridge this gap but do so at the expense of large amounts of die area, increment of the energy consumption and higher demand of memory bandwidth that can be progressively a greater limit to high performance.

We propose several microarchitectural techniques that can be applied to various parts of current microprocessor designs to improve the memory system and to boost the execution of instructions. Some techniques attempt to ease the gap between processor and memory speeds, while the others attempt to alleviate the serialization caused by data dependences. The underlying aim behind all the proposed microarchitectural techniques is to exploit the repetitive behaviour in conventional programs.

Instructions executed by real-world programs tend to be repetitious, in the sense that most of the data consumed and produced by several dynamic instructions are often the same. We refer to the repetition of any source or result value as *Value Repetition* and the repetition of source values and operation as *Computation Repetition*. In particular, the techniques proposed for improving the memory system are based on exploiting the value repetition produced by store instructions, while the techniques proposed for boosting the execution of instructions are based on exploiting the execution of instructions are based on exploiting the computation repetition produced by all the instructions.

# ACKNOWLEDGEMENTS

Supongo que todos tenemos nuestros efectos mariposa. El que ha marcado profesionalmente mi vida, y que hace que esté escribiendo estas líneas, apareció una tarde de verano de hace bastantes años cuando cursaba mis últimos años de carrera. Mi falta de puntualidad por aquel entonces hizo que respondiera a una llamada de teléfono cuando ya salía por la puerta de casa. Buscaban a un becario de docencia para el departamento de arquitectura de computadores. Fue Jordi Tubella, uno de mis directores de tesis, quien hizo esa llamada. Mi primer agradecimiento va para él. Más tarde apareció Antonio González, mi otro director, quien me propuso hacer un Erasmus tras el cual me brindó la oportunidad de cursar el doctorado. Para él, también mi agradecimiento. De hecho, para ambos el agradecimiento es doble. No sólo por estar en momentos que han marcado que hoy esté vinculado al mundo universitario, sino por lo mucho que he aprendido de ellos en estos años de doctorado. Sin su confianza y paciencia hoy no estaría aquí.

En este largo camino, hay otros compañeros de viaje a los que debo agradecer los buenos ratos que hemos pasado y lo mucho que también me han enseñado. Me estoy refiriendo a los estudiantes de doctorado del departamento de arquitectura de computadores que como yo han intentado llegar a buen puerto. Todos ellos sin excepción, siempre han tenido tiempo para aclararme cualquier duda y para hacer más ameno este viaje. Especialmente quiero agradecérselo a Pedro, Llorenç, Suso, Pepe, Ramón y Carles que estuvieron desde el principio y con los que he pasado grandes momentos.

Finalmente, quisiera agradecer a mi familia el brindarme un entorno tan propicio para hacer tan llevadero todo este trabajo. Sobre todo a mis padres por darme la tranquilidad de estudiar sin ninguna otra preocupación. A ellos va dedicada esta tesis. También quiero agradecer a mi hermano que sea mi hermano. Y como no, a Esther. Tú eres el efecto mariposa que da sentido a mi vida.

A mis padres Rafael y Olga

# **CONTENTS**

| PREFACE                                                         | . 3 |

|-----------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                | . 5 |

| CONTENTS                                                        | . 9 |

| CHAPTER 1. INTRODUCTION                                         | 15  |

| 1.1. MOTIVATION                                                 | 16  |

| <b>1.2. REPETITION IN CONVENTIONAL PROGRAMS</b>                 | 17  |

| 1.2.1. Computation and Value Repetition                         | 17  |

| 1.2.2. Analysis of Repetition                                   | 18  |

| 1.2.2.1. Amount of Computation Repetition                       | 18  |

| 1.2.2.2. Amount of Value Repetition                             | 20  |

| 1.3. MAIN CONTRIBUTIONS                                         | 22  |

| 1.3.1. Contributions to Improve the Memory System               | 22  |

| 1.3.2. Contributions for Boosting the Execution of Instructions | 23  |

| 1.3.2.1. Instruction-Level Reuse                                | 23  |

| 1.3.2.2. Trace-Level Reuse                                      | 24  |

| 1.3.2.3. Trace-Level Speculation                                | 25  |

| 1.4. METHODOLOGY AND EXPERIMENTAL FRAMEWORK                     | 27  |

| 1.4.1. Tools                                                    | 27  |

| 1.4.2. SPEC Benchmarks                                          | 28  |

| 1.4.3. Baseline Microarchitecture                               | 30  |

| CHAPTER 2. VALUE REPETITION IN DATA CACHES                      | 31  |

| 2.1. INTRODUCTION                                               | 32  |

| 2.2. VALUE REPETITION IN THE SAME STORAGE LOCATION              | 34  |

| 2.2.1. Overview                                                     | . 34 |

|---------------------------------------------------------------------|------|

| 2.2.2. Cache Write Policies                                         | . 35 |

| 2.2.3. Performance Evaluation                                       | . 36 |

| 2.2.3.1. Experimental Framework                                     | . 36 |

| 2.2.3.2. Analysis of Results                                        | . 38 |

| 2.3. REDUNDANT STORE MECHANISM FOR REDUCING MEMORY TRAFFIC $\ldots$ | . 39 |

| 2.3.1. General Description                                          | . 39 |

| 2.3.2. Performance Evaluation                                       | . 41 |

| 2.3.2.1. Experimental Framework                                     | . 41 |

| 2.3.2.2. Analysis of Results                                        | . 41 |

| 2.4. VALUE REPETITION IN SEVERAL STORAGE LOCATIONS                  | 43   |

| 2.4.1. Overview                                                     | 43   |

| 2.4.2. Performance Evaluation                                       | . 44 |

| 2.4.2.1. Experimental Framework                                     | . 44 |

| 2.4.2.2. Analysis of Results                                        | . 45 |

| 2.5. NON-REDUNDANT DATA CACHE                                       | . 48 |

| 2.5.1. General Description                                          | 48   |

| 2.5.2. Data Value Inlining                                          | 50   |

| 2.5.3. Static Analysis                                              | 51   |

| 2.5.3.1. Die Area                                                   | . 51 |

| 2.5.3.2. Latency                                                    | . 52 |

| 2.5.3.3. Energy Consumption                                         | 53   |

| 2.5.4. Dynamic Analysis                                             | . 54 |

| 2.5.4.1. Replication in Conventional L2 Caches                      | 55   |

| 2.5.4.2. Inlining Performance                                       | . 55 |

| 2.5.4.3. Miss Rate vs. Die Area                                     | 56   |

| 2.6. RELATED WORK                                                   | . 58 |

| 2.7. CONCLUSIONS                                                    | 61   |

| CHAPTER 3. INSTRUCTION LEVEL REUSE                                  | . 63 |

| 3.1. INTRODUCTION                                                   |      |

|                                                                     |      |

| 3.2. THE PERFORMANCE POTENTIAL OF INSTRUCTION LEVEL REUSE           | . 03 |

| 3.2.1. Evaluation Methodology                             | 66  |

|-----------------------------------------------------------|-----|

| 3.2.1.1. IPC for an Infinite Window Machine               | 66  |

| 3.2.1.2. IPC for a Limited Window Machine                 | 67  |

| 3.2.1.3. Experimental Framework                           | 67  |

| 3.2.2. Limits of Instruction Level Reusability            | 68  |

| 3.2.3. Performance Improvement of Instruction Level Reuse | 68  |

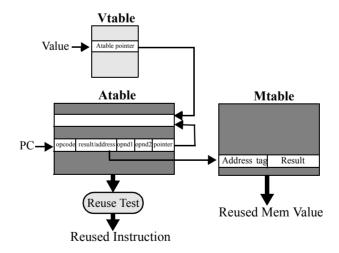

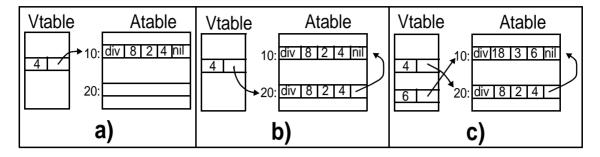

| <b>3.3. REDUNDANT COMPUTATION BUFFER</b>                  | 72  |

| 3.3.1. General Description                                | 72  |

| 3.3.2. A Working Example                                  | 74  |

| 3.3.3. Reusing From Non-Latest Results                    | 76  |

| 3.3.4. Enhanced Result Cache and Enhanced Result Buffer   | 76  |

| 3.3.5. Timing                                             | 78  |

| 3.3.6. Hybrid Redundant Computation Buffer                | 80  |

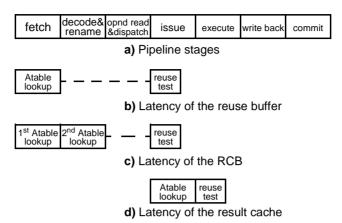

| 3.3.7. Performance Evaluation                             | 80  |

| 3.3.7.1. Experimental Framework                           | 80  |

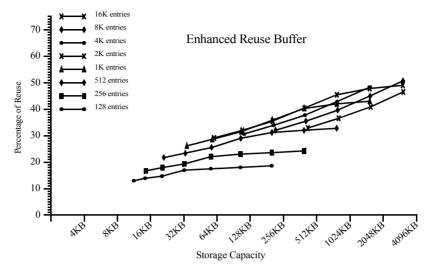

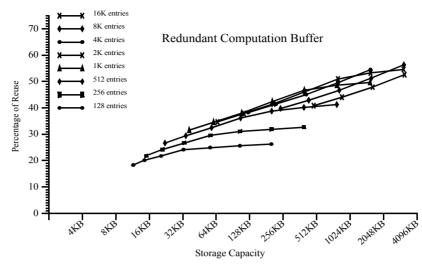

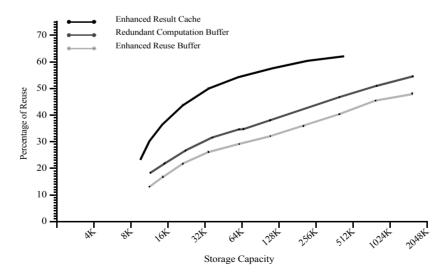

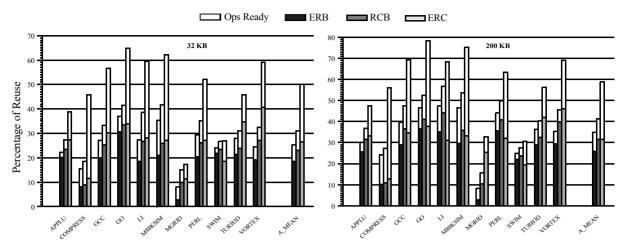

| 3.3.7.2. Basic Reuse Statistics                           | 81  |

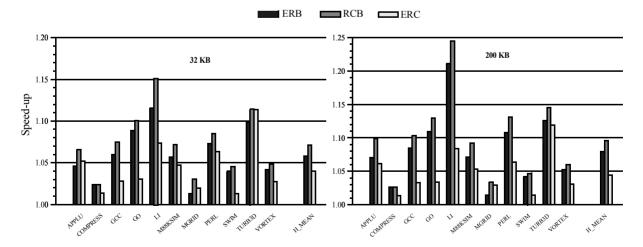

| 3.3.7.3. Performance Figures for a Superscalar Processor  | 84  |

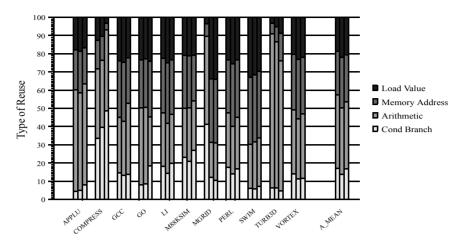

| 3.3.7.4. Performance of the Hybrid RCB Scheme             | 86  |

| 3.4. RELATED WORK                                         | 87  |

| 3.5. CONCLUSIONS                                          | 90  |

| CHAPTER 4. TRACE LEVEL REUSE                              | 91  |

| 4.1. INTRODUCTION                                         | 92  |

| 4.2. THE PERFORMANCE POTENTIAL OF TRACE-LEVEL REUSE       |     |

| 4.2.1. Evaluation Methodology                             | 93  |

| 4.2.2. Limits of Trace-Level Reusability                  |     |

| 4.2.3. Performance Improvement of Trace-Level Reuse       |     |

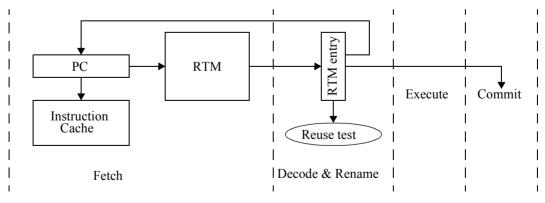

| 4.3. DESIGN ISSUES OF TRACE-LEVEL REUSE                   | 99  |

| 4.3.1. Reuse Trace Memory                                 | 99  |

| 4.3.2. Reuse Test and Processor State Update              | 100 |

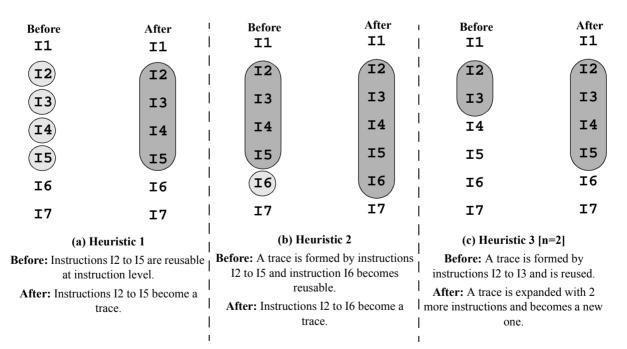

| 4.3.3. Dynamic Trace Collection                           | 101 |

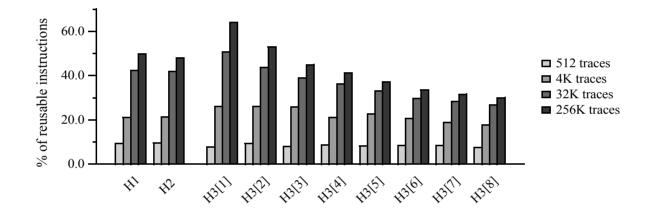

| 4.3.4. Trace-Level Reusability with Finite Tables         | 102 |

| 4.3.4.1. Experimental Framework                         | 102 |

|---------------------------------------------------------|-----|

| 4.3.4.2. Analysis of Results                            | 103 |

| 4.4. RELATED WORK                                       | 104 |

| 4.5. CONCLUSIONS                                        | 106 |

| CHAPTER 5. TRACE-LEVEL SPECULATION                      | 107 |

| 5.1. INTRODUCTION                                       | 108 |

| 5.2. APPROACHES TO TRACE-LEVEL SPECULATION              | 109 |

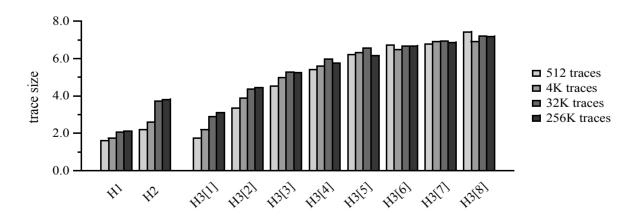

| 5.2.1. Trace-Level Speculation with Live-Input Test     | 109 |

| 5.2.2. Trace-Level Speculation with Live-Output Test    | 110 |

| 5.3. TRACE-LEVEL SPECULATIVE MULTITHREADED ARCHITECTURE | 111 |

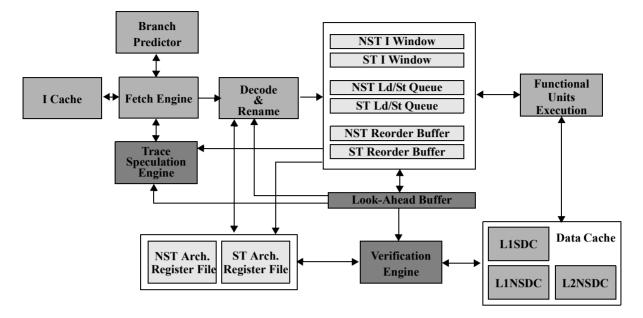

| 5.3.1. Overview                                         | 111 |

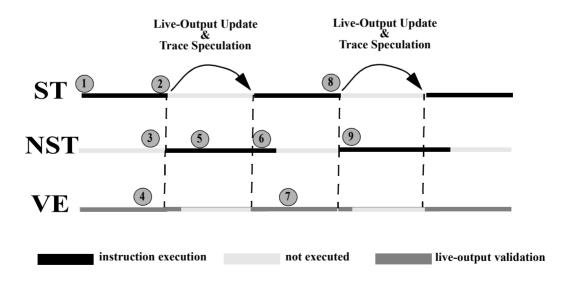

| 5.3.2. Trace Speculation Engine                         | 113 |

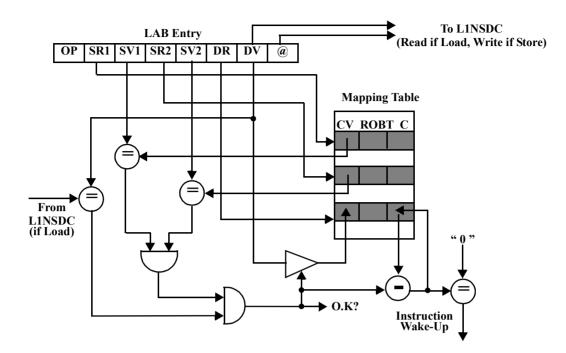

| 5.3.3. Look-Ahead Buffer                                | 114 |

| 5.3.4. Verification Engine                              | 114 |

| 5.3.5. Thread Synchronization                           | 115 |

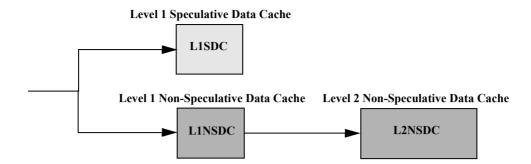

| 5.3.6. Memory Subsystem                                 | 116 |

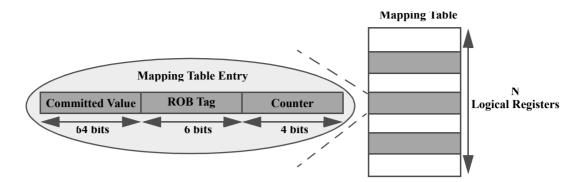

| 5.3.7. Register File                                    | 118 |

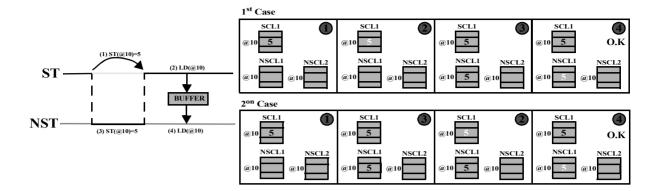

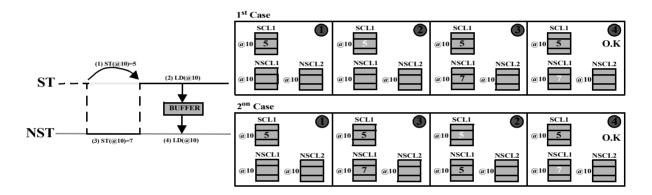

| 5.3.8. Working Example                                  | 120 |

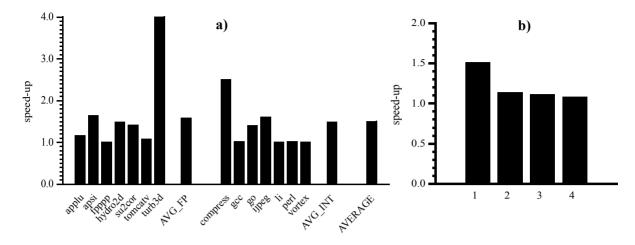

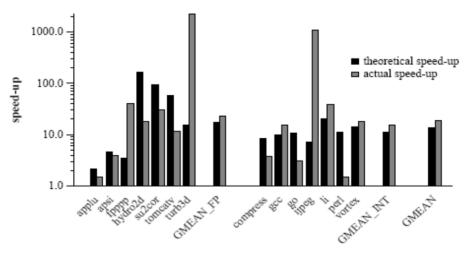

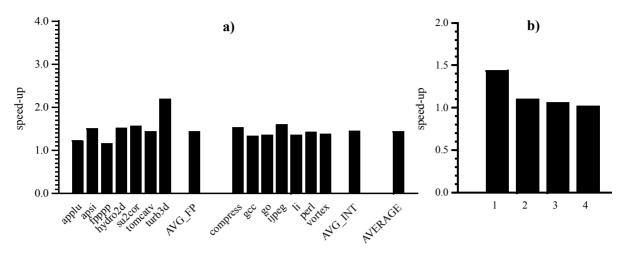

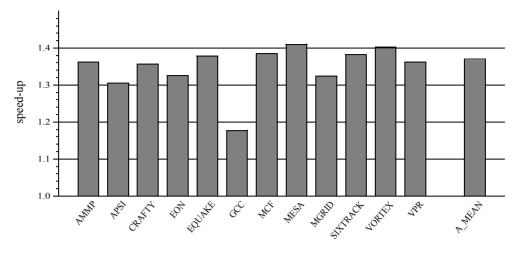

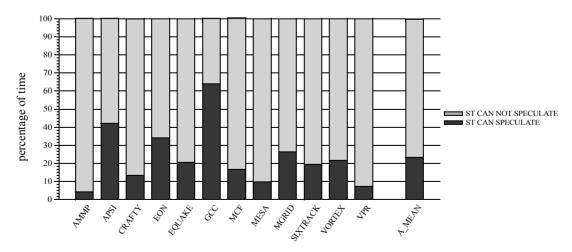

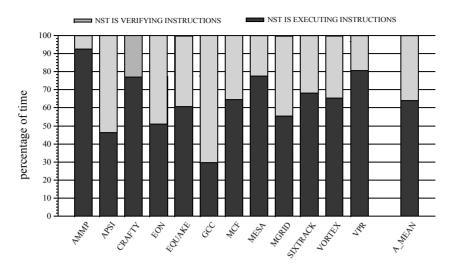

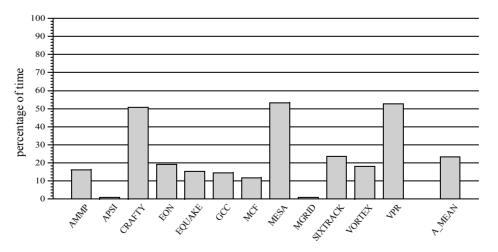

| 5.3.9. Performance Evaluation                           | 122 |

| 5.3.9.1. Experimental Framework                         | 122 |

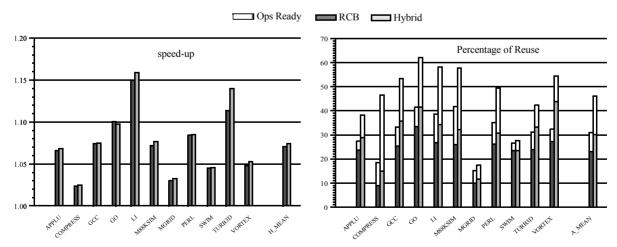

| 5.3.9.2. Analysis of Results                            | 122 |

| 5.4. EXTENSIONS TO TSMA                                 | 125 |

| 5.4.1. Reducing Misspeculation Penalty in TSMA          | 125 |

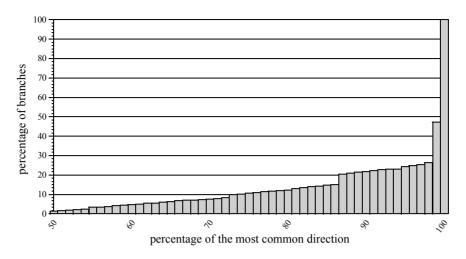

| 5.4.1.1. Thread Synchronization Analysis                | 126 |

| 5.4.1.2. Advanced Verification Engine                   | 127 |

| 5.4.2. Compiler Analysis to Support TSMA                | 129 |

| 5.4.2.1. Graph Construction                             | 129 |

| 5.4.2.2. Graph Analysis                                 | 130 |

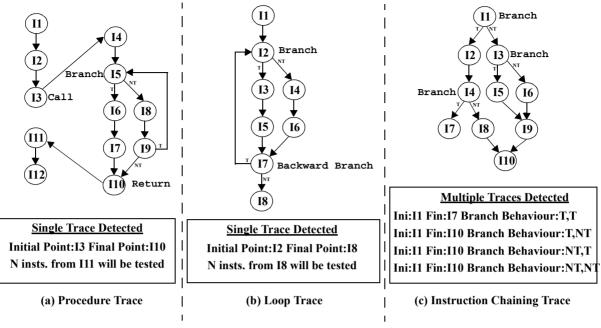

| 5.4.2.3. Procedure Trace Heuristic                      | 131 |

| 5.4.2.4. Loop Trace Heuristic                           | 132 |

| 5.4.2.5. Instruction Chaining Trace Heuristic           | 132 |

| 5.4.2.6. Hardware Modifications into the TSE                     | 133 |

|------------------------------------------------------------------|-----|

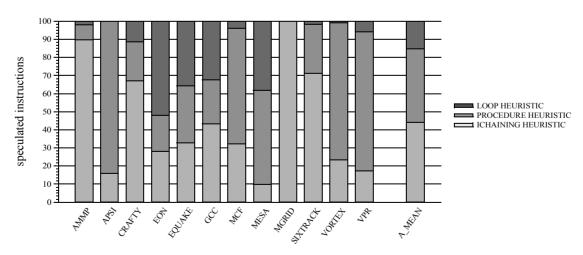

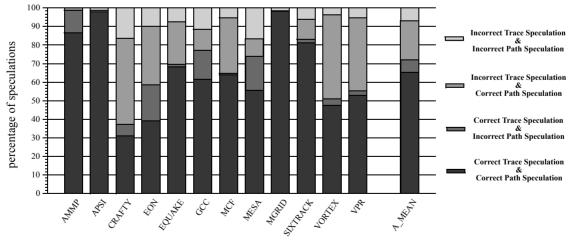

| 5.4.3. Performance Evaluation                                    | 134 |

| 5.4.3.1. Experimental Framework                                  | 134 |

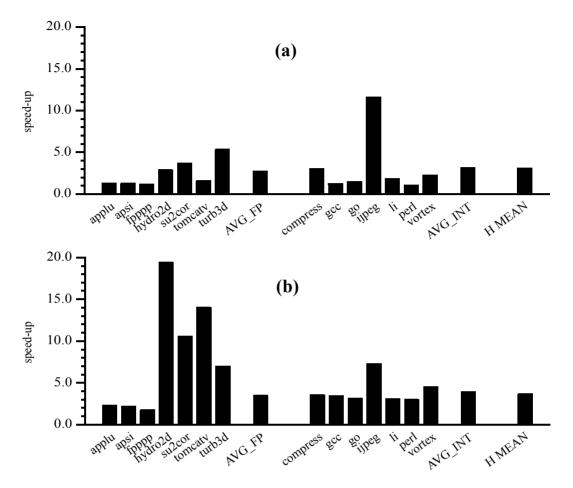

| 5.4.3.2. Analysis of Results of the Compiler Support             | 136 |

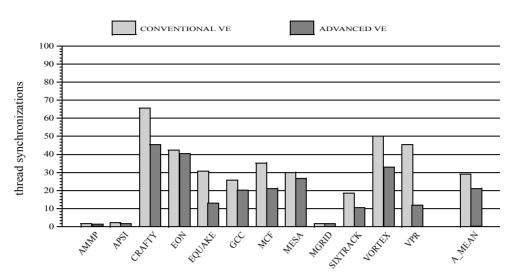

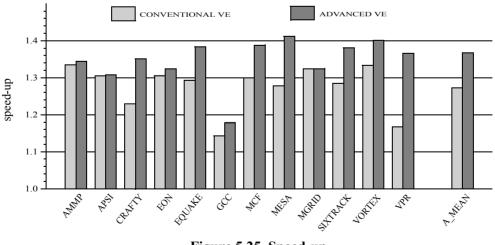

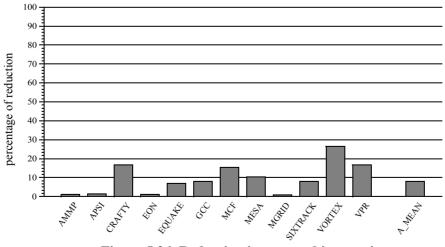

| 5.4.3.3. Analysis of Results of the Advanced Verification Engine | 141 |

| 5.5. RELATED WORK                                                | 143 |

| 5.6. CONCLUSIONS                                                 | 145 |

| CHAPTER 6. CONCLUSIONS AND FUTURE WORK                           | 147 |

| 6.1. CONCLUSIONS                                                 | 148 |

| 6.2. FUTURE WORK                                                 | 150 |

| 6.2.1. Value Repetition in Instruction Caches                    | 150 |

| 6.2.2. Program Profiling to Support Data Value Reuse Schemes     | 150 |

| 6.2.3. Quasi-Common Traces                                       | 151 |

| 6.2.4. Value Prediction in TSMA                                  | 151 |

| 6.2.5. Multiple Speculations and Threads in TSMA                 | 151 |

| APPENDIX                                                         | 153 |

| A. TRACE-LEVEL REUSE THEOREMS                                    | 153 |

| A.1. Definition of Theorems                                      | 153 |

| A.2. Definition of Terms                                         | 154 |

| REFERENCES                                                       | 157 |

| LIST OF FIGURES                                                  | 171 |

| LIST OF TABLES                                                   | 175 |

"Civilization advances by extending the number of important operations which we can perform without thinking about them" Alfred North Whitehead, English Mathematician, 1861-1947.

# Chapter 1

# INTRODUCTION

The serialization caused by data dependences and the gap between processor and memory speeds have become a key constraint in the design of current processors. Microarchitectural techniques aimed at breaking data dependences and improving the memory system are therefore becoming critical.

In this chapter we analyse the high percentage of repetition in real-world programs and introduce the work developed in this thesis.

## 1.1. Motivation

Current microprocessors designs primarily try to improve performance by increasing the clock frequency and the number of instructions that can fetch, decode, issue, execute and commit in a single cycle. Decode, execute and commit stages can manage several instructions per cycle without significant limitations, but fetch and issue stages are limited by two program characteristics: control flow and data flow [62],[125]. Control flow is defined as the sequence of execution of instructions in a program, which is determined at run time by the input data and control structures. Data flow is defined as the combination of operations and dependences which form the program and allows instructions to be executed as soon as their inputs are available, regardless of the original program order.

The program's control flow dependences, or *Control Dependences*, limit the number of instructions that can be fetched. Often, the average number of fetched instructions is below the maximum number of instructions that can be fetched in each cycle. Instruction flow techniques are still an important area of research because the throughput of the early pipeline stage determines the maximum throughput of all subsequent stages.

Issue is limited by the program's data flow dependences, or *Data Dependences*, because only data independent instructions can be issued in the same cycle. Moreover, data dependences impose a serialization on execution because processors have to stall the execution of one instruction until its source values have been produced by previous instructions. Data dependences are therefore some of the most important hurdles that limit the performance of current microprocessors.

The amount of *Instruction-Level Parallelism* (ILP) processors can exploit is significantly limited by the serialization caused by data dependences. This limitation is more severe for integer codes, where data dependences are more abundant. Some studies on the ILP limits of integer applications have shown that some of them cannot achieve more than a few tens of instructions per cycle (IPC) in an ideal processor with the sole limitation of data dependences [47],[89],[125]. This suggests that techniques for avoiding the serialization caused by data dependences are important for increasing ILP and will be crucial for future wide-issue microprocessors. In this thesis, we attempt to boost the execution of instructions to alleviate the serialization of data dependences.

In the last ten years, innovation and technological improvements in processor design have outpaced advances in memory design. For this reason, current high performance processors focus on cache memory organizations to ease the gap between processor and memory speed. The problem is that many of the techniques that are used to tolerate growing memory latencies lead to higher demand for memory bandwidth, large amounts of on-chip cache memory and increases in energy consumption. This has been shown to be a progressively greater limit to high performance [16],[17],[42],[103],[118]. In this thesis, we also attempt to improve the memory system by reducing the memory bandwidth, die area, access time and energy consumption of current data cache organizations.

To boost the execution of instructions and improve the memory system, we propose several microarchitectural techniques that can be applied to various parts of current microprocessor designs. The underlying aim behind all the proposed microarchitectural techniques is to exploit the repetitive behaviour in conventional programs.

### **1.2. Repetition in Conventional Programs**

Instructions executed by real-world programs tend to be repetitious, in the sense that most of the data consumed and produced by several dynamic instructions are often the same. Some studies [75],[106],[111] identified several tendencies that lead to repetition in many real programs, even with aggressive compilers.

Primarily, repetition is due to the input sets of real-world programs that contain data with little variation (consider, for example, sparse matrices that contain a majority of zeros). Compiler also generates repetition when it has to address error checking, program constants, branch destination computation, virtual function calls, glue code, memory alias resolution, call-subgraph identities and register spill code. Finally, the nature of some algorithms can also introduce repetitive computation. For example, convergent algorithms result in redundant computation in the convergent areas.

#### **1.2.1.** Computation and Value Repetition

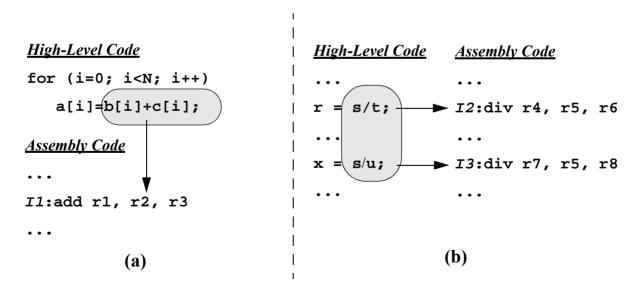

Computations performed by the instructions of a program can be summarized as follows: F[x, y]=z, where F represents the operation that is performed with x and y as source values and z represents the result of the computation. Repetition can be produced in many cases and involves operation, result and source values (individually or combined). In this thesis, we consider two types of repetition: (1) if the same combination of operation and source values have been produced exactly in the past, and (2) if source and/or result values have appeared earlier in the program. In the first case it is the left part of the

equation (F[x, y]) that is repetitive and in the second case it is any of all values that are repetitive (x, y, z).

We call *Value Repetition* to the repetition of any source or result value and *Computation Repetition* to the repetition of source values and operation.

#### 1.2.2. Analysis of Repetition

In this section we quantify the amount of repetition that is present in conventional programs.

The simulation environment is built on top of the Simplescalar [15] Alpha toolkit. The original simulator was modified to collect repetition statistics. To determine this repetition, source values, the opcode, and the destination value for all dynamic instructions are stored. Note that memory requirements are extremely high.

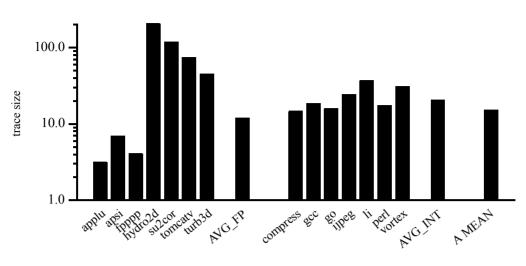

We randomly picked a subset of the SPEC2000 benchmark suite comprising both integer and FP codes: *bzip2, crafty, eon, gcc, gzip, parser, twolf, vortex* and *vpr* from the integer suite, and *ammp, applu, apsi, art, equake, mesa, mgrid, swim* and *wupwise* from the FP suite. These programs were compiled with the Compaq C compiler with -O5 -non\_shared optimization flags (i.e, maximum optimization). Each program was run with the reference input set and statistics were collected for 500 million instructions after skipping the initializations (see Section 1.4 for further details of tools and benchmarks).

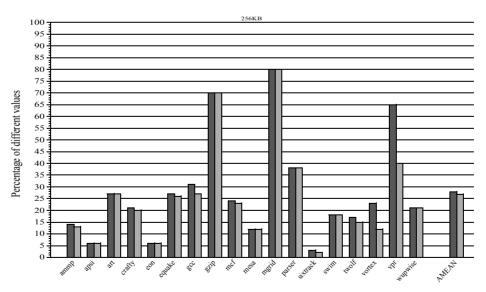

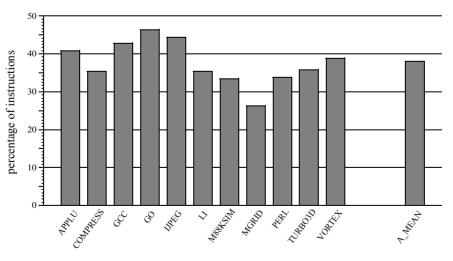

#### 1.2.2.1. Amount of Computation Repetition

We first analyse the computations performed by the instructions. As pointed out earlier, computation repetition is produced when the combination of operation and source values has been produced exactly in the past. We consider all the dynamic instructions to analyse the computation repetition.

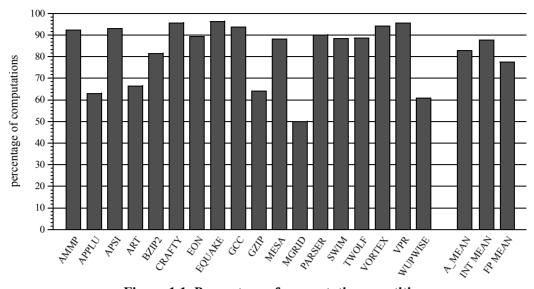

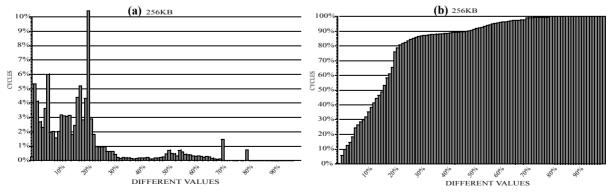

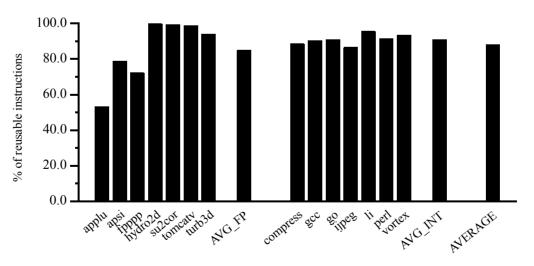

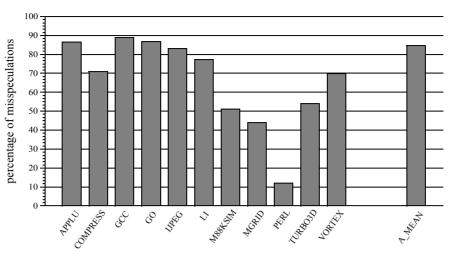

Figure 1.1 shows the percentage of repetitive computations. Note that the percentage of repetition is significant for all benchmarks and that, on average, more than 80% of the computations of a program have been done exactly in the past. Individual percentages range from 50% for *mgrid* to 96% for *equake*. Note also that this percentage is slightly lower for FP than for integer programs (77% and 87%, respectively).

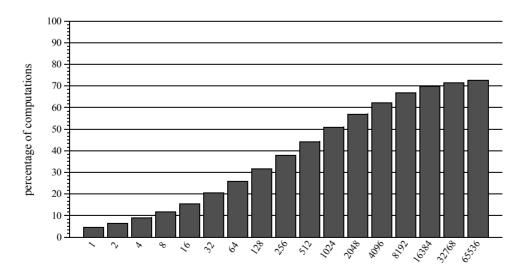

Figure 1.2 shows the contribution of the most frequent computations to the total percentage of computations in a program. We only show the average numbers of all the simulated benchmarks. Note

Figure 1.1. Percentage of computation repetition.

that the X-axis uses a logarithm range that moves from the most frequent computation on the left side to the 65,536 most frequent computations on the right side. The most important result of these simulations is that few computations contributes significantly to the total percentage of computations that programs perform. In other words, a program executes a small set of different computations a very large number of times. For instance, the 32 most frequent computations represent 20% of total computations, and we only need 1,024 different computations to obtain 50% of total computations. Intuitively, it seems that the combination of two source values and one operation will produce millions of possibilities (for

Figure 1.2. Contribution of the most frequent computations to the total computations.

instance, a 64-bit source value can contain billions of different values) but in reality with just with a few computations we can obtain most of the computations that a program performs.

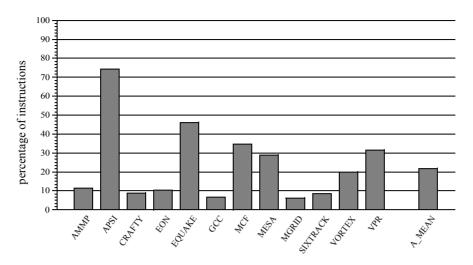

#### 1.2.2.2. Amount of Value Repetition

We now analyse the values produced by the instructions to give a flavour of the value repetition. As pointed out earlier, value repetition is produced when the values consumed/produced by one instruction have appeared earlier in the program. In this study, we only consider instructions that produce a result (in the case of store instructions, we consider the value stored in memory as a result value).

Note that computation repetition also produces value repetition of the result but value repetition does not necessarily mean computation repetition. In the first case, it is obvious that the same combination of operation and source values will always produce the same result, but in the second case the same result value can be produced by several computations. Therefore, the percentage of value repetition of the result will always be higher than the percentage of computation repetition.

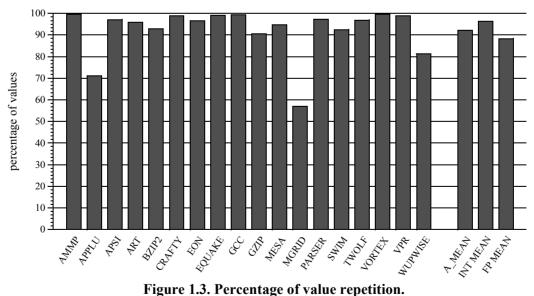

Figure 1.3 shows the percentage of repetitive values. As expected, the percentage of value repetition is better than the percentage of computation repetition and is also extremely high. Over 90% of the result values have been produced by an earlier instruction. Individual percentages range from 56% for mgrid to 99% for ammp, equake, gcc and vortex. Note also that this percentage is slightly lower for FP than for integer programs (87% and 96%, respectively).

Figure 1.3. Percentage of value repetition.

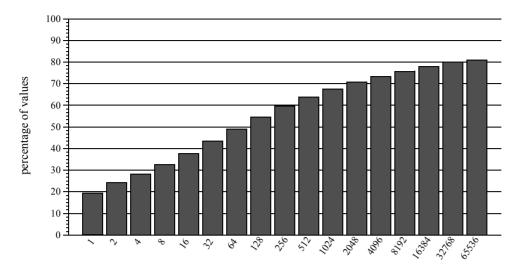

Figure 1.4. Contribution of the most frequent values to the total values.

Figure 1.4 shows the contribution of the most frequent values to the total percentage of values produced in a program. We only show the average numbers of all the simulated benchmarks. Note again that the X-axis uses a logarithm range that moves from the most frequent value on the left side to the 65,536 most frequent values on the right side. The values analysed have a 64-bit width, so billions of different values can be produced. Simulations results show that just a few values can greatly contribute to the total percentage of values produced in a program. For instance, just one value is produced by close to 20% of a program's instructions. It is easy to guess that this value is zero. Besides zero, note that we only need 1,024 different values to obtain close to 70% of the total values managed by programs.

## **1.3. Main Contributions**

We propose several microarchitectural techniques that can be applied to various parts of current microprocessor designs. These techniques attempt (1) to improve the memory system and (2) to boost the execution of instructions by exploiting the repetitive behaviour in conventional programs. In particular, the techniques proposed for improving the memory system are based on exploiting the value repetition produced by store instructions, while the techniques proposed for boosting the execution of instructions are based on exploiting the computation repetition produced by all the instructions.

#### 1.3.1. Contributions to Improve the Memory System

Modern processor designs manage large amounts of on-chip cache memories to deal with the gap between processor and memory speeds. This has special considerations in terms of memory traffic, die area, power dissipation and latency. To tackle these issues, we propose novel cache designs that benefit from the repetition in the memory hierarchy.

We therefore introduce the concept of *Redundant Store Instructions*. This type of stores do not modify memory since the value they write is equal to the existing value. In other words, they do not modify the state of the memory. In Chapter 2, we study the behaviour of these particular stores and show how they can be applied to a processor or multiprocessor system memory hierarchy in order to increase performance and decrease power consumption. This technique has no extra cost, in the sense that the added hardware and complexity are negligible. In particular, we show that we can achieve a significant saving on memory traffic between the first and second level cache by exploiting this feature. In this case, we exploit the value repetition of the effective address and the value that is stored in memory.

In Chapter 2, we also analyse the repetition of values into several storage locations of data caches. We conclude that data caches exhibit a high percentage of value replication at any given time. From this observation, we present a new data cache design called *Non-Redundant Cache* to reduce its die area, power dissipation and latency. Basically, the *Non-Redundant Cache* reduces the storage requirements of data cache by exploiting the significant amount of replication present in conventional cache designs. It also includes a simple compression scheme based on inlining narrow values. In this case, we simply exploit the value repetition of the value that is stored in memory.

Briefly, the main contributions are:

- A detailed study of value repetition in data caches.

- The concept and analysis of Redundant Store Instructions.

- A technique that exploits *Redundant Store Instructions* to reduce memory traffic between levels of memory hierarchy.

- A data cache design called *Non-Redundant Cache* that avoids the replication of values in data caches and reduces die area, power dissipation and access time.

Our work on this topic has been published in three papers. The concept of redundant store instructions and its application to reduce memory traffic was presented at the *International Conference on High Performance Computing and Networking* (HPCN 1999) [80]. The study of data cache repetition, the *Non Redundant Cache* and its analysis in terms of die area, latency and power was presented at the *International Symposium on Low Power Electronics and Design* (ISLPED 2003) [78]. Finally, a modification of the *Non-Redundant Cache* that applies extensive value compression was presented at the *International Conference on Parallel and Distributed Computing* (EUROPAR 2003) [4].

#### **1.3.2.** Contributions for Boosting the Execution of Instructions

Three techniques are applied for boosting the execution of instructions: *Instruction-Level Reuse*, *Trace-Level Reuse* and *Trace-Level Speculation*. All of these exploit the repetitive behaviour of computations present in conventional programs.

#### 1.3.2.1. Instruction-Level Reuse

Instruction-level reuse alleviates the serialization caused by data dependences. The idea is that the work done by some instructions can be non-speculatively reused when they perform the same work again. This reduces functional units utilization and, more importantly, reduces the time needed to compute the results, thus shortening the lengths of critical paths of the execution.

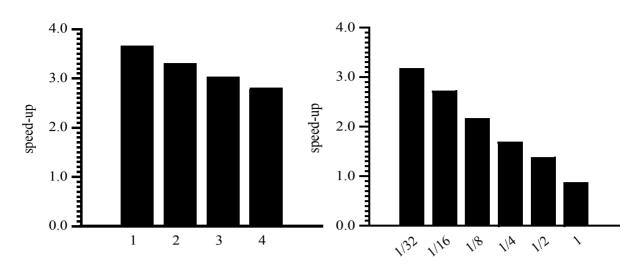

In Chapter 3, we analyse the phenomenon of instruction-level reuse by evaluating its performance potential for an infinite resource machine and for a machine with a limited instruction window. The aim is to study the performance limits of instruction-level reuse while ignoring implementation aspects. We

will show that instruction-level reuse can exploit a high degree of reuse and may provide very large speed-ups for an ideal machine. However, performance is degraded when the reuse latency is considered.

In this chapter, we also present a hardware implementation for dynamic instruction-level reuse in superscalar microprocessors. The underlying concept exploited by this mechanism is the run-time removal of redundant computations and particularly the elimination of *quasi-invariants* and *quasi-common subexpressions*. In the first case, a quasi-invariant is defined as a computation that is repeated many times and often produces the same result. In the second case, a quasi-common subexpression is defined as a computation that often produces the same result as another piece of code. Removing redundant computation is a target of optimizing compilers. Because of their limited knowledge of the data, however, they do not always succeed. The proposed mechanism can also remove quasi-redundant computations, such as subexpressions that often produce the same result but sometimes differ (depending on the data values) and cannot therefore be eliminated by the compiler.

Briefly, the main contributions are:

- A detailed study that evaluates the performance potential of instruction-level reuse.

- A mechanism called *Redundant Computation Buffer* that can exploit reuse due to quasi-invariants and quasi-common subexpressions while exhibiting a low reuse latency. Its novel features, such as memory management, can be applied to previous hardware implementations of instruction-level reuse.

Our proposals on this topic were published at the *International Conference on Supercomputing* (ICS 1999) [77] and in a technical report [37] evaluating the performance potential of instruction-level reuse.

#### 1.3.2.2. Trace-Level Reuse

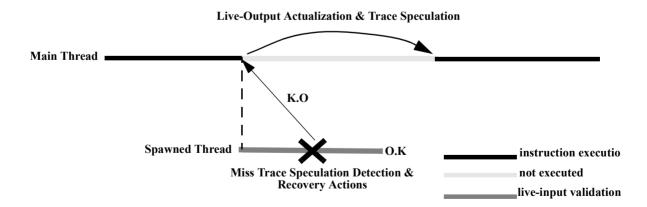

Here we introduce and study the concept of trace-level reuse. Trace-level reuse exploits the fact that many sequences of instructions are repeatedly executed (most of these repetitions have the same inputs and thus generate the same results) by buffering previous inputs and their corresponding outputs. When a trace is encountered again and its current inputs are found in that buffer, its execution can be avoided by obtaining the outputs from the buffer.

24

Exploiting reuse at trace level implies that a single reuse operation can skip the execution of a potentially large number of instructions. More importantly, as these instructions do not need to be fetched, they do not consume fetch bandwidth. Moreover, since these instructions are not placed in the reorder buffer, they do not occupy any slot of the instruction window, so the effective instruction window size is increased as a side effect. Particularly interesting is the fact that this technique may compute all at once the results of a chain of dependent instructions (e.g. in a single cycle), which allows the processor to exceed the dataflow limit that is inherent in the program.

In Chapter 4 we analyse the performance potential of trace-level reuse under several scenarios. We also compare the relative advantages of trace-level reuse and instruction-level reuse and show that trace-level reuse is more effective than instruction-level because it reduces fetch bandwidth and instruction window requirements. Trace-level reuse also has a lower overhead because a single reuse operation can avoid the execution of a long sequence of instructions. Finally, we address essential issues for integrating a trace-level reuse scheme into a superscalar processor.

Briefly, the main contributions are:

- The concept of trace-level reuse.

- A detailed analysis of the performance potential of trace-level reuse under several scenarios.

- A discussion of the design issues for integrating a trace-level reuse scheme on a superscalar processor.

Our proposals on this topic were published at the *International Conference on Parallel Processing* (ICPP 1999) [38] and in a technical report [37] evaluating the performance potential of trace-level reuse.

#### 1.3.2.3. Trace-Level Speculation

Trace-level speculation avoids the execution of a dynamic sequence of instructions by predicting the set of live-output values based on previously seen results. This prediction exploits the observation that a limited set of unique values constitutes the majority of values produced and consumed by conventional programs. Trace-level speculation solves the reuse test of trace-level reuse, that it is not easy to handle, but it introduces penalties due to a misspeculation. There are two important issues in trace-level speculation. The first of these involves the microarchitecture support for trace speculation and how the microarchitecture manages trace speculation. The second involves trace selection and data value speculation techniques.

In Chapter 5 we present a novel microarchitecture for exploiting trace-level speculation using two threads working cooperatively. One thread, called the speculative thread, executes instructions ahead of the other by speculating on the result of several traces. The other thread executes speculated traces and verifies the speculation made by the first thread. This architecture has two main advantages: (a) no significant penalties are introduced in the presence of a misspeculation and (b) any type of trace predictor can work with this proposal.

We also propose a static program analysis for identifying candidate traces to be speculated. This approach identifies large regions of code whose produced values may be successfully predicted. We present several heuristics to determine the best opportunities for dynamic speculation based on compiler analysis and program profiling information.

Briefly, the main contributions are:

- A microarchitecture to exploit trace-level speculation called *Trace-Level Speculative Multithreaded Architecture*. This architecture does not introduce significant trace misprediction penalties and does not impose any constraint on the approach to building or predicting traces.

- A trace selection method to identify large regions of code that may be successfully predicted based on a static analysis that uses profiling data.

Three papers have been published on this topic: the definition of the architecture was presented at the *International Conference on Computer Design* (ICCD 2002) [81]; a hardware improvement that reduces misspeculation penalties was presented at the *6th International Symposium on High Performance Computing* (ISHPC 2005) [79]; and compiler analysis to support *Trace-Level Speculative Multithreaded Architectures* was presented at the *9th Annual Workshop on Interaction between Compilers and Computer Architectures* (INTERACT 2005) [76].

## **1.4. Methodology and Experimental Framework**

The microarchitectural techniques introduced in this thesis have been analysed, proposed and evaluated using a similar methodology. For each technique, we first analyse a set of benchmarks to quantify a special repetitive behaviour of the instructions. Basically, this analysis is performed with the help of tools that easily provide information about the instructions executed in a program. Then, we analyse the results to define proposals that are targeted to improve the memory system or boost the execution of instructions. Once the proposals are defined, we evaluate them. To do so, we modify a set of simulators widely used in the computer architecture research community. These simulators can provide information about computer performance in terms of speed-up or cache hit/miss ratio. Finally, we also use a well-known analytical model, that greatly facilitates the work of circuit simulation, for the evaluation of area, power and cycle time of data caches.

In the following subsections we provide an overview of tools, benchmarks and baseline microarchitecture that are used to propose and evaluate the microarchitectural techniques introduced in this thesis. We detail the specific experimental framework of the techniques in their corresponding chapters.

#### 1.4.1. Tools

**ATOM** [117]: *Analysis Tools with Object Modification* (ATOM) is a single framework for building a wide range of high performance program analysis tools. It provides instrumentation routines that allow the user to have access to each procedure in an application, each basic block in that procedure, and each instruction in that basic block. In addition to the instrumentation routines, the user can also write analysis routines. The main advantage of this tool is that provides a very flexible and efficient code instrumentation interface that helps to build customized simulators with very little effort. The main disadvantage is that ATOM is a trace-driven simulator. This means that the analysis reads existing executed traces of instructions to simulate models. Thus, ATOM can not model accurately speculation or misprediction. In this thesis, we use the ATOM tool to analyse and quantify a special repetitive behaviour of programs.

**SimpleScalar Tool Set [15]:** Besides trace-driven simulation, execution-driven simulation is a useful technique for modelling high-performance of modern microprocessors. This technique, which is the most accurate and most costly of the simulation techniques, requires instruction and I/O emulators to

reproduce program computation. This means that it decodes and executes machine instructions on-thefly. The *SimpleScalar Tool Set* provide simulators ranging from a fast functional simulator to a detailed out-of-order issue processor that supports non-blocking caches, speculative execution, and state-of-theart branch prediction. In this thesis, we use the simulators of the Simplescalar tool set in several ways. The *sim-fast* simulator is modified to provide results of the repetitive behaviour of programs; the *simoutorder* simulator is modified to evaluate some techniques in an out-of-order superscalar processor with a two level memory system and speculative execution support; and finally, the *sim-cache* simulator is modified to evaluate the memory hierarchy techniques when the cache performance on execution time is not considered.

**CACTI** [107]: This tool greatly facilitates the work of circuit simulation. It was originally developed to quantify the access time trade-offs of on-chip cache organizations. Later versions of the CACTI tool provide features to estimate area, access and cycle time and power dissipation of different direct-mapped and set-associative cache configurations. Moreover, this tool is also used to determine the cache configuration that best satisfies a desired optimization criterion. In this thesis, we use the CACTI tool as an analytical model for the evaluation of area, power and cycle time of on-chip direct-mapped and set-associative caches.

#### 1.4.2. SPEC Benchmarks

The Standard Performance Evaluation Corporation (SPEC) [54] is an organization founded in 1988 dedicated to producing benchmarks that are reasonably scientific, unbiased, meaningful and relevant. This organization provides several families of benchmarks to measure the performance of different computer systems (CPU family), parallel and distributed computer architectures (HPC family), java application servers (JAPPSERVER family), mail servers (MAIL family), network file servers (SFS family) and web servers (WEB family).

In this thesis we consider the CPU family, designed to provide performance measurements that can be used to compare compute-intensive workloads on different computer systems. In particular, we consider the following suites of the CPU family: SPEC CPU95 (released in August 1995) and Spec CPU2000 (released in January 2000). Each suite defines a standard reference machine and a set of programs to run, and formulas for computing the scores. Traditionally, the SPEC benchmarks define three standard runs called reference, test and train. Moreover, each suite contains two benchmark components: CINT for measuring and comparing compute-intensive integer performance, and CFP for

| SPEC (       | CPU 95      | SPEC CPU 2000 |              |  |

|--------------|-------------|---------------|--------------|--|

| CINT95       | CFP95       | CINT2000      | CFP2000      |  |

| 099.go       | 101.tomcatv | 164.gzip      | 168.wupwise  |  |

| 124.m88ksim  | 102.swim    | 175.vpr       | 171.swim     |  |

| 126.gcc      | 103.su2cor  | 176.gcc       | 172.mgrid    |  |

| 129.compress | 104.hydro2d | 181.mcf       | 173.applu    |  |

| 130.li       | 107.mgrid   | 186.crafty    | 177.mesa     |  |

| 132.ijpeg    | 110.applu   | 197.parser    | 178.galgel   |  |

| 134.perl     | 125.turb3d  | 252.eon       | 179.art      |  |

| 147.vortex   | 141.apsi    | 253.perlbmk   | 183.equake   |  |

|              | 145.fpppp   | 254.gap       | 187.facerec  |  |

|              | 146.wave5   |               | 188.ammp     |  |

|              |             | 256.bzip2     | 189.lucas    |  |

|              |             | 300.twolf     | 191.fma3d    |  |

|              |             |               | 200.sixtrack |  |

|              |             |               | 301.apsi     |  |

Table 1.1. SPEC CPU95 and CPU2000 benchmarks.

measuring and comparing compute-intensive floating point performance. Table 1.1 shows the SPEC CPU95 and SPEC CPU2000 benchmarks Note that several SPEC CPU95 programs have been included with minor changes in SPEC CPU2000 (i.e. compress, gcc, perl and vortex form the integer component and applu, apsi, mgrid and swim from the floating point component).

We began to use the SPEC CPU95 test platform but then shifted to the SPEC CPU2000. Note that the organization of this thesis does not preserve the temporal order in which we proposed the techniques. Therefore, SPEC CPU95 and SPEC CPU2000 simulations are merged throughout the chapters.

Although SPEC CPU95 still provide a meaningful point of comparison (half of SPEC CPU95 are included in SPEC CPU2000), we believe that it is important to consider the changes in technology. SPEC CPU2000 are designed to measure compute intensive performance that reflects the current advances in microprocessor technologies. However, Yi and Lilja [135] analysed repetitive behaviour in both SPEC CPU95 and SPEC CPU2000 benchmarks and did not find significant differences.

We have compiled the programs with the DEC C and Fortran compilers with full optimizations ("non\_shared -O5 -tune ev5 -migrate -ifo" for C codes and "-non\_shared -O5 -tune ev5" for Fortran codes). In our simulations we consider the reference and test inputs of SPEC benchmarks. Furthermore, we forward a significant number of instructions to avoid the initialization behaviour of programs. We have empirically checked that skipping 500 million instructions with the reference input and 125 million instructions with the test input represent a good design point.

## 1.4.3. Baseline Microarchitecture

We use the *sim-outorder* simulator of the *SimpleScalar* tool set to determine the speed-up of a particular technique in an out-of-order superscalar processor with a two level memory system and speculative execution support. The baseline microarchitecture that we assume in this simulator is a 4-way dynamically scheduled superscalar processor based on the Register Update Unit [114]. The main characteristics of this architecture are shown in Table 1.2.

| Instruction fetch            | 4 instructions per cycle.                                                                                                                                                          |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                              |                                                                                                                                                                                    |  |  |

| Branch predictor             | 2048-entry bimodal predictor                                                                                                                                                       |  |  |

| Instruction issue/<br>commit | Out-of-order issue, 4 instructions committed per cycle, 64-entry reorder buffer,<br>loads execute only after all the preceding store addresses are known, store-load<br>forwarding |  |  |

| Architectural registers      | 32 integer and 32 FP                                                                                                                                                               |  |  |

| Functional units             | 4 integer ALUs, 4 load/store units, 4 FP adders, 2 integer mult/div, 2 FP mult                                                                                                     |  |  |

| FU latency/repeat rate       | int ALU 1/1, load/store 1/1, int mult 3/1, int div 20/19, FP adder 2/1, FP mult 4/1,<br>FP div 12/12                                                                               |  |  |

| Instruction cache            | 16 KB, direct-mapped, 32-byte block, 6-cycle miss latency                                                                                                                          |  |  |

| Data cache                   | 16 KB, 2-way set-associative, 32-byte block, 6-cycle miss latency                                                                                                                  |  |  |

| Second Level<br>Cache        | Shared instruction & data cache, 256 KB, 4-way set-associative, 32-byte block, 100-cycle miss latency                                                                              |  |  |

Table 1.2. Parameters of the baseline microarchitecture.

"Do not keep in your head what you can fit in your pocket" Albert Einstein, US (German-born) physicist, 1879-1955.

# Chapter 2

# VALUE REPETITION IN DATA CACHES

On-chip cache memories are getting bigger and bigger in order to ease the ever-increasing gap between processor speed and memory access. Die area, latency and power dissipation have therefore become a key constraint in the design of current cache organizations. Memory bandwidth is also a scarce resource in high-performance systems because modern processor techniques designed to deal with memory latencies lead to greater bandwidth demands.

In this chapter we propose novel data cache designs that reduce memory traffic and produce significant die area savings, power reduction and latency decrease. These novel schemes are based on the observation that most values managed by the memory hierarchy are frequently repetitive.

## 2.1. Introduction

In the last decade, innovation and technological improvements in processor design have outpaced those in memory design. That is why current high performance processors focus on cache memory organizations [128] to ease the gap between processor and memory speed. Several studies [42],[109] have shown the importance of a good design to maximise the hit ratio, minimise the access time to cache, minimise the delay due to a miss and minimise the overheads of updating the next memory level.

One problem is that many of these techniques for tolerating growing memory latencies do so at the expense of increased memory bandwidth, and this has been shown to be a progressively greater limit to high performance [16],[17],[42]. Techniques such as lookup free caches [115], software and hardware prefetching [21], stream buffers [58], speculative load execution [39], and multithreading [122] reduce latency related stalls but also increase the total traffic between the main memory and the processor. Memory bandwidth has therefore also become a key constraint in the design of current cache organizations.

Processor and memory integration can build cheaper and less complex competitive systems [103]. On-chip cache memories of microprocessor are getting larger because the scale of integration continues to grow and because applications are using larger working sets. Chip multiprocessor designs are also a promising way of increasing throughput. However on-chip memories and processing cores both compete for the die area, and the area occupied by one affects the amount left for the other [52]. Table 2.1 summarizes cache occupancy for several commercial processors [53]. For instance, in a Power4 processor, the die contains 2 processors and a unified 1.5MB second level cache that occupies close to 50% of the total die area. Even small processors such as Mips-R20k devote a significant area to implementing caches. On average, caches use close to 50% of the total die area. Moreover, some

|             | L1 Dcache | L1 Icache | L2 Cache | Total Area |

|-------------|-----------|-----------|----------|------------|

| Pentium 4   | 2%        | 3%        | 20%      | 25%        |

| MipsR20k    | 23%       | 26%       | none     | 54%        |

| Crusoe:5400 | 10%       | 9%        | 27%      | 46%        |

| Power4      | 2%        | 1%        | 50%      | 53%        |

| Alpha 21364 | 4%        | 3%        | 36%      | 43%        |

Table 2.1. Die are occupied by caches in some commercial processors.

authors [14],[43] have reported that caches may be responsible for 10% to 20% of the total power dissipated by a processor.

In processor design several trade-offs are needed to obtain a good balance between cost and performance. For high productions volumes, cost can be associated with area chip, so a way to reduce the cost is to reduce area requirements. On the other hand, power dissipation is becoming a critical issue for microprocessors. Power dissipation determines the cost of the cooling system and ultimately may limit the performance of the microprocessor. Dynamic power dissipation of on-chip memories is strongly related to its area, whereas static power dissipation depends on the number of transistors.

In the previous chapter we demonstrated the high percentage of repetition produced by instructions in conventional programs. Therefore, store instructions manage values that are frequently repetitive. Those repetitive values may be stored in the same storage location or in several storage locations of the memory hierarchy. The first case means that the effective address and the value stored in memory are repetitive. The second case means that just the value stored in memory is repetitive. We will show that both repetitive behaviours can be exploited to improve several aspects of conventional data caches.

In this chapter, value repetition in the same storage location is exploited by a novel technique for reducing memory traffic with no special hardware requirement. In particular, we show that a significant saving on memory traffic between the first and the second level cache can be avoided with no extra cost, since the added hardware and complexity are negligible. This technique is based on the observation that some memory writes do not modify memory because the value they write is equal to the existing value. In other words, they do not modify the state of the memory. We refer to these stores which exploit this value repetition as *Redundant Stores*. We study how they behave and show how they can be applied to a processor or multiprocessor system memory hierarchy in order to increase performance and decrease power consumption.

We also present in this chapter a novel cache design, the *Non-Redundant Cache*, which reduces the storage requirements of data cache by exploiting the significant amount of replication in conventional data cache designs. These storage savings lead to significant die area savings, power reduction and latency decrease. The underlying concept behind this approach is the exploitation of value repetition in several storage locations of data caches.

The rest of this chapter is organized as follows. Section 2.2 analyses the value repetition in the same storage location of data caches and introduces the concept of *Redundant Store Instructions*.

Section 2.3 proposes a technique based on *Redundant Store Instructions* that reduces memory traffic between levels of the memory hierarchy. Section 2.4 evaluates the value repetition in several storage locations of conventional data caches. Section 2.5 introduces a novel cache design called *Non-Redundant Cache* which avoids the replication of values and reduces die area, power dissipation and access time. Finally, Section 2.6 reviews related work and Section 2.7 summarizes our main conclusions.

### 2.2. Value Repetition in the Same Storage Location

#### 2.2.1. Overview

Lipasti *et al* [72] coined the term *value locality* to describe the likelihood to references of a previously seen value within a storage location. These authors reported that the most recent value produced by an instruction is frequently also the next. Based on this observation, they initially proposed last value prediction as a mechanism for predicting load values [72] and, in a subsequent study, for predicting all values produced by instructions that write into a register [71]. Unfortunately, store instructions were not analysed, since the target was to boost the execution of instructions.

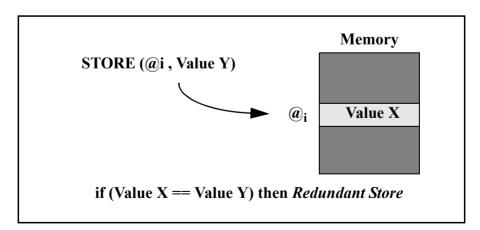

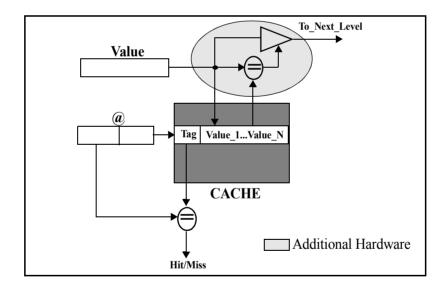

We observed that several memory writes do not modify memory since the value they write is equal to the existing value. In other words, they do not modify the state of memory. These stores are what we call *Redundant Stores*. Figure 2.1 summarizes the underlying concept behind *Redundant Stores* and the next section quantifies them by analysing a set of benchmarks. Note again that a *Redundant Store* is produced when the stored value is the same as the previous one.

Figure 2.1. Redundant store concept.

Since our initial definition [80], several authors [10], [60], [65], [66], [67] have evaluated this particular behaviour for several stores. All these authors called them *Silent Stores* but the underlying concept is the same as in our definition of Redundant Stores.

*Redundant Stores* can be applied to any part of the processor which has a buffer that is modified such as cache memories, write buffers, load/store queues for memory disambiguation, buffers of instruction reuse or prediction schemes, etc. We will show the behaviour of redundant stores in the memory hierarchy. Rather than boosting the execution of instructions, the proposal reduces the memory bandwidth demand. By exploiting the redundancy of some stores we can achieve a significant saving on memory traffic between the different levels of the hierarchy, thus increasing the performance. We also achieve a reduction in power consumption because the memory bus is used less.

In the following subsections, we first revise different cache write policies and then quantify the amount of *Redundant Stores* in several data cache configurations.

#### 2.2.2. Cache Write Policies

Cache memories are largely known as small amount storage of high speed access designed to supply the processor with the most frequently requested instructions and data. When data is read from, or written to, main memory, a copy is also saved in the cache, along with the associated main memory address. The cache monitors addresses of subsequent reads to see if the required data is already in the cache. If the data is cached (i.e. a cache hit), it is returned immediately and the main memory read is not started. If the data is not cached (i.e. a cache miss), it is fetched from the main memory and saved in the cache.

Basically, there are two options when writing to cache [47], [57]:

- *Write Through*, where the information is written both to the block in the cache and to the block in the lower level memory.

- *Copy Back,* where the information is written only to the block in the cache and the modified cache block is written to the next memory level only when it is replaced. This technique uses a dirty bit that indicates whether the block was written, thus reducing the frequency of writing back blocks on replacement.

Similarly, there are two options on a write miss[47],[57]:

- Write Allocate, where the new block is loaded into the cache.

- *No Write Allocate,* where the new block is *not* loaded in the cache and is modified in the next level of the memory hierarchy.

The combination of the above options leads to four main configurations in cache: *Write Through with Write Allocate (WT-WA), Write Through with No Write Allocate (WT-NWA), Copy Back with Write Allocate (CB-WA),* and finally *Copy Back with No Write Allocate (CB-NWA).* Normally Copy Back with Write Allocate, and Write Through with No Write Allocate are used because, in the first case, subsequent writes to the same block can be captured by the cache and, in the second case, subsequent writes to the same block still have to go to memory.

#### 2.2.3. Performance Evaluation

This section evaluates the amount of redundant store instructions in several data cache configurations.

#### 2.2.3.1. Experimental Framework

We have developed a functional parameterized simulator for cache memories. Briefly, this simulator provides information about hit/miss ratios and quantifies the number of writes that does not modify the state of memory.

For the evaluation we have considered a subset of the Spec95 benchmark suite. The programs have been compiled with the DEC Fortran and C compilers for a DEC AlphaStation 600 5/266 with full optimizations, and instrumented by means of the Atom tool [117]. Each program was run with the reference input sets, and statistics were collected for 1 billion instructions after skipping the initial part, which corresponds to initializations (see Section 1.4 for further details of tools and benchmarks).

We simulated several cache configurations and cache write policies. We considered four cache sizes: 32 KB, 16 KB, 8 KB and 4 KB, and 32-byte line size. We simulated the following cache policies: *Copy Back with Write Allocate (*CB-WA for short*)* and *Write Through with No Write Allocate* (WT-NWA for short). Direct mapped caches were assumed for all simulations. Table 2.2 shows the miss ratio of every combination of the above described sizes and policies.

|         | COPY BAC           | K WRITE AI         | WRITE THROUGH NO WRITE ALLOCATE |                    |                    |                    |                    |                    |  |

|---------|--------------------|--------------------|---------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|

|         | 32 KB              | 16 KB              | 8 KB                            | 4 KB               | 32 KB              | 16 KB              | 8 KB               | 4 KB               |  |

| Applu   | 10.81<br>8.31 16.5 | 11.29<br>8.88 16.8 | 12.15<br>9.86 17.4              | 14.01<br>12.0 18.5 | 16.40<br>8.09 35.4 | 16.84<br>8.51 35.9 | 17.65<br>9.27 36.8 | 19.48<br>11.0 38.7 |  |

| Apsi    | 12.61<br>14.0 9.95 | 13.12<br>14.5 10.4 | 15.03<br>16.6 11.9              | 29.59<br>28.3 31.9 | 14.99<br>13.9 16.9 | 15.71<br>14.3 18.2 | 18.95<br>16.9 22.8 | 35.26<br>26.4 51.9 |  |

| Gcc     | 2.40<br>2.85 1.01  | 5.13<br>5.89 3.64  | 7.81<br>8.96 5.53               | 11.61<br>13.5 7.88 | 2.85<br>2.98 2.41  | 6.57<br>7.01 5.08  | 11.58<br>12.3 8.83 | 18.90<br>20.4 13.5 |  |

| Go      | 3.52<br>3.96 2.65  | 5.73<br>6.74 2.28  | 10.26<br>11.9 4.54              | 17.13<br>19.8 7.72 | 7.71<br>4.23 14.6  | 9.67<br>6.26 16.4  | 12.90<br>9.59 19.4 | 17.87<br>14.5 24.4 |  |

| Ijpeg   | 1.58<br>2.10 0.06  | 2.69<br>3.46 0.43  | 7.32<br>9.64 0.54               | 15.34<br>20.3 0.67 | 1.63<br>2.11 0.22  | 3.16<br>3.57 1.96  | 7.87<br>9.77 2.32  | 15.98<br>20.5 2.72 |  |

| M88ksim | 0.67<br>1.05 0.01  | 1.30<br>1.95 0.18  | 5.52<br>6.85 3.21               | 7.68<br>9.30 4.86  | 1.22<br>1.05 1.51  | 1.82<br>1.05 1.60  | 7.11<br>7.32 6.74  | 11.49<br>10.7 12.8 |  |

| Mgrid   | 4.97<br>4.51 13.8  | 5.21<br>4.76 13.8  | 5.35<br>4.90 13.9               | 8.46<br>8.17 14.0  | 6.89<br>4.55 51.4  | 7.12<br>4.80 51.4  | 7.25<br>4.93 51.5  | 10.35<br>8.19 51.5 |  |

| Perl    | 0.27<br>0.22 0.37  | 0.55<br>0.43 0.75  | 1.64<br>1.93 1.13               | 7.35<br>8.25 5.78  | 1.80<br>0.43 4.19  | 3.37<br>0.86 7.75  | 4.91<br>2.58 8.99  | 12.86<br>10.7 16.6 |  |

| Tomcatv | 12.06<br>14.5 5.64 | 15.98<br>18.8 8.44 | 29.13<br>31.9 21.8              | 36.26<br>39.8 27.0 | 16.07<br>14.2 20.9 | 18.76<br>17.7 21.4 | 30.87<br>31.9 28.1 | 38.87<br>40.3 35.0 |  |

| Turb3d  | 5.82<br>5.55 6.18  | 7.59<br>7.40 7.84  | 8.92<br>8.73 9.17               | 10.60<br>10.6 10.5 | 5.79<br>5.73 5.87  | 7.93<br>7.59 8.37  | 10.62<br>9.17 12.5 | 13.52<br>11.3 16.4 |  |

| Vortex  | 1.88<br>2.57 0.87  | 3.45<br>4.51 1.87  | 5.40<br>7.09 2.88               | 8.04<br>10.3 4.58  | 2.96<br>2.79 3.22  | 5.83<br>5.31 6.59  | 9.09<br>8.04 10.6  | 14.22<br>11.6 18.0 |  |

| Wave    | 15.33<br>13.3 18.8 | 25.85<br>23.2 30.5 | 36.02<br>32.0 43.3              | 41.97<br>40.0 45.5 | 21.36<br>11.1 40.0 | 31.93<br>20.5 52.7 | 40.90<br>31.5 57.8 | 47.93<br>40.0 62.3 |  |

| A_MEAN  | 5.99<br>6.09 6.33  | 8.16<br>8.39 8.09  | 12.05<br>12.5 11.2              | 17.34<br>18.3 14.9 | 8.31<br>5.93 16.4  | 10.73<br>8.20 18.9 | 14.98<br>12.7 22.2 | 21.39<br>18.8 28.6 |  |

Table 2.2: Miss ratios of CB-WA and WT-NWA for different cache sizes

Cell Description

Total Miss Ratio

Load\_Miss\_Ratio Store\_Miss\_Ratio

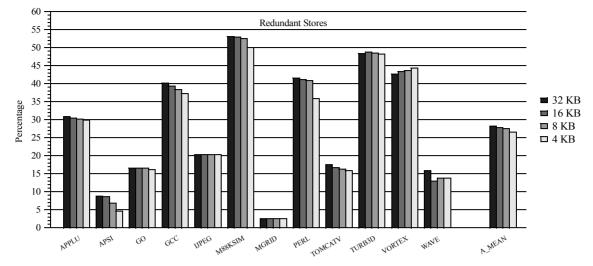

Figure 2.2. Percentage of redundant stores for CB-WA with different cache sizes.

#### 2.2.3.2. Analysis of Results

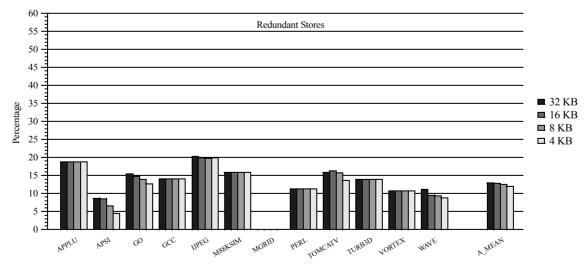

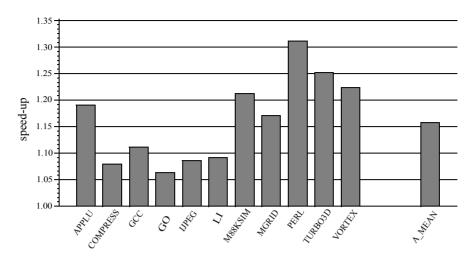

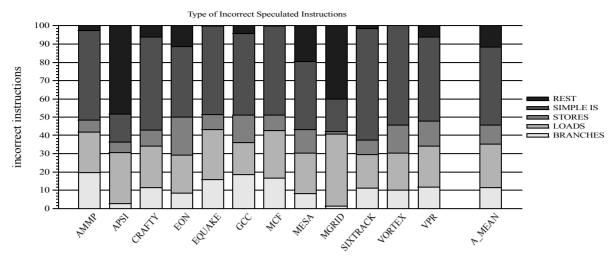

Figure 2.2 and Figure 2.3 show the percentage of *Redundant Stores* over all the stores that access the simulated caches. Specifically, Figure 2.2 shows the percentage of *Redundant Stores* for CB-WA caches and Figure 2.3 shows the percentage for WT-NWA caches.

Note that the amount of *Redundant Stores* in cache was significant in all benchmarks. Only *mgrid* did not present a significant number of *Redundant Stores*. On average, around 30% of the stores were redundant for a CB-WA cache and 15% were redundant for a WT-NWA cache. This difference is due to

Figure 2.3. Percentage of redundant stores for WT-NWA with different cache sizes.

the fact that CB-WA has a lower store miss ratio than WT-NWA (on average, about half), so storage locations refer longer to the same memory address. The results also show that the size of the caches did not modify the percentage of *Redundant Stores*.

Using this observation, in the next section we propose a novel technique that can significantly reduce the memory bandwidth required between levels of the memory hierarchy.

# 2.3. Redundant Store Mechanism for Reducing Memory Traffic

In this section, we propose to benefit from redundant store instructions by slightly modifying conventional data cache designs in order to achieve significant traffic reduction between levels of the memory hierarchy.

#### 2.3.1. General Description

We first describe the changes required in different cache configurations in order to take advantage of the *Redundant Stores* for memory traffic reduction. Note that the additional hardware required is minimal and is highlighted in each scheme.

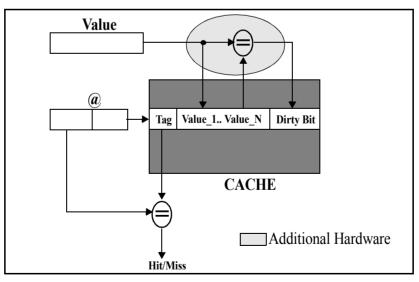

• Cache memory with copy-back policy: In the regular version, a store accesses cache to write its value and sets the dirty bit. We propose first checking whether the current value in cache matches the value that this store is going to write. If so, it is a *Redundant Store* and the dirty bit is not set.

Figure 2.4. Redundant store mechanism with copy back

A store in a conventional cache first reads the tag and then writes the new value. Our mechanism simultaneously reads the old value and the tag and then writes the new value if necessary, so the cache latency is not increased. For the sake of simplicity, direct mapped caches are assumed. Note that associative caches will only need to replicate the additional hardware for each way. Figure 2.4 shows how the mechanism works for copy back caches. Here we have a reduction in the frequency at which the dirty bit is set. This reduces memory traffic because fewer blocks of the cache will have to go to the next level of the memory hierarchy when there is a cache miss. Note that, to exploit the benefit of *Redundant Stores*, we have to read the old value from the cache and compare it with the value that is going to be written. We just need a simple comparator that decides whether the dirty bit is set.

• Cache memory with write-through policy: In this case, *Redundant Stores* do not need to update either the cache or the next memory level. As explained earlier, it is identified by reading the old value and comparing it with the current one (see Figure 2.5). Note that the output of the comparator decides whether the buffer can send the value to the next level of the hierarchy.

Figure 2.5. Redundant store mechanism with write through

#### 2.3.2. Performance Evaluation

In this section we evaluate the reduction of memory traffic in different cache configurations.

#### 2.3.2.1. Experimental Framework

We have developed a functional parameterized simulator for cache memories, as described in Section 2.2.3.1. This simulator is now modified to provide information about required memory bandwidth. We consider the same subset of the Spec95 benchmark suite and evaluated the same cache sizes and cache write policies (see Section 2.2.3.1 for further details of the specific experimental framework and Section 1.4 for further details of tools and benchmarks).

#### 2.3.2.2. Analysis of Results

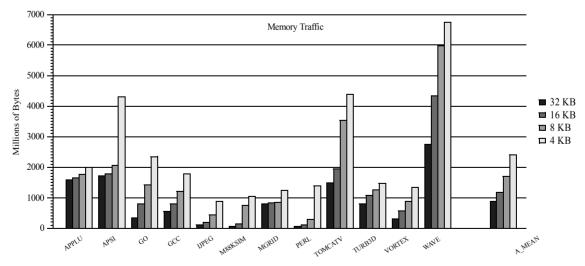

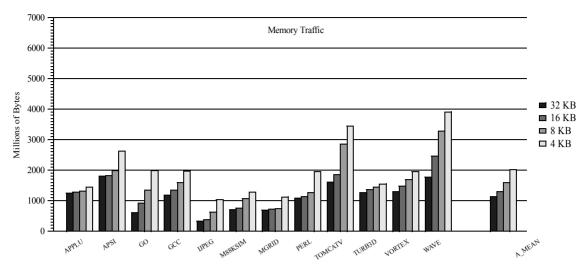

Memory traffic between the memory cache and its next level of the memory hierarchy is now analysed. The traffic is computed as the number of bytes transmitted between levels.

Figure 2.6 and Figure 2.7 show the memory traffic for each policy and for several cache sizes. As expected, the memory traffic decreased when we used bigger cache sizes because the miss ratio decreased. Note that memory traffic has two main sources: the hit/miss ratio and the size of the cache block. Intuitively, CB-WA caches should have less memory traffic than WT-NWA caches because they have a better hit ratio (see Table 2.2). Our results show that, on average, CB-WA and WT-NWA caches

Figure 2.6. Memory traffic (millions of bytes) for CB-WA with different cache sizes

Figure 2.7. Memory traffic (millions of bytes) for WT-NWA with different cache sizes

have similar amount of memory traffic. This is because CB-WA caches have to transmit the whole cache block on a miss if the replaced block is dirty, while WT-NWA only has to transmit a single value for each write.

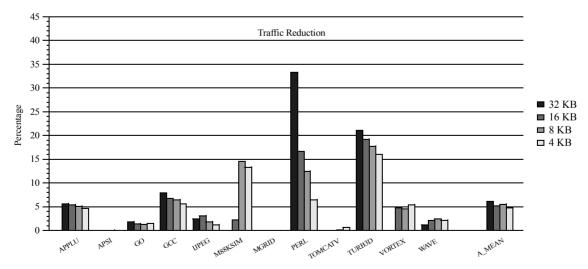

Figure 2.8 and Figure 2.9 show the percentage reduction in memory traffic after the redundant store mechanism is applied. Figure 2.8 shows the results for CB-WA caches and Figure 2.9 shows the results for WT-NWA caches. Note that both are significant, though WT-NWA caches provide higher percentage reductions than CB-WA caches.

Figure 2.8. Reduction of memory traffic of CB-WA with different cache sizes

Figure 2.9. Reduction of memory traffic of WT-NWA with different cache sizes

PERL

TOMCATY

TURB3D

VORTEX

WAVE

MGRID

M88KSIM

UPEG

GCC

60

For example, there is a 7% memory traffic reduction for a 32KB CB-WA cache and 19% traffic reduction for a 32KB WT-NWA. This difference is mainly due to the fact that all the stores have to go to the next level of the memory hierarchy for Write Through, so every Redundant Store leads to a saving on memory traffic. On the other hand, when Copy Back is used, every Redundant Store reduces the frequency of the dirty bit setting, which does not always lead to a traffic reduction. For instance, two consecutive Redundant Stores mapped to the same cache line just reduce the traffic in one block. The same argument explains why the size of the caches affects the percentage reduction of the WT-NWA caches (this increases when the caches get bigger) and does not affect the percentage reduction of the CB-WA caches (which is similar for all sizes).

#### 2.4. Value Repetition in Several Storage Locations

#### 2.4.1. Overview

45

40 35 30

Percentage 25

20

APPLU

APS1

Several studies [34],[59],[72],[112],[139] have pointed out that value replication is common in different parts of a processor. In this section, we focus on value replication into several storage locations of data caches during the execution of programs. As explained before, Lipasti et al [72] coined the term of value locality to describe the likelihood of references of a previously seen value within a storage location. We are interested in analysing references of a previously seen value into several storage locations.

32 KB

🗖 16 KB **8 KB**

🗖 4 KB

AMEAN

We will consider a repetitive value if is frequently stored into several storage locations of the data cache. In this way, we will analyse at any given time the percentage of values that are repeated in a conventional data cache.

#### 2.4.2. Performance Evaluation

In this section we analyse in greater detail the percentage of value replication into several storage locations that can be achieved for individual benchmarks under several scenarios.

#### 2.4.2.1. Experimental Framework

Several configurations of data cache memories have been simulated with sizes ranging from 1KB to 256KB, and different degrees of associativity. The evaluation was done with the sim-cache simulator from the Alpha version of the Simplescalar toolset [15]. The original simulator was modified to collect value repetition statistics.

We now consider the next generation of Spec95 benchmarks: Spec2000. However, Yi and Lilja [135] analysed computation repetition in both Spec95 and Spec2000 benchmarks and did not find significant differences. Thus, the following Spec2000 benchmarks were randomly picked: *crafty, eon, gcc, gzip, mcf, parser, twolf, vortex and vpr* from the integer suite; and *ammp, apsi, art, equake, mesa, mgrid, sixtrack, swim* and *wupwise* from the floating point suite. The programs were compiled with the Compaq C compiler with -O5 -non\_shared optimization flags (i.e, maximum optimization). Each program was run with the reference input set and statistics were collected for 1 billion instructions after skipping the initializations (see Section 1.4 for further details of tools and benchmarks).

#### 2.4.2.2. Analysis of Results

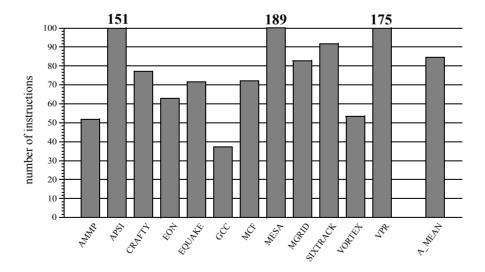

In this section we analyse the value replication of several data caches ranging from 1KB to 256 KB. Our conclusion from all the simulations performed is that there is significant value replication in data caches at any given time.

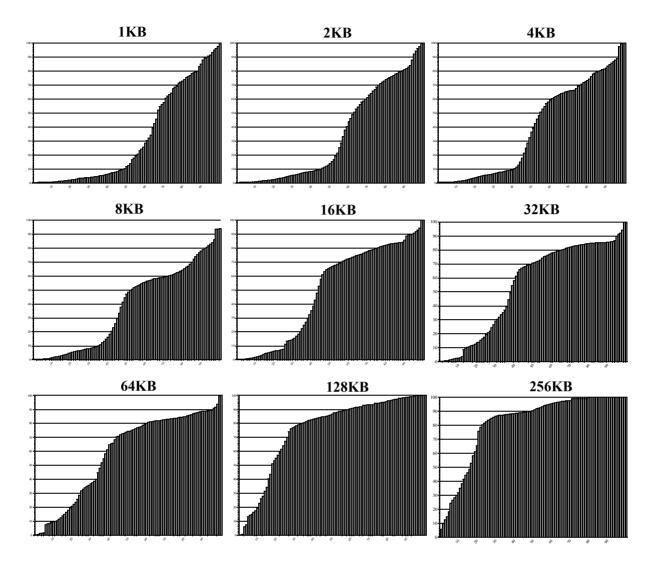

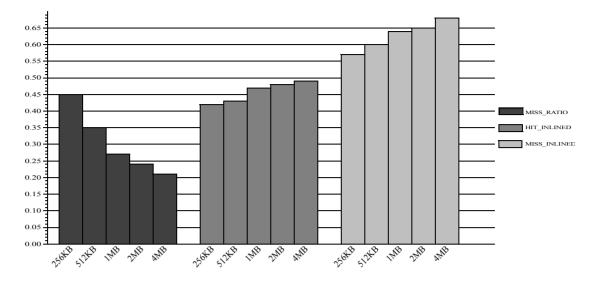

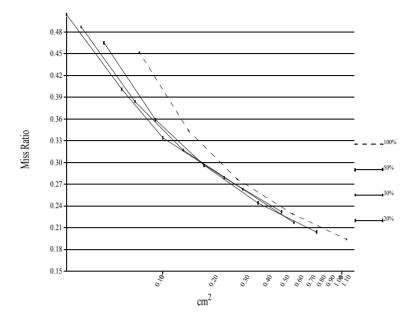

For example, Figure 2.10 shows the value replication of a 256 KB direct-mapped data cache. To obtain this data, the content of the data cache is analysed every cycle and the percentage of replicated 64-bit values is obtained. The X-axis represents the percentage of different values (0% means that all the values in the cache are the same and 100% means that all the values in the cache are different). The Y-axis represents the percentage of total execution time that the corresponding percentage of different values has been observed. Figure 2.10.a is a histogram of the degree of variability and Figure 2.10.b shows the accumulated distribution. We can see that there is a huge degree of value replication. For instance, Figure 2.10.b shows that during 80% of the execution time, less than 25% of the values of the cache are different. This means that on average, a value is stored four times. Note also that this cache never has more than 80% of different values.

Another important observation from these simulations is that the percentage of value replication increases when the caches get bigger. Figure 2.11 shows the accumulated histograms of caches ranging from 1KB to 256KB. As we indicated earlier, there is a huge percentage of value replication at any given time in all caches, but the percentage gets better when the size of the cache increases. For example, the percentage of the values in the cache that are different during 80% of the time changes from 80% in a 1KB cache to 25% in a 256KB cache. This percentage drops dramatically when caches manage the storage locations of megabytes. Finally, we also observed that the value replication degree was not affected by associativity.

Figure 2.10. Average histograms of a 256KB data cache

Figure 2.11. Average histograms of data caches ranging from 1KB to 256KB

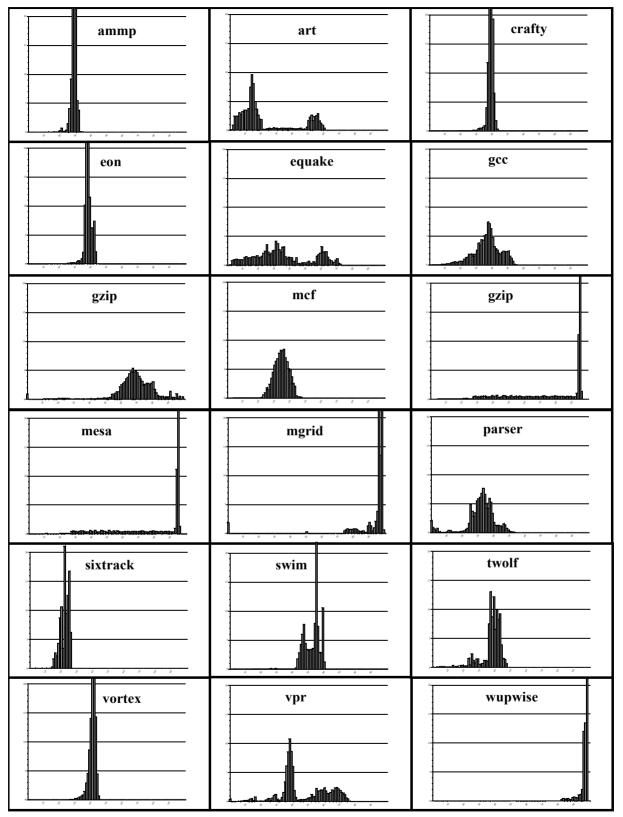

Figure 2.12 shows the histograms of the degree of variability for benchmarks considered to obtain average numbers of a 32KB data cache. In this figure the Y-axis goes from 0% to 20% because is not an accumulative histogram. Note that only a few benchmarks do not present a significant percentage of replication (i.e. *gzip*, *mesa*, *mgrid* and *wupwise*). The rest are significantly repetitive (i.e. *ammp*, *art*, *crafty*, *eon*, *gcc*, *mcf*, *parser*, *sixtrack* and *vortex* exhibit a high degree of replication) which encourages further work to develop novel techniques to exploit this feature. Moreover, value replication increases when the caches get bigger.

From the observation that many values stored in data caches are repeated, novel cache designs can be proposed and analysed to reduce die area, power dissipation and latency.

Figure 2.12. Individual histograms of a 32KB level 1 data cache

# 2.5. Non-Redundant Data Cache

We propose a new cache architecture, which we call *Non-Redundant Cache* to reduce storage area, power dissipation and latency. The underlying concept behind this proposal is based on the observation that data caches exhibit a high percentage of value replication at any given time. We first present a general description and then discuss a simple encoding/decoding scheme that can be applied to the cache. Finally, we evaluate this scheme using a dynamic and static analysis.

As it is shown in Figure 2.11, the percentage of replication gets better when the size of the cache increases. Thus, we concentrate on second-level data caches because they occupy a very important part of the die area in most processors.

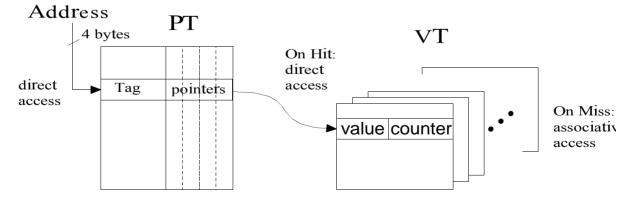

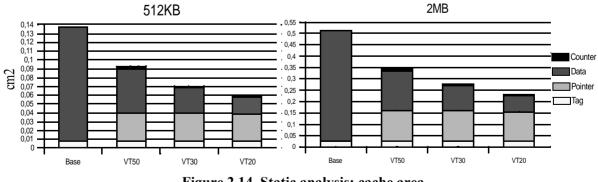

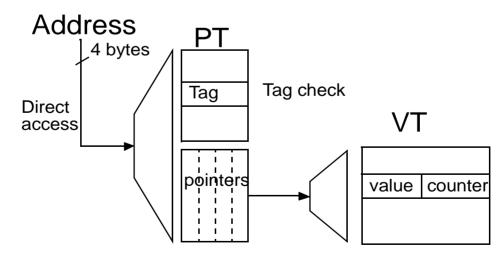

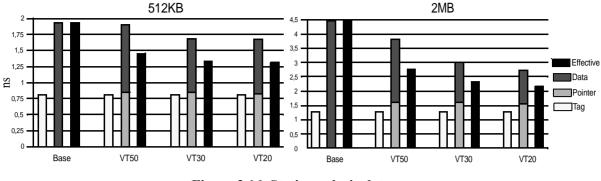

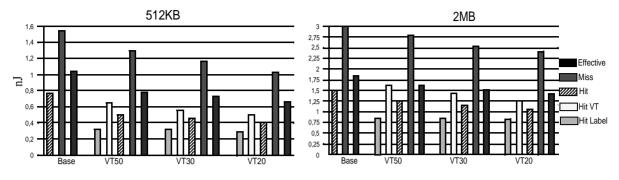

#### 2.5.1. General Description