# Capítulo III

# Estudio y Modelizado del MRC (MOS Resistive Circuit)

Las Ciencias no tratan de explicar y casi no intentan interpretar: se consagran sobre todo a hacer modelos. Por modelo se entiende una construcción matemática que, con la adición de ciertas aclaraciones verbales, describe los fenómenos observados. La justificación de esa construcción matemática es que precisamente sea única y eficaz.

John von Neumann

Tomo se ha comentado en el capítulo 2, los resistores necesarios en los filtros continuo integrados normalmente tiempo están implementados mediante transistores MOS trabajando en zona óhmica, lo que hace que su valor resistivo pueda ser ajustado mediante una o varias tensiones de control. En este capítulo se presentan las características más significativas de dichos dispositivos y el problema básico que presentan: su comportamiento no lineal. Tras estudiar una primera aproximación para realizar resistencias lineales controlables electrónicamente, consistente en una célula de dos transistores MOS, se realizará un completo análisis de la celda que se ha utilizado de forma reiterada en el trabajo de investigación de la presente tesis doctoral: el MRC (MOS Resistive Circuit), que permitirá plantear un modelo preciso que contemple diferentes aspectos de su comportamiento no ideal.

| <br> | <br> | <br> |  |

|------|------|------|--|

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

|      |      |      |  |

# SUMARIO DEL CAPÍTULO.

| Capítulo 3 Estudio y Modelizado del MRC (MOS<br>Resistive Circuit)                                                                  |      |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 3.1 Principios Básicos. El Transistor MOSFET Trabajando en Zona Óhmica                                                              | 71.  |  |  |  |  |

| 3.2 Célula Resistiva con Dos Transistores                                                                                           | 74.  |  |  |  |  |

| 3.3 Circuito Resistivo MOS (Célula MRC)                                                                                             | 76.  |  |  |  |  |

| 3.4 Una Primera Mirada al Comportamiento en Simulación del MRC                                                                      | 81.  |  |  |  |  |

| 3.5 Primera aproximación al Modelo Analítico Completo No<br>Lineal para el MRC                                                      | 83.  |  |  |  |  |

| 3.5.1 Introducción                                                                                                                  |      |  |  |  |  |

| 3.5.2 Simulación del MRC con el Modelo 'BSIM'                                                                                       |      |  |  |  |  |

| <ul><li>3.5.3 Modelo Analítico No Lineal para el MRC</li><li>3.5.4 Simulación del MRC con el modelo 'EKV'</li></ul>                 |      |  |  |  |  |

| 3.6 Modelo No Lineal Completo para el MRC                                                                                           | 94.  |  |  |  |  |

| <ul><li>3.6.1 Análisis a Través del Modelo 'EKV'</li><li>3.6.2 Efecto de la Tensión de Modo Común sobre el Comportamiento</li></ul> | 96.  |  |  |  |  |

| del MRC                                                                                                                             | 98.  |  |  |  |  |

| <b>3.6.3</b> Efecto de la Desigualdad de las Tensiones de Salida sobre el Comportamiento del MRC                                    | 100. |  |  |  |  |

| <b>3.6.4</b> Conclusiones e Indicaciones para Minimizar los Efectos No Lineales del MRC en la Práctica                              |      |  |  |  |  |

| 3.7 Caracterización Experimental de Células MRC                                                                                     | 101  |  |  |  |  |

|  | <br> |  |

|--|------|--|

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

# 3.1.- <u>PRINCIPIOS BÁSICOS. EL TRANSISTOR MOSFET TRABAJANDO EN ZONA ÓHMICA.</u>

uchos elementos resistivos emplean transistores MOS operando en la región de saturación. No obstante, cuando se necesitan elementos resistivos controlables electrónicamente (mediante una determinada tensión –o corriente– de control), se pueden emplear transistores MOS trabajando en la región óhmica (también denominada región de no saturación o región triodo). Estos elementos tienen ventajas como pueden ser simplicidad, excelente sintonía y una disipación de potencia en régimen estático prácticamente nula [CZA86], [ISM88], [KHA91]. En este capítulo se examinarán los principios básicos que rigen los elementos conductores trabajando en la región óhmica.

Un reto que se tiene en una aplicación donde aparece un transistor MOS funcionando en zona óhmica es la cancelación de las no linealidades propias del dispositivo. En este capítulo se verá que únicamente se necesitan dos transistores para cancelar las no linealidades dominantes de orden par del MOSFET [TOU90]. Asimismo, se analizará con detalle una versión, basada en el mismo principio que, en primera aproximación, cancela también las no linealidades de orden impar mediante cuatro transistores MOS [CZA86] dando, además, unos mejores resultados en sistemas que trabajan en altas frecuencias [TOU90]. Este conjunto de cuatro transistores es el denominado 'Circuito Resistivo MOS' (MRC, de MOS Resistive Circuit) o Resistor Diferencial MOSFET Doble (Double MOSFET Differential Resistor), que se ha empleado mayoritariamente en esta tesis para poder implementar los dispositivos resistivos variables electrónicamente que servirán para la autosintonía de filtros de tiempo continuo.

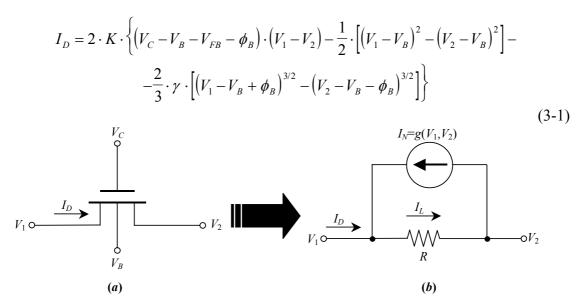

Considérese inicialmente un transistor *nMOS* como el representado en la figura 3.1.*a*, junto con su modelo de gran señal de la figura 3.1.*b*. Asumiendo que el dispositivo opera en fuerte inversión, la corriente de drenador en zona óhmica está dada de manera muy precisa por [ISM88], [TOU90]:

**Fig. 3.1.-** (*a*) Transistor MOSFET. (*b*) Modelo del MOSFET para gran señal trabajando en la zona óhmica.

Donde el parámetro y viene fijado por la expresión:

$$\gamma = \frac{1}{C_{OX}} \cdot \sqrt{2 \cdot q \cdot N_A \cdot \varepsilon_s}$$

(3-2)

siendo:

$K = (\mu \cdot C_{OX}/2) \cdot (W/L)$ : Constante del MOS, función de la relación anchura/longitud del canal.

μ: Movilidad de portadores efectiva.

V<sub>FB</sub>: Tensión de banda plana (flat band).

$C_{OX}$ : Capacidad de óxido de puerta por unidad de área.

$\phi_B$ : Potencial de superficie aproximado en fuerte inversión para polarización de puerta nula.

$N_A$ : Concentración de dopado del substrato.

$\varepsilon_S$ : Constante dieléctrica del silicio.

q: Carga del electrón.

Para simplificar el análisis del dispositivo en la región triodo, los términos de potencia 3/2 en la expresión anterior pueden ser expresados en forma de series de Taylor respecto a  $V_1$  y  $V_2$ . Así,  $I_D$  en la expresión (3-1) puede ser escrita en forma general de la siguiente manera [TOU90]:

$$I_D = K \cdot \left[ a_1 \cdot (V_1 - V_2) + a_2 \cdot (V_1 - V_2)^2 + a_3 \cdot (V_1 - V_2)^3 + \ldots \right]$$

(3-3)

donde los coeficientes  $a_i$  son independientes de  $V_1$  y  $V_2$ , pero son función de los potenciales de puerta y substrato ( $V_C$  y  $V_B$ ), así como de los parámetros del proceso.

Rescribiendo la expresión (3-1) en la forma (3-3), queda [ISM88]:

$$a_1 = 2 \cdot \left( V_C - V_T \right)$$

$$a_2 = -\left[ 1 + \frac{1}{2} \cdot \gamma \cdot \left( \phi_B - V_B \right)^{-1/2} \right]$$

(3-4)

(3-5)

$$a_{i} = \left[ A(i) \cdot \gamma \cdot \left( \phi_{B} - V_{B} \right)^{-(2 \cdot i - 3)/2} \right] \quad \text{para} \quad i \ge 3$$

(3-6)

donde  $V_T$  es el voltaje umbral, dado por:

$$V_T = V_{FB} + \phi_B + \gamma \cdot \sqrt{\phi_B + V_{SB}} = V_{TO} + \gamma \cdot \left(\sqrt{\phi_B + V_{SB}} - \sqrt{\phi_B}\right)$$

(3-7)

y los valores de las constantes A(i) son: A(3) = -1/12; A(4) = +1/32; A(5) = -1/64 ...; etc. Obsérvese que los coeficientes  $a_i$  de segundo y mayor orden son independientes de las tensiones  $V_1$  y  $V_2$ , pero son función de parámetros físicos y del proceso de fabricación del dispositivo. A medida que el coeficiente es de mayor orden, su importancia en la expresión (3-3) cada vez es menor [BAN83].

Despreciando los términos de orden mayor o igual a dos, el inverso de  $(a_1 \cdot K)$  en la expresión (3-3) es la componente lineal, denominada resistencia en pequeña señal del transistor, R, dada por:

$$R = \frac{1}{a_1 \cdot K} = \frac{1}{\mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_C - V_T)} = \left(\frac{L}{W}\right) \cdot R_S$$

(3-8)

donde  $R_S$  es la resistencia de cuadro. Como se ve, el comportamiento aproximado del MOS en pequeña señal (como ya se ha dicho, no considerando los términos de orden mayor o igual a dos) es equivalente a un resistor lineal, cuyo valor depende del punto de operación. El  $ratio\ L/W$  se utiliza para fijar el valor nominal de R. Ésta puede también ser variada mediante el cambio de  $V_C$  (denominada entonces 'tensión de control'). Los términos de segundo orden y superiores son los no lineales. Si estos términos se cancelan de alguna forma, el dispositivo MOS se convierte en un dispositivo perfectamente lineal, operando en la región triodo, donde es condición necesaria que:

$$V_{DS} \le (V_G - V_S) - V_T \Longrightarrow V_1 \le V_C - V_T$$

(3-9)

Un problema, que a menudo tienen los diseñadores de sistemas analógicos que incluyen dispositivos MOS trabajando en la zona lineal, es el de conseguir valores óhmicos elevados con dimensiones de los transistores aceptables (es decir, que el valor de L no sea demasiado grande ni el de W demasiado pequeño). Una técnica para reducir la longitud de canal manteniendo valores óhmicos elevados consiste en trabajar con tensiones puerta-surtidor pequeñas. Ahora bien, esto limita seriamente el margen dinámico de la señal de entrada  $V_1$ , en el que el transistor MOSFET trabaja en la zona de operación óhmica.

Una indicación de cómo los términos no lineales de orden superior afectan las características del transistor se puede obtener gracias a la relación entre la magnitud de los diferentes coeficientes  $a_i$  respecto del coeficiente  $a_1$ . Una situación típica [TOU90] en la práctica se puede ilustrar tomando  $V_2$ =0,  $V_1$ =1 V,  $(V_C$ - $V_T)$ =2 V,  $\mu$ · $C_{OX}$ (W/L)=10  $\mu A/V^2$  y  $V_B$ =-5 V (para una tensión de alimentación bipolar de  $\pm 5V$ , el substrato estará conectado al potencial más negativo del circuito). En este caso, el primer sumando en la parte derecha de la ecuación de la expresión (3-3) es de 20  $\mu A$ , el segundo término es de -6  $\mu A$ , el tercer término adopta un valor de  $3\cdot10^{-2}$   $\mu A$ , el cuarto de  $-2\cdot10^{-3}$   $\mu A$ , ... etc. Se ve claramente que la desviación respecto a un dispositivo lineal viene dominada por el término de segundo orden. Es por ello que interesa de manera importante eliminar o cancelar este sumando mediante conexiones particulares de dispositivos MOS. En general se cancelarán, o bien solamente los sumandos de orden par, o bien tanto los términos superiores de orden par como los de orden impar.

Para poder operar de manera mucho más simple, se supondrá que la expresión (3-3) queda dividida en términos lineal y no lineal. Si se mira el modelo de la figura 3.1.*b*, la corriente de drenador puede ser expresada como:

$$I_D = I_L - I_N (3-10)$$

donde  $I_L$  es el término lineal dado por:

$$I_{L} = \frac{1}{R} \cdot (V_{1} - V_{2}) = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{C} - V_{T}) \cdot (V_{1} - V_{2})$$

(3-11)

de forma similar,  $I_N$  es la función no lineal de  $V_1$  y  $V_2$ , y puede ser expresada como:

$$I_N = g(V_1) - g(V_2)$$

(3-12)

donde:

$$g(V_i) = g_e(V_i) + g_o(V_i).$$

(3-13)

siendo las funciones  $g_e(V_i)$  y  $g_o(V_i)$  una función par (even) e impar (odd), respectivamente, por lo que se debe cumplir:

$$g_e(V) = g_e(-V)$$

$g_o(V) = -g_o(-V)$  (3-14)

Reescribiendo  $I_N$  en términos de  $g_e(V_i)$  y  $g_o(V_i)$  resulta:

$$I_N = \{g_e(V_1) - g_e(V_2)\} + \{g_o(V_1) - g_o(V_2)\}.$$

(3-15)

El término impar  $\{g_o(V_1) - g_o(V_2)\}$  es muy pequeño comparado con el término lineal dado en la expresión (3-11) (es del orden del 0,1 % o incluso menor). Dependiendo de  $V_1$  y  $V_2$ , el término  $\{g_e(V_1) - g_e(V_2)\}$  puede ser grande y, entonces, sus efectos deben de ser eliminados. A continuación se describirán dos métodos posibles de cancelación de las no linealidades. Se comenzará por el circuito conductor de dos transistores, que consigue una cancelación parcial solamente de los términos no lineales pares, y después se pasará a describir el circuito MRC (MOS Resistive Circuit) o conductor con cuatro transistores, que consigue una cancelación (teóricamente completa) de las no linealidades.

## 3.2.- CÉLULA RESISTIVA CON DOS TRANSISTORES.

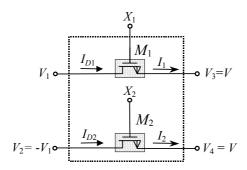

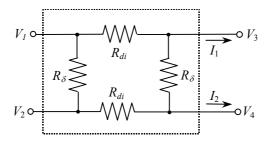

Un conductor simple que utiliza únicamente dos dispositivos MOS puede ser realizado como se presenta en la figura 3.2 [TOU90], si se cumple la condición de que los terminales de entrada estén balanceados; es decir,  $V_2 = -V_1$ , y los terminales de salida de la célula estén al mismo potencial V.

Fig. 3.2.- Conductor con dos transistores MOS.

Las corrientes de salida del conductor son las propias de drenador en ambos transistores:  $I_1 = I_{D1}$  e  $I_2 = I_{D2}$ . Descomponiendo las funciones  $g(V_i)$  ( $i = \{1,2\}$ ) en términos par e impar, tal y como se mostró en la ecuación (3-13), la componente no lineal  $I_{N1}$  de la corriente de drenador de  $M_1$  y la componente no lineal  $I_{N2}$  de la corriente de drenador  $I_2$  del transistor  $I_2$  pueden ser expresadas respectivamente como:

$$I_{N1} = \{g_e(V_1) + g_o(V_1)\} - g(V)$$

$$I_{N2} = \{g_e(V_2) + g_o(V_2)\} - g(V)$$

(3-16)

(3-17)

Examinando estas dos últimas expresiones, se observa que la no linealidad par dominante en la diferencia de corrientes puede ser cancelada mediante señales balanceadas; es decir,  $V_2 = -V_1$ . Por tanto, y como se sabe que:

$$g_e(V_1) = g_e(-V_1)$$

$g_o(V_1) = -g_o(-V_1)$  (3-18)

tomando la diferencia ( $I_{N1}$ – $I_{N2}$ ) de las componentes no lineales de las corrientes de salida se tiene:

$$(I_{N1} - I_{N2}) = [g_e(V_1) + g_o(V_1) - g(V)] - [g_e(V_2) + g_o(V_2) - g(V)] =$$

$$= [g_e(V_1) + g_o(V_1) - g(V)] + [-g_e(-V_1) - g_o(-V_1) + g(V)] =$$

$$g_e(V_1) + g_o(V_1) - g_e(V_1) + g_o(V_1)$$

$$I_{N1} - I_{N2} = 2 \cdot g_o \cdot (V_1)$$

(3-19.b)

quedando una no linealidad impar residual. Por su lado, a partir de la expresión (3-11), la componente lineal de  $I_1$ – $I_2$  será:

$$I_{1} - I_{2} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot [(X_{1} - V_{T}) \cdot (V_{1} - V) - (X_{2} - V_{T}) \cdot (V_{2} - V)] =$$

$$= \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot [(X_{1} - V_{T}) \cdot (V_{1} - V) + (X_{2} - V_{T}) \cdot (V_{1} + V)] =$$

$$= \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot [(X_{1} + X_{2} - 2 \cdot V_{T}) \cdot V_{1} + (X_{2} - X_{1}) \cdot V]$$

(3-20)

donde el término no lineal en V de la expresión se puede anular haciendo  $X_1 = X_2$  (=  $V_C$  o tensión de control). Si se ignora o desprecia la no linealidad impar dada en (3-19.b), se puede definir una conductancia diferencial en pequeña señal aproximadamente lineal y cuyo valor será:

$$G_{di} = \frac{1}{R_{di}} = \frac{i_1 - i_2}{v_1} = 2 \cdot \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (X_1 - V_T) = 2 \cdot \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_C - V_T)$$

(3-21)

que depende de la tensión umbral  $V_T$ , lo que resulta una limitación respecto de la conductancia realizada mediante los cuatro transistores MOS que se verá a continuación.

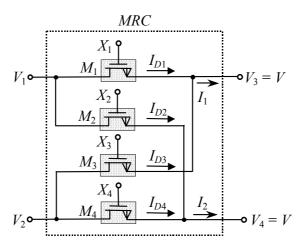

## 3.3.- CIRCUITO RESISTIVO MOS (CÉLULA 'MRC').

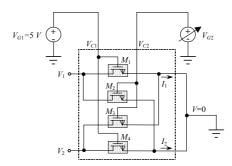

Un conductor con una mejor linealidad puede ser realizado a partir de una modificación del circuito de la figura 3.2, usando dos transistores adicionales cruzados entre las dos entradas y las dos salidas del circuito. Así se tiene una estructura con cuatro transistores MOSFET idénticos, conectados en una configuración como la mostrada en la figura 3.3, denominada dispositivo MRC (MOS Resistive Circuit o Circuito Resistivo MOS), Resistor Diferencial MOSFET Doble (Double MOSFET Differential Resistor) o también circuito de Czarnul-Song [ISM88], [TSI94]. El MRC es un circuito que está siendo utilizado ampliamente en los últimos años para la implementación de circuitos de tiempo continuo sintonizables tanto en bajas como en medias frecuencias [ISM87], [ISM88], [KHA90b], [JOH93], [BRA98a], [OSA98a], [OSA98b], [SOL99], [OSA00], [GRO00].

En este apartado se verá que con el MRC se consigue anular completamente las no linealidades (pares e impares) del conductor, sin necesidad, además, de tener entradas balanceadas; es decir, sin necesidad de cumplirse  $V_2$ = $-V_1$ , aspecto muchas veces deseable, sobre todo cuando se trabaja con alimentación unipolar. Por estas dos principales razones, este dispositivo con cuatro transistores servirá de base para la implementación de resistencias ajustables electrónicamente de los filtros autosintonizados diseñados a lo largo de la presente tesis. No obstante, como se puede apreciar en la figura 3.3, y al igual que la célula con dos transistores, es necesario que se continúe teniendo igualdad en las tensiones de los terminales de salida para conseguir la adecuada cancelación de los términos no lineales, tal y como se mostrará a continuación. Para obtener dicha igualdad de tensiones en estos terminales, éstos suelen conectarse en la mayoría de aplicaciones a las entradas de un amplificador operacional trabajando en zona lineal.

Los cuatro dispositivos MOS de la figura 3.3 pueden ser transistores de empobrecimiento o enriquecimiento, de canal n o de canal p (aunque los cuatro del mismo tipo). Si se considera que cada corriente de drenador puede ser expresada de acuerdo con la expresión (3-10), la componente no lineal  $I_{N1}$  de la corriente  $I_1$  puede ser escrita como [TOU90]:

$$I_{N1} = I_{ND1} + I_{ND3} = \{g(V_1) - g(V)\} + \{g(V_2) - g(V)\}$$

(3-22)

y la componente no lineal  $I_{N2}$  de la corriente  $I_2$ :

$$I_{N2} = I_{ND2} + I_{ND4} = \{g(V_1) - g(V)\} + \{g(V_2) - g(V)\}$$

(3-23)

Las expresiones anteriores muestran que las componentes no lineales de las corrientes  $I_1$  e  $I_2$  son idénticas. Por ello, la cancelación completa de los términos no lineales sucede cuando se toma la diferencia de las corrientes de salida de la célula MRC ( $I_1$ – $I_2$ ). Por otro lado, la componente lineal de  $I_1$  viene dada por:

$$I_{L1} = I_{LD1} + I_{LD3} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (X_1 - V_T) \cdot (V_1 - V) + (X_3 - V_T) \cdot (V_2 - V) \right]$$

(3-24)

Fig. 3.3.- Conductor con cuatro transistores (MRC).

y, de forma similar, la componente lineal de  $I_2$  vale:

$$I_{L2} = I_{LD2} + I_{LD4} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (X_2 - V_T) \cdot (V_1 - V) + (X_4 - V_T) \cdot (V_2 - V) \right]$$

(3-25)

tomando la diferencia de corrientes:  $(I_1-I_2) = (I_{L1}-I_{L2})$ , queda:

$$I_{1} - I_{2} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (X_{1} - X_{2}) \cdot (V_{1}) + (X_{3} - X_{4}) \cdot (V_{2}) + (X_{2} + X_{4} - X_{1} - X_{3}) \cdot V \right]$$

(3-26)

Por otro lado, la tensión V (en los surtidores de los transistores) es una función no lineal de las señales  $V_1$  y  $V_2$  (en los drenadores de los mismos) [ISM88]. Así, para obtener una verdadera diferencia de corrientes completamente lineal  $(I_1-I_2)$ , el sumando con V en la expresión anterior debe ser forzado a cero. De esta forma, resulta una cancelación total de las no linealidades si se cumple:

$$X_1 + X_3 = X_2 + X_4 \tag{3-27}$$

considerando asimismo que todos los dispositivos MOS son iguales (no existen errores de desapareamiento entre ellos) y están siempre trabajando en su región óhmica. Esta última condición se satisface cuando se cumple:

$$V_i \le \min \left( X_j - V_T \right)$$

donde  $j=1, 2$  para  $i=1$  y  $j=3, 4$  para  $i=2$ . (3-28)

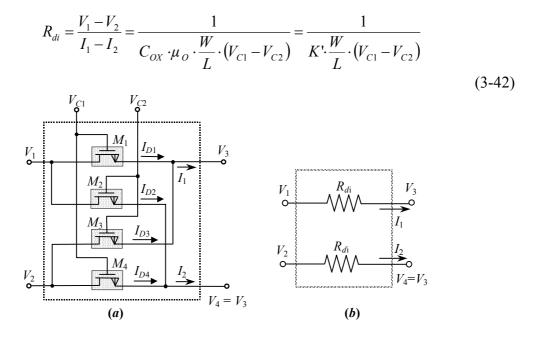

Se llega a una particularización de las propiedades del conductor general descritas anteriormente cuando  $V_1$  y  $V_2$  son las señales AC de entrada al MRC ( $v_1$  y  $v_2$ ). En este caso, las señales  $X_i$  son utilizadas como tensiones DC de control con  $X_1 = X_4 = V_{C1}$  y  $X_2 = X_3 = V_{C2}$ . Así, se satisface la expresión (3-27) y resulta un equivalente a una conductancia diferencial en pequeña señal dada por la expresión:

$$G_{di1} = \frac{1}{R_{di1}} = \frac{i_1 - i_2}{v_1 - v_2} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{C1} - V_{C2})$$

(3-29)

donde se ha de cumplir:

$$V_{1} + v_{1} \leq \min \left[ (V_{C1} - V_{T}), (V_{C2} - V_{T}) \right]$$

$$V_{2} + v_{2} \leq \min \left[ (V_{C1} - V_{T}), (V_{C2} - V_{T}) \right]$$

(3-30.a)

(3-30.b)

para asegurar en todo momento que los cuatro transistores MOS se encuentran trabajando en zona lineal, y donde  $V_1$  y  $V_2$  (en mayúsculas) son niveles de polarización DC que podrían tener las entradas del MRC superpuestos a las señales de AC ( $v_1$  y  $v_2$ , respectivamente).

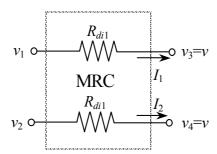

Teniendo en cuenta el análisis anterior, el MRC puede modelarse como un par de resistencias diferenciales idénticas, cada una de ellas de valor  $R_{di1}$ , tal como se aprecia en la figura 3.4:

Fig. 3.4.- Modelo básico con dos resistores del MRC.

Otra posible configuración, por simetría con el caso anterior, se obtiene mediante el intercambio de la entrada y las tensiones de polarización (es decir, las tensiones de control). Esto significa que  $X_1=X_4$  y  $X_2=X_3$  son las entradas de señal AC ( $v_{C1}$  y  $v_{C2}$ , respectivamente), mientras que  $V_1$  y  $V_2$  son ahora las entradas de control. En estas condiciones, la conductancia  $G_{di2}$  equivalente vendrá dada por la expresión:

$$G_{di2} = \frac{1}{R_{di2}} = \frac{i_1 - i_2}{v_{C1} - v_{C2}} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_1 - V_2)$$

(3-31)

donde ahora las condiciones a cumplir son:

$$V_{C1} + v_{C1} \ge \max \left[ (V_1 + V_T), (V_2 + V_T) \right]$$

$$V_{C2} + v_{C2} \ge \max \left[ (V_1 + V_T), (V_2 + V_T) \right]$$

(3-32.a)

(3-32.b)

para asegurar también que en todo momento los dispositivos MOS se encuentran trabajando en su zona óhmica. En este caso  $V_{C1}$  y  $V_{C2}$  (en mayúsculas) son posibles niveles de polarización DC de las entradas del MRC superpuestos a las señales de AC ( $v_{C1}$  y  $v_{C2}$ , respectivamente).

Supóngase ahora que a las entradas  $X_i$  y  $V_j$  se les someten sendas señales AC, con valores tales que todos los transistores están trabajando en su zona óhmica, de manera que la expresión dada en (3-28) se cumple. En este caso, la conductancia equivalente resultante será variable en el tiempo. Se puede apreciar que se consigue a la salida el producto de las dos señales de entrada:

$$i_1 - i_2 = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (v_1 - v_2) \cdot (x_1 - x_2)$$

(3-33.a)

De esta manera se pueden realizar multiplicadores de cuatro cuadrantes de tiempo continuo. Si se asume, por conveniencia, señales balanceadas (es decir,  $x=x_1=-x_2$  e  $y=v_1=-v_2$ ) se llega a:

$$i_1 - i_2 = 4 \cdot \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot x \cdot y$$

(3-33.b)

Además, utilizando las expresiones (3-30) o (3-32), la condición para que los dispositivos MOS operen en la zona lineal es:

$$x(t) - y(t) \ge V_T \tag{3-34}$$

para cualquier valor de t. Esta condición es fácil de satisfacer si los dispositivos son de deplexión (empobrecimiento), pues tienen una tensión umbral  $V_T$  negativa y pueden aceptar señales alternas en sus puertas con valor medio nulo. Si se utilizan dispositivos de enriquecimiento, se necesita un nivel DC en las señales de entrada para que los transistores puedan trabajar de forma correcta.

Aprovechando esta propiedad del circuito MRC, el diseño e implementación de detectores de fase (bloque necesario en el sistema que se ha diseñado posteriormente) es sencillo, pues solamente se necesitan cuatro transistores MOSFET para cada multiplicador analógico.

Es importante considerar también que las entradas AC al conductor MRC, independientemente de si son las  $x_j$  o las  $v_i$ , no necesitan estar balanceadas. Por tanto, este circuito puede ser utilizado para desarrollar filtros continuos MOSFET simples (single-ended), sin necesidad de tener amplificadores operacionales con salidas balanceadas, evitando así la complejidad de este tipo de amplificadores. Las estructuras completamente balanceadas, sin embargo, eliminan la no linealidad de segundo orden dominante generada como resultado del fenómeno conocido como 'degradación de la movilidad', que ha sido despreciada en el análisis anterior, pero cuyos efectos se analizarán detalladamente más adelante en el presente capítulo.

También es significativo hacer notar que las anteriores demostraciones, y las correspondientes cancelaciones de los términos no lineales, se han realizado considerando que las funciones g(V) que forman dichas componentes no lineales de  $I_D$ :

$$I_N = g(V_D) - g(V_S)$$

(3-35)

son funciones totalmente arbitrarias. Un modelo del MOSFET sencillo, dado por la ecuación aproximada (pero muy utilizada) que describe su comportamiento en zona óhmica es el que se expresa a continuación:

$$I_{D} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{GS} - V_{T}) \cdot V_{DS} - \frac{V_{DS}^{2}}{2} \right] = K' \cdot \frac{W}{L} \cdot \left[ (V_{GS} - V_{T}) \cdot V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(3-36)

donde se distingue una componente lineal y una componente no lineal de segundo orden, que corresponde al término no lineal dominante. Así, a partir del circuito de la figura 3-3,  $I_1$  valdrá:

$$I_{1} = I_{D1} + I_{D3} = K' \cdot \frac{W}{L} \cdot \left[ (X_{1} - V - V_{T}) \cdot (V_{1} - V) - \frac{(V_{1} - V)^{2}}{2} \right] + K' \cdot \frac{W}{L} \cdot \left[ (X_{3} - V - V_{T}) \cdot (V_{2} - V) - \frac{(V_{2} - V)^{2}}{2} \right]$$

(3-37)

Mientras que  $I_2$  es:

$$I_{2} = I_{D2} + I_{D4} = K' \cdot \frac{W}{L} \cdot \left[ (X_{2} - V - V_{T}) \cdot (V_{1} - V) - \frac{(V_{1} - V)^{2}}{2} \right] + K' \cdot \frac{W}{L} \cdot \left[ (X_{4} - V - V_{T}) \cdot (V_{2} - V) - \frac{(V_{2} - V)^{2}}{2} \right]$$

(3-38)

Tomando la diferencia de ambas corrientes se tendrá:

$$I_{1} - I_{2} = K' \cdot \frac{W}{L} \cdot \left\{ \left[ (X_{1} - V - V_{T}) \cdot (V_{1} - V) - \frac{(V_{1} - V)^{2}}{2} \right] + \left[ (X_{3} - V - V_{T}) \cdot (V_{2} - V) - \frac{(V_{2} - V)^{2}}{2} \right] - \left[ (X_{2} - V - V_{T}) \cdot (V_{1} - V) - \frac{(V_{1} - V)^{2}}{2} \right] - \left[ (X_{4} - V - V_{T}) \cdot (V_{2} - V) - \frac{(V_{2} - V)^{2}}{2} \right] \right\}$$

$$(3-39.a)$$

Haciendo que  $X_1=X_4$  (= $V_{C1}$ ) y  $X_2=X_3$  (= $V_{C2}$ ), operando y simplificando términos se obtiene:

$$I_{1} - I_{2} = K \cdot \frac{W}{L} \cdot \{ [(X_{1} \cdot V_{1}) + (X_{2} \cdot V_{2})] - [(X_{1} \cdot V_{2}) + (X_{2} \cdot V_{1})] \}$$

(3-39.b)

o lo que es lo mismo:

$$I_1 - I_2 = K' \cdot \frac{W}{L} \cdot [(V_1 - V_2) \cdot (X_1 - X_2)]$$

(3-39.c)

Por lo que resulta una conductancia diferencial equivalente de valor:

$$G_{di1} = \frac{I_1 - I_2}{V_1 - V_2} = K' \cdot \frac{W}{L} \cdot (X_1 - X_2) = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{C1} - V_{C2})$$

(3-40)

que coincide con la expresión (3-29) obtenida anteriormente.

Dos problemas asociados al MRC son que, por un lado, cuando la diferencia de tensiones  $(X_1-X_2)$  disminuye, el dispositivo (y, por tanto, el circuito del cual forma parte) es más sensible a los posibles (y casi inevitables) errores de apareamiento entre los cuatro transistores. Por otro lado, el ruido térmico a la salida del dispositivo es mayor que el dispositivo con dos transistores [OSA99], [OSA01].

Además de estos dos, existe un tercer problema cuyo efecto es una no linealidad adicional causada por la dependencia de la movilidad de portadores de la tensión de puerta en los dispositivos MOS que en los análisis previos se ha considerado (por simplicidad) constante, pero que modelos más avanzados del MRC debe contemplarse como parámetro variable, función del campo eléctrico transversal en el transistor MOS. En los apartados 3.5 y 3.6 se incluirá dicho efecto en el modelo desarrollado en los mismos.

### 3.4.- <u>UNA PRIMERA MIRADA AL COMPORTAMIENTO</u> EN SIMULACIÓN DEL 'MRC'.

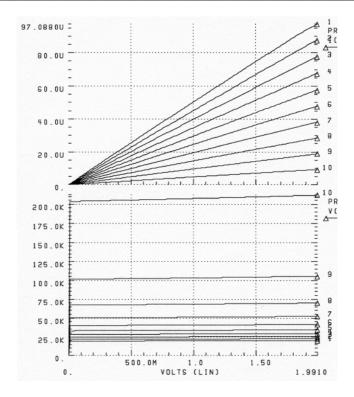

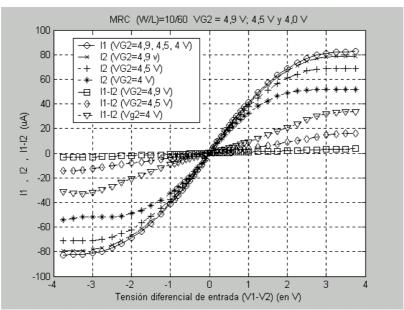

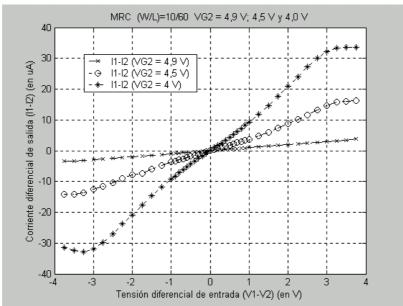

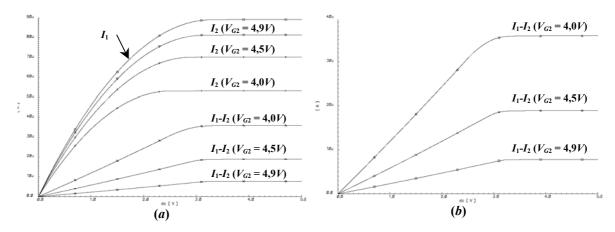

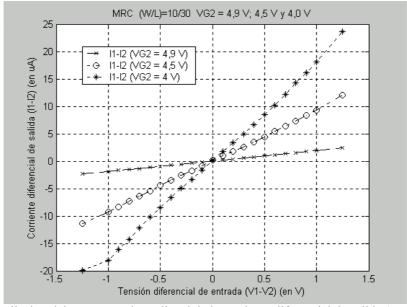

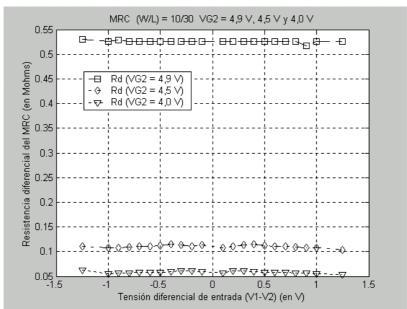

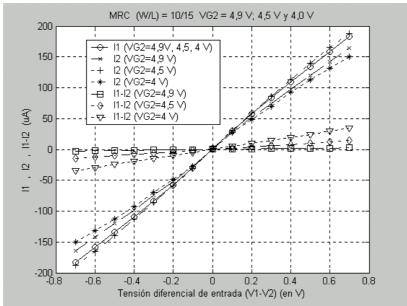

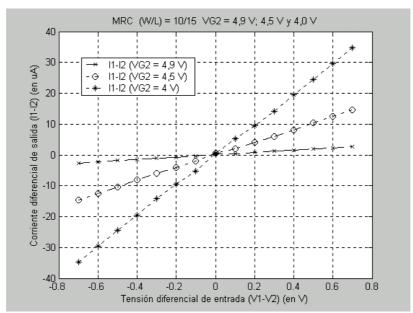

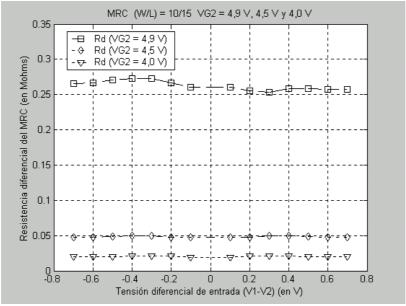

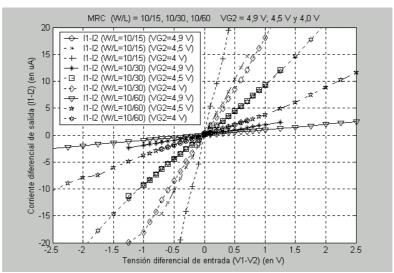

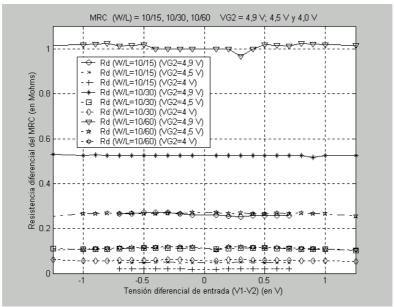

Antes de continuar con el análisis del MRC, resulta conveniente mostrar los resultados de simulación efectuada sobre una célula MRC con HSPICE<sup>®</sup> y el modelo BSIM3v2 (*level* 47) del transistor MOS (Berkeley Short-Channel IGFET Model [SHE87], [HSP96a], [HSP96b], [HSP96c], [STA98]) y extraer algunas conclusiones interesantes. Los parámetros del modelo son para un proceso CMOS de 0,8  $\mu$ m:  $C_{OX}$  = 1,04385·10<sup>-7</sup>  $F/cm^2$ ,  $\mu_O$  = 479  $cm^2/V \cdot s$ ,  $V_{TO}$  = 0,8 V. Dichos parámetros son suministrados por AMS para el entorno de simulación y diseño Cadence Design Systems, Inc. La figura 3.5 presenta los resultados de esta simulación. En ella se efectúa un barrido de la tensión de entrada al MRC (( $V_1$ – $V_2$ ) en la figura 3.3) entre 0 y 2 V, para diferentes valores de la tensión de control ( $V_{C1}$ – $V_{C2}$ ) de 0,1 a 1 V en incrementos de 0,1 V. En el abanico de curvas de la gráfica superior de la figura 3.5 se representa la corriente de salida diferencial del MRC (( $I_1$ – $I_2$ ) en la figura 3.3) en función de la tensión diferencial de entrada (( $V_1$ – $V_2$ ) en la misma figura); es decir, la pendiente de las curvas son los valores de la conductancia  $G_{di1}$ , obtenida en la expresión (3-30). La linealidad de dicha relación es apreciable, según se ve en dichas gráficas.

Fig. 3.5.- Resultados de la simulación para un MRC en el que se puede observar la linealidad existente entre la corriente diferencial de salida y la tensión diferencial de entrada  $(V_1-V_2)$ . En la gráfica superior se muestra la corriente diferencial de salida  $(I_1-I_2)$  en función de la tensión diferencial de entrada  $(V_1-V_2)$ . Por su parte, en la gráfica inferior se muestra la resistencia diferencial (o relación  $(V_1-V_2)/(I_1-I_2)$ ) en función de la misma tensión diferencial  $(V_1-V_2)$ . Las gráficas corresponden a diferentes valores de la tensión de control  $(V_{C1}-V_{C2})$  de 0,1 a 1 V en incrementos de 0,1 V.

En la gráfica inferior de la misma figura se muestra, para el mismo abanico de valores de las tensiones de control, la resistencia diferencial que presenta el MRC definida como:

$$R_{di} = \frac{v_1 - v_2}{i_1 - i_2} \tag{3-41}$$

Conviene destacar que en dicha figura se aprecia un incremento de la resistencia diferencial cuando la tensión drenador—surtidor aumenta. Dicho incremento se ve acentuado para valores óhmicos elevados. Este comportamiento contradice la expresión de la conductancia diferencial dada en (3-40), cuyo valor es independiente de la tensión drenador—surtidor. Por tanto, si quiere mejorarse el modelo del MRC, éste debe contemplar la variación de la resistencia, función de la tensión de entrada al MRC.

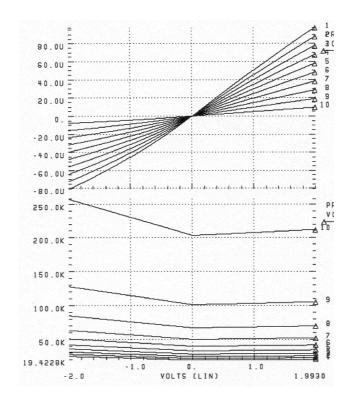

En una segunda simulación, y para comprobar si el MRC tiene un comportamiento simétrico para una tensión de entrada bipolar, se amplía el barrido de entrada hasta el margen entre -2 V y +2 V. Los resultados se pueden ver en la figura 3.6.

Estas simulaciones muestran que el MRC no presenta, ni mucho menos, un comportamiento simétrico para valores positivos o negativos similares de la tensión de entrada al mismo  $(V_1-V_2)$ . Esta asimetría se ve acentuada para valores óhmicos elevados. Esto tendría como resultado un procesado diferente para el semiciclo positivo y negativo de una señal aplicada a la entrada de la célula, obteniendo distorsión en la

señal de salida del circuito donde se empleen los MRCs. Sin embargo, estas simulaciones contradicen claramente el comportamiento totalmente simétrico que tiene el transistor MOS (y por tanto el MRC) entre los terminales de drenador y surtidor respecto del terminal de puerta. En los siguientes apartados se estudiará con detalle el porqué de estos fenómenos no lineales que presenta la simulación con el modelo BSIM del MRC: la asimetría respecto al signo en sus terminales de entrada y el incremento que sufre la resistencia diferencial del MRC en función de su tensión de entrada.

Fig. 3.6.- Resultados de la simulación para un MRC con un barrido de la tensión diferencial de entrada  $(V_1-V_2)$  entre  $-2\ V\ y+2\ V$ . En la gráfica superior se muestra la corriente diferencial de salida  $(I_1-I_2)$  en función de la tensión diferencial de entrada  $(V_1-V_2)$ . Por su parte, en la gráfica inferior se muestra la resistencia diferencial (o relación  $(V_1-V_2)/(I_1-I_2)$ ) en función de la misma tensión diferencial  $(V_1-V_2)$ . Las gráficas corresponden a diferentes valores de la tensión de control  $(V_{C1}-V_{C2})$  de 0,1 a 1 V en incrementos de 0,1 V.

# 3.5.- <u>PRIMERA APROXIMACIÓN AL MODELO ANALÍ-</u> TICO COMPLETO NO LINEAL PARA EL 'MRC'.

#### 3.5.1.- Introducción.

En circuitos basados en células MRC pueden encontrarse importantes diferencias, como se ha comentado en el apartado anterior, entre el comportamiento real y el predicho por el modelo simple de dos resistencias diferenciales presentado hasta este momento: el valor de la resistencia real del MRC no coincide con el ideal y lo que es más importante, se observan comportamientos no lineales. Uno de estos comportamientos no lineales es descrito y modelado en [OSA98a] y [OSA99], donde se analizan los efectos derivados de la desigualdad en las tensiones de los dos terminales de salida del MRC o, en otras palabras, el efecto de la ganancia no infinita del

amplificador operacional y su tensión de *offset* de entrada al que el MRC es conectado. En los siguientes subapartados, y con el fin de separar efectos, se supondrá que la igualdad de las tensiones de salida del MRC se cumple perfectamente. Posteriormente en este mismo capítulo se estudiarán, además, los efectos acarreados al considerar el MRC trabajando con sus salidas conectadas a un amplificador operacional con ganancia de lazo abierto no infinita y, a partir del ellos, ampliar y completar el modelo del MRC desarrollado en [OSA98a] y [OSA99].

Por otra parte, y como se verá a continuación, el ampliamente utilizado modelo BSIM [SHE87], [HSP96a], [HSP96b], [HSP96c], [STA98] no es capaz de modelar adecuadamente el comportamiento no lineal que muestra la resistencia controlada que se realiza con la célula MRC, aún cuando se asegura que la tensión diferencial a la salida es despreciable. Este comportamiento no lineal está relacionado con la dependencia que presenta la movilidad de los portadores del transistor MOS con la tensión de puerta aplicada. Por lo tanto, un conocimiento preciso de este comportamiento requiere un modelo de simulación capaz de reflejar adecuadamente esta variación. En los siguientes subapartados, y tras demostrar la invalidez en este aspecto del modelo BSIM y proponer el uso en su lugar del modelo analítico EKV (C.C. Enz, F. Krummenacher y E.A. Vittoz [ENZ95], [MAC96]), se realiza una descripción analítica no lineal completa de la célula MRC.

#### 3.5.2.- Simulación del MRC con el Modelo 'BSIM'.

Como ya se ha deducido en apartados anteriores, idealmente, la célula MRC (figura 3.7) es equivalente a un transconductor diferencial cuya corriente diferencial de salida ( $I_1$ – $I_2$ ) depende linealmente de la tensión diferencial aplicada a la entrada ( $V_1$ – $V_2$ ), supuesta nula la tensión diferencial de salida ( $V_3$ = $V_4$ ). Asumiendo una movilidad de portadores  $\mu_O$  constante, el valor de las dos resistencias diferenciales idénticas que constituyen el modelo básico del MRC de la figura 3.7 es [CZA86], [ISM87]:

Fig. 3.7.- (a) Circuito MRC (MOS Resistive Circuit). (b) Modelo básico de dos resistencias.

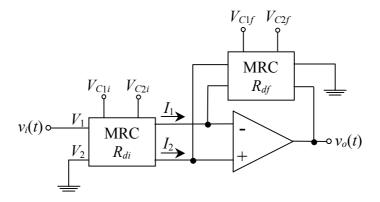

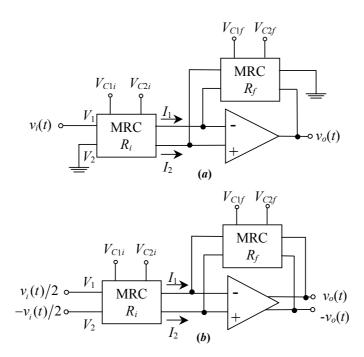

Cuando para simular esta célula se utilizan modelos para el transistor MOS sencillos, como el basado en la ecuación (3-36), los resultados son coincidentes a las predicciones teóricas. Sin embargo, cuando los modelos de simulación son más complejos, como por ejemplo el modelo BSIM3 del MOS que implementa el nivel 47 de HSPICE<sup>®</sup> [STA98], [BAK98], el valor obtenido difiere notablemente del predicho por (3-42) [VID99], [VID00a], [VID00b], [VID02]. A modo de ejemplo, supóngase el amplificador clásico de la figura 3.8 implementado con dos células MRC idénticas con una relación de aspecto W/L=2/300, y un amplificador operacional de ganancia lo suficientemente elevada como para poder considerar la tensión diferencial de entrada prácticamente nula. Los MRC tienen unas tensiones de control idénticas ( $V_{C1i} = V_{C1f} = 3,3 V y V_{C2i} = V_{C2f} = 2,8 V$ , con  $V_B = -1,7 V$ ) para conseguir de esta manera resistencias idénticas y, por tanto, una ganancia de tensión en el circuito de -1.

**Fig. 3.8.-** Amplificador implementado con dos células MRC idénticas con una relación de aspecto de W/L = 2/300. Los parámetros del modelo son suministrados por AMS para un proceso CMOS de 0,8  $\mu$ m:  $C_{OX} = 1,04385 \cdot 10^{-7} \ F/cm^2$ ,  $\mu_O = 479 \ cm^2/V \cdot s$ ,  $V_{TO} = 0,8 \ V$ .

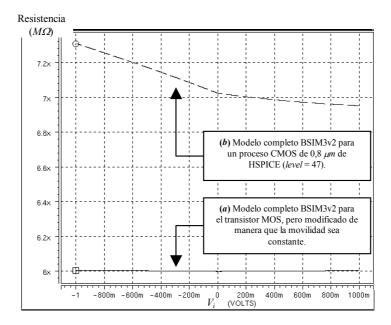

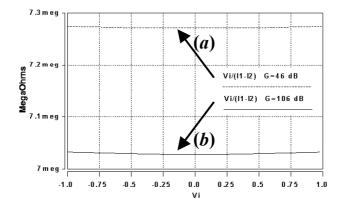

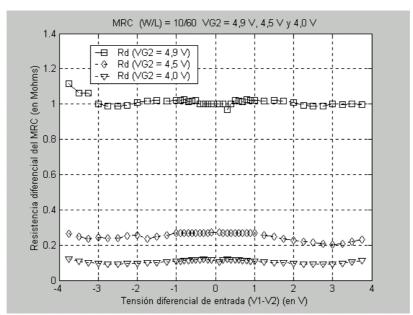

En la figura 3.9 se presentan los resultados de simulación de la resistencia diferencial  $R_{di}$  (= $V_i/(I_1-I_2)$ ) del MRC de entrada en función de la tensión de entrada  $V_i$  (= $V_1-V_2$ ) del modelo BSIM3v2 para un proceso CMOS de 0,8  $\mu$ m de HSPICE (level = 47). Por un lado, el valor resistivo predicho por el modelo completo BSIM3 (línea discontinua superior de la figura 3.9) muestra una no linealidad, pues presenta una dependencia con la tensión de entrada (eje x), que no aparece descrita en absoluto en (3-42), además de tener un valor óhmico mayor que el predicho por esta ecuación.

Por otro lado, al modificar en el mismo modelo BSIM3 el parámetro que modela la movilidad de los portadores debida al campo eléctrico transversal, de manera que permanezca constante y, por tanto, independiente de cualquier tensión aplicada al dispositivo MOS, se obtiene una relación entre la tensión de entrada  $V_i$  y la diferencia de corrientes de salida del MRC ( $I_1$ – $I_2$ ) prácticamente constante, reflejando el comportamiento ideal de la expresión (3-42) (línea continua inferior de la misma figura 3.9). En consecuencia, ya que esta dependencia con la tensión de entrada de la resistencia incremental diferencial del MRC desaparece cuando se impone un valor constante para la movilidad  $\mu_O$ , debe achacarse a la variación de este parámetro el comportamiento no lineal del MRC que aparece en simulación.

Fig. 3.9.- Resultados obtenidos de simulación con HSPICE<sup>®</sup> de la resistencia diferencial  $R_{di}$  del MRC entrada del amplificador inversor de la figura 3.8. (a) Modelo BSIM3v2 para el transistor MOS, pero modificado de manera que la movilidad sea constante (línea continua). (b) Modelo completo BSIM3v2 (level = 47) (línea discontinua).

Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en V, donde  $V_i = V_1-V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos terminales de entrada la MRC.

De la figura 3.9 también se deduce que la pendiente de la resistencia depende de la polaridad de la tensión de entrada. Este extraño resultado contradice claramente la simetría física del transistor MOS real (entre los terminales de drenador y surtidor, respecto del terminal de puerta) y, como consecuencia, de la célula MRC. Esta simetría física inherente puede verse en la expresión de la característica tensión-corriente de MOSFET operando en la zona óhmica propuesta por el modelo de primer orden del transistor:

$$I_{D} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{GS} - V_{T}) \cdot V_{DS} - \frac{V_{DS}^{2}}{2} \right] = K' \cdot \frac{W}{L} \cdot \left[ (V_{GS} - V_{T}) \cdot V_{DS} - \frac{V_{DS}^{2}}{2} \right] = K' \cdot \frac{W}{L} \cdot \left[ (V_{G} - V_{T}) \cdot (V_{D} - V_{S}) - \frac{1}{2} \cdot (V_{D}^{2} - V_{S}^{2}) \right]$$

$$(3-43)$$

puesto que la ecuación anterior solamente sufre un cambio total de signo cuando los subíndices D y S son intercambiados entre sí. Conviene decir que aunque la anterior ecuación muestra un modelo de primer orden, la simetría se sigue teniendo en modelos más completos del transistor MOS.

La causa de estos resultados no simétricos presentados en la característica (*b*) de la figura 3.9 es la dependencia de la movilidad con la tensión puerta-surtidor que implementa el modelo BSIM, que puede ser expresada aproximadamente por [STA98]:

$$\mu \approx \frac{\mu_O}{1 + \theta \cdot (V_{GS} - V_T)} \tag{3-44}$$

donde  $\mu_O$  es la movilidad máxima,  $\theta$  un parámetro que depende de la anchura del óxido y  $V_T$  la tensión umbral de los transistores. Como puede observarse, ésta es una expresión no simétrica de los terminales de drenador y surtidor respecto el de puerta y, por lo tanto, no modeliza apropiadamente el comportamiento y la estructura inherentemente simétricos al dispositivo del transistor MOS.

Para corroborar la afirmación de que este modelizado de la movilidad es el responsable de la asimetría observada en la simulación HSPICE se determinará, a partir de la expresión de la movilidad dada en (3-44), la corriente diferencial de salida ( $I_1$ – $I_2$ ) de la célula MRC. Si se asume que en la mayoría de los casos se tiene  $\theta \approx 0.03V^{-1}$  y ( $V_{GS}$ – $V_T$ )<3,3 V, la ecuación anterior puede ser expresada de forma más simple mediante una aproximación de primer orden:

$$\mu_i \approx \frac{\mu_O}{1 + \theta \cdot (V_{GSi} - V_T)} \cong \mu_O \cdot \left[1 - \theta \cdot (V_{GSi} - V_T)\right] \qquad \text{con} \qquad i = \{1, 2\}$$

(3-45)

Si cada transistor de la figura 3.7 se describe con un modelo sencillo, dado por la ecuación aproximada que modeliza su comportamiento en zona óhmica, vista en (3-43), pero teniendo en cuenta la movilidad no constante expresada en (3-45), la corriente diferencial de salida  $(I_1 - I_2)$  valdrá:

$$I_{1} - I_{2} = (V_{1} - V_{2}) \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (\eta_{1}V_{C1} - \eta_{2}V_{C2}) + (\eta_{2} - \eta_{1}) \cdot \left( V_{T} + \frac{V_{1} + V_{2}}{2} \right) \right] +$$

$$+ C_{OX} \cdot \frac{W}{L} \cdot \mu_{O} \cdot \theta \cdot \left[ V_{3} \cdot (V_{1} - V_{3}) - \gamma \cdot (V_{2} - V_{3}) \right] \cdot (V_{C1} - V_{C2})$$

(3-46)

donde  $\eta$  y  $\gamma$  se definen a partir del agrupamiento de términos como:

$$\eta_{i} = \mu_{O} \cdot \left[1 - \theta \cdot (V_{Ci} - V_{T})\right] \quad \text{con} \quad i = \{1, 2\}$$

$$\gamma = \begin{cases} V_{3} & \text{si} & sign(V_{1} - V_{3}) = sign(V_{2} - V_{3}) \\ V_{2} & \text{si} & sign(V_{1} - V_{3}) \neq sign(V_{2} - V_{3}) \end{cases}$$

(3-48)

es decir,  $\gamma = V_3$  cuando el terminal de salida del MRC al que corresponde una tensión  $V_3$  (que es igual a  $V_4$ ) es el drenador (o el terminal de fuente) simultáneamente para los cuatro transistores del MRC de la figura 3.7, y  $\gamma = V_2$  cuando este terminal actúa como terminal de drenador (o terminal de fuente) para los transistores 1 y 3, mientras que es fuente (o terminal de drenador) para los transistores 2 y 4. Recuérdese, tal y como se ha explicado en apartados anteriores, que para el correcto funcionamiento del MRC es necesario que se tenga igualdad en las tensiones de sus terminales de salida ( $V_3 = V_4$ ) para conseguir la adecuada cancelación de los términos no lineales.

Se aprecia que la expresión resultante para la corriente diferencial es no lineal y es no simétrica respecto los terminales de drenador y fuente. Ambos comportamientos pueden observarse en la curva superior de la figura 3.9 obtenida con el modelo BSIM. Como ya se ha comentado, este comportamiento claramente no simétrico contradice la propia simetría del MOSFET. Es precisamente el modelizado de la dependencia que

tiene la movilidad del MOSFET ( $\mu$ ) respecto la tensión puerta-surtidor ( $V_{GS}$ ) en el modelo BSIM3 la que rompe la simetría en la simulación de las expresiones (3-42) y (3-43), y su inclusión en el análisis del MRC lleva a la expresión no simétrica dada en (3-46).

#### 3.5.3.- Modelo Analítico No Lineal para el MRC.

Para poder obtener un modelo más preciso para la resistencia diferencial equivalente del MRC que pueda explicar también la simetría inherente de la célula, se propone el uso de una expresión simétrica para la dependencia de la movilidad  $\mu$  de los portadores con el campo transversal del transistor MOS inspirada en el modelo EKV [ENZ95]. La expresión que se propone y que tiene en cuenta la variación de la movilidad de los portadores con la tensión aplicada es:

$$\mu = \frac{\mu_O}{1 + \theta \cdot (V_G - V_B - V_T)}$$

(3-49)

donde  $V_B$  es el potencial de substrato o *body* del transistor.

Esta expresión permite obtener una expresión simétrica para la corriente de salida diferencial ( $I_1$ – $I_2$ ) del MRC. En efecto, teniendo en cuenta la ecuación (3-43) mostrada anteriormente para la corriente  $I_D$  en un dispositivo MOS:

$$I_{D} = I_{1} - I_{2} = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{GS} - V_{T}) \cdot V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(3-43)

y que la movilidad  $\mu$  de cada transistor es diferente en función de su potencial de puerta,  $V_G$ , las corrientes de salida de la célula MRC,  $I_1$  e  $I_2$ , valdrán, respectivamente:

$$I_{1} = I_{D1} + I_{D3} = \mu_{1} \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{C1} - V_{3} - V_{T}) \cdot (V_{1} - V_{3}) - \frac{(V_{1} - V_{3})^{2}}{2} \right] +$$

$$+ \mu_{3} \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{C2} - V_{3} - V_{T}) \cdot (V_{2} - V_{3}) - \frac{(V_{2} - V_{3})^{2}}{2} \right]$$

$$I_{2} = I_{D2} + I_{D4} = \mu_{2} \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{C2} - V_{4} - V_{T}) \cdot (V_{1} - V_{4}) - \frac{(V_{1} - V_{4})^{2}}{2} \right] +$$

$$+ \mu_{4} \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (V_{C1} - V_{4} - V_{T}) \cdot (V_{2} - V_{4}) - \frac{(V_{2} - V_{4})^{2}}{2} \right]$$

$$(3-50.b)$$

Tomando de nuevo la diferencia de ambas corrientes, y teniendo en cuenta que las movilidades de los transistores  $M_1$  y  $M_4$  (figura 3.7) son iguales ( $\mu_1=\mu_4$ ), así como las de los transistores  $M_2$  y  $M_3$  ( $\mu_2=\mu_3$ ), pues se les supone idéntico potencial de substrato y de puerta, y que las tensiones de los dos terminales de salida del MRC son iguales ( $V_3=V_4=V$ ) se tendrá:

$$I_{1} - I_{2} = (V_{1} - V_{2}) \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (\mu_{1}V_{C1} - \mu_{2}V_{C2}) + (\mu_{2} - \mu_{1}) \cdot \left( V_{T} + \frac{V_{1} + V_{2}}{2} \right) \right]$$

(3-51)

A partir de esta expresión, se puede apreciar que existe un término lineal, función de las tensiones de control  $V_{C1}$  y  $V_{C2}$ , pero independiente de los voltajes de entrada  $V_1$  y  $V_2$ :

$$(I_1 - I_2)_L = (V_1 - V_2) \cdot C_{OX} \cdot \frac{W}{L} \cdot [(\mu_1 V_{C1} - \mu_2 V_{C2}) + (\mu_2 - \mu_1) \cdot V_T]$$

(3-52)

y un segundo término no lineal, función de la semisuma de las tensiones de entrada:

$$(I_1 - I_2)_{NL} = (V_1 - V_2) \cdot C_{OX} \cdot \frac{W}{L} \cdot \left[ (\mu_2 - \mu_1) \cdot \left( \frac{V_1 + V_2}{2} \right) \right]$$

(3-53)

lo que permite proponer un modelo más completo que el dado por la ecuación (3-42) y figura 3.7.b. Este modelo propuesto incluye dos resistencias lineales iguales (de valores  $R_{dL}$ ), y otras dos no lineales (de valores  $R_{dNL}$ ) conectadas en paralelo con las primeras, y dependientes de la tensión en modo común de las entradas. Las expresiones para estas resistencias son, a partir de la ecuación (3-51):

$$R_{dL} = \frac{1}{C_{OX} \cdot \frac{W}{L} \cdot \left[ (\mu_{1}V_{C1} - \mu_{2}V_{C2}) + (\mu_{2} - \mu_{1}) \cdot V_{T} \right]}$$

$$R_{dNL} = \frac{1}{C_{OX} \cdot \frac{W}{L} \cdot \left[ (\mu_{2} - \mu_{1}) \cdot \left( \frac{V_{1} + V_{2}}{2} \right) \right]}$$

$$(3-54)$$

$$V_{1} \circ V_{3}$$

$$R_{dNL} \circ V_{3}$$

$$R_{dNL} \circ V_{4} = V_{3}$$

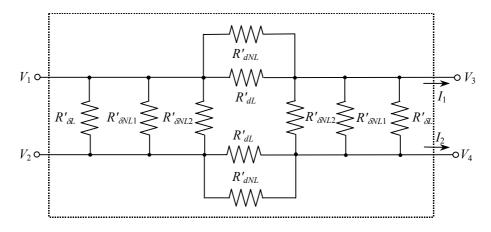

**Fig. 3.10.-** Modelo no lineal propuesto para el MRC que tiene en cuenta la degradación de la movilidad de los portadores con la tensión de puerta aplicada.

Las expresiones previas pueden ser simplificadas si se asume (de forma similar a como se ha realizado en (3-45)) que en la mayoría de los casos  $\theta \approx 0.03V^{-1}$  y  $(V_G - V_B - V_T) < 4 V$ . De este modo, la movilidad puede ser expresada como:

$$\mu_i \approx \frac{\mu_O}{1 + \theta \cdot (V_{Ci} - V_B - V_T)} \cong \mu_O \cdot [1 - \theta \cdot (V_{Ci} - V_B - V_T)] \qquad \text{con} \qquad i = \{1, 2\}$$

(3-56)

y por tanto las expresiones (3-54) y (3-55) para las resistencias en el modelo propuesto se reducen a:

$$R_{dL} = \frac{1}{C_{OX} \cdot \frac{W}{L} \cdot \mu_{O} \cdot (V_{C1} - V_{C2}) \cdot \left[1 - \theta \cdot (V_{C1} + V_{C2} - 2 \cdot V_{T}) \cdot V_{T}\right]}$$

$$R_{dNL} = \frac{1}{C_{OX} \cdot \frac{W}{L} \cdot \mu_{O} \cdot \theta \cdot (V_{C1} - V_{C2}) \cdot \left(\frac{V_{1} + V_{2}}{2}\right)}$$

(3-57)

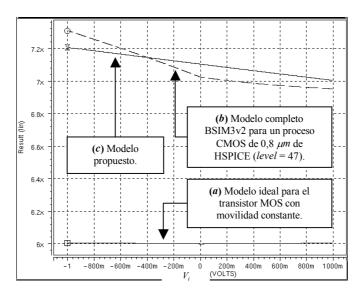

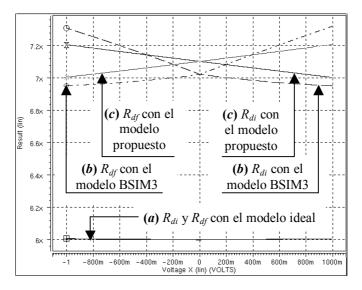

Los resultados de simulación del modelo propuesto con las mismas condiciones de la figura 3.8 se representan en la figura 3.11 (línea continua superior). La línea continua inferior representa la resistencia  $R_{di}$  considerando un modelo ideal con movilidad constante, y la línea discontinua es el resultado de simulación con el modelo BSIM3 completo. Puede observarse que el modelo propuesto tiene en cuenta la diferencia predicha por BSIM respecto al modelo ideal pero sin perder la simetría propia del transistor MOSFET (y por tanto de la célula MRC). La diferencia entre el modelo simétrico propuesto y el modelo BSIM3 es menor del 2%.

**Fig. 3.11.-** Resultados de simulación mediante HSPICE<sup>®</sup> de la resistencia diferencial del MRC de entrada del amplificador de la figura 3.8 mediante (*a*) un modelo para el transistor MOS con movilidad constante (línea continua inferior), (*b*) con el modelo BSIM3v2 (*level* 47) (línea discontinua) y (*c*) con el modelo propuesto simplificado (línea continua superior).

Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en V, donde  $V_i = V_1-V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos terminales de entrada la MRC.

La figura 3.12 representa los resultados de simulación obtenidos para las resistencias equivalente  $R_{di}$  y  $R_{df}$  de los MRCs de entrada y realimentación, respectivamente, del amplificador mostrado en la figura 3.8 en función de la tensión de entrada  $V_i$  (= $V_1$ - $V_2$ ). Como se predijo, en ambos casos existe una dependencia de la

resistencia respecto de la tensión en modo común aplicada ( $V_i$ /2 para  $R_{di}$  y  $V_O$ /2 para  $R_{df}$ ) que implicará una característica no lineal para el amplificador global (en un subapartado posterior se estudiarán las implicaciones de este fenómeno con más detalle y como puede, si no anularse, al menos sí minimizarse mediante técnicas circuitales).

**Fig. 3.12.-** Resultados de simulación mediante HSPICE<sup>®</sup> de las resistencias diferenciales de los dos MRCs del amplificador de la figura 3.8 mediante (a) un modelo para el transistor MOS con movilidad constante (líneas continuas inferiores), (b) con el modelo BSIM3v2 (*level* 47) (líneas discontinuas) y (c) con el modelo propuesto simplificado (líneas continuas superiores).

Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en V, donde  $V_i = V_1-V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos terminales de entrada la MRC.

#### 3.5.4.- Simulación del MRC con el modelo 'EKV'.

Para obtener unos resultados de simulación más precisos del transistor MOS y, por extensión, de la célula MRC, capaces de tener en cuenta la simetría inherente a ambos elementos y el efecto sobre el comportamiento del transistor de la movilidad de los portadores, se propone el uso del modelo EKV para el transistor MOS, presentado por C. C. Enz, F. Krummenacher y E. A. Vittoz en 1995 [ENZ95]. Éste es un modelo de simulación pensado especialmente para diseños analógicos *low-voltage* y *low-current*, basado en propiedades físicas fundamentales de la estructura MOS que explota la inherente simetría del dispositivo. Tiene la ventaja de ser perfectamente válido para todas las regiones de operación del MOSFET (corte, saturación y óhmica) y modela correctamente el dispositivo tanto en inversión débil, moderada como fuerte.

En el modelo EKV la variación de la movilidad es simétrica respecto a los terminales de drenador y surtidor ya que su expresión sólo depende de la tensión puertasubstrato, a través de la llamada tensión de  $pinch-off(V_P)$  definida en el propio modelo [ENZ95]. Esta tensión podría ser interpretada como una tensión "efectiva" de puerta, y cuyo valor aproximado es:

$$V_P \approx \frac{V_G - V_{TO}}{n} \tag{3-59}$$

donde  $V_{TO}$  es la tensión umbral, y n es el llamado  $slope\ factor$  (factor de pendiente de la característica  $V_G\ versus\ V_P$ ), dado por:

$$n = \frac{dV_G}{dV_P} = 1 + \frac{\gamma}{2 \cdot \sqrt{\psi_0 + V_P}}$$

(3-60)

donde a su vez  $\psi_0$  es el potencial electroestático en la superficie del transistor en fuerte inversión y en equilibrio, y  $\gamma$  un parámetro del modelo. Una expresión simple en dicho modelo que modeliza la reducción en la movilidad  $\beta$  es la mostrada en (3-61), donde KP y  $\theta$  son parámetros del modelo y  $W_{eff}$  y  $L_{eq}$  están relacionados con la geometría del MOS [ENZ95]:

$$\beta = KP \cdot \frac{W_{eff}}{L_{eq}} \frac{1}{1 + \theta \cdot V_P}$$

(3-61)

Si cada transistor de la figura 3.7.*a* se describe con el modelo EKV en la región activa dado por:

$$I_D = n \cdot \beta \cdot \left(V_P - \frac{(V_D + V_S)}{2}\right) \cdot (V_D - V_S)$$

(3-62)

donde todas las tensiones están referidas a la tensión de substrato, y asumiendo (en primera aproximación) que tanto la movilidad ( $\beta$ ) como el *slope factor* son constantes, el valor de las dos resistencias idénticas que implementan el modelo básico del MRC de la figura 3.7.b es:

$$R_{di} = \frac{V_1 - V_2}{I_1 - I_2} = \frac{1}{n \cdot \beta \cdot (V_{P1} - V_{P2})}$$

(3-63)

donde  $V_{P1}$  y  $V_{P2}$  son función de las tensiones de control  $V_{C1}$  y  $V_{C2}$  de la figura 3.7.a, respectivamente. Es fácil comprobar que esta expresión ideal para el MRC coincide con la ecuación (3-42), excepto en el nombre de los parámetros del modelo. Sin embargo, cuando se considera la dependencia de la movilidad y el *slope factor* con la tensión de *pinch-off*, la expresión ideal de la resistencia dada en la ecuación (3-63) es reemplazada por la siguiente:

$$R_{di} = \frac{1}{\left[ (n_1 \cdot \beta_1 \cdot V_{P1}) - (n_2 \cdot \beta_2 \cdot V_{P2}) + (n_2 \cdot \beta_2 - n_1 \cdot \beta_1) \cdot \left( \frac{V_1 + V_2}{2} \right) \right]}$$

(3-64)

donde:

$$\beta_{i} = KP \cdot \frac{W_{eff}}{L_{eq}} \frac{1}{1 + \theta \cdot V_{Pi}} \bigg|_{i=1,2} \qquad n_{i} = 1 + \frac{\gamma}{2 \cdot \sqrt{V_{Pi} + \psi_{0}}} \bigg|_{i=1,2}$$

(3-65)

son las movilidades y el *slope factor*, respectivamente, para los transistores 1 y 4 (para i=1) ó 2 y 3 (para i=2). La expresión propuesta en (3-64) no sólo tiene en cuenta la diferencia entre los valores ideal y real de la resistencia implementada con un MRC, sino también el comportamiento no lineal introducido por la dependencia del *slope*

factor y la movilidad de los portadores con la tensión de puerta. Puede observase además que si tanto el slope factor como la movilidad se suponen constantes  $(n_1 \cdot \beta_1 = n_2 \cdot \beta_2 = n \cdot \beta)$ , se recupera el valor ideal dado en la ecuación (3-63). Por otra parte, de (3-64) se deduce que la no linealidad puede anularse si se utiliza un circuito balanceado que imponga a la entrada  $V_1 = V_2$ , como se verá a continuación.

En la expresión (3-64) puede descomponerse el denominador en dos partes claramente diferenciadas. La primera estaría compuesta por los dos primeros sumandos de dicho denominador, y la segunda estaría formada por el tercero de ellos. A partir de dicha descomposición, se ve que el par de resistencias diferenciales implementadas por el MRC puede asemejarse al paralelo de dos nuevas resistencias: una, que se denominará  $R_{dL}$ , que representará al término lineal, dada por:

$$R_{dL} = \frac{1}{(n_1 \cdot \beta_1 \cdot V_{P1}) - (n_2 \cdot \beta_2 \cdot V_{P2})}$$

(3-66)

y una segunda,  $R_{dNL}$ , que representará a un término no lineal, ya que depende de la tensión de modo común de las entradas  $V_1$  y  $V_2$  (figura 3.7.*a*), expresada mediante:

$$R_{dNL} = \frac{1}{(n_2 \cdot \beta_2 - n_1 \cdot \beta_1) \cdot \left(\frac{V_1 + V_2}{2}\right)}$$

(3-67)

y cuyo modelo circuital sería el propuesto en la figura 3.10.

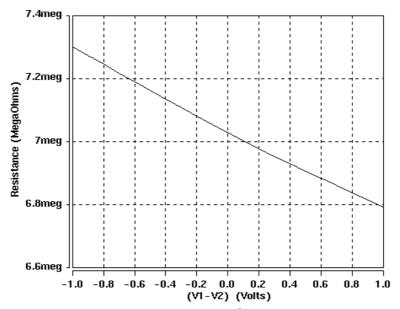

En la figura 3.13 se presenta una simulación de la resistencia diferencial  $R_{di}$  del MRC de entrada al amplificador inversor estudiado previamente (figura 3.8) en función de la tensión de entrada ( $V_i$ ). La simulación en este caso está realizada con SABER® debido a que para este simulador se dispone del modelo EKV, no disponible para HSPICE® en el momento de hacer estas pruebas. El valor resistivo predicho por el modelo EKV muestra la misma dependencia (y a la misma altura) con la tensión diferencial de entrada (eje x) que se observó con el modelo BSIM, (y que no aparece descrita en absoluto en la expresión ideal dada por (3.42)). Sin embargo, la diferencia más importante entre ambos modelos se haya en la relación entre el valor de la resistencia y la tensión diferencial de entrada al MRC, siendo la pendiente de la resistencia obtenida con el modelo EKV independiente de la polaridad de la tensión de entrada. Así, se aprecia que desaparece la discontinuidad de la curva que se observaba en la figura 3.11 (con el modelo BSIM) en el punto de 0 V del eje de abcisas.

De este estudio se extrae como conclusión la significativa mejora que presenta la utilización del modelo EKV respecto del BSIM para simulación de circuitería analógica de forma precisa.

Fig. 3.13.- Resultados obtenidos de simulación con SABER<sup>®</sup> de la resistencia diferencial  $R_{di}$  del MRC de entrada de la etapa amplificadora inversora de la figura 3.8 realizados con el modelo EKV para los transistores MOS.

$KP = 58 \text{ mA/V}^2$ ,  $q = 0.057 \text{ V}^{-1}$ . Relación de aspecto: W/L = 2/300. Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en V, donde  $V_i = V_1-V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos terminales de entrada la MRC.

#### 3.6.- MODELO NO LINEAL COMPLETO PARA EL 'MRC'.

Ya se ha comentado anteriormente que para conseguir que los dos terminales de salida del MRC estén a la misma tensión, éstos suelen conectarse en la mayoría de aplicaciones a las entradas de un amplificador operacional trabajando en su zona lineal. Por lo tanto, otra consideración importante al realizar el estudio detallado del MRC es la relacionada con la ganancia de tensión no infinita y dependiente de la frecuencia que en la práctica tendrá dicho amplificador operacional. Como el requerimiento de un cortocircuito virtual ideal entre los dos terminales de entrada del amplificador operacional no se puede conseguir en la práctica con amplificadores operacionales reales, las características presentadas por los circuitos prácticos que contienen MRCs con sus salidas conectadas a AO no ideales son peores de lo esperado en el modelo teórico, con lo cual el modelo sencillo de dos resistores presentado en la figura 3.7.b tampoco puede dar explicación a esta diferencia. En este apartado se estudiarán los efectos acarreados al considerar este caso, así como sus implicaciones, con lo que se podrá completar el modelo no lineal del MRC.

En [OSA98a] y [OSA99] se realiza el análisis de los efectos derivados de la no perfecta igualdad de las tensiones en los nodos de salida del MRC, presentando un modelo que explica el comportamiento del MRC bajo estas circunstancias.

Supóngase el MRC de la figura 3.7.a, pero sin que en el mismo se cumpla la igualdad  $V_3=V_4$ , donde  $V_3$  y  $V_4$  son las tensiones de los terminales superior e inferior, respectivamente, de salida del MRC. En estas condiciones, y tomando la ecuación (3-35) para describir el comportamiento del MOSFET en su zona óhmica (considerando un factor  $\mu_O$  de movilidad constante), la corriente diferencial de salida ( $I_1-I_2$ ) es:

$$I_{1} - I_{2} = (V_{1} - V_{2}) \cdot \mu_{O} \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{C1} - V_{C2}) - \mu_{O} \cdot C_{OX} \cdot \frac{W}{L} \cdot [V_{C1} + V_{C2} - 2 \cdot V_{T} - V_{3} - V_{4}] \cdot (V_{3} - V_{4})$$

$$(3-68)$$

donde el primer término es el que se asocia con la resistencia ideal del MRC (ecuación (3-42)). De la anterior expresión, en [OSA98a] y [OSA99] se llega a obtener un modelo no lineal del MRC que refleja el comportamiento ante diferencias en las tensiones de los dos terminales de salida de la célula (figura 3.14).

Fig. 3.14.- Nuevo modelo propuesto del MRC con cuatro resistores propuesto en [OSA98a].

donde las dos resistencias no lineales  $R_{\delta}$  conectadas cada una de ellas entre los terminales de entrada y salida del modelo propuesto son iguales y de valor:

$$R_{\delta} = \frac{1}{K' \cdot \frac{W}{L} \cdot \left[ V_{C2} - V_T - \frac{1}{2} \cdot \left( V_3 + V_4 \right) \right]}$$

(3-69)

y consideran las "pérdidas" en la corriente diferencial del puerto de salida del MRC debido a la desigualdad en las tensiones  $V_3$  y  $V_4$  de los nodos de salida de la célula.

Debería notarse que esta última expresión corresponde exactamente a la resistencia drenador-surtidor presentada por cualquiera de los dos transistores MOS con la puerta conectada a la tensión  $V_{C2}$  y que la no linealidad de  $R_{\delta}$  depende de la tensión en modo común del puerto de salida del MRC; es decir, del término  $(V_3 + V_4)/2$ .

Se ve inmediatamente que si las tensiones de salida del MRC de la figura 3.7.a cumplen:  $V_3=V_4$ , y los nodos de entrada  $V_1$  y  $V_2$  están conectados a fuentes de tensión ideales (es decir, con impedancias de salida nulas), el nuevo modelo se simplifica hasta el modelo clásico de dos resistores, puesto que las resistencias  $R_\delta$  se pueden eliminar del circuito.

En el subapartado siguiente se hallará un modelo del MRC que incluya tanto los efectos estudiados en [OSA98a], como los tratados en los párrafos precedentes de la presente tesis sobre el comportamiento no lineal debido a la dependencia de la movilidad de los portadores con el campo magnético transversal del transistor MOS.

#### 3.6.1.- Análisis a Través del Modelo 'EKV'.

Cuando la característica tensión-corriente de cada uno de los transistores MOSFET del MRC se modela mediante la expresión (3-62) propuesta en el modelo EKV, y se considera que tanto la movilidad como el *slope factor* dependen de la tensión de *pinch-off*, la corriente diferencial de salida de la célula cuando no se cumple la igualdad  $V_3$ = $V_4$  puede expresarse como:

$$I_{1} - I_{2} = \left[ \left( n_{1} \cdot \beta_{1} \cdot V_{P1} \right) - \left( n_{2} \cdot \beta_{2} \cdot V_{P2} \right) + \left( n_{2} \cdot \beta_{2} - n_{1} \cdot \beta_{1} \right) \cdot \left( \frac{V_{1} + V_{2}}{2} \right) \right] \cdot \left( V_{1} - V_{2} \right) - \left[ \left( n_{1} \cdot \beta_{1} \cdot V_{P1} \right) + \left( n_{2} \cdot \beta_{2} \cdot V_{P2} \right) - \left( n_{2} \cdot \beta_{2} - n_{1} \cdot \beta_{1} \right) \cdot \left( \frac{V_{3} + V_{4}}{2} \right) \right] \cdot \left( V_{3} - V_{4} \right)$$

$$(3-70)$$

A pesar de la complejidad que pueda entrañar esta expresión como modelo del MRC, puede desgranarse en dos términos de forma que se identifiquen un modelo con dos resistencias similar al de la figura 3.14. Estas dos resistencias ( $R'_{di}$  y  $R'_{\delta}$  en la figura 3.15) tendrán en cuenta el efecto de movilidad no constante considerado. Sus valores, a partir de (3-70) serán:

**Fig. 3.15.-** Nuevo modelo propuesto del MRC con cuatro resistores a partir del modelo EKV para los transistores MOS.

La resistencia  $R'_{di}$  dada en (3-71) (e idéntica a la  $R_{di}$  obtenida en (3-64)) puede ser dividida en dos componentes, asemejándose el comportamiento a la conexión en paralelo de dos resistencias,  $R'_{dL}$  (= $R_{dL}$ ) y  $R'_{dNL}$  (= $R_{dNL}$ ), cuyos valores coinciden con los de las expresiones (3-66) y (3-67), respectivamente.

Por otro lado, cuando se observa la expresión (3-72), se aprecia que existen tres contribuciones diferentes:

▶ Un término lineal que depende de la tensión de control  $V_{C2}$  (a través de la tensión de *pinch-off*  $V_{P2}$ ). Esta contribución puede modelarse por una resistencia de valor  $R'_{\delta L}$ , fijada por  $V_{C2}$  y dada por:

$$R'_{\delta L} = \frac{1}{\left(n_2 \cdot \beta_2 \cdot V_{P2}\right)} \tag{3-73}$$

➤ Un primer término no lineal existente debido a la dependencia de la movilidad de portadores con el campo transversal aplicado, y función de la tensión de modo común de las entradas (que podrá ser cancelado mediante la utilización de circuitos completamente balanceados). Esta contribución puede a su vez modelarse por una resistencia no lineal (R'oNLI) dada por:

$$R'_{\delta NL1} = \frac{1}{\left[ \left( \frac{n_2 \cdot \beta_2 - n_1 \cdot \beta_1}{2} \right) \cdot \left( \frac{V_1 + V_2}{2} \right) \right]}$$

(3-74)

Un segundo término no lineal, que depende de la tensión de modo común de los terminales de salida, y modelado por una tercera resistencia  $R'_{\delta NL2}$ :

$$R'_{\delta NL2} = \frac{1}{\left[ \left( \frac{n_1 \cdot \beta_1 + n_2 \cdot \beta_2}{2} \right) \cdot \left( \frac{V_3 + V_4}{2} \right) \right]}$$

(3-75)

Como el valor de esta última resistencia depende de la inversa del valor medio entre  $(n_1 \cdot \beta_1)$  y  $(n_2 \cdot \beta_2)$ , mientras que el de la resistencia  $R'_{dNL1}$  depende de la inversa de su diferencia  $(n_2 \cdot \beta_2 - n_1 \cdot \beta_1)$ , es fácil concluir que el valor de  $R'_{dNL1}$  será mayor que el de  $R'_{dNL2}$ .

A partir de todas estas contribuciones, el modelo no lineal completo del MRC quedaría como muestra la figura 3.16:

Fig. 3.16.- Modelo no lineal completo del MRC.

Es importante hacer notar en las expresiones (3-71) y (3-72) que si se asume una movilidad constante para los transistores, el factor  $(n_1 \cdot \beta_1)$  será igual a  $(n_2 \cdot \beta_2)$ , con lo que

el término asociado a la tensión de modo común de las entradas se anula en ambas ecuaciones, obteniendo expresiones similares a las iniciales dadas en (3-42) y (3-69), respectivamente. Finalmente, si se hace  $V_3 = V_4$ , el segundo término en la expresión (3-70) desaparece y, por tanto, no habrá contribución alguna de las resistencias  $R'_{\delta}$ , con lo que el MRC quedará modelado solamente con  $R'_{dL}$  y  $R'_{dNL}$ , tal y como se tenía en la figura 3.10.

#### 3.6.2.- <u>Efecto de la Tensión de Modo Común sobre el Comporta-</u> miento del MRC.

En los puntos precedentes se ha deducido que cada una de las dos resistencias diferenciales  $(R_{di})$  del modelo simple de un MRC (figura 3.7.b) se podía descomponer en dos resistencias (una lineal,  $R_{dL}$ , y otra no lineal,  $R_{dNL}$ ) modeladas mediante las expresiones (3-66) y (3-67), respectivamente, siempre y cuando se consiga cumplir la igualdad  $V_3=V_4$ . La componente no lineal presentaba una dependencia clara de la tensión en modo común de las dos entradas a la célula MRC (semisuma de las tensiones  $V_1$  y  $V_2$  de la figura 3.7). En este apartado se hará hincapié en las implicaciones de dicha dependencia. Para ello, se supondrá un par de amplificadores compuestos por dos células MRC y un amplificador operacional tal y como muestra la figura 3.17. La forma de garantizar que no existe contribución de la resistencia  $R'_{\delta}$  no ideal del modelo propuesto para este análisis es mediante la utilización de sendos amplificadores operacionales ideales en la simulación (con ganancia en lazo abierto muy elevada y no dependiente de la frecuencia), que aseguren plenamente la condición  $V_3=V_4$ . Ambos amplificadores serán idénticos, salvo que el de la figura 3.17.a es no balanceado (singleended), mientras que el segundo (figura 3.17.b) es completamente balanceado (fully balanced).

**Fig. 3.17.-** Amplificadores de tensión compuestos por un amplificador operacional y MRCs. (a) Amplificador no balanceado (*single-ended*). (b) Amplificador completamente balanceado (*fully balanced*).

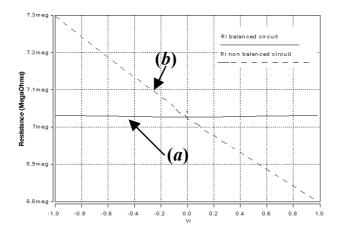

La gráfica de la figura 3.18 muestra una simulación representativa de la resistencia diferencial de entrada  $R_i$  implementada por los MRCs de entrada de ambos amplificadores en función de la tensión de entrada  $V_i$  (= $V_1$ - $V_2$ ) aplicada a ellos. El simulador utilizado es SABER<sup>®</sup> con parámetros tecnológicos del modelo EKV para los transistores y una relación de aspecto W/L = 2/300.

**Fig. 3.18.-** Resistencia diferencial  $R_i$  implementada con el MRC de entrada de los amplificadores de la figura 3.17. (a) Para el circuito balanceado (*fully balanced*). (b) Para el circuito no balanceado (*single-ended*).  $KP = 58 \ mA/V^2$ ,  $q = 0.057 \ V^{-1}$ . Relación de aspecto: W/L = 2/300. Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en  $V_i$  donde  $V_i = V_1-V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos

terminales de entrada la MRC.

En esta figura se puede apreciar que cuando la tensión en modo común a la

entrada del MRC permanece nula (es decir, cuando la semisuma o promedio de las tensiones en los dos terminales de entrada al MRC es cero), como es el caso del circuito completamente balanceado de la figura 3.17.b, la resistencia diferencial implementada por la célula es prácticamente independiente de la tensión de entrada  $V_i$  (línea continua), con un valor  $R_i=R_{dL}=7,03$   $M\Omega$ . Por el contrario, cuando el amplificador es no balanceado (caso del circuito de la figura 3.17.a), la tensión en modo común a la entrada del MRC (que en este caso siempre será diferente de cero para cualquier valor de  $V_i$  no nulo) hace que  $R_i$  presente una fuerte dependencia respecto  $V_i$  (línea discontinua), debida a la contribución de  $R_{dNL}$ . Esta contribución se suma o se resta al valor de  $R_{dL}$  dependiendo, obviamente, de la polaridad de la tensión de modo común de las entradas. Conviene recordar que, al igual que sucedía en las características de las respectivas figuras 3.9, 3.11 y 3.12, el valor de este MRC predicho por la ecuación ideal mostrada en (3-42), donde no se tiene en cuenta los efectos provocados por la movilidad y factor de pendiente no constantes, es de 6  $M\Omega$ , inferior a los valores presentados en esta gráfica.

En esta simulación, para un margen de la tensión de entrada  $V_i$  de  $\pm 1V$ , la variación relativa de la resistencia diferencial es mayor del 7%. Por tanto, a partir de lo expuesto en este apartado, se puede concluir que puede minimizarse la distorsión debida a la movilidad no constante mediante el uso de circuitos balanceados (*fully balanced*) en la medida de lo posible. En cualquier caso, y con el fin de reducir la distorsión, el nivel de tensión de modo común a la entrada de una célula MRC ha de ser lo más pequeño posible.

# 3.6.3.- <u>Efecto de la Desigualdad de las Tensiones de Salida sobre el Comportamiento del MRC.</u>

Aun cuando se utilice la célula MRC en estructuras completamente balanceadas, en el caso en que  $V_3 \neq V_4$ , los efectos de la resistencia  $R'_{\delta}$  del modelo de la figura 3.15 no son en absoluto despreciables. La resistencia  $R'_{\delta}$  es no lineal, y depende de las tensiones en modo común tanto de los nodos de entrada como de los de salida.

La misma etapa inversora balanceada de la figura 3.17.b ha sido utilizada para obtener los resultados de simulación representados en la figura 3.19 que validan el modelo cuando  $V_3 \neq V_4$ . En este caso, utilizar la estructura balanceada permite garantizar que la dependencia de la resistencia diferencial  $R_i$  respecto al valor de la tensión de entrada es mínima. Debido a que se quiere estudiar el efecto de la tensión diferencial de los terminales de salida del MRC sobre el valor de  $R'_{\delta}$  (y por tanto sobre la resistencia diferencial  $R_i$  implementada por él), se han realizado dos simulaciones para valores muy diferentes de  $(V_3-V_4)$ . La línea continua corresponde a una simulación donde la ganancia en lazo abierto del amplificador operacional es elevada (106 dB), para asegurar de esta forma una mínima diferencia en su tensión diferencial de entrada  $(V_3-V_4)$  y, por tanto, una mínima contribución de  $R'_{\delta}$ . Por el contrario, la línea discontinua resulta de la simulación a partir de un amplificador operacional de mucha menor ganancia en lazo abierto (solamente 46 dB), donde claramente se aprecia una significativa diferencia en el valor de la resistencia diferencial  $R_i$  implementada con el MRC.

**Fig. 3.19.-** Comparación de la resistencia diferencial  $R_i$  implementada con el MRC de entrada del amplificador balanceado de la figura 3.17.b. (a) Cuando el amplificador operacional presenta una ganancia en lazo abierto de 46 dB. (b) Cuando el amplificador operacional presenta una ganancia en lazo abierto de 46 dB.

$KP = 58 \text{ mA/V}^2$ ,  $q = 0.057 \text{ V}^{-1}$ . Relación de aspecto: W/L = 2/300. Eje y:  $(V_i)/(I_1-I_2)$  en  $M\Omega$ . Eje x:  $V_i$  en  $V_i$  donde  $V_i = V_1 - V_2$ , siendo  $V_1$  y  $V_2$  las tensiones en los dos terminales de entrada la MRC.

#### 3.6.4.- <u>Conclusiones e Indicaciones para Minimizar los Efectos No</u> Lineales del MRC en la Práctica.

A partir de las expresiones y resultados de simulación hallados en los puntos precedentes, se puede cuantificar el comportamiento no lineal del MRC, determinando de esta forma un modelo no lineal preciso. Los fenómenos causantes de estos comportamientos no ideales son, principalmente:

- ➤ El asociado a la degradación de la movilidad de portadores debido al campo magnético transversal en los transistores MOSFET (reducción de la movilidad en el canal).

- ➤ El asociado a la desigualdad en las tensiones de los dos terminales de salida del MRC.

Teniendo en cuenta estos fenómenos y los diferentes aspectos estudiados en los apartados precedentes, algunas indicaciones o consejos genéricos para minimizar dichos efectos en los circuitos que utilicen células MRC son:

- ➤ Minimizar la distorsión debida a la movilidad no constante mediante circuitos balanceados (*fully-balanced*). En cualquier caso, para reducir la distorsión, el nivel de tensión común a la entrada del MRC ha de ser mantenido bajo cierto valor máximo.

- La ganancia mínima requerida para el amplificador operacional utilizado a la salida del MRC deber ser suficientemente grande como para minimizar los efectos no lineales provocados por desigualdad en las tensiones de los dos terminales de salida del dispositivo.

- ➤ Además, a la hora de simular diseños analógicos con buena precisión, se recomienda el uso del modelo EKV sobre el BSIM3, puesto que el primero describe de forma más adecuada el comportamiento simétrico del transistor MOSFET.

El análisis efectuado sobre la degradación de la movilidad debido al campo magnético transversal en los transistores MOS de la célula MRC (publicado en la referencia bibliográfica [VID99]) ha sido referenciado por R.L. Geiger et al. en [SCH01] como justificación de las diferencias existentes entre el comportamiento real y de simulación de la célula MRC. En este trabajo, Geiger et al. proponen una alternativa de transresistencia CMOS lineal a la célula MRC estudiada en este capítulo.

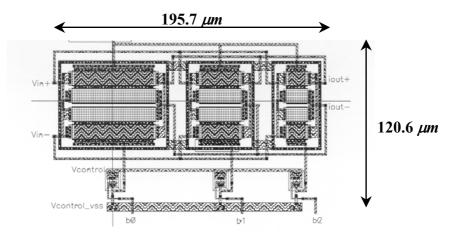

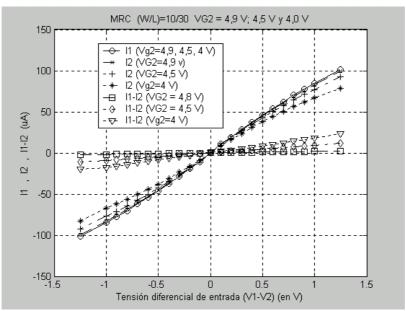

## 3.7.- <u>CARACTERIZACIÓN EXPERIMENTAL DE CÉLU-</u> LAS 'MRC'.