#### UNIVERSITAT POLITECNICA DE CATALUNYA

# Enhancing Timing Analysis for COTS Multicores for Safety-Related Industry: a Software Approach

by

Gabriel Alejandro Fernandez Diaz

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

$\begin{array}{c} \text{in the} \\ \text{Informatics Faculty} \\ \text{Computer Architecture Department} \end{array}$

September 2018

#### UNIVERSITAT POLITECNICA DE CATALUNYA

# Enhancing Timing Analysis for COTS Multicores for Safety-Related Industry: a Software Approach

by

Gabriel Alejandro Fernandez Diaz September 2018

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Informatics Faculty Computer Architecture Department

Advisor: Francisco J. Cazorla

Barcelona Supercomputing Center and IIIA-CSIC

Co-Advisor: Jaume Abella

Barcelona Supercomputing Center

## Declaration of Authorship

- I, Gabriel Fernandez, declare that this thesis titled, 'Enhancing Timing Analysis for COTS Multicores for Safety-Related Industry: a Software Approach' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signea: |  |  |  |

|---------|--|--|--|

|         |  |  |  |

|         |  |  |  |

| Date:   |  |  |  |

"I only know that I know nothing"

Socrates

#### Abstract

Artificial system interaction with the real environment is in general based on the deployment of properly coordinated sensors and actuators, establishing a "dynamic controlloop" between them. The time to close this control-loop characterizes the functionality and applicability to critical systems in response time. In the case of digital control, the performance of the processor is directly related to response time. In this line computational demands in many Critical Embedded System industries such as avionics, space, automotive and railway have experienced an unprecedented growth as a consequence of the need to cope with more sophisticated software functionalities. The use of highperformance hardware features in critical embedded systems, such as multicore architectures, to respond to those performance requirements, challenges the computation of tight worst case execution time (WCET) estimates. The source of this complexity comes from the interferences (contention) when accessing hardware resources shared across the different tasks running simultaneously. Several proposals advocate for hardware support to either eliminate or control inter-task conflicts on access to shared hardware resources (e.g. Time Division Multiple Access (TDMA) in buses, partitioning for caches), to simplify timing analysis via removing or controlling effect of contention. However, to the best of our knowledge, no current Commercial Off-The-Shelf (COTS) multicore processor provides complete isolation or full control of inter-task interference. As a consequence, the execution time of a software program may be inordinately affected by the load that its co-runners place on the hardware shared resources. This Thesis provides software methodologies to characterize and control the contention on COTS multicore processors so that they can be factored in measurement-based timing analysis. To that end, we make the following contributions. First, we perform a study of the vast state of the art on the topic and we propose a taxonomy to classify existing approaches with emphasis on their goals and assumptions. This helps better understanding the symbiosis and overlapping elements of the state-of-the-art works. Second, we propose a measurement-based methodology to derive the longest delay requests from a task can take accessing FIFO and round-robin arbitrated resources, which is fundamental to derive tasks' worst-case contention effects. Third, with the goal of deriving time composable WCET estimates, we introduce signatures and templates to abstract contention caused and incurred by tasks in a multicore. Fourth, we present a methodology to derive WCET estimates during early design stages, before tasks (software units) are integrated. And fifth, we report our experience with timing analysis on two COTS ARM-based multicores.

# Acknowledgements

The research leading to this thesis has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 644080(SA-FURE), the European Space Agency under Contract 789.2013 and NPI Contract 40001102880; and COST Action IC1202, Timing Analysis On Code-Level (TACLe)., and the Spanish Ministry of Science and Innovation under grant TIN2015-65316-P.

I would like to express my gratitude to my advisors Francisco J. Cazorla and Jaume Abella for their support, guidance and help. I would also like to acknowledge to Eduardo Quinones, Javier Jalle, Luca Fossati, Guillem Bernat, Marco Zulianello, Christine Rochange, Tullio Vardanega and Sylvain Girbal for their contribution to this thesis. Also I want to thanks to all my colleagues in the Barcelona Supercomputing Center, especially in the CAOS group for all this past years shared together.

# Contents

| D  | eclar | ation of A  | uthorship   | )         |        |        |       |            |    |       |       |       |   |        |

|----|-------|-------------|-------------|-----------|--------|--------|-------|------------|----|-------|-------|-------|---|--------|

| A  | bstra | ct          |             |           |        |        |       |            |    |       |       |       |   | ii     |

| A  | ckno  | wledgemer   | ıts         |           |        |        |       |            |    |       |       |       |   | iv     |

| Li | st of | Figures     |             |           |        |        |       |            |    |       |       |       |   | ix     |

| Li | st of | Tables      |             |           |        |        |       |            |    |       |       |       |   | X      |

| A  | bbre  | viations    |             |           |        |        |       |            |    |       |       |       |   | xi     |

| 1  | Intr  | oduction    |             |           |        |        |       |            |    |       |       |       |   | 1      |

|    | 1.1   | Requireme   | nts of Crit | ical Eml  | bedded | l Syst | ems   |            |    |       |       |       |   | <br>2  |

|    | 1.2   | Challenges  | in Timing   | g Analysi | is     |        |       |            |    |       |       |       |   | <br>4  |

|    | 1.3   | Contributi  | ons         |           |        |        |       |            |    |       |       |       |   | <br>6  |

|    | 1.4   | Structure   | of this The | esis      |        |        |       |            |    |       |       |       |   | <br>6  |

|    | 1.5   | List of Pul | olications. |           |        |        |       |            |    |       |       |       |   | <br>6  |

|    |       | 1.5.1 Rel   | ated public | cations   |        |        |       |            |    |       | <br>• |       |   | <br>11 |

| 2  | Exp   | erimental   | Framewo     | ork       |        |        |       |            |    |       |       |       |   | 12     |

|    | 2.1   | COTS Hai    |             |           |        |        |       |            |    |       |       |       |   | 12     |

|    |       | 2.1.1 The   | e LEON pr   | rocessor  |        |        |       |            |    |       |       |       |   | <br>13 |

|    |       | 2.1.2 The   | e LEON pl   | atforms   |        |        |       |            |    |       |       |       |   | <br>14 |

|    |       | 2.1.3 The   | e ARM big   | g.LITTL   | E arch | itectu | re .  |            |    |       |       |       |   | <br>15 |

|    |       |             | e ARM pla   |           |        |        |       |            |    |       |       |       |   | 16     |

|    | 2.2   | Simulation  | Insfrastru  | icture .  |        |        |       |            |    |       | <br>٠ |       |   | <br>17 |

|    | 2.3   | Benchmarl   | s Suites .  |           |        |        |       |            |    | <br>• | <br>٠ |       |   | <br>18 |

|    |       |             | MBC Auto    |           |        |        |       |            |    |       |       |       |   | 18     |

|    |       |             | diabench .  |           |        |        |       |            |    |       |       |       |   | 19     |

|    | 2.4   | Space App   |             |           |        |        |       |            |    |       |       |       |   |        |

|    | 2.5   | Resource S  | Stressing K | lernels   |        |        |       |            |    |       | <br>• | <br>• | • | <br>20 |

| 2  | ΛТ    | nyonomy     | of the W    | onka in   | the St | tata   | of th | ο <b>Λ</b> | nt |       |       |       |   | 20     |

*Contents* vi

|   | 3.1 |             | sible taxonomy of state-of-the-art techniques to analyse the timing               | 0.0 |

|---|-----|-------------|-----------------------------------------------------------------------------------|-----|

|   |     | -           | t of resource contention                                                          |     |

|   |     | 3.1.1       | 1,000                                                                             |     |

|   |     |             | 3.1.1.1 Timing analysis frameworks                                                |     |

|   |     |             | 3.1.1.2 Task scheduling and allocation                                            |     |

|   |     | 3.1.2       | WCET-centric techniques                                                           |     |

|   |     |             | 3.1.2.1 Joint analysis of concurrent tasks/threads                                |     |

|   |     |             | 3.1.2.2 Independent analysis of tasks/threads                                     |     |

|   |     | 3.1.3       | Architecture-centric techniques                                                   |     |

|   |     | 3.1.4       | COTS-based techniques                                                             |     |

|   | 3.2 | Other       | aspects of interest                                                               | 30  |

|   |     | 3.2.1       | Parallel applications                                                             |     |

|   |     | 3.2.2       | The probabilistic approach                                                        | 31  |

|   | 3.3 |             | ue                                                                                |     |

|   | 3.4 | Concl       | usions                                                                            | 34  |

| 4 | T   | <del></del> | n nolichility on Massaured UnnanDoured Delays(UDD)                                | 35  |

| 4 | 4.1 | _           | g reliability on Measured UpperBound Delays(UBD) ntion analysis for RoRo and FIFO |     |

|   | 4.1 | 4.1.1       | Studying the Bus and the Memory Controller                                        |     |

|   |     | 4.1.2       | Difficulties in Determining the ubd                                               |     |

|   | 4.2 |             | ents of the Proposed Solution                                                     |     |

|   | 1.2 | 4.2.1       | Resource Stressing Kernels                                                        |     |

|   | 4.3 |             | ynchrony Effect                                                                   |     |

|   | 1.0 | 4.3.1       | Synchrony Effect under FIFO                                                       |     |

|   |     | 4.3.2       | Synchrony Effect under RoRo                                                       |     |

|   | 4.4 |             | ing the UBD for the bus                                                           |     |

|   | 1.1 | 4.4.1       | Nop-based Methodology                                                             |     |

|   |     | 4.4.2       | bsk-nop for $FIFO$                                                                |     |

|   |     | 4.4.3       | bsk-nop for $RoRo$                                                                |     |

|   |     | 4.4.4       | Applying the rsk-nop method                                                       |     |

|   |     | 4.4.5       | Deriving $l_{bus}^{max}$                                                          |     |

|   |     | 4.4.6       | Multicycle nop operation                                                          |     |

|   |     | 4.4.7       | Summary                                                                           | 51  |

|   | 4.5 | UBD         | for the memory controller                                                         |     |

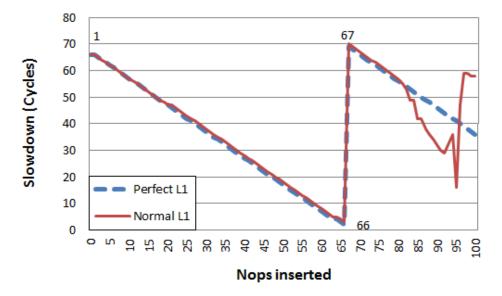

|   |     | 4.5.1       | msk-nop for FIFO                                                                  | 52  |

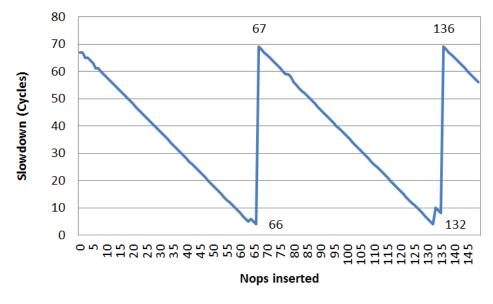

|   |     | 4.5.2       | msk-nop for RoRo                                                                  | 53  |

|   |     | 4.5.3       | Deriving $l_{mem}^{max}$                                                          | 53  |

|   |     | 4.5.4       | Memory refresh                                                                    | 54  |

|   | 4.6 | Evalua      | ation                                                                             | 55  |

|   |     | 4.6.1       | Experimental Setup                                                                | 55  |

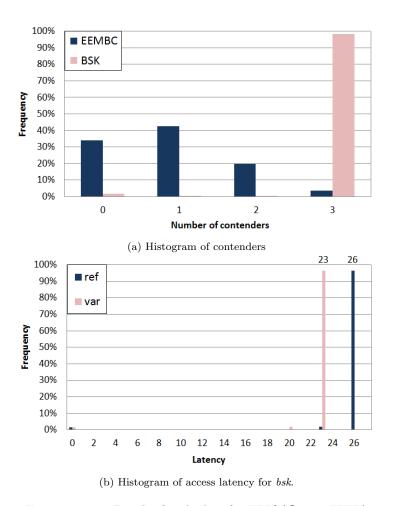

|   |     | 4.6.2       | Synchrony Effect on the Bus                                                       | 56  |

|   |     | 4.6.3       | Using store operations instead of loads                                           | 58  |

|   |     | 4.6.4       | Synchrony Effect on the Memory                                                    | 59  |

|   |     | 4.6.5       | Evaluation of bsk-nop methodology for the bus                                     | 60  |

|   |     | 4.6.6       | Evaluation of msk-nop methodology for the memory                                  | 61  |

|   |     | 4.6.7       | Summary                                                                           | 63  |

|   | 47  | Relate      | ed Work                                                                           | 64  |

*Contents* vii

|   | 4.8  | Conclusions                                                                | 65 |

|---|------|----------------------------------------------------------------------------|----|

| 5 | Abs  | stracting Multicore Contention Interference: Templates and Signa-          |    |

|   | ture | es                                                                         | 66 |

|   | 5.1  | Formalization of RUs and RUl                                               | 68 |

|   |      | 5.1.1 Resource Usage signature $(RUs)$                                     | 68 |

|   |      | 5.1.2 Resource Usage template $(RUl)$                                      | 69 |

|   |      | 5.1.3 Illustration of RUs and RUl use through an example                   | 70 |

|   | 5.2  | RUs & RUl for Measurement-Based Timing Analysis                            | 71 |

|   |      | g v                                                                        | 72 |

|   |      | 5.2.2 The case of a NGMP-like architecture                                 | 73 |

|   |      | 5.2.3 Bus                                                                  | 74 |

|   |      |                                                                            | 76 |

|   |      | ·                                                                          | 77 |

|   | 5.3  |                                                                            | 78 |

|   |      |                                                                            | 79 |

|   | 5.4  |                                                                            | 80 |

|   | 5.5  |                                                                            | 81 |

| 6 | Sur  | rogate Applications Generation                                             | 82 |

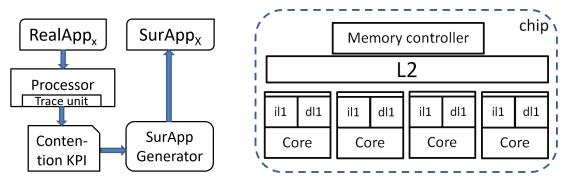

|   | 6.1  | Overall Approach and Target Platform                                       | 83 |

|   | 6.2  | Surrogate Applications                                                     | 85 |

|   |      | 6.2.1 Stack Distance as a Proxy for Multicore Contention                   | 85 |

|   |      | 6.2.2 Stack Distance per Kilo Instruction (sdki)                           | 86 |

|   | 6.3  | Surrogate Application Generator                                            | 87 |

|   | 6.4  | Experimental Evaluation                                                    | 90 |

|   |      | 6.4.1 Experimental setup                                                   | 90 |

|   |      | 6.4.2 Experimental Results                                                 | 92 |

|   | 6.5  | Related Works                                                              | 95 |

|   | 6.6  | Conclusions                                                                | 95 |

| 7 | The  | e ARM big.LITTLE architecture: the Juno Board and DragonBoard              |    |

|   | 7.1  | Goal and Scenario                                                          |    |

|   |      | Section 1997                                                               | 99 |

|   |      |                                                                            | 99 |

|   | 7.2  | Qualitative Analysis of the ARM big.LITTLE Architecture: Specifications 10 |    |

|   | 7.3  | Quantitative Analysis of the SnapDragon 810 Processor                      |    |

|   |      | 7.3.1 Microbenchmarks                                                      |    |

|   |      | 7.3.2 Disabling the Data Prefetcher                                        |    |

|   |      | 7.3.3 Assessing Microbenchmark Results                                     |    |

|   | 7.4  | Summary of Lessons Learned for the SnapDragon 810 Processor 10             |    |

|   | 7.5  | Quantitative Analysis of the Juno SoC                                      |    |

|   |      | 7.5.1 Experimental Setup                                                   |    |

|   |      | 7.5.2 Assessing Stressing Benchmark Results                                |    |

|   | 7.6  | Summary of Lessons Learned for the Juno SoC                                |    |

|   | 7.7  | ARM big.LITTLE Comparison                                                  |    |

|   | 7.8  | Final Remarks on ARM big.LITTLE Architectures                              | 13 |

| Contents   | viii |

|------------|------|

| 0011161113 | VIII |

| 8  |       | nclusions and Future Work |       |       |  |   |  |   |       |   |       | 115   |   |

|----|-------|---------------------------|-------|-------|--|---|--|---|-------|---|-------|-------|---|

|    |       | Summary of Contributions  |       |       |  |   |  |   |       |   |       |       |   |

|    | 8.2   | Future Work               | <br>• | <br>• |  | • |  | • | <br>• | • | <br>• | . 117 | , |

|    |       |                           |       |       |  |   |  |   |       |   |       |       |   |

|    |       |                           |       |       |  |   |  |   |       |   |       |       |   |

| Bi | bliog | graphy                    |       |       |  |   |  |   |       |   |       | 119   | ) |

# List of Figures

| 1.1  | Challenges identified for future critical embedded systems and main proposals of this Thesis                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1  | Block diagram of the GR712RC implementation of the LEON3 architecture used in this study                                                                                                                                |

| 2.2  | Block diagram of the ML510 implementation of the LEON4 architecture used in this study                                                                                                                                  |

| 2.3  | Schematic view of the elements of the SnapDragon 810 processor 10                                                                                                                                                       |

| 2.4  | Schematic view of the elements of the Juno SoC processor                                                                                                                                                                |

| 4.1  | Pseudo-code of $rsk$ for the bus made with load operations (©2016 IEEE) 39                                                                                                                                              |

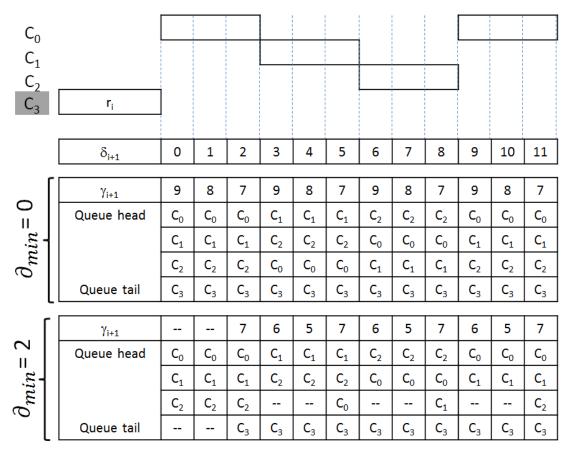

| 4.2  | Contention delay $\gamma$ as a function of $\delta$ (FIFO) for $\delta_{min} = 0$ and $\delta_{min} = 2$ , respectively. In each cycle priorities are those at the start of the cycle, prior to arbitration(©2016 IEEE) |

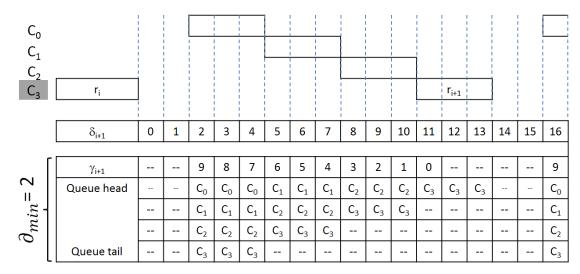

| 4.3  | Example where contention delay $\gamma$ is maximized for FIFO(©2016 IEEE) 4                                                                                                                                             |

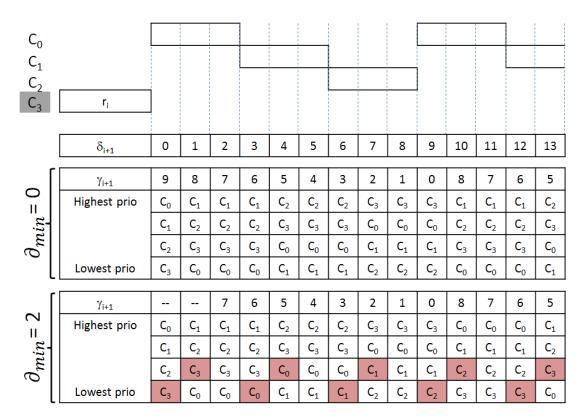

| 4.4  | Contention delay $\gamma$ as a function of $\delta$ (RoRo). In each cycle priorities are those                                                                                                                          |

| 1.1  | at the start of the cycle, prior to arbitration. Shaded cells in the priority rows                                                                                                                                      |

|      | correspond to requests not in the queue(©2016 IEEE)                                                                                                                                                                     |

| 4.5  | Code of $rsk_{nop}$ implementations: bsk-nop and msk-nop(©2016 IEEE) 40                                                                                                                                                 |

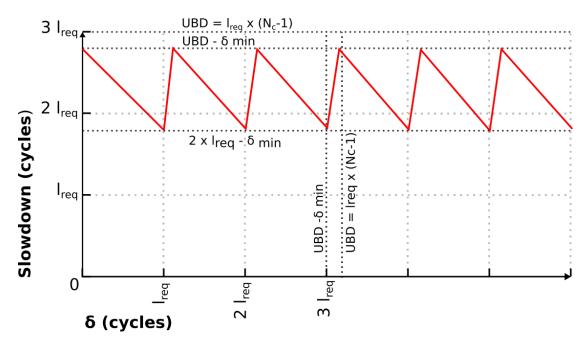

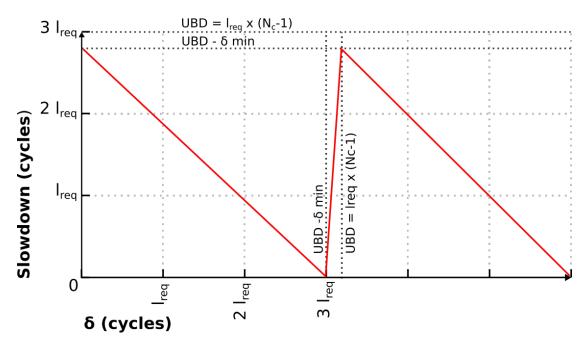

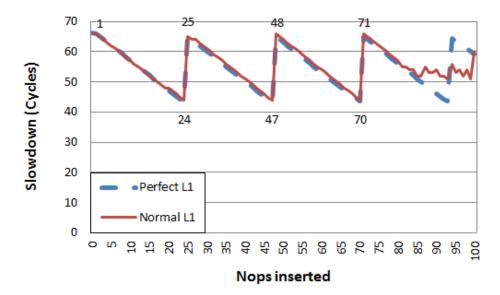

| 4.6  | Saw-tooth behavior for FIFO with $\delta_{min} = 1 (©2016 \text{ IEEE})$                                                                                                                                                |

| 4.7  | Timeline of the FIFO scenario for different $k$ nop instructions: a) $k=0$ , b) $k=1$ , c) $k=2(@2016 \text{ IEEE})$                                                                                                    |

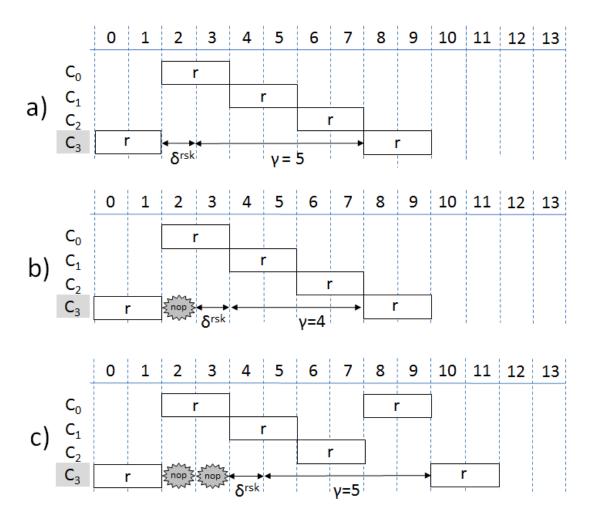

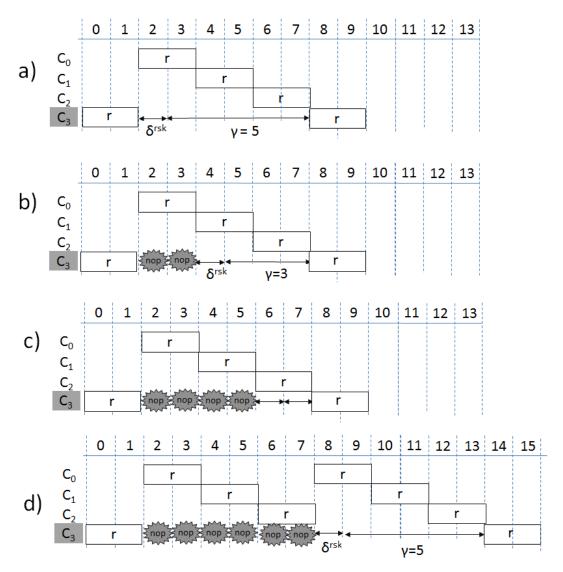

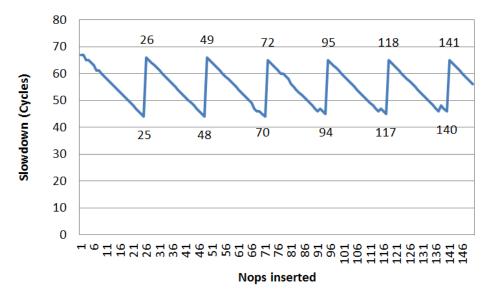

| 4.8  | Saw-tooth behavior for $RoRo$ with $\delta_{min} = 1 (©2016 \text{ IEEE}) $                                                                                                                                             |

| 4.9  | Timeline of the <i>RORO</i> scenario for different $k$ nop instructions: a) $k = 0$ , b) $k = 2$ , c) $k = 4$ , d) $k = 6 (©2016 \text{ IEEE})$                                                                         |

| 4.10 | Results for the bus for FIFO(©2016 IEEE)                                                                                                                                                                                |

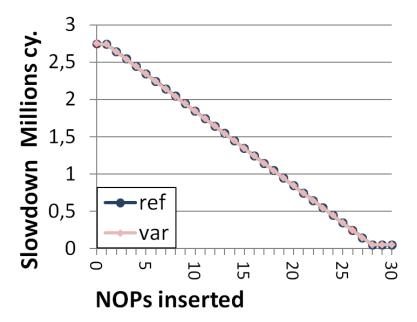

| 4.11 | Slowdown when executed $rsk$ -nop as $scua$ against 3 $rsk$ co-runners. Results shown as a function of nop instructions (©2016 IEEE) 58                                                                                 |

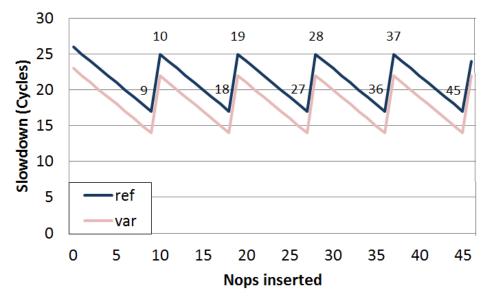

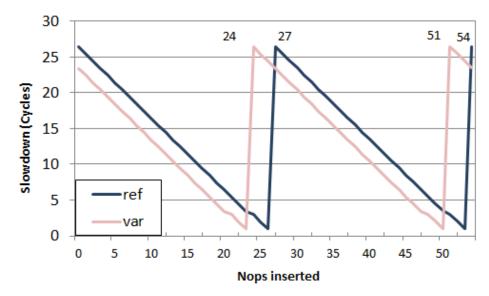

| 4.12 | Slowdown when executing $bsk$ -nop as $scua$ against 3 $bsk$ co-runners with $FIFO(©2016 \text{ IEEE})$                                                                                                                 |

| 4.13 | Slowdown when executing $bsk$ -nop as $scua$ against 3 $bsk$ co-runners with $RoRo(©2016 \text{ IEEE})$                                                                                                                 |

| 4.14 | msk-nop methodology for FIFO(©2016 IEEE)                                                                                                                                                                                |

|      | msk-nop instcache aware methodology for FIFO(©2016 IEEE) 69                                                                                                                                                             |

|      | msk-nop methodology for RoRo(©2016 IEEE)                                                                                                                                                                                |

|      | msk-nop instcache aware methodology for RoRo(©2016 IEEE) 63                                                                                                                                                             |

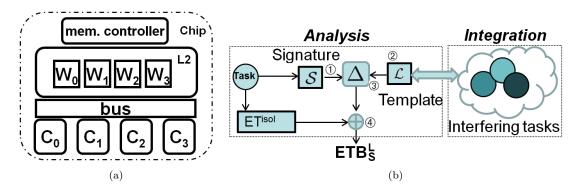

| 5.1  | Reference multicore architecture (a), and main steps in the <i>RUs</i> and <i>RUl</i> methodology (b)                                                                                                                   |

List of Figures x

| 5.2 | Impact from/to the different access types to the bus                                                                                                 | 74  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

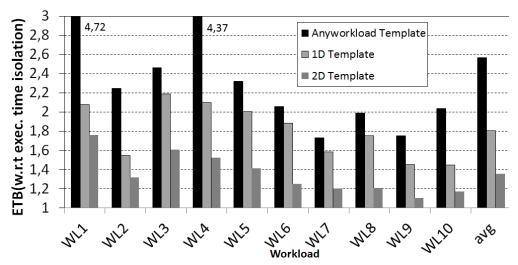

| 5.3 | WCET bounds for different templates for 10 4-task workloads. Results                                                                                 |     |

|     | are normalized to the execution time in isolation                                                                                                    | 78  |

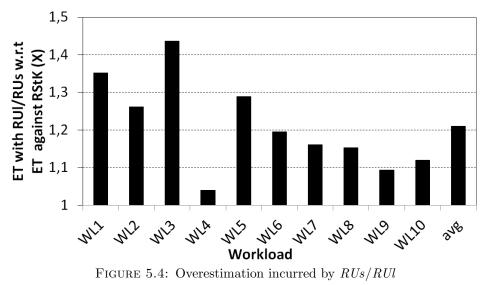

| 5.4 | Overestimation incurred by $RUs/RUl$                                                                                                                 | 80  |

| 6.1 | Diagram of SurApp generation                                                                                                                         | 85  |

| 6.2 | Simplified view of NGMP's main shared resources                                                                                                      | 85  |

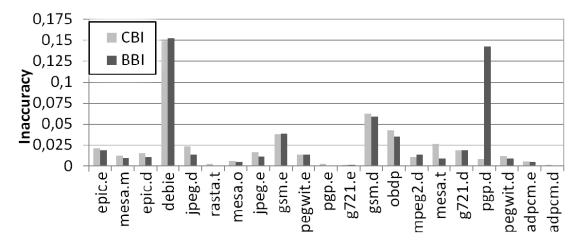

| 6.3 | cbi and $bbi$ accuracy results                                                                                                                       | 92  |

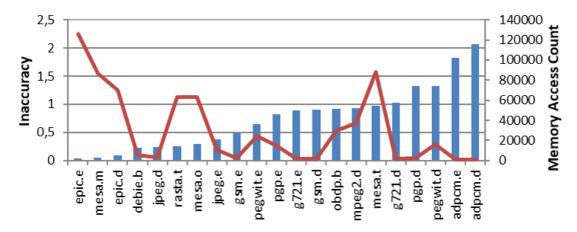

| 6.4 | $mbi$ (blue columns) and correlation to mem. access count $n_{mem}^{real}$ (red line)                                                                | 92  |

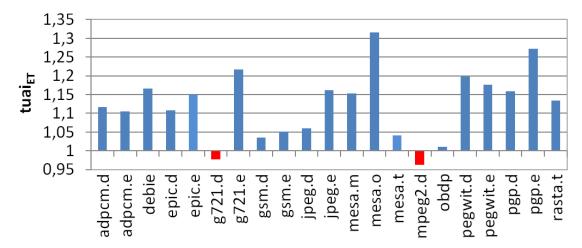

| 6.5 | Multicore Execution Time Inaccuracy of the <i>scua</i> when executed in the workloads shown in Table 6.1 (against real contenders and their SurApps) | 93  |

| 6.6 | Inaccuracy Results                                                                                                                                   | 94  |

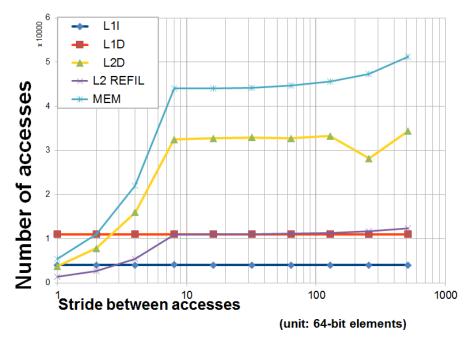

| 7.1 | Avg. number of IL1 (L1I), DL1 (L1D), L2 (L2D) and memory (MEM) accesses, and L2 refills per loop iteration for different data strides (©2018 IEEE)   | 105 |

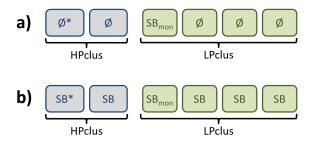

| 7.2 | Experimental setup (a) in isolation and (b) with contention (©2018 IEEE).                                                                            |     |

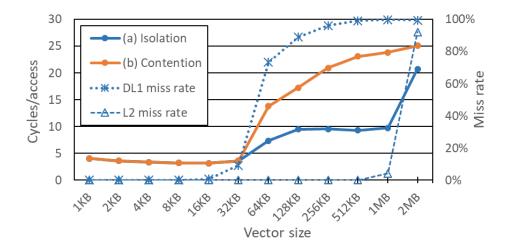

| 7.3 | Cycles per access for the two setups when varying vector size (©2018 IEEE)                                                                           |     |

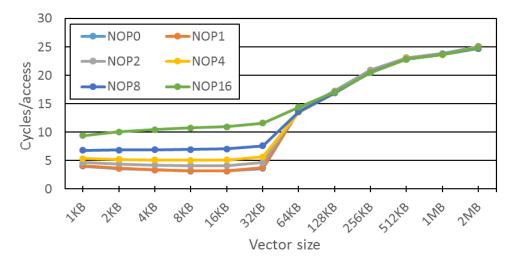

| 7.4 | CPA with contention varying the number of NOPs between accesses                                                                                      |     |

|     | (©2018 IEEE)                                                                                                                                         | 110 |

# List of Tables

|     | EEMBC names                                                                                      |     |

|-----|--------------------------------------------------------------------------------------------------|-----|

|     | Main terms used in this chapter                                                                  |     |

| 6.1 | 4-thread workloads used in this work (Benchmarks and Kernel full-names are listed in Figure 6.3) | 90  |

| 0.2 | SurApp. Space kernels in italics. Programs sorted from lowest to highest RealApp slowdown        | 94  |

| 7.1 | Juno Soc vs SnapDragon 810 comparison                                                            | 112 |

# **Abbreviations**

AMBA Advanced Microcontroller Bus Architecture

APKI Access per Kilo Instruction

BSK Bus Stressing Kernel

CABA Cycle Accurate /Bit Accurate

CLS Cache Lines

COTS Commercial Off-The-Shelf

DL1 First Level Data Cache

EEMBC Embedded Microprocessor Benchmark Consortium

FCFS First-Come First-Served

FIFO First-In First-Out

FR-FCFS First-Ready First-Come First-Served

IL1 First Level Instruction Cache

IMA Integrated Modular Avionics

IMA-SP IMA for Space

IP Intelectual Property

L2 Second Level Cache

LRU Least Recently Used

MBTA Measurement Base Time Analysis

MRU Most Recently Used

MSK Memory Stressing Kernel

NDA Non Disclosure Agreement

NoC Network-on-Chip

PMC Program Monitoring Counter

RoRo Round Robin

RSeK Resource Sensitive Kernel

Abbreviations xiii

RSK Resource Stressing Kernel RUl Resource Usage Template

RUs Resource Usage Signature

scua Software Component Under Analysis

sdki Stack Distance per Kilo Instruction

SDV Stack Distance Vector

SoC System on Chip

STA Static Time Analysis

SurApp Surrogative Application

TDMA Time Division Multiple Access

UBD Upper Bound Delay

WCET Worst-Case Execution Time

This Thesis is dedicated to Enrique Fernandez Garcia, my father who nurtured my thirst for knowledge answering every scientific question that a child can come with.

In memory of Aranzazu Diaz Urrestarazu, my mother who gave me the wits to follow this path and I miss so much.

## Chapter 1

### Introduction

During the last decades our society has witnessed a steady growth of all kind of computers. With this increase in the availability of computational power, which has reached the point where we can hold a gigantic amount of computation on the palm of our hands, the demand for these products has followed suit. While most of this growth may pass unnoticed by most of the common users, whom may picture only general purpose computers as the only commercial use of this technology, in fact, computing devices have been taking over several applications that traditionally were in the realm of mechanical or simpler electronics. Such applications have come to be labeled as Embedded Computation, being distinguishable by how focused to a very specific functionality they are. In other words, they correspond to computers embedded in vehicles, industrial equipment, etc. As an illustrative example, let us take the computers that control any modern car, where originally things regulated by mechanical or electrical appliances (e.g. fuel injection, ABS control, etc) now are done by a embedded computer with more efficiency. Far from reaching a stalling point, the development of better embedded computing systems has continued in line with the increasing demand of these kinds of devices, e.g. in the smartphone market. The continued increase of the performance available, far from deter or satiate the demand for these products, has kept growing reanimating even other fields now in high demand like Machine Learning. So now we can see High Performance processors with embedded applications becoming the new norm like using multicores CPUs and GPUs in cellphones.

Even thought the most widely known application of embedded systems may be entertainment and communication, they are used in domains where failures can have devastating consequences. As such, embedded systems in those domains are referred to as critical embedded systems, and can be broadly classified into several non exclusive categories depending on how critical they are. A embedded system may take care of a critical

mission whose failure may generate economical or social harm for the company. These systems may be classified as "mission critical". Aside, a different or the same system may take care of security functions, like cryptography, whose failure may involve security issues, so this system may be classified as "security critical". And last but not least, critical embedded system may be in charge of functionalities related to the safety of human beings, so that a failure may cause fatalities, material loss or environmental damage. Those systems can be classified as "safety critical".

The market for critical embedded systems covers a significant share of the overall embedded market [1] and it is in fact on the rise with further expectations of growth [2]. Evidence of the growth of critical embedded systems can be found in the increasing attention that chip manufacturers have drawn to this market, with specific products targeting them [3, 4].

#### 1.1 Requirements of Critical Embedded Systems

Evidence of correct timing behavior. As for mainstream computing systems, the correctness of critical embedded systems depends on their ability to provide correct functional results. However, unlike regular embedded systems, critical embedded systems involve non-functional results that are as important as the functional ones. Non-functional metrics include, among others, timing (or guaranteed performance), security, and energy. In this Thesis we focus on timing behavior. The timing Validation and Verification of Critical Embedded Systems focuses on providing evidence that system functions will be performed timely. Timing Validation and Verification builds on two elements: First, timing analysis methods that estimate bounds to the WCET of tasks [5]; and second, task scheduling techniques that assess whether all application software implementing system functions are actually executed timely [6]. Further, in many cases the behavior of critical embedded systems is subject to legal directives. Critical embedded systems providers must show adherence to those directives, before they are allowed to deploy a critical embedded system device. Legal directives are "implemented" showing adherence to safety standards, e.g. ISO26262 [7] in automotive. Those standards aim at reducing the risk of malfunction so that it is as low as reasonably practicable, either in the functional or non-functional behavior of the critical embedded systems, so the system is considered safe enough. The level of evidence to be provided depends on the criticality of the system/subsystem under consideration.

Unprecedented performance requirements. Most new "smart" services in current and future critical embedded systems, e.g. autonomous driving in cars, are software-based. This makes software one of the central elements to increase critical embedded

systems' competitive edge [8]. Smart software services translate into software managing huge amounts of data (e.g. coming from camera and LIDAR in cars). Further, software is instrumental for decision making implementing complex artificial intelligence algorithms. As a result, software complexity and performance requirements raise to unprecedented levels. For instance, in the automotive domain, performance is expected to increase by 100x by 2024 with respect to applications performance requirements in 2016 [9].

Increased integration and use of Commercial Off-The-Shelf multicores. Several sources claim that, by the end of 2016, luxury cars embedded up to 150 Electronic Control Units, in response to the need for high computer performance. This trend towards high Electronic Control Units count faces the problem of limitations in the physical space available in a car and also the cost, weight, and low-reliability of physical components (the electronic control units and the wiring to connect them). To address this problem, critical embedded systems industry has begun the process to adopt multicore processors (multicores in the following) as their baseline computing solution. This situation extends across a variety of application domains, including automotive, avionics and space. In this line, despite the interest of chip providers in the growing critical embedded systems' market, they are driven by the mainstream market (e.g. mobile market). As a result, industrial developers of critical embedded systems have to turn to Commercial Off-The-Shelf (COTS) processors to abate the procurement costs and obtain the performance needed. However, mainstream COTS processors are equipped with several features that complicate timing validation and verification.

Integrated Architectures, Mixed criticality and multi-provider critical embedded systems. In the past, the design of critical embedded systems built on the concept of federated architectures [10], under which critical embedded system consisted of independent interconnected subsystems, each implementing one or few functionalities. This physical separation allows incremental certification by construction. However, as the number of functions to implement by software grows, it is infeasible to devote a dedicated hardware (e.g. Line Replaceable Unit) to run it. Industry has addressed this challenge by adopting integrated architectures, in which several applications, usually subject to different criticality characteristics, run concurrently on a single hardware platform. Examples of integrated architectures are Integrated Modular Avionics (IMA) [11] in avionics, Integrated Modular Avionics for space (IMA-SP) [12] for the space domain, and AUTOMotive Open System ARchitecture (AUTOSAR) [13] for the automotive domain.

In terms of software design, integrated approaches allow system integrators to subcontract the development of different software elements to various software providers. Software Providers are given a specification of the required functionality and time budgets

in which their application(s) must fit. Time budgets are defined according to a global schedule designed by the integrator to run all software functionalities timely. In general, a Software Provider carries out the implementation of its applications in increments, checking in every release applications' functional and non-functional behavior against their specifications.

#### 1.2 Challenges in Timing Analysis

The trends shown in the previous section on the design and use of critical embedded systems have caused disruptive changes in current practice timing analysis.

Multicore Timing Analysis. In spite of the potential to improve performance, embracing multicores for real-time systems industry is challenging as they bring their own difficulties, especially for timing analysis. At a conceptual level, the intent of timing analysis is to provide, at low-enough cost, a WCET bound for programs running on a given processor, so that high guaranteed utilization of the computation resources can be assured. In this formulation, "high" utilization implies tight bounds (hence with as little pessimistic over-provisioning as possible) and "guaranteed" means truly upper bounding (hence with no risk of incautious under-provisioning). In particular, research on timing analysis for multicore processors is still in its infancy, particularly for COTS hardware. Ideally, the transition to multicore processors should allow industrial users to achieve higher levels of guaranteed utilization, together with attractive reduction in the performance-per-watt ratio, design complexity, and procurement costs. Unfortunately, however, the architecture of multicore processors poses hard challenges on (worst-case) timing analysis. The interference effects arising from contention on access to processorlevel shared resources need far greater attention than in the single-core case, as much greater is the arbitration delay and state perturbation that resource sharing may cause. In consequence, the "padding" factor that needs to be captured in the computed bounds to compensate for the relevant effects is much greater. The difficulty with the timing analysis of software programs running on multicore processors is, thus, a serious impediment to their adoption in real-time systems industry. Static or Measurement-Based Timing Analysis (STA and MBTA respectively) [14] are affected by the disruption of complex hardware and in particular multicores.

• Static Timing Analysis relies on an accurate timing model of the hardware under test. Static timing analysis further creates a mathematical representation of the application, which is combined with the timing model to derive bounds to the applications' timing behavior in that hardware. Static timing analysis focuses on

the soundness and safeness of its application, which allows theoretically, meeting all safety standard requirements. However, the validity of the bounds depends on the correctness of the hardware timing models, which are difficult to develop and validate especially for complex hardware. This is compounded with the lack of timing information of the processor implementation [15]. Even when hardware manufacturers provide timing information (e.g. in the reference manuals), it can be inaccurate or outdated with respect to the deployed chip implementation. As illustrative example, the FreeScale e500mc core documentation comprises several revisions already with non-negligible changes across them [16]. In the case of multicores, this lack of information affects the impact of contention that tasks suffer in the access to shared hardware resources. All these difficulties have made that real-time industry and static timing analysis tool providers resort to measurement-based approaches [17] to derive contention bounds, as done for the Freescale P4080 processor [18].

• Measurement Based Timing Analysis executes the program on the realplatform under stressing conditions and collects measurements, This approach also requires certain level of understanding of its behavior, in order to measure the longest and more sensitive path in the code of the program. Those measures are latter operated to derive a bound to the timing behavior of the application. For instance, the longest-observed execution time, or high water-mark time, is recorded and inflated with a safety margin (e.g. 20%). For multicores, the reliability of measurement based timing analysis provided results depends on, among others, ensuring that in the experiments performed the application suffers the maximum contention in its access to the hardware shared resources, but also in the experience of engineers [15]. Designing a proper set of experiments and analyze the measurements taken requires knowledge and proper documentation about the hardware shared resources and the available hardware tools to monitor the execution. Even thought the amount of documentation available and its level of detail required for this approach compared with a static timing analysis approach is lesser, it has a direct impact on how tight the estimates can be.

Timing Analysis of Commercial Off-The-Shelf hardware. Current COTS multicores are designed to improve average performance rather than time predictability, which is an essential ingredient to compute tight and sound WCET bounds for real-time software programs. This kind of processors usually implements several hardware resources and optimizations that are very disruptive for the timing analysis required for critical embedded systems, some of them as common and widespread as shared caches and out-of-order execution. Also, COTS hardware is aimed for a wide market that until

now does not demand the amount of documentation that would be helpful for timing analysis. Sadly, at the present state of the art, analysis solutions capable of delivering tight and sound worst case-execution bounds for COTS multicores are not fully mature.

Time Composable Worst-Case Execution Time estimates. Every new critical embedded system generation sees an increase in the number and complexity of their components. The timing analysis of each component, and also of the system as a whole, is not an easy task, but it can be eased if the analysis of the components is time composable. We use the term *compositional* to mean that some properties of an individual part of the system can only be determined on (assumed) knowledge of the constituents of the system. This is in contrast with the term *composable*, which regards those properties of an individual part that can be determined considering that part in isolation and hold true on composition into the system [19]. Applied to WCET and multicores, a WCET estimate would be composable if it is not dependent on the load co-runner tasks put on hardware shared resources.

Early Timing Estimates. While time composable WCET estimates are desirable, they may account for over-pessimistic interference and lead to pessimistic WCET estimates w.r.t. real operation conditions. In this scenario, one may want to account for some information on contender applications to tighten WCET estimates. However, multicores challenge validating that the application fits its assigned timing budget since the timing behavior of one Software Provider's application depends on how other (contender) applications – likely developed by other Software Providers – use multicore shared resources. To make things worse, contender applications may not be shared among Software Providers or with the integrator for Intellectual Property reasons. This poses new challenges in deriving time estimates during early design phases, relegating time budget testing to late design phases. Clearly, the cost of managing any violation of the time budgets significantly increases during late design phase, potentially jeopardizing the whole design and product's time to market.

#### 1.3 Contributions

While COTS multicores offer a number of advantages for critical embedded system industry, their complexity challenges the overall timing validation and verification process. This Thesis proposes several methodologies to i) increase the confidence on derived WCET bounds; ii) increase the time composability of derived WCET bounds; and iii) help deriving WCET estimates as early as possible during early development phase and system integration. The main contributions of this work can be summarized as follows:

- 1. Taxonomy of existing approaches. Over the years, the critical embedded system community has devoted considerable attention to the impact on execution time that arises from contention on access to hardware shared resources. The relevance of this problem has been accentuated with the arrival of multicore processors. From the state of the art on the subject, there appears to be considerable diversity in the understanding of the problem and in the approach to solve it. This sparseness makes it difficult for any reader to form a coherent picture of the problem and solution space. As first contribution of this Thesis we provide a taxonomy to categorize each known approach to the problem based on its specific goals and assumptions. This piece of work aims at becoming a reference publication for future works on this area.

- 2. Increasing the confidence on MBTA WCET estimates. For measurement based timing analysis, the most used timing analysis technique in industry, one of the main challenges when it comes to time analyze COTS multicores, is deriving the worst-case impact that contention can cause on the access to hardware shared resources. This longest-possible delay, usually referred to as ubd (upperbound delay), is central to derive the worst-case contention that tasks can suffer. State-of-the-art techniques used to compute ubd employ resource stressing kernels (RSK) [20][21][22] that put high load on the shared resources. However, we show that those techniques do not achieve the goal of exposing the highest contention. With focus on two of the most used fair arbitration policies, round robin and firstin first-out, we show that under heavy contention scenarios, a "synchrony effect" arises that causes each request issued to suffer a contention delay that can be systematically inferior to ubd. This challenges the use of measurement based timing analysis together with resources stressing kernels. We propose a measurementbased methodology to accurately derive ubd without needing latency information from the hardware provider. Experimental results, obtained on multiple processor configurations, demonstrate the robustness of the proposed methodology.

- 3. Signatures and Templates to increase Time Composability. Contention in the access to hardware shared resources causes that task's timing behavior depends on its co-runners, and in particular, on the load they put on shared resources. This dependence, negatively affects (reduces) time composability and constrains incremental verification. To attack this problem, we introduce the concepts of resource-usage signatures and templates, to abstract the potential contention caused and incurred by tasks running on a multicore. Building on them, we propose an approach that enables the analysis of individual tasks largely in isolation, with low integration costs, producing execution time estimates per task that are easily composable throughout the whole system integration process. Templates

and signatures make the WCET estimate derived for task  $\tau$ , time composable with respect to a particular usage u of the hardware shared resources made by the interfering co-runner tasks. The WCET derived under u upper bounds  $\tau$ 's execution time under any workload as long as the co-runners of  $\tau$  can be proven to make a resource usage smaller than u. As a result, the system integrator only needs to characterize the tasks' access to hardware shared resources (a low-cost abstraction of the task execution time), ignoring any finer-grain detail of that access behavior.

- 4. Surrogate Applications for Early Design Phase WCET estimation. Properly allocating time budgets to applications during system's early design phase prevents costly-to-handle time over-runs in late design phase. Applications running on a multicore affect each others' behavior, which complicates reaching this goal. Further, in multi-provider software developments, software providers are reluctant to share their applications for intellectual property reasons. Both factors prevent deriving tight bounds until late design phase when applications are actually integrated. We propose a modelling approach that simplifies time budgeting in early design phase by developing surrogate applications (SurApps) and an automatic framework to generate them. A SurApp copies the non-functional behavior of a given target application automatically. Each software provider generates, for an application  $App_A$ , a surrogate application  $SurApp_A$  and gives it to other providers without the risk of revealing any intellectual property. By running their applications against  $SurApp_A$ , other providers obtain a tight estimate of the slowdown their applications will suffer when run against  $App_A$ . This process is repeated for all providers facilitating early time budgeting for multicores.

- 5. Assessment of a COTS architectures (ARM big.LITTLE) for critical embedded systems. COTS processors pose a number of challenges for their use in critical embedded systems. Amongst COTS architectures, we regard high-performance ARM architectures as very popular in consumer electronics and increasingly tested in critical embedded systems. However, time budgeting on those architectures is an open problem. Thus, in this thesis we assess the suitability of the ARM big.LITTLE architecture for real-time critical embedded systems by attempting to measure the maximum contention that can be experienced in the access to shared resources. We perform this task in two different incarnations of this architecture: the Qualcomm SnapDragon 810 processor and the ARM Juno System-on-Chip. Our qualitative and quantitative assessment of these boards provides indications of how they can be used for critical embedded systems.

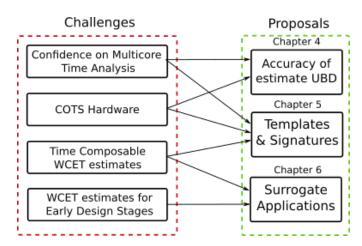

Figure 1.1: Challenges identified for future critical embedded systems and main proposals of this Thesis

Overall, the ultimate goal of this Thesis is to provide software support, in the form of concepts and specific methodologies, to improve the quality (i.e. tightness and reliability) on WCET estimates that can be derived with measurement based timing analysis, including early design stages of the software.

#### 1.4 Structure of this Thesis

Each of the major technical contributions of this Thesis covers some of the main challenges identified for critical embedded systems, see Figure 1.1. Further, each such contribution is mapped to a different chapter: Increasing accuracy deriving *ubd* is presented in Chapter 4; Signatures and Templates in Chapter 5; and Surrogate Applications in Chapter 6. In addition to those:

- Chapter 2 introduces our experimental methodology in terms of simulation platforms and applications.

- Chapter 3 proposes a taxonomy of the works in the state of the art.

- Chapter 7 presents the results of our first-hand experience with timing analysis on two different ARM big.LITTLE-based boards.

- Chapter 8 summarizes the main conclusions of this Thesis and presenting the main future directions.

#### 1.5 List of Publications

This Thesis has resulted in the following publications:

• Gabriel Fernandez, Jaume Abella, Eduardo Quiñones, Christine Rochange, Tullio Vardanega and Francisco J. Cazorla.

"Contention in multicore hardware shared resources: Understanding of the state of the art."

In 14th International Workshop on Worst-Case Execution Time Analysis (WCET). Madrid, Spain. July, 2014.

DOI: 10.4230/OASIcs.WCET.2014.31

• Gabriel Fernandez, Javier Jalle, Jaume Abella, Eduardo Quinones, Tullio Vardanega, Francisco J. Cazorla

"Increasing Confidence on Measurement-Based Contention Bounds for Real-Time Round-Robin Buses"

Design Automation Conference (DAC) San Francisco, CA. June, 2015. https://doi.org/10.1145/2744769.2744858

Gabriel Fernandez, Javier Jalle, Jaume Abella, Eduardo Quinones, Tullio Vardanega, Francisco J. Cazorla

"Resource Usage Templates and Signatures for COTS Multicore Processors"

In Design Automation Conference (DAC) San Francisco, CA. June, 2015. https://doi.org/10.1145/2744769.2744901

• Gabriel Fernandez, Jaume Abella, Eduardo Quinones, Luca Fossati, Marco Zulianello, Tullio Vardanega, Francisco J. Cazorla

"Computing Safe Contention Bounds for Multicore Resources with Round-Robin and FIFO Arbitration" © 2016 IEEE

• Gabriel Fernandez, Francisco J. Cazorla, Jaume Abella.

"Consumer Electronics Processors for Critical Real-Time Systems: a (Failed) Practical Experience"

The ERTS2: Embedded Real Time Software and Systems, Toulouse, France. January, 2018.

https://hal.archives-ouvertes.fr/hal-01708723

Gabriel Fernandez, Jaume Abella, Guillem Bernat, Francisco J. Cazorla

"Surrogate Applications for Early Design Stage Multicore Contention Modeling"

IEEE Transactions on Emerging Topics in Computing 2018.  $\label{eq:http://dx.doi.org/10.1109/TETC.2018.2852760}$

Gabriel Fernandez, Francisco J Cazorla, Jaume Abella and Sylvain Girbal

"Assessing Time Predictability Features of ARM big.LITTLE Multicores" © 2018 IEEE

In International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD), Lyon, France, September 2018.

#### 1.5.1 Related publications

The following publications were done as preamble to this thesis during my master studies.

- Gabriel Fernandez, Jaume Abella, Eduardo Quiñones, Luca Fossati, Marco Zulianello, Tullio Vardanega, Francisco J. Cazorla

- "Introduction to Partial Time Composability for COTS Multicores". In 23th ACM/SIGAPP Symposium On Applied Computing (SAC). Salamanca (Spain), April 13-17 2015.

- Gabriel Fernandez, Jaume Abella, Eduardo Quiñones, Luca Fossati, Marco Zulianello, Tullio Vardanega, Francisco J. Cazorla

- "Seeking Time-Composable Partitions of Tasks for COTS Multicore Processors"

In IEEE International Symposium On Real-Time Computing (ISORC) Auckland, New Zealand. April, 2015.

## Chapter 2

# **Experimental Framework**

This Chapter introduces the experimental infrastructure used to quantitatively assess the proposals made in this Thesis. It also provides a description of the benchmarks and reference applications used to that end.

In terms of experimental infrastructure, we use the following:

- 1. COTS hardware multicore boards. These are specially used for the software-only proposals.

- 2. Architectural simulators. The use of simulators is widespread in industry and academia for low-level performance analysis and hardware design. In this line we use simulators for our hardware proposals.

In terms of benchmarks we use:

- 1. Representative benchmark suites commonly used in research in the area of critical embedded systems (MediaBench and EEMBC Autobench).

- 2. Space representative applications provided by the European Space Agency.

- 3. Synthetic applications aimed at capturing extreme (corner) behaviours.

#### 2.1 COTS Hardware Multicore Platforms

In order to fulfil the experimental needs of this Thesis, we have used several hardware platforms. In this section we describe the architecture of the platforms and the boards where these architectures are implemented. We use two very different architectures: LEON and ARM.

#### 2.1.1 The LEON processor

LEON processors are provided by Cobham Gaisler AB as synthesizable VHDL models. We use two versions of these processors: LEON3 and LEON4. Both of them are 32-bit cores compliant with the SPARC V8 architecture, but they are highly configurable, making them suitable for systems-on-chip (SoC) designs.

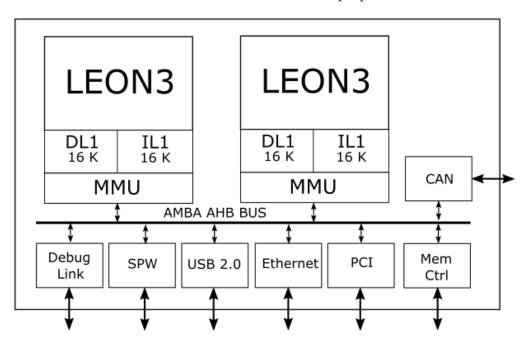

• LEON3 implements a 7-stage pipeline with hardware multiply, divide and MAC units. The cache follows the Harvard architecture, separating instruction and data cache, see Figure 2.1. Caches comprise ways whose size may range from 1 to 256 kilobytes. They implement least-recently used (LRU) replacement policy. LEON3 uses an AMBA-2.0 AHB bus interface that is used to connect with external components (e.g. memory controller). The core has also Advanced on-chip debug support with instruction and data trace buffers. The source code is available under GNU GPL license, free for research and educational purposes, but it is also available under a low-cost license for commercial purposes.

FIGURE 2.1: Block diagram of the GR712RC implementation of the LEON3 architecture used in this study.

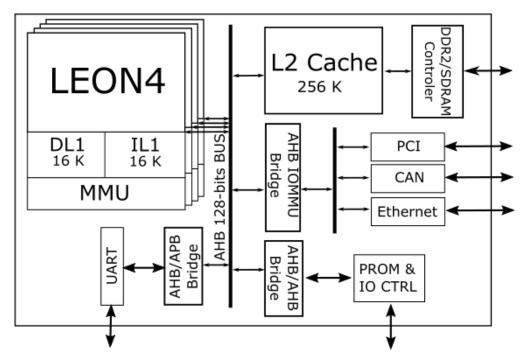

• LEON4 implements a 7-stage pipeline with a branch predictor. Even though the ISA is 32-bits, the core implements a 64-bit internal data path for loads and stores. The AMBA-2.0 AHB interface can be configured to use either 64 or 128 bits. The cache follows the Harvard architecture, separating instruction and data cache. First level caches also comprise 1 to 256 kilobytes per way, and implement LRU replacement policy. The core has also Advanced on-chip debug support with

instruction and data trace buffers. The source code is only available under a low-cost commercial license.

FIGURE 2.2: Block diagram of the ML510 implementation of the LEON4 architecture used in this study.

#### 2.1.2 The LEON platforms

We have used two platforms that implement the LEON3 and LEON4 multicore processors respectively: the GR712RC and the ML510 respectively.

- The GR712RC platform implements an ASIC with two LEON3 cores (see Figure 2.1). Each one comprises private first-level 16KB data and 16KB instruction caches, both being 4-way and 32 bytes/line. The ASIC is connected to the on-chip SRAM and the memory controller through an AMBA AHB bus [23]. The memory controller connects both cores to the off-chip SDRAM and SRAM devices. In the GR712RC there is no shared L2 cache, so the effect of the slowdown that a task suffers is mainly due to inter-task interferences in accessing the on-chip bus to reach main memory.

- The ML510 platform contains a Virtex 5 FPGA on which we use a preliminary implementation of the Next Generation Multipurpose Processor (NGMP) [24, 25] owing to FPGA space limitations, this platform does not have an on-core floating point unit. The NGMP was developed by Cobham Gaisler and the European Space Agency. This implementation comprises 4 LEON4 cores with always-taken

branch predictors and private data and instruction caches of 16KB each. Both the instruction and the data caches have 32-byte lines and are 4-way associative. The data cache employs a write-through with no-allocate miss policy. Each LEON4 core connects to a shared 256KB L2 cache through an AMBA AHB processor bus with 128-bit data width and round-robin arbitration policy. The L2 cache uses LRU replacement policy and implements a write-back, write-allocate policy. The L2 cache connects to the memory controller through a single memory channel shared by all cores (see Figure 2.2), but its space can be partitioned assigning ways to specific cores. In the NGMP, the effect of the slowdown that a task (benchmark) suffers is due to inter-task interference in accessing the on-chip bus, the on-chip shared L2 cache and the memory bandwidth [26].

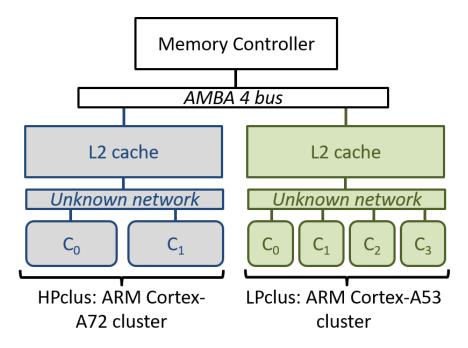

#### 2.1.3 The ARM big.LITTLE architecture

The ARM big.LITTLE architecture is mostly intended for mobile applications, although it is also used in other domains. It implements two clusters with different types of cores: a high-performance cluster with Cortex-A72 or Cortex-A57 cores, and a low power cluster with Cortex-A53 cores. The purpose of this design is enabling both, high-performance operation despite relatively high energy consumption, and low-power operation despite relatively low performance. This IP is highly configurable by the chip manufacturer. Next, we provide some details of this architecture. However, a large fraction of details are not provided in the documentation, and some others are specified as "implementation dependent" in ARM documentation.

- Cortex-A72 and Cortex-A57: this IP provided by ARM uses the architecture Armv8-A. It can work alone or in a cluster with up to 4 cores. The cluster can be interconnected using AMBA 5 CHI or 4 ACE buses. These cores are 64-bit supporting the AArch64 ISA and the AArch32 ISA for full backward compatibility with Armv7 code. These cores are designed for high performance so they implement a triple-issue out-of-order pipeline and a branch predictor. Aside, all the cores in the cluster share a L2 cache that can go from 512 KB to 4MB.

- Cortex-A53: as the A72 and A57 cores, the A53 may be deployed in clusters of 1 to 4 cores. They also uses the Armv8-A architecture, able to use the AArch32 and AArch64 ISAs. These cores are designed for power efficiency so the pipeline is in-order and dual-issue. Still, it has a branch predictor. It includes several power saving features like hierarchical clock gating. The cluster also shares a L2 cache, but its size can only be in the range 128KB up to 2MB.

#### 2.1.4 The ARM platforms

During the experiments we did for this Thesis, we used originally the platform Snap-Dragon 810, but later on we switched to another platform the Juno Board. The design of the processor is the roughly the same, but implemented by different manufacturers. The reason behind using both boards is a technical issues in the SnapDragon 810, in Chapter 7 we describe in detail this issues.

• The SnapDragon 810 processor is a Qualcomm implementation of the ARM big.LITTLE architecture used by Sony in some of their Xperia devices during 2015. It comprises abundant hardware events that can be tracked with Performance Monitoring Counters (PMCs), so conclusions obtained on this specific processor apply to several others in the consumer electronics market, especially those building upon ARM big.LITTLE architecture and those implemented by Qualcomm.

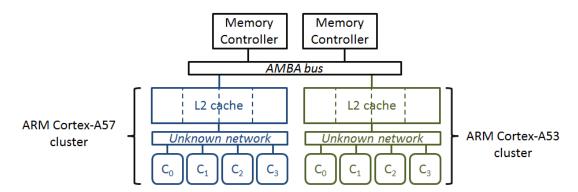

FIGURE 2.3: Schematic view of the elements of the SnapDragon 810 processor

The architecture of the processor, shown in Figure 2.3, comprises 2 clusters (also referred to as processors according to ARM's nomenclature): an ARM Cortex-A57 cluster with 4 cores and an ARM Cortex-A53 cluster with 4 cores. Each core is equipped with local first level instruction (IL1) and data (DL1) caches. Caches of the cores in one cluster are connected to a shared L2 cache, local to the cluster. An AMBA bus interface connects both clusters to two shared memory controllers to access DRAM. Peripherals and accelerators, also present in this platform but not shown in the figure, are connected to the AMBA bus too. In this Thesis we discount their effect by keeping them either disabled or idle.

Both clusters (A57 and A53) and the AMBA bus have been developed by ARM, the IP provider. Qualcomm, the chip manufacturer, integrates those components along with some others, which may or may not be provided by ARM. Moreover, in the integration process, Qualcomm may have introduced modifications in some IP

- components and/or their interfaces w.r.t. what is described in the documentation (not only those parameters regarded as implementation dependent).

- The **Juno SoC** is a Development Platform provided by ARM intended for software development. As the previous platform, it implements a big.LITTLE configuration with a Dual-core Cortex-A72 processor and a Quad-core Cortex-A53. The former has 48KB IL1, a 32KB DL1 and a shared 2MB L2 cache. In the latter cluster, it IL1 and DL1 caches of 32KB and a shared L2 of 1MB.

FIGURE 2.4: Schematic view of the elements of the Juno SoC processor

#### 2.2 Simulation Insfrastructure

We use a modified version of the SystemC component library SoCLib [27] as baseline platform in order to create a cycle accurate execution-driven simulator. SoCLib is an open platform for virtual prototyping especially for multi-core systems. It is designed to be programmed using Object-Oriented Coding, easing the creation of modular elements and providing tools to connect and synchronize them. For this purpose it is build upon the SystemC framework. Its modular organization helps the development and maintenance of the system. In this way each component (e.g. cache, core, memory, etc.) is coded individually and then easily connected to the rest of the system. Aside we can divide the system in two entities: the emulator and the timing simulator. The former handles the functional execution of the guest code and the latter uses the information provided by the first in order to provide cycle accurate timing. SoCLib has two types

of models: Cycle Accurate/Bit Accurate (CABA) and Transaction Level Modeling with Distributed Time. The implementation we use follows the former model.

We use an emulator that mimics a LEON4 processor core with the same configuration as the ML510 platform, previously described. But this configuration may be modified in some Chapters for experimental purposes. The main target of this modifications is the memory hierarchy configuration. Each Chapter describes the specific cache configuration used. The last level of the memory hierarchy is the memory controller which has been simplified to always hit using the same timing parameters that the ML510 platform. Moreover, the arbitration policy has been changed in Chapter 4. In a study with the European Space Agency [27], the performance accuracy provided by the simulator was assessed against a real NGMP implementation, the N2X [28] evaluation board. To that end, a low-overhead operating-system (kernel) that allowed cycle-level validation was deployed. Results for EEMBC benchmarks showed a deviation in terms of accuracy of less than 3% on average. For the HAWAII benchmark [29], an algorithm used to process raw frames coming from the sate-of-the-art near infrared (NIR) HAWAII-2RG detector, the inaccuracy reduced to less than 1%. Following the modular philosophy of SoCLib, we added new instrumentation inside the timing simulator in order to assess our solutions in an agile manner.

#### 2.3 Benchmark Suites

Interestingly so far multicores are mainly exploited in real-time systems by consolidating independent applications on the same chip. Those applications either share no data or the sharing is performed off-chip (e.g. on memory). This is made more evident as current timing analyses rely on splitting the last-level cache, hence, preventing data sharing. Hence, while it is clear that in the long-term parallel execution will be adopted, this is still a recent (and very active) research area of research not yet ready for industrialization. Overall, we build on the fact that applications do not share data and hence the coherence mechanism does not disturb the execution time measurements.

#### 2.3.1 EEMBC Autobench

The Embedded Microprocessor Benchmark Consortium (EEMBC) [30] has produced several benchmark suites. Among them, we have chosen the Autobench set that is designed for the automotive industry. All the benchmarks in the suite share a common loop that executes several times an algorithm that changes across benchmarks. These algorithms include bit manipulation, matrix mapping, a specific floating-point tester, a

cache buster, pointer chasing, pulse-width modulation, multiplication, and shift operations.

Table 2.1 lists all benchmarks providing their acronym and their description.

Table 2.1: EEMBC names

| Name    | Description                            |

|---------|----------------------------------------|

| a2time  | Angle to Time Conversion               |

| basefp  | Basic Integer and Floating Point       |

| bitmnp  | Bit Manipulation                       |

| cacheb  | Cache 'Buster'                         |

| canrdr  | CAN Remote Data Request                |

| aifft   | Fast Fourier Transform (FFT)           |

| aifirf  | Finite Impulse Response (FIR) Filter   |

| aiifft  | Inverse Fast Fourier Transform (iFFT)  |

| aiirflt | Infinite Impulse Response (IIR) Filter |

| matrix  | Matrix Arithmetic                      |

| pntrch  | Pointer Chasing                        |

| puwmod  | Pulse Width Modulation (PWM)           |

| rspeed  | Road Speed Calculation                 |

| tblook  | Table Lookup and Interpolation         |

| ttsprk  | Tooth to Spark                         |

#### 2.3.2 Mediabench

The Mediabench benchmark suite is composed of multimedia applications. Real-time systems are used more and more for executing this kind of applications, which makes this suite highly representative. Aside, the applications in this suite have a considerable bigger memory footprint than EEMBC, which makes them more attractive for certain parts of our research. Table 2.2 lists all the benchmarks and a simple description of each one. Several of these benchmarks are multimedia compressors, so they provide a encoder and decoder binary.

Name Description adpcm Simple and well known audio coder epic Image compression application g.721Voice compression application ghostscript PostScript interpreter Full-rate speech transcoding gsmJPEG standard compressor jpeg 3D graphic library Mesa MPEG2 standard compressor mpeg pegwit Public key encryption "Message digests signature" generator pgp Speech recognition application rasta

Table 2.2: Mediabench names and descriptions

#### 2.4 Space Applications

In addition to the previous benchmark suites, we use some applications used by the space industry.

- OBDP benchmark [29], is an algorithm used to process raw frames coming from the state-of-the-art near infrared (NIR) HAWAII-2RG detector, already deployed in space projects like the Hubble Space Telescope.

- DEBIE software controls an instrument, which was carried on PROBA-1 satellite, to observe micrometeoroids and small space debris by detecting impacts on its sensors, both mechanically and electrically.

### 2.5 Resource Stressing Kernels

During this Thesis we make use of *micro-kernels* [17, 26, 31], a set of single-phase user-level programs with a single execution behavior designed so that all their operations access a given shared resource, e.g. the bus. Due to their purpose these micro-kernels are referred as *Resource Stressing Kernels* (RSK) These micro-kernels consist of a main loop whose body includes a substantial number (e.g. 256) of instructions designed to generate a steady stress load on target resources. The fact that the loop body executes repeatedly the same instruction causes the target resource to be continuously accessed. Moreover, placing a high number of identical instructions in the loop body drastically reduces the impact of control instructions (down to 2-4%) [26]. The shape of a RSK

depends on the platform where is going to be executed and of its purpose. For this reason, more details on the RSK are provided n those Chapters where they are used.

# Chapter 3

# A Taxonomy of the Works in the State of the Art

This Chapter presents the first contribution of this Thesis, namely, a taxonomy of the related works on the topic of multicore contention analysis. It also introduces some basic concepts that are further used in the rest of this document. It is noted that, the most specific related works to each proposal are presented in the corresponding Chapters describing those proposals. From that point of view, this Chapter does not provide an exhaustive list of all related works but a categorization of those.

Different angles have been considered to address the timing effects of contention for shared resources, either on-chip or off-chip, leading to a number of families of techniques. However, while many solutions are claimed to exist, there is evident lack of common understanding of the problem space, in terms of processor features, and of the assumptions made to solve it. We attempt to cure this problem with the following taxonomy.

# 3.1 A possible taxonomy of state-of-the-art techniques to analyse the timing impact of resource contention

Under the umbrella term of resource contention, we capture the various forms of timing interference that software programs suffer owing to access to shared hardware resources. Notably, our analysis does not cover the contention on access to software resources. Furthermore, contentions arising from parallel execution of a software program fall outside of our analysis and are recognized in Section 3.2 as an important emerging ramification of the problem.

The challenge of contention in multicore processors has been addressed with various approaches. In this chapter we classify them in four broad categories, dependent on where they seem to direct their focus:

- 1. on system considerations, which address the contention problem top down, from the software perspective;

- 2. on WCET considerations, which take the opposite view, studying how contention phenomena affect the timing behaviour of the software;

- 3. on architecture considerations, which devise processor features and arbitration policies that help achieve composable timing behavior; and

- 4. on Commercial Off-The-Shelf(COTS) considerations, which propose processor-specific ways to deal with processor-specific contention and arbitration features.

We discuss the approaches in each category in isolation and we break them down into subgroups where appropriate.

# 3.1.1 System-centric techniques

System-centric techniques take a top-down approach to the problem. The techniques in this category take an off-chip, hence coarse-grained, perspective. Off-chip resources have longer latency than on-chip resources, and also a higher degree of visibility from the software standpoint than on-chip resources. For instance, at software level one can easily tell where a set of addresses is mapped to memory, but it is (much) harder to determine which data item is in cache at a given time and which is not. Similarly, software 'sees' (hence can program or directly effect) higher-level resources such as the Direct-Memory Access, but it is unaware of (and unable to directly control) low-level resources like a bus for inter-core communication and, other than in very special cases, the on-chip shared cache. In fact, the cache impact has characteristics that can be captured, from different angles and with different precision, with techniques that we classify in different categories of our taxonomy (system-centric and WCET-centric). Besides this cross-boundary overlap, the techniques in this category predominantly focus on off-chip resources.

We single out three angles worth of specific discussion: timing analysis frameworks; access scheduling and allocation; and works on COTS architectures.

#### 3.1.1.1 Timing analysis frameworks