# Evaluation of STT-MRAM main memory for HPC and real-time systems

## by Kazi ASIFUZZAMAN

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional TDX **UPCommons** (http://upcommons.upc.edu/tesis) i el repositori cooperatiu (http://www.tdx.cat/) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA** La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<u>http://upcommons.upc.edu/tesis</u>) y el repositorio cooperativo TDR (<u>http://www.tdx.cat/?locale-attribute=es</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual **únicamente para usos privados enmarcados** en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (*framing*). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the i n s t i t u t i o n a I r e p o s i t o r y UPCommons (<u>http://upcommons.upc.edu/tesis</u>) and the cooperative repository TDX (<u>http://www.tdx.cat/?locale-attribute=en</u>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# UNIVERSITAT POLITÈCNICA DE CATALUNYA

## **DOCTORAL THESIS**

# **Evaluation of STT-MRAM Main Memory** for HPC and Real-time Systems

by

## Kazi ASIFUZZAMAN

Supervisor: Dr. Petar RADOJKOVIĆ Dr. Eduard AYGUADÉ

Tutor: PARRA

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Department of Computer Architecture

2019

"You never fail until you stop trying."

Albert Einstein

#### UNIVERSITAT POLITÈCNICA DE CATALUNYA

# Abstract

Department of Computer Architecture

Doctor of Philosophy

#### Evaluation of STT-MRAM Main Memory for HPC and Real-time Systems

by Kazi ASIFUZZAMAN

It is questionable whether DRAM will continue to scale and will meet the needs of next-generation systems. Therefore, significant effort is invested in research and development of novel memory technologies. One of the candidates for next-generation memory is Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM). STT-MRAM is an emerging nonvolatile memory with a lot of potential that could be exploited for various requirements of different computing systems. Being a novel technology, STT-MRAM devices are already approaching DRAM in terms of capacity, frequency and device size. Special STT-MRAM features such as intrinsic radiation hardness, non-volatility, zero stand-by power and capability to function in extreme temperatures also make it particularly suitable for aerospace, avionics and automotive applications. Intensified efforts in STT-MRAM research by the memory manufacturers may indicate a revolution with STT-MRAM memory technology is imminent, and therefore, it is now the time to explore computing domains that can benefit from this technology. Although STT-MRAM technology got significant attention of various major memory manufacturers, to this day, academic research of STT-MRAM main memory remains marginal. This is mainly due to the unavailability of publicly available detailed timing and current parameters of this novel technology, which are required to perform a reliable main memory simulation on performance and power estimation.

This thesis demonstrates an approach to perform a cycle accurate simulation of STT-MRAM main memory, being the first to release detailed timing and current parameters of this technology from academia - essentially enabling researchers to conduct reliable system level simulation of STT-MRAM using widely accepted existing simulation infrastructure. The results show a fairly narrow overall performance deviation in response to significant variations in key timing parameters. The power consumption experiments also identify the key power component that is mostly affected with STT-MRAM. Furthermore, the thesis analyzes the feasibility of using STT-MRAM in realtime embedded systems by investigating STT-MRAM main memory impact on average system performance and Worst Case Execution Time (WCET). The results show that systems comprising STT-MRAM main memory can be analyzed with the same WCET approaches used in the systems with conventional DRAM. In quantitative terms, the results suggest STT-MRAM main memory in real-time embedded systems provides performance and WCET comparable to conventional DRAM, while opening up opportunities to exploit various advantages.

Overall, this thesis presents the first comprehensive exploration of possibilities to use STT-MRAM in HPC and real-time embedded domain and reveals that STT-MRAM would provide performance and WCET estimates comparable to DRAM while opening up several key advantages that the domains could benefit from. I dedicate this thesis to the memory of my dear friend Afnan Hadi Shourov (1984 - 2011)

# Acknowledgements

I start by thanking my supervisors Dr. Petar Radojković and Prof. Eduard Ayguadé Parra for their sincere support and continuous guidance during my thesis. I am truly privileged to conduct my Phd studies under their supervision and leadership.

I can not thank Petar enough for facilitating close supervision and exceptional inspiration, without which it would have been extremely difficult to pass over the challenging path of my PhD studies. He has been an outstanding mentor and leader all the way — assisting me in every obstacle I faced during the course of my PhD. Being a dynamic team leader, he connected me to the people and resources efficiently to solve each and every problem that came on our path. Petar also provided me enough scope to take decisions and grow my skills to be an independent researcher. I genuinely feel honored to pursue my PhD under his supervision.

I would like to thank Barcelona Supercomputing Center (BSC) for accepting me to be a part this prestigious institution. While consistent funding is a common challenge for all PhD students around the world, BSC relieved me from this concern, and allowed me to focus on my work that really matters. I am also grateful to BSC for providing me the office space, equipments and access to its state-of-the-art supercomputing resources. I would like to thank all staff and employees from different groups and departments of BSC with whom I interacted, for their sincere support and assistance. Special thanks to my colleagues Milan Pavlovic, Renan Fischer E Silva, Milan Radulovic and Rommel Sánchez Verdejo for their help and suggestions in professional and practical matters during my stay in Barcelona.

I thank the Department of Computer Architecture (DAC) of Universitat Politècnica de Catalunya (UPC) for carrying out the administrative procedures, providing access to its resources, forming academic committees for evaluation in different stages of the PhD thesis.

I am indebted to my father, Kazi Aktaruzzaman, who encourages me to be ambitious, prepares me to be capable to chase that ambition and supports me unconditionally on all of my endeavors. I would like to express my gratitude to my mother and brothers for always being there and assisting me in every step in my life. I thank my friends back home for their unconditional love viii

and support all the way. I owe a special thanks to Milladur Rahman (and family) for backing me up during the most difficult time of my life.

It will never be enough to thank my wife Zeba and daughter Yalina for their sacrifices to make this dissertation a reality. Zeba is an extraordinarily kind and cooperative woman with great capability to bring the best out of anyone. She goes an extra mile to accommodate my obligations, making way for me to progress. Without her support and encouragement, it would have been extremely difficult to complete the thesis.

This work is supported by the Collaboration Agreement between Samsung Electronics Co., Ltd. and BSC, Spanish Government through Programa Severo Ochoa (SEV-2015-0493), by the Spanish Ministry of Science and Technology through TIN2015-65316-P project and by the Generalitat de Catalunya (contracts 2014 -SGR-1051 and 2014-SGR-1272). This work has also received funding from the European Union's Horizon 2020 research and innovation programme under ExaNoDe project (grant agreement No 671578). The author wish to thank Terry Hulett, Duncan Bennett and Ben Cooke from Everspin Technologies Inc., for technical support.

# Contents

| Al               | Abstract in |            |                        |     |

|------------------|-------------|------------|------------------------|-----|

| Acknowledgements |             |            |                        | vii |

| 1                | Intro       | roduction  |                        |     |

|                  | 1.1         | Thesis     | s contribution         | 3   |

|                  | 1.2         | Public     | cations                | 5   |

|                  |             | 1.2.1      | Conferences            | 5   |

|                  |             | 1.2.2      | Under submission       | 6   |

|                  |             | 1.2.3      | Other publications     | 6   |

|                  | 1.3         | Thesis     | s organization         | 6   |

| 2                | Bacl        | kgroun     | ıd                     | 9   |

|                  | 2.1         | DRAN       | м                      | 9   |

|                  |             | 2.1.1      | DRAM organization      | 9   |

|                  |             | 2.1.2      | DRAM operation         | 11  |

|                  |             | 2.1.3      | DRAM challenges        | 11  |

|                  | 2.2         | Hybri      | id Memory Cube (HMC)   | 12  |

|                  | 2.3         | High       | Bandwidth Memory (HBM) | 14  |

|                  | 2.4         | Phase      | Change Memory (PCM)    | 15  |

|                  | 2.5         | Resist     | ive RAM (RRAM)         | 16  |

|                  | 2.6         | 5 STT-MRAM |                        | 17  |

|                  |             | 2.6.1      | Technology overview    | 17  |

|                  |             | 2.6.2      | Development trend      | 18  |

|                  |             | 2.6.3      | STT-MRAM opportunities | 19  |

|                  |             |            | DRAM refresh           | 19  |

|     |        | Memory errors                       | 20 |

|-----|--------|-------------------------------------|----|

|     | 2.6.4  | STT-MRAM special advantages         | 21 |

|     |        | Radiation hardness                  | 21 |

|     |        | Zero standby power                  | 22 |

|     |        | Operational temperature             | 22 |

|     |        | Integrated memory                   | 23 |

|     | 2.6.5  | STT-MRAM challenges                 | 23 |

|     |        | Simulation challenges               | 23 |

|     |        | Timing parameters: Dead ends        | 25 |

|     |        | Our approach                        | 26 |

|     |        | Commercial challenges               | 28 |

| OTT |        |                                     | •  |

|     |        | M Performance Impact in HPC Systems | 29 |

| 3.1 |        | luction                             | 29 |

| 3.2 | Exper  | imental setup                       | 29 |

|     | 3.2.1  | Application suite                   | 29 |

|     | 3.2.2  | HPC system simulation               | 30 |

|     |        | Target HPC platform                 | 31 |

|     |        | HPC application behavior            | 31 |

|     |        | Trace Collection                    | 32 |

|     | 3.2.3  | Simulated CPU                       | 33 |

|     |        | CPU pipeline                        | 33 |

|     |        | Cache memory                        | 34 |

|     | 3.2.4  | Simulated main memory               | 34 |

| 3.3 | Result | ts                                  | 36 |

|     | 3.3.1  | Industry estimate                   | 36 |

|     | 3.3.2  | Sensitivity analysis                | 39 |

| 3.4 | Summ   | nary                                | 39 |

x

3

| 4 | Ena        | bling a                                   | Reliable STT-MRAM Main Memory Simulation                                                                                      | 41                                                                                                                                 |

|---|------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1        | Introc                                    | luction                                                                                                                       | 41                                                                                                                                 |

|   | 4.2        | STT-N                                     | /IRAM timing parameters                                                                                                       | 41                                                                                                                                 |

|   | 4.3        | STT-N                                     | /IRAM power estimations                                                                                                       | 45                                                                                                                                 |

|   | 4.4        | Exper                                     | rimental setup                                                                                                                | 46                                                                                                                                 |

|   |            | 4.4.1                                     | Benchmark suite                                                                                                               | 47                                                                                                                                 |

|   |            | 4.4.2                                     | CPU Simulation                                                                                                                | 47                                                                                                                                 |

|   |            | 4.4.3                                     | Main memory simulation                                                                                                        | 48                                                                                                                                 |

|   |            | 4.4.4                                     | Validation                                                                                                                    | 49                                                                                                                                 |

|   |            | 4.4.5                                     | Methodology                                                                                                                   | 50                                                                                                                                 |

|   | 4.5        | Resul                                     | ts                                                                                                                            | 50                                                                                                                                 |

|   |            | 4.5.1                                     | Performance analysis                                                                                                          | 50                                                                                                                                 |

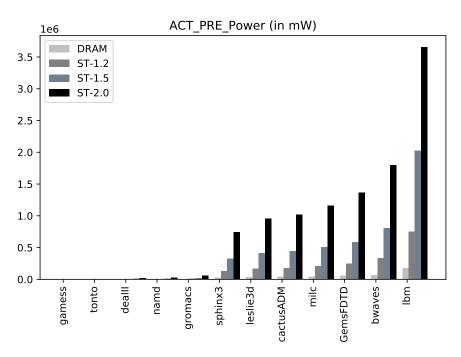

|   |            | 4.5.2                                     | Power consumption                                                                                                             | 54                                                                                                                                 |

|   | 4.6        | Sumn                                      | nary                                                                                                                          | 58                                                                                                                                 |

| 5 | Perf       | forman                                    | ce and WCET Implications in Real-Time Systems                                                                                 | 59                                                                                                                                 |

|   |            |                                           |                                                                                                                               |                                                                                                                                    |

|   | 5.1        | Introc                                    | luction                                                                                                                       | 59                                                                                                                                 |

|   | 5.1<br>5.2 |                                           | luction                                                                                                                       | 59<br>59                                                                                                                           |

|   |            |                                           |                                                                                                                               |                                                                                                                                    |

|   |            | Exper                                     | rimental setup                                                                                                                | 59                                                                                                                                 |

|   |            | Exper<br>5.2.1                            | imental setup                                                                                                                 | 59<br>59                                                                                                                           |

|   |            | Exper<br>5.2.1<br>5.2.2                   | Timental setup          Processor platform          Main Memory platform                                                      | 59<br>59<br>60                                                                                                                     |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3          | rimental setup                                                                                                                | 59<br>59<br>60<br>61                                                                                                               |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | imental setup                                                                                                                 | 59<br>59<br>60<br>61<br>62                                                                                                         |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | imental setup                                                                                                                 | 59<br>59<br>60<br>61<br>62<br>64                                                                                                   |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | Simulation infrastructure:SoCLib & DRAMSim2.Main ganalysis of real-time systemsMasurement-based probabilistic timing analysis | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>62</li> <li>64</li> <li>65</li> </ul>                                     |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | imental setup                                                                                                                 | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>62</li> <li>64</li> <li>65</li> <li>65</li> </ul>                         |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | imental setup                                                                                                                 | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>62</li> <li>64</li> <li>65</li> <li>65</li> <li>66</li> </ul>             |

|   |            | Exper<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | imental setup                                                                                                                 | <ul> <li>59</li> <li>59</li> <li>60</li> <li>61</li> <li>62</li> <li>64</li> <li>65</li> <li>65</li> <li>66</li> <li>66</li> </ul> |

xi

|   |      | 5.3.1   | Performance estimation                    | 69 |

|---|------|---------|-------------------------------------------|----|

|   |      | 5.3.2   | Worst case execution time (WCET) analysis | 71 |

|   | 5.4  | Sumn    | nary                                      | 76 |

| 6 | Rela | ated Wo | orks                                      | 77 |

|   | 6.1  | STT-N   | IRAM as main memory                       | 77 |

|   | 6.2  | STT-N   | IRAM as on-chip caches                    | 79 |

| 7 | Futi | ure woi | ·k                                        | 81 |

|   | 7.1  | Explo   | iting non-volatility                      | 81 |

|   | 7.2  | Check   | -pointing                                 | 82 |

| 8 | Con  | clusior | n                                         | 83 |

# **List of Figures**

| 2.1  | DRAM Read Cycle (not in scale)                                     | 10 |

|------|--------------------------------------------------------------------|----|

| 2.2  | Internal Structure of Hybrid Memory Cube (HMC) [12]                | 13 |

| 2.3  | Internal Structure of High Bandwidth Memory (HBM) [12]             | 14 |

| 2.4  | STT-MRAM cell                                                      | 18 |

| 2.5  | DRAM and STT-MRAM capacity growth in years                         | 19 |

| 2.6  | STT-MRAM and DRAM cell-array                                       | 27 |

| 3.1  | Repetitive behavior of HPC applications: ALYA, 1024 processes      | 32 |

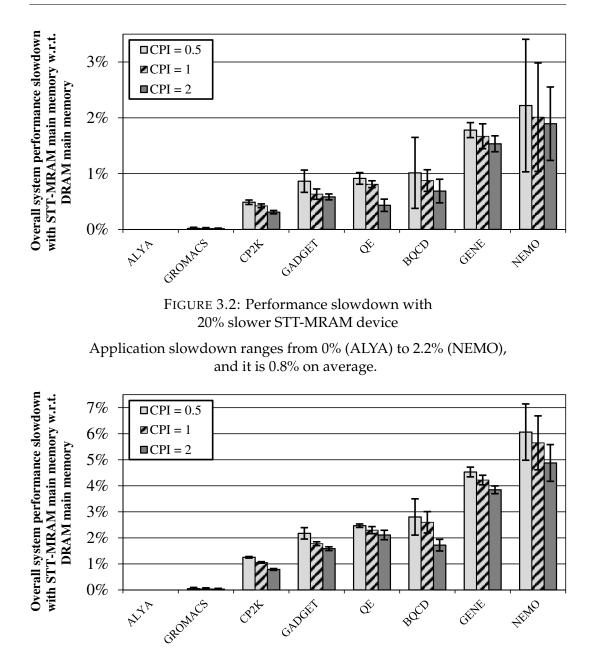

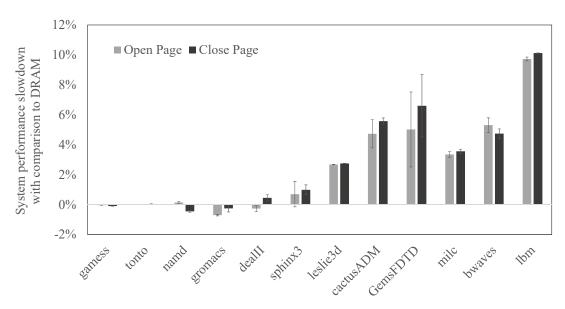

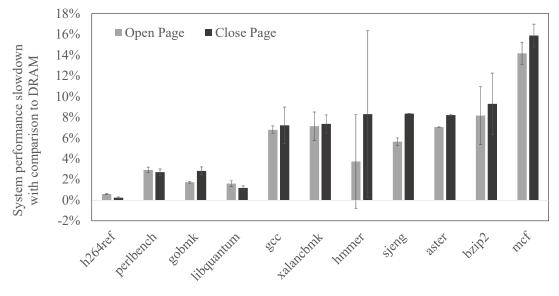

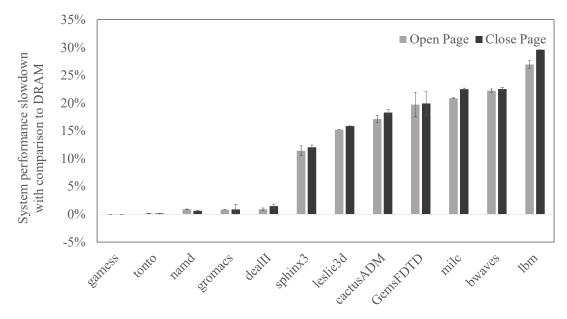

| 3.2  | Performance slowdown with 20% slower STT-MRAM device .             | 37 |

| 3.3  | Performance slowdown with 50% slower STT-MRAM device .             | 37 |

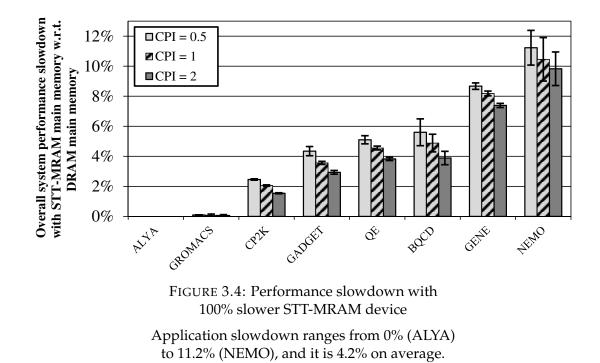

| 3.4  | Performance slowdown with 100% slower STT-MRAM device              | 38 |

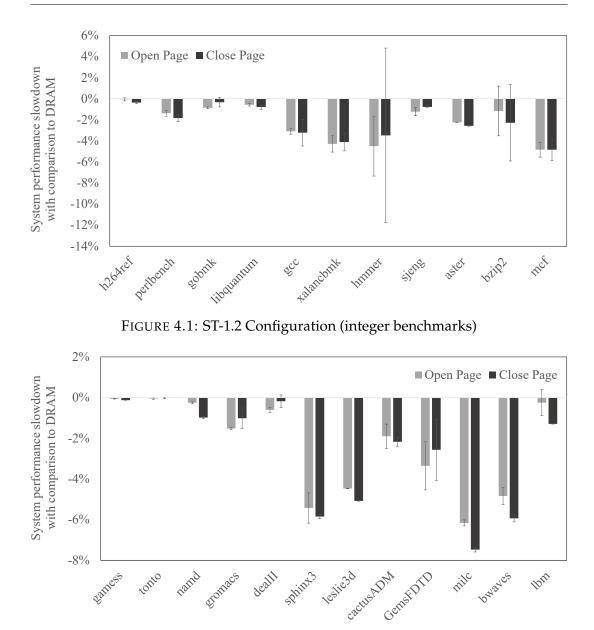

| 4.1  | ST-1.2 Configuration (integer benchmarks)                          | 51 |

| 4.2  | ST-1.2 Configuration (floating point benchmarks)                   | 51 |

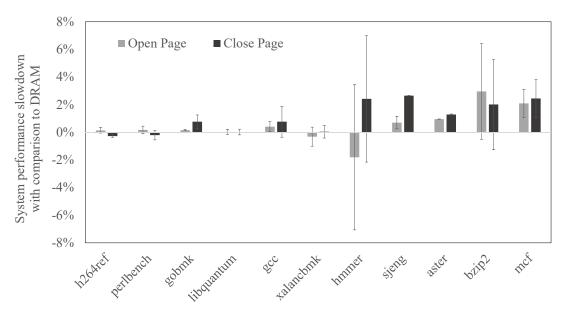

| 4.3  | ST-1.5 Configuration (integer benchmarks)                          | 52 |

| 4.4  | ST-1.5 Configuration (floating point benchmarks)                   | 53 |

| 4.5  | ST-2.0 Configuration (integer benchmarks)                          | 53 |

| 4.6  | ST-2.0 Configuration (floating point benchmarks)                   | 54 |

| 4.7  | Activate/Pre-charge power consumption of floating point benchmarks | 55 |

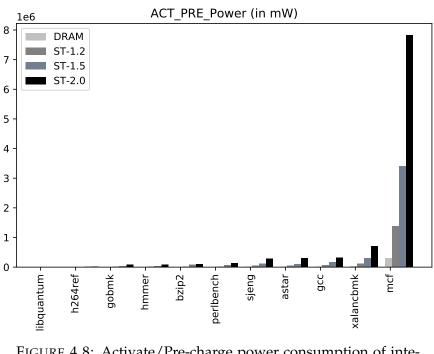

| 4.8  | Activate/Pre-charge power consumption of integer benchmarks        | 55 |

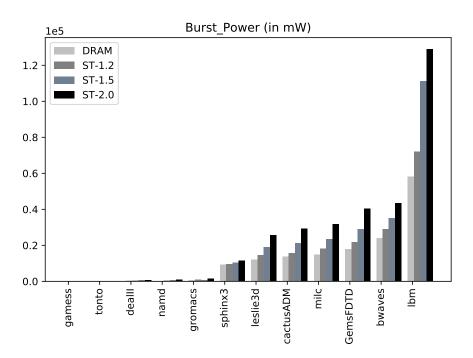

| 4.9  | Burst (Read/Write) power consumption of floating point benchmarks  | 56 |

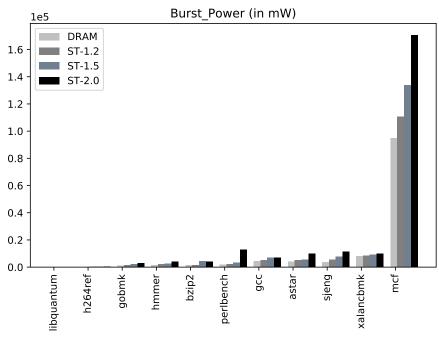

| 4.10 | Burst (Read/Write) power consumption of integer benchmarks         | 56 |

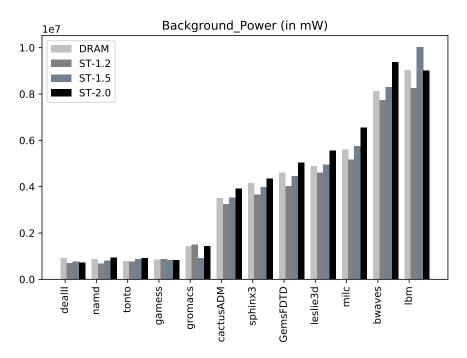

| 4.11 | Background power consumption of floating point benchmarks          | 57 |

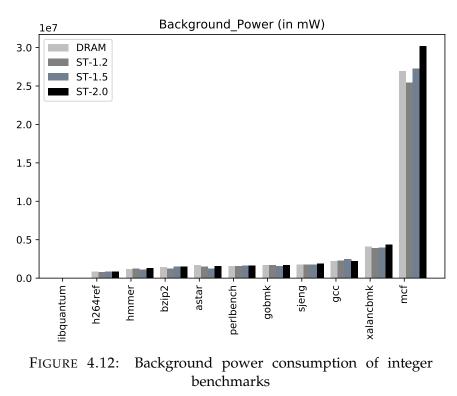

| 4.12 | Background power consumption of integer benchmarks                 | 57 |

| •  |   |

|----|---|

| X1 | V |

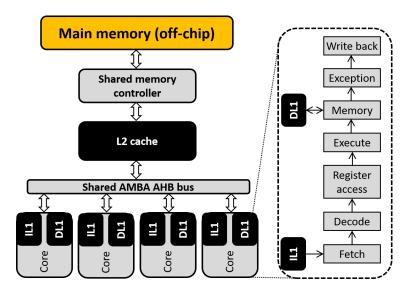

| 5.1 | Schematic view of the Next Generation Microprocessor (NGMP)           | 60 |

|-----|-----------------------------------------------------------------------|----|

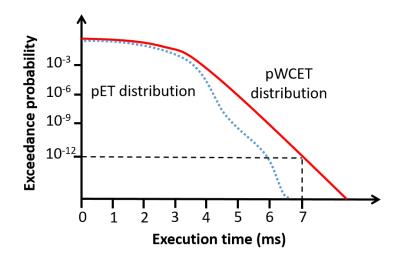

| 5.2 | pWCET distribution                                                    | 64 |

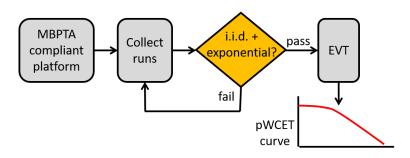

| 5.3 | Schematic of the MBPTA application process                            | 65 |

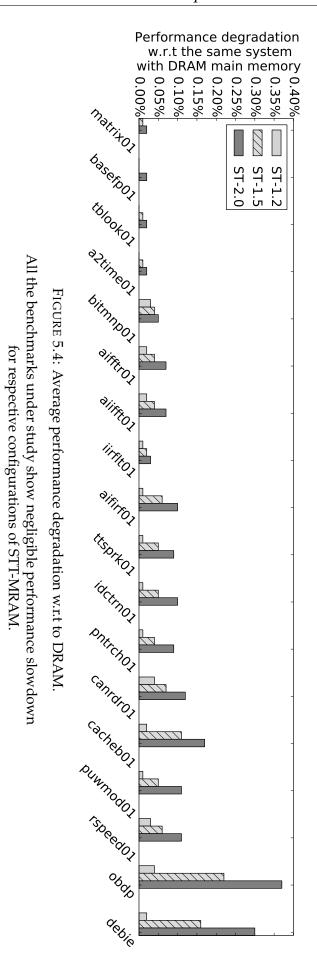

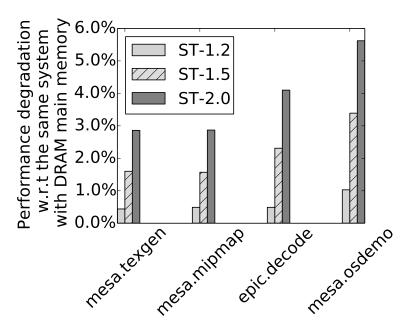

| 5.4 | Average performance degradation w.r.t to DRAM                         | 70 |

| 5.5 | Performance degradation for applications with high memory utilization | 71 |

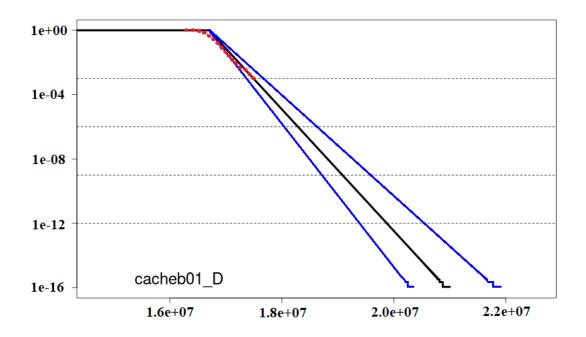

| 5.6 | pWCET distribution for cacheb01 with DRAM                             | 72 |

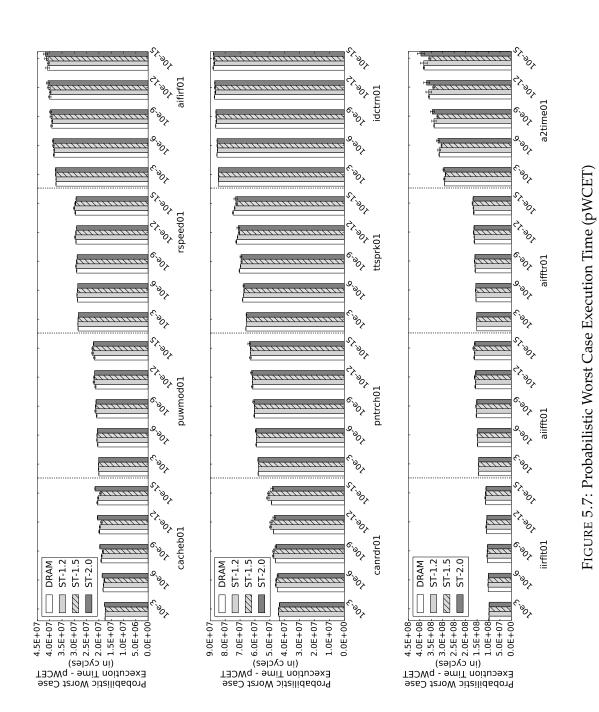

| 5.7 | Probabilistic Worst Case Execution Time (pWCET)                       | 73 |

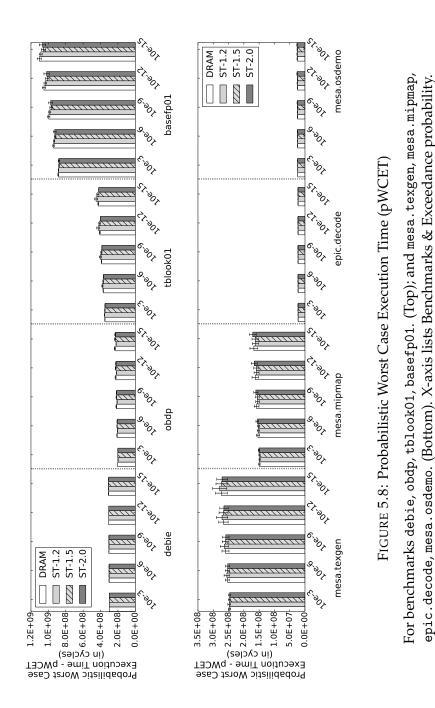

| 5.8 | Probabilistic Worst Case Execution Time (pWCET)                       | 75 |

# List of Tables

| 2.1 | DRAM vs STT-MRAM for embedded real-time systems                      | 22 |

|-----|----------------------------------------------------------------------|----|

| 2.2 | STT-MRAM simulation parameters used by previous studies .            | 24 |

| 2.3 | Comparison of DRAM and STT-MRAM main memory                          | 28 |

| 3.1 | UEABS applications used in the study                                 | 30 |

| 3.2 | Cache parameters of Sandy Bridge E class processor used in the study | 34 |

| 4.1 | Timing parameters not associated with row operation                  | 43 |

| 4.2 | Timing parameters associated with row operation                      | 44 |

| 4.3 | DRAM and STT-MRAM current parameters                                 | 46 |

| 4.4 | SPEC CPU 2006 benchmarks used in the study                           | 47 |

| 4.5 | Main memory simulator settings                                       | 48 |

| 5.1 | Next Generation Microprocessor (NGMP): Main features                 | 61 |

| 5.2 | DRAM and STT-MRAM timing parameters associated with row operation    | 62 |

| 5.3 | Benchmarks used in the study                                         | 68 |

## Chapter 1

# Introduction

Today, we live our life depending on a range of computing systems from smartphones, desktop computers, laptops, embedded systems to high performance computing (HPC) systems. Most people of the society are direct or indirect users of these systems, and such systems provide the crucial support to uphold the modern and efficient lifestyle. All of these computing systems innately incorporate some form of memory systems which are indispensable for their operation and functionality. In modern computing systems, *Memory* usually refers to the *Main Memory* of the system, which holds and provides data to perform computation. Since processor design has undergone an unprecedented development in recent years and subsequently expanded the gap between processor and memory speed, it made the memory system a vital design aspect to improve performance.

For many years, DRAM devices have been the dominant building blocks for main memory systems in most computing systems including desktop, laptop, smartphones and HPC systems. DRAM technology became matured over decades of persistent research and development. For production in mass volume, DRAM has also become a very affordable technology for deployment across all computing domains. However, for a long time researchers have so heavily concentrated on improving processor and cache design that, improving the main memory itself has been far-overlooked. As a result, we are *hitting the memory wall*, which would not be solved unless main memory technology is significantly improved.

Perhaps the greatest challenge that DRAM faces is technology scaling. Extreme scaling is forcing to shrink the size of the DRAM capacitor in an unprecedented ratio making it increasingly vulnerable to errors. Due to several design challenges, this approach of DRAM scaling is not expected to sustain forever. We need innovations, new methods and perhaps new technologies to move forward to meet next-generation computing needs.

Therefore, significant effort is invested in research and development of novel memory technologies. Among the emerging memory technologies notable candidates are Phase Change Memory (PCM), Resistive RAM (RRAM) and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), along with the 3D-stacked variants of DRAM namely Hybrid Memory Cube (HMC) and High Bandwidth Memory (HBM). Although all of these technologies have their own advantages, two of the major contenders, PCM and RRAM have significantly slower access time in comparison to DRAM, which makes them unsuitable to be considered as a main memory alternative. Since HMC and HBM are practically based on DRAM technology, STT-MRAM stands out to be most promising novel memory technology which has a true potential to be a main memory alternative. STT-MRAM is a byte-addressable, highendurance non-volatile memory, with access time comparable to DRAM. STT-MRAM is still a novel technology with a lot of scope to be improved in terms of cell size, read/write latency and energy. These improvements require research on the circuit level — involving geometry of the cells and physical properties of their composing materials.

Although STT-MRAM technology was introduced only fourteen years ago [1], STT-MRAM devices are already approaching DRAM in terms of capacity, frequency and device size. Actually, various STT-MRAM commercial products already found their way to some segments of the memory market [2]. Therefore, now is the time to perform system level research to explore usecases and identify computing domains that could benefit from this technology. System-level research can also detect key STT-MRAM limitations, and estimate their impact on overall system performance and power consumption.

Special STT-MRAM features such as intrinsic radiation hardness, non-volatility, zero stand-by power and capability to function in extreme temperatures also makes it particularly suitable for aerospace, avionics and automotive applications. Such applications often have real-time requirements – that is, certain tasks must complete within a strict deadline. Analyzing whether this *dead-line* is met requires Worst Case Execution Time (WCET) Analysis, which is a fundamental part of evaluating any real-time system. Therefore, it is also interesting to see how STT-MRAM would function and comply with the timing

requirements of real-time applications through system level analysis.

STT-MRAM technology has recently got significant attention of various major memory manufacturers; however, academic pursuance to conduct systemlevel research on this technology is still marginal, mainly due to the lack of publicly available, detailed, and reliable timing parameters of STT-MRAM. These timing parameters are essential to conduct a system level simulation. Some researchers adopt simplistic memory models to simulate main memory, but such models can introduce significant errors in the analysis of the overall system performance [3][4]. Therefore, detailed timing parameters are a *must-have* for any evaluation or architecture exploration study of STT-MRAM main memory. However, these detailed parameters are not publicly available because STT-MRAM manufacturers are reluctant to release any delicate information on the technology. Also, being a rapidly evolving technology, it is difficult even for the manufacturers to predict the exact timing for an upcoming STT-MRAM main memory device.

This thesis attempts to (1) propose a way to reliably model STT-MRAM with existing simulation infrastructures enabling academia to simulate this technology; (2) include STT-MRAM detailed timing parameters to the main repository of two most widely accepted main memory simulators; (3) evaluate system performance impact and power consumption of STT-MRAM in HPC systems; and (4) analyze the performance and WCET implication of STT-MRAM for real-time embedded systems.

## 1.1 Thesis contribution

The main contributions of the thesis are summarized below:

Demonstrate the approach to perform a cycle accurate simulation of STT-MRAM main memory, being the first to release detailed timing and current parameters of this technology from academia — essentially enabling researchers to conduct reliable system level simulation of STT-MRAM using widely accepted existing simulation infrastructure. The approach that we present converged through research cooperation with Everspin technologies Inc., one of the leading MRAM manufacturers, and it provides reliable STT-MRAM timing parameters while releasing no confidential information about any commercial products. We seamlessly incorporate our STT-MRAM timing and power analysis into the DRAMSim2 [3] memory simulator and use it as a part of the simulation infrastructure of the high performance computing systems running the SPEC 2006 benchmark suite. Our results show a fairly narrow overall performance deviation in response to significant variations in key timing parameters. The results also identify the key power component that is mostly affected with STT-MRAM.

- Include detailed STT-MRAM main memory timing parameters into the main repositories of DramSim2 [3] and Ramulator [5], two of the most widely used and accepted state-of-the-art main memory simulators. The STT-MRAM timing parameters that have originated as a part of this thesis, are till date the only reliable and publicly available timing information on this memory technology published from academia.

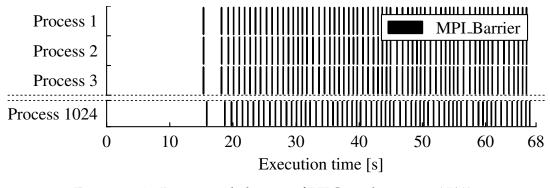

- Evaluate how HPC system performance is affected by STT-MRAM main memory. To that end, we analyze the performance of production HPC applications running on large-scale clusters with STT-MRAM main memory. Our results show that 20% slower STT-MRAM main memory device (w.r.t. DRAM) introduces only around 1% overall performance loss for most of the applications under experiment. We also perform a sensitivity analysis and repeat the simulation with pessimistic 50% and 100% slower STT-MRAM devices w.r.t. DRAM. Again, the results show a small overall performance difference between HPC systems with STT-MRAM and DRAM main memory.

- Analyze the feasibility of using STT-MRAM in real-time embedded systems by investigating STT-MRAM main memory impact on average system performance and WCET. We focus on Cobham Gaisler's NGMP architecture [6] as a representative multicore processor. In a validated simulator, we model STT-MRAM main memory with recently-published detailed timing parameters. STT-MRAM's suitability for the real-time embedded systems is validated on benchmarks provided by the European Space Agency (ESA) and EEMBC Autobench suite [7] by analyzing performance and WCET impact. To portray a broader spectrum of scenarios, we further extend the scope of our experiments executing additional benchmarks with high memory utilization from Mediabench [8]. Our results show that systems comprising STT-MRAM main memory can be analyzed with the same WCET approaches used in the

systems with conventional DRAM. This is a compelling finding, as it is fundamental to reduce STT-MRAM adoption costs, without requiring new tools that must undergo a costly qualification process [9]. In quantitative terms, our results show that STT-MRAM main memory in real-time embedded systems provides performance and WCET comparable to conventional DRAM, while opening up opportunities to exploit various advantages.

In this thesis, we target to evaluate different aspects of using STT-MRAM as the main memory across various computing platforms with a range of workloads to understand its feasibility and effectiveness as a potential future memory system. To achieve this, we extend our experiments into different domains, which requires setting-up and using appropriate simulation infrastructures for each platform under observation. It contributes significant overhead to the workload of the thesis, but it also provides a great opportunity to compare and validate that experiments carried out in different simulation infrastructure do not have significant deviation in outcome. All of the results suggest that STT-MRAM is indeed a viable alternative to DRAM from a performance and WCET perspective, while it opens up opportunities to exploit some highly desired properties such as non-volatility, zero stand-by power, and unlimited endurance.

## **1.2** Publications

In this section we list the research articles related to the thesis that have been published, those which are under submission and publications on other topics that are not a part of this thesis.

#### 1.2.1 Conferences

Kazi Asifuzzaman, Milan Pavlovic, Milan Radulovic, David Zaragoza, Ohseong Kwon, Kyung-Chang Ryoo, and Petar Radojković. *Performance Impact of a Slower Main Memory: A Case Study of STT-MRAM in HPC*. In the Proceedings of the Second International Symposium on Memory Systems (MEMSYS), Washington DC, USA, 2016. • Kazi Asifuzzaman, Rommel Sánchez Verdejo, and Petar Radojković. *Enabling a reliable STT-MRAM main memory simulation*. In Proceedings of the Third International Symposium on Memory Systems (MEMSYS), Washington DC, USA, 2017.

#### 1.2.2 Under submission

• Kazi Asifuzzaman, Mikel Fernandez, Petar Radojković, Jaume Abella and Francisco J. Cazorla. *STT-MRAM for Real-Time Embedded Systems: Performance and WCET Implications*. Under submission.

#### **1.2.3** Other publications

- Rommel Sánchez Verdejo, Kazi Asifuzzaman, Milan Radulovic, Petar Radojković, Eduard Ayguadé, and Bruce Jacob. *Main Memory Latency Simulation: The Missing Link*, in Proceedings of the Fourth International Symposium on Memory Systems (MEMSYS), Washington DC, USA, 2018.

- Milan Radulovic, Kazi Asifuzzaman, Darko Zivanovic, Nikola Rajovic, Guillaume Colin de Verdiére, Dirk Pleiter, Manolis Marazakis, Nikolaos Kallimanis, Paul Carpenter, Petar Radojković, and Eduard Ayguadé. *Mainstream vs. Emerging HPC: Metrics, Trade-offs and Lessons Learned,* in 30th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD), Lyon, France, 2018.

- Milan Radulovic, Kazi Asifuzzaman, Paul Carpenter, Petar Radojković, and Eduard Ayguadé. HPC Benchmarking: Scaling Right and Looking Beyond the Average, in Euro-Par: Parallel Processing, 2018.

### **1.3** Thesis organization

The thesis is organized as follows:

Chapter 2 provides a brief description of conventional main memory systems based on DRAM, its organization and operation along with the challenges

that this technology faces. In addition, it introduces emerging memory technologies with an in-depth discussion on STT-MRAM's technical overview, development trend, organization, opportunities and challenges.

Chapter 3 investigates the performance impact of a slower main memory (STT-MRAM) in high performance computing (HPC) systems. The chapter describes the simulation methodology, HPC workloads and results obtained from the experiments.

Chapter 4 describes the journey of estimating reliable timing and current parameters of STT-MRAM. It releases detailed main memory parameters explaining the methodologies used to estimate them. We also discuss the experimental setup, applications used and results obtained from the study.

Chapter 5 explores the feasibility of using STT-MRAM in real-time embedded systems by analyzing average system performance impact and WCET implications. This chapter further discusses the timing analysis technique of real-time systems, describes experimental setup, benchmarks used and results obtained from the experiments.

Chapter 6 discusses the related works; Chapter 7 explains possible future avenues of research in continuation to the thesis; and finally, Chapter 8 summarizes the conclusions.

## Chapter 2

# Background

In modern computing systems main memory is closely interfaced with the CPU. There can be multiple memory modules connected to the CPU through different channels. In this chapter, we describe main memory systems, their organization and operation. We discuss the current memory technology (DRAM) that dominates the main memory landscape as well as emerging memory technologies that have strong potential to be a future alternative. Since any new main memory technology is most likely to adopt DRAM standards for easy incorporation, it is very important to understand the organization and operation of DRAM in detail. We further discuss technical details of STT-MRAM, its development trend in recent years, opportunities, advantages as well as the challenges that this technology faces.

### 2.1 DRAM

DRAM is the most widely used main memory technology used till date. This technology developed over several decades through persistent research and development. Since DRAM is being supplied in mass volumes, its production cost reduced to an affordable range making it the most economical option for main memory systems.

#### 2.1.1 DRAM organization

DRAM main memory systems usually consist of three fundamental units: Memory controller, memory bus and DRAM devices organized in dual-inline memory modules (DIMMs). Modern CPUs are generally fabricated with

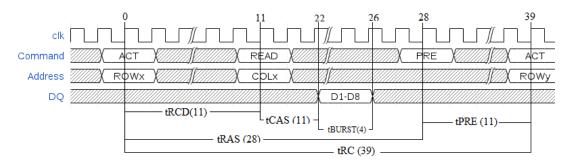

FIGURE 2.1: DRAM Read Cycle (not in scale)

an integrated memory controller. Memory channels connect DIMMs to memory controller in order to transmit data, command and addresses. DIMMs are connected through separate slots on the motherboard to facilitate easy replacement and servicing.

Any memory technology that is built on CMOS stores one bit data in a *cell*, which is considered as the basic building block of that memory. A DRAM cell is constituted of one transistor and one capacitor. In the cell, if a capacitor is fully charged, it represents logical "1" and a discharged capacitor holds the value "0". The transistor of the cell works as a switch to read/write these values. These cells are organized into array structures being connected to a *wordline* and a *bitline*. Specific wordlines are activated with *row address*. Once activated, capacitor charge (stored data) from all the cells connected to that wordline come to the row buffer through bitlines. At this point, the row buffer holds the data of the entire row that has been activated. Then the *column address* further selects a single column out of the entire row buffer and transmits the data to the physical pins of the memory to carry out a read operation. For write operations, row buffer receives data from physical pins of the memory and writes it back to the specific memory location as specified by row address and column address.

DRAM capacitors inherently suffers from *leakage current*. That is, the charge stored in the capacitors dissipates over time. For this reason, DRAM cells are periodically refreshed by the memory controller to preserve the data stored.

#### 2.1.2 DRAM operation

In order to access data from DRAM arrays, first a row needs to be *activated* (ACT). Figure 2.1 abstractly illustrates the procedure of a DRAM read cycle [10]. The memory controller transmits the ACT command along with the address of the row that is to be activated. This transfers the data of that particular row to the row buffer. Now, to carry out a *read* operation, the memory controller issues a READ command along with the column address to access the specific column in the row buffer. The selected data of the specific row and column is then placed on the data bus to be transmitted. Since DRAM read is *self-destructive*, meaning when a row is *open* (i.e. having its data in the row-buffer), it needs to be *closed* to have the data written back in the cells. This procedure of closing a row is referred as *precharge* (PRE) operation.

As you can see in Figure 2.1, the delays between issuing commands are denoted by a set of parameters such as Row to column command delay (tRCD), column access strobe latency (tCAS), row precharge (tRP) etc. These are the generic DRAM timing parameters that are used to describe different timing constraints of the device.

#### 2.1.3 DRAM challenges

The term *Memory Wall* was introduced in 1995 in a note published in Computer Architecture News [11]. Back in that time, the article implied that researchers so heavily concentrated on improving cache designs and latencytolerance techniques, that they mostly overlooked enhancing the main memory system itself. The study projected that, no matter how efficient the caches become, increasing main memory latency would always keep the processor waiting, and this situation was termed as *hitting the memory wall* which persists till today.

Another challenge is to achieve higher bandwidth with existing DRAM technology. There are two ways of increasing the bandwidth for off-chip memories: by increasing either memory channel frequencies or their bit width. Both of these approaches have particular challenges. Increasing frequency requires the memory modules to be placed in close proximity to the processor to ensure signal integrity, thus limiting the number of modules that can be used by a processor. Increasing bit width implies to have more physical pins to the processor chip and contributes to higher cost as well as significantly increases main memory power consumption.

Perhaps the greatest challenge that DRAM faces is technology scaling. Scaling appeared as a promising technique to keep up with the increasing need of capacity, performance and power reduction. To scale down the area occupied by a DRAM cell, it is imperative to take into account the area taken by the capacitor. The capacitor should be able to hold enough capacitance to swiftly set the sense amplifiers above the sensing threshold. It also needs to be strong enough to ignore the bit manipulating disturbances. Extreme scaling requires excessive reduction in the capacitor's size, making it increasingly vulnerable to errors. Smaller capacitors also possess lower retention time, requiring more frequent refresh operations causing additional power consumption, which is further aggregated for the increased capacity of scaled DRAM. Moreover, extremely scaled DRAM devices deployed in special situations such as space bound electronics, suffer from an additional challenge of being erroneously affected by the striking of a charged particle such as ions, photons or alpha particles causing a Single Event Upset (SEU). DRAM devices deployed in such systems are also a cause of continuous power consumption due its refresh requirement.

Due to several such design challenges, this approach of DRAM scaling can not sustain forever. We need innovations, new methods and perhaps new technologies to move forward to meet next-generation computing needs.

### 2.2 Hybrid Memory Cube (HMC)

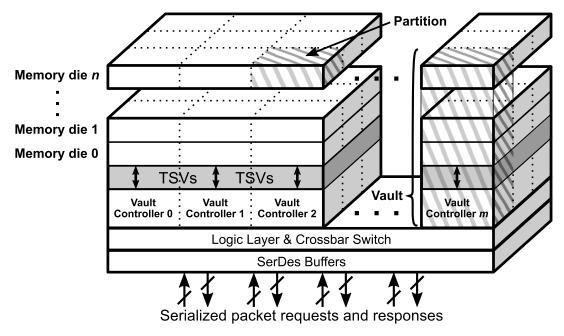

Hybrid memory cube (HMC) is a DRAM derivative that is constituted with DRAM dies stacked in a 3D fashion. HMC stacks DRAM dies in an innovative approach by interconnecting them with through-silicon vias (TSVs) to achieve higher internal bandwidth, low latency and low energy consumption [13]. Each DRAM die is distributed in *partitions* which are vertically connected with other partitions of adjacent dies forming a *vault*. A *vault* (i.e. a group of *partitions*) is operated collectively through an vault controller residing in the logic base layer (See Figure 2.2). Each vault controller is responsible for managing DRAM banks within the *vault*, thus eliminating the need of an off-chip memory controller in conventional DRAM systems. Thus, a HMC

FIGURE 2.2: Internal Structure of Hybrid Memory Cube (HMC) [12]

vault resembles a *channel* in traditional DRAM based memory systems, since it consists of all the units of a DRAM channel — a memory controller, multiple memory ranks and a data bus. This implies, that HMC is essentially a multi-channel DRAM which is capable of handling a large number of concurrent memory requests [14].

Vault controllers are connected with other HMCs or host devices with a packet based communication protocol which is implemented with a high speed serialization/deserialization circuit. This allows to achieve higher link bandwidth in comparison to synchronous bus based interfaces with the standard JEDEC protocol [13]. Packets are grouped into 16-byte elements, called *FLIT* (FLow unIT). A FLIT is the smallest data unit that can be transmitted on the high speed interface. Each transaction supports packet sizes of one FLIT (16 B) to eight FLITs (128 B), depending on the link granularity. In addition to the link granularity, HMC also implements configurable memory address granularity. HMC uses 34 bits for internal memory addressing which consists vault, bank, row, column and byte addresses. Different address mapping schemes can be used by changing the maximum payload size for a packet to take advantage of the configurable memory address granularity. This scheme can be very useful to achieve desired configurations with specific latency and throughput.

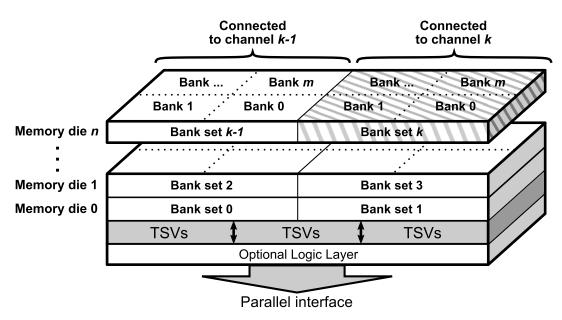

FIGURE 2.3: Internal Structure of High Bandwidth Memory (HBM) [12]

## 2.3 High Bandwidth Memory (HBM)

High bandwidth memory (HBM) is another variant of 3D-stacked DRAM which complies with the JEDEC standard. HBM is introduced in an attempt to reduce the bandwidth gap between processor's memory bandwidth requirements and actual bandwidth performance with conventional DRAM systems. The basic structure of HBM consists of a base logic die and and stacked core DRAM dies, which are interconnected by TSVs as shown in Figure 2.3. A core DRAM die has 2n-prefetch with a minimum access granularity of 16 bytes per channel. To support independent channel operations, each channel of a core DRAM die employs independent address and data TSVs with point-to-point (P2P) connections from the base die. With the semi-independent row and column command interfaces, HBM can allow RAS and CAS commands in parallel [15].

HBM has a DIMM-like system organization: the memory controller is associated with the CPU, and a point-to-point parallel interface links it to the main memory [12]. HBM implements an additional logic layer that is capable of implementing logic functions — opening an opportunity for in-memory computations. Each DRAM die of HBM is grouped into banks and connected to individual channels. HBM is generally targeted to be tightly coupled to the processor die with wide interface in order to facilitate high speed and lowpower memory operations.

### 2.4 Phase Change Memory (PCM)

Phase Change Memory (PCM) is one of the emerging non-volatile (NVM) memories which has availed considerable attention in recent years as an alternative memory technology. PCM storage cell consists two electrodes separated by a phase-change substance typically being the chalcogenide material Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) [16]. The physical state of this substance can be changed from crystalline to amorphous, each of which have distinct electrical resistance properties making it an obvious element to consider for data storage.

A PCM memory system has three fundamental operations: *READ*, *SET* and *RESET*. To *READ* data from a PCM cell, small sensing current is applied through it. The current senses the resistance state of the GST to get one bit of data ("0" or "1"). To *RESET* a PCM cell a strong current pulse is applied for a short duration. The strong current pulse quickly increases the temperature of the GST material to the melting point and subsequently programming it in the amorphous state (representing "0"). To *SET* a PCM cell, a programming current pulse is applied for a longer period to program the cell from amorphous state to crystalline state (representing "1"). While the *READ* and *RE-SET* operations are relatively faster (tens of nanoseconds), the *SET* operation is significantly slower (hundreds of nanoseconds). Therefore, for writing in a PCM based memory system, both *SET* and *RESET* operations will appear but the average write latency will only be limited by the significantly slower *SET* operation [17].

PCM can essentially have a density advantage over DRAM having the possibility of using multiple states of crystallization to hold muti-bit data in one cell [18]. However, despite of having several advantages, PCM suffers from low access latency, which makes it impractical to use as the main memory of high performance computing systems. In addition, having significantly low endurance suggests, PCM may not be a viable option for commercial systems.

PCM has also been reportedly used to construct **3D-XPoint** memory [19]; developed jointly by Intel and Micron technology. As the name suggests, it has a transistor-less 3D structure, where the data resides in the intersection of perpendicular wires. Current is applied to these wires in order to access the data that is stored in the corresponding intersection (i.e. cell). 3D-Xpoint is being projected as superior storage class technology and less likely as a main

memory alternative.

### 2.5 Resistive RAM (RRAM)

Resistive RAM (RRAM) is another potential candidate for future memory systems. An RRAM cell is typically constituted as a two terminal device with a simple metal–insulator–metal structure. RRAM cells are operated by voltage driven resistance switching of the metal oxide insulator between the low resistance state (LRS) and the high resistance state (HRS). This is usually done by creating and dissolving the conductive filament (CF) that has oxygen vacancies [20].

Like PCM, three main operations are usually performed on an RRAM cell: *SET*, *RESET* and *READ*. The *SET* operation is performed by applying a positive voltage between the top and bottom metal layers to transform the cell from the HRS to LRS [21]. In order to limit the current to perform the *SET* operation, a transistor is used. This constitutes or extends a filament of oxygen vacancies from the bottom metal layer to the top metal layer, thus decreasing RRAM cell resistance. Similarly, a negative voltage is applied to perform a *RESET* operation which transforms the cell from LRS to HRS by dissolving the conductive filaments. A *READ* operation is performed to detect the current state (i.e. data) of the cell by applying a sensing voltage which is weak enough not to change the resistance of the cell [22].

RRAM is highly scalable; and having low read/write energy makes it a viable alternative of storage class memories. Recent enhancements improving access latencies could suggest to consider it as a main memory alternative. However, RRAM access time is still significantly slower than other emerging non-volatile memories such as STT-MRAM. It also lacks comparable endurance w.r.t DRAM and STT-MRAM.

### 2.6 STT-MRAM

#### 2.6.1 Technology overview

Research exploring the magneto-resistance caused by the spin polarized current can be tracked back to the '90s [23][24][25]. However, significant scientific efforts of optimizing and applying this phenomenon to create a novel non-volatile memory is a relatively new approach. Only around fourteen years ago, in 2005, Hosomi *et al.* [1] presented a non-volatile memory utilizing spin transfer torque magnetization switching for the first time. In the following years, there has been a notable dedication of memory manufacturers researching this novel non-volatile memory technology.

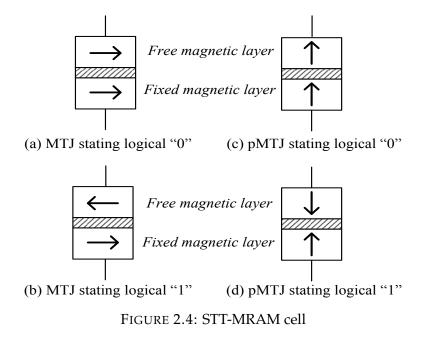

The storage and programmability of STT-MRAM revolve around a Magnetic Tunneling Junction (MTJ). An MTJ is constituted by a thin tunneling dielectric being sandwiched between two ferro-magnetic layers. One of the layers has a fixed magnetization while the other layer's magnetization can be flipped. As Figure 2.4 depicts, if both of the magnetic layers have the same polarity, the MTJ exerts low resistance, therefore representing a logical "0"; in case of opposite polarity of the magnetic layers, the MTJ has a high resistance and represents a logical "1". In order to read a value stored in an MTJ, a low current is applied to it. The current senses the MTJ's resistance state in order to determine the data stored in it. Likewise, a new value can be written to the MTJ through flipping the polarity of its free magnetic layer by passing a large amount of current through it [26].

A more recent variation of MTJ is perpendicular MTJ (pMTJ). In contrast with the conventional MTJ, the poles of pMTJ magnetic layers are perpendicularly aligned with the plane of the wafer; see Figure 2.4 (c) and (d). In 2010, Ikeda et al. presented pMTJ for the first time and demonstrated that it requires much lower write current than the conventional MTJ [27]. Recently, Janusz et al. has reported to achieve good write performance with pMTJ down to 11 nm device size [28].

Other variants of STT-MRAM cell design incorporated advanced 2T-2MTJ, 3T-2MTJ and 4T-2MTJ cells in a pursuit to improve performance and energy efficiency [29][30][31].

#### 2.6.2 Development trend

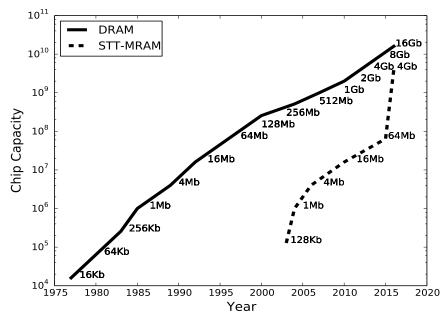

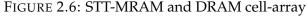

Around fourteen-years-old, STT-MRAM is rapidly catching up with the mature DRAM technology. Figure 2.5 shows an approximate timeline of DRAM and STT-MRAM chip capacity development, and clearly illustrates the diminishing gap between these two technologies.

Development of DRAM devices started back in the '70s, and by the year 2003, DRAM chip capacity could reach upto 256Mb. Around at the same time, the first reported STT-MRAM chip appeared with the capacity of 128Kb, which is a 2000× smaller capacity than DRAM (note the logarithmic scale of the vertical axes). DRAM chip capacity gradually increased and reached 16Gb by the year 2016. Following a sharp incline, STT-MRAM chip capacity gradual to 4Gb by the same year [32], reducing the capacity gap between these two technologies from  $2000 \times in 2003$  to only  $4 \times in 2016$ .

Promising development has also been made improving STT-MRAM's bus frequency. While the first generation of DDR SDRAM had 133Mhz bus frequency, present day DDR3 and DDR4 compatible STT-MRAM are catchingup with the frequencies of the high-end DRAM devices [33].

The STT-MRAM device improvements come mainly from the enhancements in the MTJ design. With the recent variation of pMTJ, different memory manufacturers have demonstrated a fierce competition to achieve the smallest device size for MTJs. In 2011, Samsung developed pMTJ at 17nm. In 2016, IBM

FIGURE 2.5: DRAM and STT-MRAM capacity growth in years

demonstrated an 11nm STT-MRAM junction. By the end of the year 2016, IMEC researchers reported to develop world's smallest pMTJ at 8nm.

An intensified effort in STT-MRAM research by the memory manufacturers may indicate that a revolution with STT-MRAM memory technology is imminent, and we can expect to see a lot of exciting developments with this memory technology in the near future.

#### 2.6.3 STT-MRAM opportunities

Some of the STT-MRAM main memory advantages were already analyzed in the context of other non-volatile memory technologies and other application domains [34] [35] [36]. Here, we briefly summarize the ones that are of main interest in the HPC domain.

#### **DRAM** refresh

In a DRAM cell, the information is stored as a charge in small capacitors that have to be refreshed periodically in order to preserve the content. DRAM refresh degrades system performance because it interferes with application memory accesses. Also, refresh increases energy consumption, directly, because refresh operations consume energy, and indirectly, because degradation of system performance increases execution time, and therefore overall energy consumption. Performance and energy overheads of DRAM refresh have been deemed insignificant for long, but with the increasing frequency and size of DRAM devices, refresh becomes an important factor of memory performance and energy consumption. In state-of-the-art 32 Gb DRAM devices (specified in the DDR4 standard), refresh contributes to more than 20% of the DRAM energy consumption and degrades the memory bandwidth by more than 30%. In the upcoming 64 Gb devices, it is estimated that refresh will degrade memory throughput and increase the energy consumption by more than 50% [37][38]. STT-MRAM is a non-volatile technology and, therefore it requires no refresh. Thus, a great performance and energy advantage over the DRAM technology can come from resolving the memory refresh problem.

#### Memory errors

One of the leading causes of hardware failures in modern HPC clusters are main memory DRAM errors [39][40][41][42]. In the future, DRAM errors will pose an even larger threat to the reliability of HPC systems. First, the number of memory errors will increase because the amount of DRAM in HPC systems keeps growing at a consistent rate [40]. Another source of increasing the memory error rate is the scaling of the DRAM technology [43]. DRAM cells are getting smaller and they hold a decreasing amount of charge, which makes them more vulnerable to any disturbance and data corruption. Also, the distance between DRAM elements is already so small that electromagnetic coupling causes undesired interactions between the adjacent cells. STT-MRAM is a non-volatile technology that mitigates the transient faults (caused by magnetic or electrical interference) that account for a significant portion of the overall memory faults. Since STT-MRAM technology would improve the reliability of the memory systems, the complexity and overheads of the contemporary error correction approaches can be reduced.

Clearly, STT-MRAM is not a failure-free technology. However, its retention failures (stochastic in nature), can be efficiently controlled with proper ECC mechanisms [44]. A Recent study of Pajouhi *et al.* [45] analyzes the interactions between device parameters, bit-cell level parameters and different ECCs to optimize the robustness and energy-efficiency of a STT-MRAM cache. A compelling follow up would be to extend this work on STT-MRAM main memory.

### 2.6.4 STT-MRAM special advantages

In this section, we make a qualitative analysis of STT-MRAM specific features. In particular, intrinsic radiation hardness, non-volatility, zero standby power and the capability to function in extreme temperatures offer a great opportunity to explore its usability in real-time embedded systems in aerospace and automotive domains, where computer systems must operate with guaranteed behavior in harsh environments under stringent constraints. A summary of the main differences between DRAM and STT-MRAM is provided in Table 2.1.

#### **Radiation hardness**

A *Single Event Upset (SEU)* occurs when the state of a memory cell or transistor is erroneously changes by the striking of a charged particle such as ions, photons or alpha particles [46]. Continuous scaling of CMOS devices has further amplified the chances of being affected, which is a serious concern for DRAM and SRAM main memories and caches, which account for a large fraction of the silicon in computing systems.

Microelectronic devices deployed in space are particularly vulnerable to such events. For instance, it has been reported that soft error rates due to radiation grow by a factor of  $650 \times$  when moving from sea level to 12,000m of altitude [47], a usual altitude for commercial planes. Radiation in the space further exacerbates the issue due to the lack of the Earth atmosphere to mitigate radiation. These phenomena lead to increased bit upset rates that require expensive coding and scrubbing techniques to guarantee error correction.

STT-MRAM offers a promising solution to this problem as it replaces chargebased storage with Magnetic Tunnelling Junction (MTJ), which stores data in the form of magnetic resistance that is intrinsically tolerant to radiation.

| Feature               | DRAM | STT-MRAM |

|-----------------------|------|----------|

| Radiation-hard        | -    | +++      |

| Standby power         | -    | +++      |

| Temperature tolerance | +    | +++      |

| Storage capacity      | ++   | ++       |

| Access speed          | +++  | ++       |

| Endurance             | +++  | +++      |

TABLE 2.1: DRAM vs STT-MRAM for embedded real-time systems

STT-MRAM memory chips have reportedly been deployed on space bound satellites [48].

#### Zero standby power

Electronic devices in the aerospace and automotive domains are usually deployed once to be operated for a long period of time without regular maintenance. Due to its non-volatility, STT-MRAM also ensures that no data is lost if an unexpected power down or voltage drop takes place. Implementing appropriate measures, the operations can resume from the same point as it was interrupted. Also, STT-MRAM having long term data retention with zero standby power is set to offer great advantage from the power consumption perspective. For instance, many instruments in space missions are operated at a given (low) frequency, taking pictures or measurements every second or minute. STT-MRAM allows activating and deactivating systems with negligible power cost, without requiring any form of backup space.

#### **Operational temperature**

STT-MRAM's another crucial feature is being operational under an extended range of temperatures. One of the STT-MRAM manufacturers states that a Grade 1 qualified MRAM will contain data for 20 years being operational under extreme temperatures ranging from -40C to 125C. [49]. This makes STT-MRAM suitable to be used both in aerospace (extreme cold) and automotive (occasionally extreme hot) parts.

#### Integrated memory

Having comparable speed and density to DRAM, with unlimited endurance and long retention time, STT-MRAM really opens up the opportunity to use it as single memory replacing DRAM and long term storage from the conventional real-time embedded systems.

#### 2.6.5 STT-MRAM challenges

Being a promising memory technology with a lot of potential, STT-MRAM also faces specific challenges on its way to be a future memory alternative. There are simulation challenges which correspond to the struggle of performing a reliable simulation of the technology, and there are commercial challenges, which refer to the obstacles that is preventing STT-MRAM to appear in the market as a competing main memory technology.

#### Simulation challenges

To find suitable use cases for STT-MRAM main memory, it is essential to conduct reliable simulation of STT-MRAM. However, simulation of STT-MRAM main memory with detailed timing parameters has been a challenging task due to the unavailability of reliable estimations of timing and power consumption parameters. Only three studies simulate and analyze STT-MRAM main memory. Table 2.2 summarizes timing parameters used in these studies — parameters of main memory devices (DRAM and STT-MRAM) along with *before main memory device* latency.

Meza *et al.* [50] use a cycle-accurate DDR3-DRAM memory simulator and estimate STT-MRAM parameters based on Fujitsu's 16kb test-chip built in 2010 with  $0.13\mu$ m technology [53]. The authors assume, that t<sub>WR</sub> and t<sub>RCD</sub> parameters for STT-MRAM main memory would change on a range of twice as slow to twice as fast with respect to DRAM. In our opinion, it is difficult to estimate a reasonable assessment of STT-MRAM main memory using such a wide range of values for key latency parameters. The study also does not provide any information about latency components before main memory device, making it it infeasible to repeat the study or to quantify the impact of

| math                               | memory <i>aevice</i> latence                      | y is not valida                 | ited versus rea                                 | analysis.                                                                                                             | <i>mun menory deoice</i> latericy is not vandated versus real systems, or it is directly offitted from the simulation intrastructure analysis. |

|------------------------------------|---------------------------------------------------|---------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                                                   | Memory access latency           | ss latency                                      |                                                                                                                       |                                                                                                                                                |

| Study                              | Before                                            | Mai                             | Main memory device                              | rice                                                                                                                  | Observations                                                                                                                                   |

|                                    | memory de-<br>vice                                | DRAM                            | STT Read                                        | STT Write                                                                                                             |                                                                                                                                                |

| Meza et. al<br>[ <mark>50</mark> ] | l No<br>information                               | Cycle<br>accurate<br>simulation | twr $t_{ m RCD}$ : $0.5 \leqslant \overline{l}$ | $\begin{array}{ll} t_{\rm WR} & \text{and} \\ t_{\rm RCD}: \\ 0.5 \leqslant \frac{STT}{DRAM} \leqslant 2 \end{array}$ | - Latency before main memory: No info - Wide range of $t_{\rm WR}$ and $t_{\rm RCD}$ values.                                                   |

| Kultursay et.<br>al [51]           | . Row buffer hit: 30 ns<br>Row buffer miss: 50 ns | t: 30 ns<br>iss: 50 ns          | +0 ns                                           | +10 ns                                                                                                                | <ul><li>Main memory latency: No source</li><li>Obsolete STT parameters.</li></ul>                                                              |

| Suresh et. al<br>[52]              | No information                                    | nation                          | 35 ns                                           | 35 ns                                                                                                                 | <ul> <li>Latency before main memory: No info</li> <li>DRAM latency: No info</li> </ul>                                                         |

TABLE 2.2: Previous studies use obsolete STT-MRAM parameters or the parameters with no available source. The before

the STT-MRAM  $t_{WR}$  and  $t_{RCD}$  parameters to the *overall* main memory access latency.

Kultursay *et al.* [51] compare DRAM and STT-MRAM performance by simulating fixed latencies for row buffer hit (30 ns) and conflict (50 ns) without specifying the breakdown or inclusion of the latency components for this delay. The source of these estimations are not revealed in the paper. The authors also state that they modified CACTI to model STT-MRAM, however there is no information how this modification was formulated, taking into account the fact that CACTI is widely used as a cache memory simulator, but least likely to be used to simulate main memories. The study also proposes an additional 10 ns penalty for STT-MRAM write, which as an obsolete parameter used in early STT-MRAM designs. Practically all recent studies and commercial products suggest STT-MRAM cells with symmetrical (same latency) read and write operations [30][31][54].

Suresh *et al.* [52] simulate STT-MRAM read and write operations with a fixed latency of 35 ns, obtaining these estimation from ITRS report, 2013 [55]. The study provides no information about the latency components before main memory device, or DRAM device latencies.

To summarize, previous studies use obsolete STT-MRAM timing parameters or parameters with no reliable source. In addition to this, the before main memory device latency is not validated versus real systems, or it is directly omitted from the simulation infrastructure analysis. STT-MRAM main memory evaluation is incomplete without cycle-accurate simulation with reliable timing parameters. The lack of detailed timing parameters is also the main problem for any STT-MRAM microarchitectural exploration, improvement and evaluation.

#### **Timing parameters: Dead ends**

Our search for reliable STT-MRAM timing parameters was not straightforward; it lasted three years and involved collaboration with two STT-MRAM memory manufacturers.

Initially, we planned to simulate STT-MRAM main memory by using the NVMain simulator [56]. After analyzing NVMain STT-MRAM timings, we noticed that several key parameters had values that differ significantly from

our understanding of STT-MRAM main memory, as well as the timings provided by manufacturers. For example, the NVMain configuration file for a 4GB MRAM<sup>1</sup> listed tRAS (row access strobe) to be 0. Whereas, in DDR*x* standard, tRAS is constituted by tRCD, tCAS, tBURST and the delay for the data restoration which corresponds to 28 cycles in DDR3-1600. In addition, tRCD was set to 14 cycles with an explanation to have it derived from the Everspin MR2A16A product datasheet. We could not verify this derivation to be correct. To clear up the confusion, we contacted the NVMain developers asking for a clarification and source of their STT-MRAM parameters, but got no reply. Since we were unable to verify how these timing parameter values were formulated and we had some serious doubts about their validity, we had to classify the NVMain STT-MRAM main memory parameters as unreliable and discard them from being used in our experiments.

A couple of studies [57][51] simulate STT-MRAM main memory by integrating publicly available STT-MRAM cell parameters into the CACTI [58] cache simulator. Using a *cache simulator* to estimate timing and energy parameters of a *main memory* is not a straightforward approach. Main memory devices have higher capacity by several orders of magnitude, different organization (DIMMs, ranks, banks, chips, rows, columns) and interface (e.g. row buffer), which would yield completely different parameter values. We failed to find any information on how CACTI could be adopted for main memory simulation, and the studies that use this approach provide no information on how they bridged the gap between cache and main memory simulation.

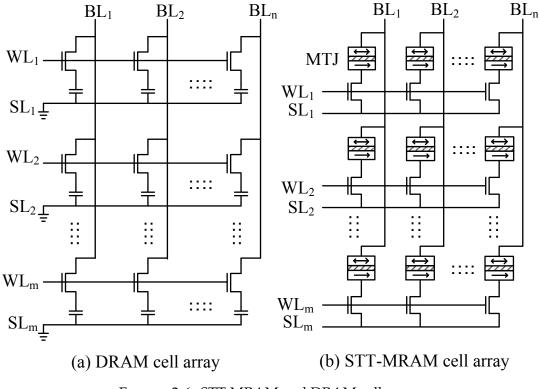

#### Our approach

Although STT-MRAM is catching-up rapidly in terms of cell size, capacity and frequency, DRAM still has a great advantage — it is a standardized plugand-play device. Today, we have various DRAM and CPU manufacturers and OEMs, and we have a full compatibility — we can connect any CPU (Intel, AMD, ARM-based) to any DRAM (Samsung, Micron, Hynix) as long as they follow the same DDR*x* standard. Although we probably take this for granted, it is very important to understand that this standardization requires a tremendous effort and it is done only for mainstream products (technologies) with volumes that justify the investment.

<sup>&</sup>lt;sup>1</sup>NVMain configuration file describes the parameters of the 4GB MRAM device. This configuration file was released in 2015, even before 64MB devices were manufactured.