ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons: http://cat.creativecommons.org/?page\_id=184

**ADVERTENCIA.** El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons: http://es.creativecommons.org/blog/licencias/

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

# A versatile framework for the statistical characterization of CMOS time-zero and time-dependent variability with array-based ICs

Author:

Javier Díaz Fortuny

Supervisors:

Dr. Javier Martín Martínez

Dr. Rosana Rodríguez Martínez

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Telecommunication Engineering

in the

Reliability of Electron Devices and Circuits group (REDEC)

Department of Electronic Engineering

July 2019

The undersigned, Dr. Javier Martín Martínez and Dr. Rosana Rodríguez Martínez, Associate Professors of the Electronic Engineering Department (Engineering School) of the *Universitat Autònoma de Barcelona*

#### **CERTIFY:**

that the thesis entitled "A versatile framework for the statistical characterization of CMOS time-zero and time-dependent variability with array-based ICs" has been written by the Ph.D candidate **Javier Díaz Fortuny** under their supervision, in fulfilment of the requirements for the Ph.D degree in Electrical and Telecommunication Engineering.

#### Author:

## Supervisors:

Mr. Javier Díaz Fortuny

Dr. Javier Martín Martínez

Dr. Rosana Rodríguez Martínez

You do not really understand something unless you can explain it to your grandmother.

Albert Einstein

# Agradecimientos

Me gustaría comenzar mi tesis doctoral dedicando unas palabras de agradecimiento a todas aquellas personas que me han acompañado durante estos cuatro años de travesía.

En primer lugar, querría dar las gracias a mis directores de tesis, el Dr. Javier Martín Martínez y la Dra. Rosana Rodríguez Martínez, por guiarme y orientarme durante el largo camino recorrido durante mi tesis doctoral. Vuestro apoyo, ayuda e ideas compartidas a lo largo de estos cuatro años han sido imprescindibles para llegar a la culminación de esta tesis. También me gustaría agradecer la confianza depositada en mí a la Dra. Montserrat Nafría Maqueda, quien me ofreció la oportunidad de realizar mis estudios de doctorado dentro del grupo de investigación REDEC en el Departamento de Ingeniería Electrónica de la Universidad Autónoma de Barcelona.

Por otro lado, quisiera dar las gracias encarecidamente a mis compañeros de despacho, así como a todos los miembros del grupo REDEC. En especial quiero destacar a Alberto Rodríguez, Carlos Couso, Oscar Súchil, Miquel Moras, Cristian Herrojo y Marcos Maestro. Cada uno de vosotros, vuestra compañía y apoyo durante estos años, ha marcado un punto de inflexión imposible de olvidar. Nuestras discusiones, chascarrillos, bromas y excentricidades perdurarán en mi memoria para siempre. También quisiera extender mi gratitud a los miembros del Departamento de Ingeniería Electrónica por todos los buenos momentos que hemos compartido, en especial a Javier Hellín por su ayuda professional con el diseño gráfico de la tesis doctoral.

Una parte muy importante de esta tesis corresponde a la colaboración mantenida con el Instituto de Microelectrónica de Sevilla. En especial me gustaría destacar todo el apoyo recibido por parte de Rafael Castro López, Francisco V. Fernández y Elisenda Roca. Las innumerables horas invertidas en el laboratorio de caracterización y la generación de algoritmos y setups de medida, que culminaron con una curva  $I_{DS}$ - $V_{GS}$ , junto con las intensas discu-

siones llevadas a cabo a lo largo de estos años, han contribuido enormemente a crear una relación profesional y personal difícil de superar. Por descontado, también me gustaría agradecer sinceramente a los que fueron mis compañeros durante mis estancias en Sevilla, en especial a Antonio Toro, Pablo Sarazá y Fabio Moreira. Nuestras discusiones e interminables skypes han contribuido notablemente al desarrollo de esta tesis doctoral.

También quisiera extender mis agradecimientos a Víctor Van Saten y Hussam Hamroch con quienes trabajé conjuntamente durante mi estancia de investigación en el Karlsruher Institute Für Technologie en Alemania. Una experiencia enriquecedora en la que dedicamos largas noches a la creación de algoritmos de procesado de datos e interesantes discusiones que han contribuido a mi crecimiento como investigador. Quisiera también transmitir mi mas sincero agradecimiento a todos los compañeros del grupo de investigación Device Reliability and Electrical Characterization group en IMEC, Bélgica. En especial a Dimitri Lintern, Erick Bury, Ben Kaczer, Marko Simicic, Md Nur Kutubul Alam y Geert Hellings. Vuestra acogida me permitió integrarme en vuestro grupo de investigación como si fuera uno más y adquirir nuevos y valiosos conocimientos. Asimismo me gustaría agradecer el apoyo y colaboración recibidos por el grupo de investigación HIPICS de la Universidad Politécnica de Catalunya durante la fase de diseño del chip.

Antes de terminar, quisiera dedicar todo el trabajo realizado a lo largo de mi vida académica a mi familia, en especial a mi madre Amalia Fortuny y a mi padre Francisco Javier Díaz por apoyarme y guiarme desde muy pequeño para continuar avanzando y ser competitivo. A Pedro Sánchez y a mi hermana Meritxell Díaz por apoyarme durante todos estos años de estudio. También quiero dedicar una mención especial a mis abuelos, Carme Bartolomé y Josep Fortuny, por impulsarme cada día a estudiar y creer siempre que lograría mis objetivos. Por último, quiero agradecer a mis suegros, Carmen Hinojosa y Herminio Albaladejo, su constante e inestimable apoyo y los ánimos que me han dado durante todos estos años. A todos ellos, gracias.

Finalmente, y desde lo más profundo de mi corazón, me gustaría otorgar mi más sincero agradecimiento a mi esposa, Gloria Albaladejo. De no haber estado a mi lado, con tu amor y apoyo incondicionales, nunca habría llegado tan lejos. No hay palabras para describir mi gratitud por todos estos años y por toda la vida que nos queda por vivir juntos. Te amo.

Javier Díaz Fortuny Barcelona, Julio 2019.

# Acknowledgements

I would like to start my PhD thesis extending a word of thanks to all the people who have supported me during these past four years.

Firstly, I would like to thank my thesis directors, Dr. Javier Martín Martínez and Dr. Rosana Rodríguez Martínez, for guiding me throughout my PhD thesis. Your support, help and ideas during these past four years have been indispensable for the completion of this thesis. I would also like to take this opportunity to recognize the trust placed in me by Dr. Montserrat Nafría Maqueda, who offered me the opportunity to carry out my PhD studies within the REDEC group in the Engineering Department in the Autonomous University of Barcelona.

Secondly, I would like to thank my fellow office colleagues, as well as to all REDEC group members. I would specially like to pay tribute to Alberto Rodríguez, Carlos Couso, Oscar Súchil, Miquel Moras, Cristian Herrojo and Marcos Maestro. Each one of you, your companionship and support, have set an inflexion point impossible to forget. Our discussions, jokes, and eccentricities will forever live in my memory. I would also like to extend my thanks to all Electronic Engineering Department members for all the good moments shared, especially to Javier Hellín, for his professional help with the graphic design of my PhD thesis.

A very important part of this thesis corresponds to the collaboration with the Microelectronic Institute of Seville. I would specially highlight the support I have been given by Rafael Castro López, Francisco V. Fernández and Elisenda Roca. The countless hours invested in the characterization laboratory and the algorithm and measurement setups generation, which led to a  $I_{DS}$ - $V_{GS}$  curve, together with the intense discussions carried out during these years, have greatly contributed to create a professional and personal relationship difficult to top. It goes without saying that I sincerely thank my fellow colleagues during my stay at Seville, especially Antonio Toro,

Pablo Sarazá and Fabio Moreira. Our debates and endless skypes contributed significantly to the development of this PhD thesis.

I would also like to extend my gratitude to Víctor Van Saten and Hussam Hamroch, whom I worked with during my research stay at Karlsruher Institute Für Technologie in Germany. A rewarding experience in which we dedicated long nights to the creation of processing algorithms and maintained interesting debates, which have contributed to my growth as a researcher. I would also like to give my most sincere thanks to all the colleagues in the Device Reliability and Electrical Characterization group at IMEC, Belgium. Especially, to Dimitri Lintern, Erick Bury, Ben Kaczer, Marko Simicic, Md Nur Kutubul Alam and Geert Hellings. Your warm welcome allowed me to become part of your reasearch group, as well as to acquire new and valuable knowledge. Likewise, I would like to thank all the support and collaboration received by the HIPICS research group from the Politechnic University of Cataluña (UPC) during the design phase of the chip.

Before I finish, I would like to dedicate of the work done throughout my academic life to my family, especially to my mohter Amalia Fortuny and my father Francisco Javier Díaz, for supporting and guiding me since my early years in life to make further progress and to be competitive. To Pedro Sánchez and my sister Meritxell Díaz for supporting me throughout all these years of study. I would also like to make a special reference to my grandparents, Carme Bartolomé and Josep Fortuny, for pushing me every day to study and always believe that I would achieve my goals. Last but not least, I want to thank my in-laws, Carmen Hinojosa and Herminio Albaladejo, for their constant and invaluable support and for all their encouragement throughout the years. To all of them, thank you.

Finally, and from the bottom of my heart, I would like to express my sincerest thanks to my dear wife, Gloria Albaladejo. Had you not been by my side, with unconditional love and support, I would have never come this far. I cannot emphasize enough my gratitude for all these years and for those still to come. I love you.

Javier Díaz Fortuny Barcelona, Julio 2019.

## **Preface**

Since the invention in 1960 of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET), the CMOS semiconductor industry has invariably invented new feats to progressively reduce the minimum gate length, from the micrometer scale ( $\approx 10 \mu m$ ) to the current 7-14-nm gate lengths or the new 5-nm technology node predicted to be manufactured in 2020-2021, all with the aim of fabricating more reliable devices and even more advanced circuits and systems, with billions of transistors per chip.

With all the benefits that transistor size scaling brings to power, area and performance, approaching the atomic scale poses, due to the very discreteness of matter, an important peril: the increase of variations of the transistor's intrinsic performance, thus critically compromising the fundamental reliability of the fabricated devices and circuits. In this way, variations of fabricated transistor parameters, like for instance threshold voltage or mobility, as well as their degradation during circuit functionality, have become an increasing concern in nanometer integrated circuit design. Moreover, a significant increase of gate leakage current has emerged due to the scaling in the thickness of the transistor's insulator. In this scenario, to increase performance and reliability of the fabricated devices, new and more complex stack materials have been introduced, such as silicon oxynitride (SiON), High-K Metal gate insulators (HKMG) and new device geometries like FinFETs, FDSOI or MuGFETs have emerged in ultra-scaled technology nodes to continue with the scaling trend and have better control of the short channel effects.

The variability in the transistor parameters, stochastic by nature, must be massively characterized in order to capture those variations with a representative and sound statistical sampling. Variability sources are divided in two different types: first, the time-zero variability, typically known as process variability which occurs during the fabrication process and consists in a permanent either random or systematic, shift of the device parameters; second, the time-dependent variability, which occurs during device or circuit operation over time and includes transient effects like Random Telegraph Noise, and degradation mechanisms or aging effects, like Hot Carrier Injection, Bias Temperature Instability, Time Dependent Dielectric Breakdown, Stress Induced Leakage Current, etc., which are potential sources of device and IC variability that can lead transistors to a progressive degradation or to a permanent failure.

In order to reduce or mitigate variability effects, novel variability-aware circuit design techniques are required to assess the combined impact of time-zero and time-dependent variability in advanced technology nodes. Variability-aware techniques utilizes accurate compact models, which are based in statistical characterization of individual MOSFET devices. In this regard, providing statistically accurate characterization of time-zero and time-dependent variability effects in modern CMOS technologies has, therefore, become a key step in the path towards attaining truly reliable integrated circuits.

In this context, this thesis, structured in 4 chapters, will contribute to the characterization and lifetime prediction of nanometer CMOS technologies through a thorough study of extensive statistical data samples. To do so, issues related to typical serial characterization techniques, which require months or even years of continuous non-stop device testing, are overcome thanks to a novel and versatile array-based IC chip design in conjunction with a full-custom characterization framework. These two key elements, the IC and the framework, can effectively be utilized to statistically characterize the impact of different device variability sources in nanometer-scale MOSFETs while significantly and outstandingly reducing the required characterization time.

To gently introduce the reader to the material, in the first chapter of this thesis, a brief discussion of the most relevant time-zero and time-dependent variability phenomena in today's fabricated nano-MOSFETs is provided. The role that the interface states, present in the transistor insulator, plays in the device variability is also explained here. Moreover, the necessary requirements for both a capable array-based IC design and a trustworthy measurement framework for the statistical device characterization will be described. Finally, a state-of-the-art review of the pros and cons of the most recent array-based ICs reported in the literature, for the statistical characterization of variability phenomena, is presented highlighting the basic but important concept of parallel stress in IC chips.

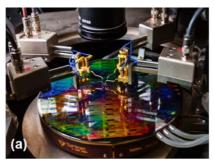

In the context of getting enough statistical data to accurately characterize transistor variability while avoiding non-feasible, on-wafer serial device characterization times, the second chapter will describe the design of a novel array-based IC chip, named ENDURANCE, by which time-zero and time-dependent variability effects can be both observed and measured. To significantly cut down the time for aging phenomena characterization, the versatility of the ENDURANCE chip hardware, guaranteeing massively parallel aging testing, will be described.

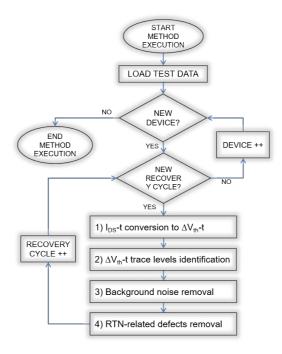

The third chapter describes an innovative and automated measurement framework, named TARS, whose focus is to provide statistical measurements to help CMOS analog and digital circuit designers to fight against variability phenomena. Moreover, a novel and smart parallel aging testing technique that introduces a significant reduction of the on-wafer serial aging tests from years to hours will be described.

In chapter four, all data collected through the statistical measurements conducted using TARS sofware have been used to study the effects of time-zero and time-dependent variability phenomena towards attaining a precise prediction of the expected technology lifetime. Moreover, several novel methodologies utilized for the extraction of transistor model parameters intended for accurate circuit simulation will be also presented and described.

Finally, the most relevant conclusions of the work presented in this thesis are summarized.

# Publications related to this thesis

#### International journal papers as first author:

- J. Diaz-Fortuny, P. Saraza-Canflanca, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, F. V. Fernandez and M. Nafria, "Flexible Setup for the Measurement of CMOS Time-dependent Variability with Array-based Integrated Circuits." in IEEE Transactions on Instrumentation and Measurement, March 2019. DOI: 10.1109/TIM.2019. 2906415 Impact factor (2017): 2.794. Quartile: Q1.

- J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, R. Castro-Lopez, E. Roca, X. Aragones, E. Barajas, D. Mateo, F. V. Fernandez and M. Nafria, "A Versatile CMOS Transistor Array IC for the Statistical Characterization of Time-Zero Variability, RTN, BTI, and HCI," in IEEE Journal of Solid-State Circuits, vol. 54, no. 2, pp. 476-488, February 2019. DOI: 10.1109/JSSC.2018.2881923. Impact factor (2017): 4.075. Quartile: Q1.

- 3. J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, R. Castro-Lopez, E. Roca, F. V. Fernandez and M. Nafria, "A Smart Noise- and RTN-Removal Method for Parameter Extraction of CMOS Aging Compact Models" in Solid-State Electronics (Elsevier), March 2019. DOI: 10.1016/j.sse.2019.03.045. Impact factor (2017): 1.666. Quartile: Q3.

- 4. J. Diaz-Fortuny, M. Maestro, J. Martin-Martinez, A. Crespo-Yepes, R. Rodriguez, M. Nafria and X. Aymerich, "Current-limiting and ultrafast system for the characterization of Resistive Random Access Memories", AIP Review of Scientific Instruments, vol. 87, no. 6. DOI: 10.1063/1.4954973. Impact factor (2016): 1.515. Quartile: Q3.

#### Contributions to conferences as first author:

1. <u>J. Diaz-Fortuny</u>, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca, F. V. Fernandez, "CMOS Characterization and

- Compact Modelling for Circuit Reliability Simulation" in Proc. 24th IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS), July 2018. (Invited paper).

- 2. <u>J. Diaz-Fortuny, P. Saraza-Canflanca, A. Toro-Frias, J. Martin-Martinez, E. Roca, R. Rodriguez, F. V. Fernandez and M. Nafria "A Model Parameter Extraction Methodology Including Time-Dependent Variability for Circuit Reliaility Simulation", in Proc. 15th International Conference on Synthesis, Modeling, Analysis and simulation Methods and Applications to Circuit Design (SMACD), July 2018. (Runner-up Best Paper Award).</u>

- 3. J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca, F. V. Fernandez., "A noise and RTN-removal smart method for parameters extraction of CMOS aging compact models" in Proc. Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), May 2018.

- 4. <u>J. Diaz-Fortuny</u>, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca, F.V. Fernandez, E. Barajas, X. Aragones, D. Mateo "Statistical chatacterization of reliability effects in nanometer CMOS using a versatile transistor array IC", abstract in the 32nd Conference on Design of Circuits and Integrated Systems (DCIS), November 2017.

- J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca, F.V. Fernandez, "Statistical characterization of unreliability effects in a 65-nm CMOS transistor array", abstract in the 22nd International Mixed-Signal Testing Workshop (IMSTW), July 2017.

- J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca and F. V. Fernandez, "TARS: A toolbox for statistical reliability modeling of CMOS devices", in Proc. 14th International Conference on Synthesis, Modeling, Analysis and simulation Methods and Applications to Circuit Design (SMACD), June 2017.

- 7. J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, M. Nafria, R. Castro-Lopez, E. Roca, F. V. Fernandez, D. Mateo, E. Barajas, "A transistor array chip for the statistical characterization of process variability, RTN and BTI/CHC aging", in Proc. 14th International Conference on Synthesis, Modeling, Analysis and simulation Methods and Applications to Circuit Design (SMACD), June 2017.

- 8. <u>J. Diaz-Fortuny</u>, M. Maestro, J. Martin-Martinez, A. Crespo-Yepes, R. Rodriguez, M. Nafria and X. Aymerich, "A new experimental setup for

the ultrafast characterization of the resistive switching phenomenon", in Proc. 19th Workshop on Dielectric in Microelectronics, July 2016.

#### Co-authored international journal papers:

- M. Maestro, J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, M. Nafria, F. Campabadal and X. Aymerich, "New high resolution Random Telegraph Noise (RTN) characterization method for resistive RAM" in Solid-State Electronics (Elsevier), January 2016. DOI: 10.1016/j.sse.2015.08.010, impact factor (JCR 2016): 1.58, quartile: Q3.

- 2. J. Martin-Martinez, J. Diaz-Fortuny, R. Rodriguez, M. Nafria, and X. Aymerich, "New Weighted Time Lag Method for the Analysis of Random Telegraph Signals" in IEEE Electron Device Letters, April 2014. DOI: 10.1109/LED.2014.2304673, impact factor (JCR 2016): 2.754, quartile: Q1.

#### Co-authored Conference contributions:

- G. Pedreira, J. Martin-Martinez, J. Diaz-Fortuny, P. Saraza-Canflanca, R. Rodriguez, R. Castro-Lopez, E. Roca, F. V. Fernandez and M. Nafria, "A new time efficient methodology for the massive characterization of RTN in CMOS devices", in Proc. IEEE International Reliability Physics Symposium (IRPS), April 2019.

- 2. P. Saraza-Canflanca, J. Diaz-Fortuny, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F. V. Fernandez, "New method for the automated massive characterization of Bias Temperature Instability in CMOS transistors", in Proc. Design, Automation and test in Europe (DATE), March 2019.

- 3. P. Saraza-Canflanca, D. Malagon, F. Passos, A. Toro, J. Nuñez, <u>J. Diaz-Fortuny</u>, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, <u>M. Nafria and F. V. Fernandez</u>, "Design considerations of an SRAM array for the statistical validation of time-dependent variability models" in Proc. 15th International Conference on Synthesis, Modeling, Analysis and simulation Methods and Applications to Circuit Design (SMACD), July 2018.

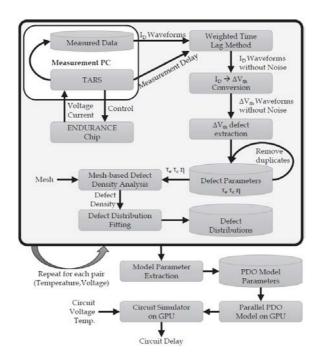

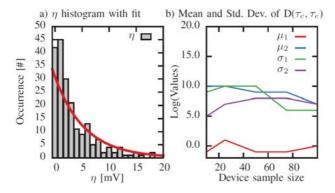

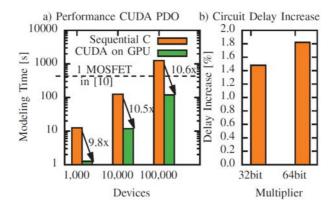

- 4. V. M. van Santen, J. Diaz-Fortuny, H. Amrouch, J. Martin Martinez, R. Rodriguez, R. Castro-Lopez, E. Roca, F. V. Fernandez, Jörg Henkel and M. Nafria. "Weighted time lag plot defect parameter extraction and GPU-based BTI modelling for BTI variability" in Proc. IEEE International Reliability Physics Symposium (IRPS), March 2018.

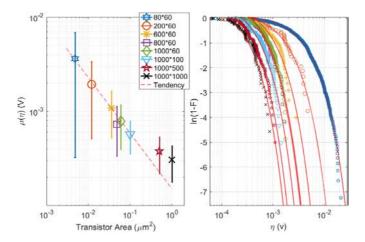

- C. Couso, J. Diaz-Fortuny, J. Martin-Martinez, M. Porti, R. Rodriguez, M. Nafria, F. V. Fernandez, E. Roca, R. Castro-Lopez, E. Barajas, D. Mateo and X. Aragones, "Dependence of MOSFETs threshold voltage variability on channel dimensions", in Proc. Joint International EU-ROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), April 2017.

- 6. M. Maestro, J. Diaz-fortuny, A. Crespo-Yepes, J. Martin-Martinez, R. Rodriguez, M. B. Gonzalez, F. Campabadal, M. Nafria and X. Aymerich, "Random Telegraph Noise (RTN) analyzed by using Weighted Time Lag Method in Resistive Switching devices" in Proc. 7th International Conference on Unsolved Problems on Noise (UPoN), July 2015.

- M. Maestro, J. Martin-Martinez, <u>J. Diaz-Fortuny</u>, A. Crespo-Yepes, M. B. Gonzalez, R. Rodriguez, F. Campabadal, M. Nafria, X. Aymerich, Poster: "Analysis of Set and Reset mechanisms in Ni/HfO<sub>2</sub>-based RRAM with fast ramped voltages", in Proc. 19th Conference on "Insulating Films on Semiconductors (INFOS), July 2015.

- 8. M. Maestro, J. Diaz-Fortuny, A. Crespo-Yepes, M. B. Gonzalez, J. Martin-Martinez, R. Rodriguez, M. Nafria, F. Campabadal, X. Aymerich, "A new high resolution Random Telegraph Noise (RTN) characterization method for resistive RAM", in Proc. Joint International EUROSOI Workshop and International Conference on Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), January 2015.

- 9. J. Martin-Martinez, J. Diaz-Fortuny, R. Rodriguez, M. Nafria, X. Aymerich, E. Roca, F. V. Fernandez and A. Rubio, "Characterization of Random Telegraph Noise and its impact on reliability of SRAM sense amplifiers", in Proc. 5th European Workshop on CMOS Variability (VARI), October 2014.

# Contents

| $\boldsymbol{A}$ | grad      | e <b>cimie</b> | ntos                                                       | i    |

|------------------|-----------|----------------|------------------------------------------------------------|------|

| A                | ckno      | wledgn         | nents                                                      | iii  |

| P                | refac     | e              |                                                            | v    |

| P                | ublic     | ations         | related to this thesis                                     | viii |

| 1                | Var<br>FE |                | y and reliability phenomena in nanometer MOS-              | 1    |

|                  | 1.1       | Time-          | zero variability                                           | 2    |

|                  |           | 1.1.1          | Random Dopant Fluctuations                                 | 2    |

|                  |           | 1.1.2          | Line-Edge and Line-Width Roughness                         | 3    |

|                  |           | 1.1.3          | Oxide Thickness and Poly-Si-Gate granularity               | 4    |

|                  | 1.2       |                | dependent variability: the role of defects in CMOS technes | 5    |

|                  |           | 1.2.1          | Transient effects: The Random Telegraph Noise              | 6    |

|                  |           | 1.2.2          | Voltage and temperature dependence of $	au_c$ and $	au_e$  | 8    |

|                  | 1.3       | Time-          | dependent variability: Aging                               | 9    |

|                  |           | 1.3.1          | The Bias Temperature Instability phenomenon                | 10   |

|   |     | 1.3.2  | The flot Carrier injection phenomenon                                                     | 14 |

|---|-----|--------|-------------------------------------------------------------------------------------------|----|

|   |     | 1.3.3  | BTI and HCI effects in circuit operation                                                  | 16 |

|   |     | 1.3.4  | Aging phenomena modelling                                                                 | 17 |

|   |     | 1.3.5  | The Probabilistic Defect Occupancy model                                                  | 18 |

|   | 1.4 | BTI/H  | ICI aging advanced characterization                                                       | 20 |

|   |     | 1.4.1  | The Enhanced Stress-Measurement aging characterization methodology                        | 21 |

|   |     | 1.4.2  | Defects characterization: The Weighted Time Lag Method                                    | 24 |

|   | 1.5 | From   | wafer-level to array-based IC MOSFET characterization                                     | 27 |

|   |     | 1.5.1  | Hardware and software design requirements for array-based IC variability characterization | 28 |

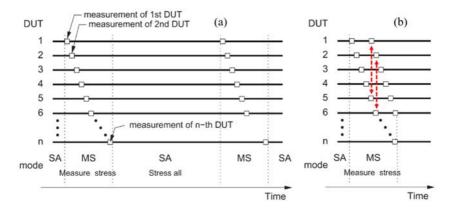

|   |     | 1.5.2  | Parallel-Stress Pipeline-Measurement method                                               | 29 |

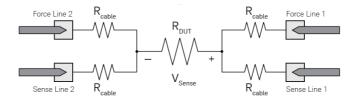

|   |     | 1.5.3  | Force-&-Sense voltage biasing                                                             | 32 |

|   |     | 1.5.4  | Previous works in array-based characterization                                            | 33 |

|   | 1.6 | Contri | butions of this thesis                                                                    | 37 |

| 2 | The | END    | URANCE array-based Integrated Circuit chip                                                | 39 |

|   | 2.1 | ENDU   | VRANCE IC design considerations                                                           | 40 |

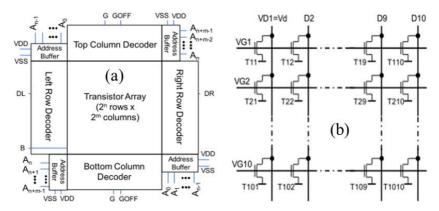

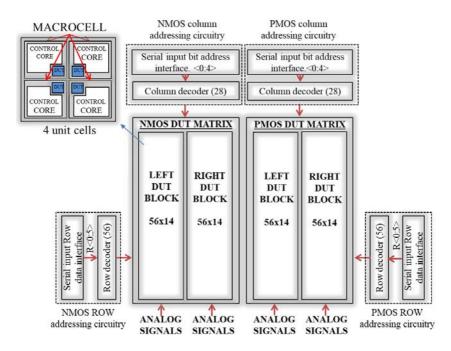

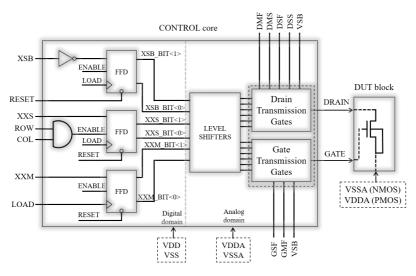

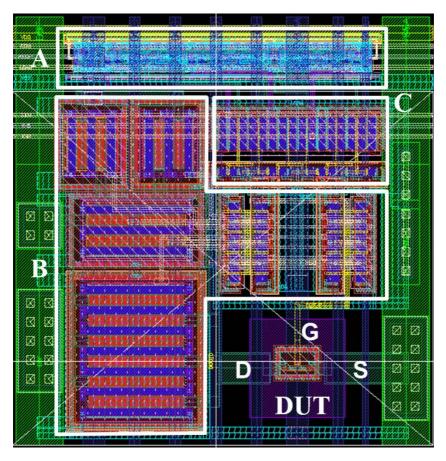

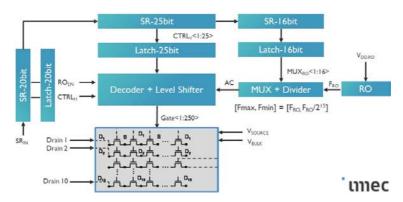

|   |     | 2.1.1  | The IC architecture                                                                       | 41 |

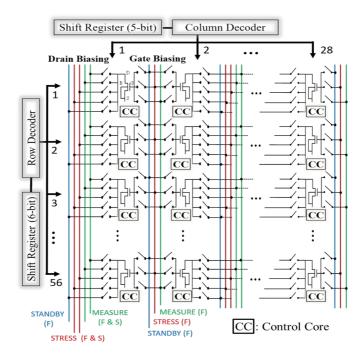

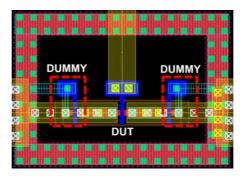

|   |     | 2.1.2  | The core: unit cell circuit and layout design                                             | 45 |

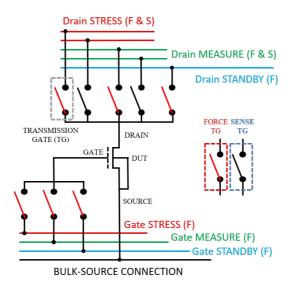

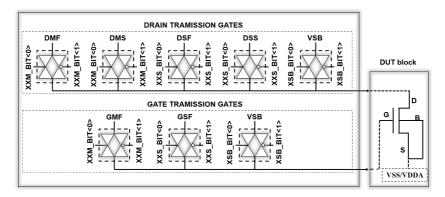

|   |     | 2.1.3  | Unit cell transmission gates block                                                        | 49 |

|   |     | 2.1.4  | Unit cell level shifter block                                                             | 51 |

|   | 2.2 | IC die | ital control: operation modes                                                             | 53 |

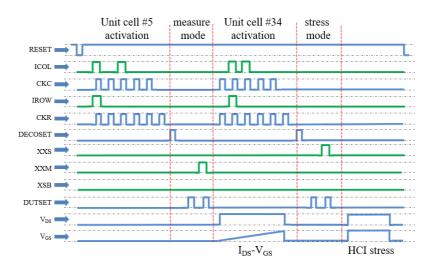

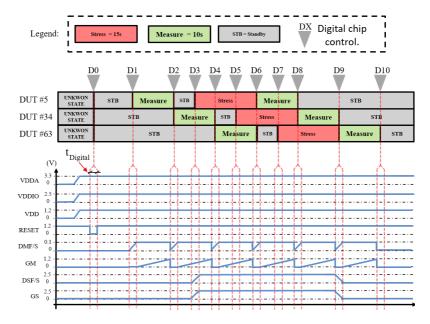

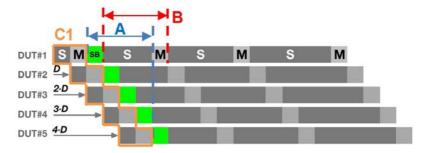

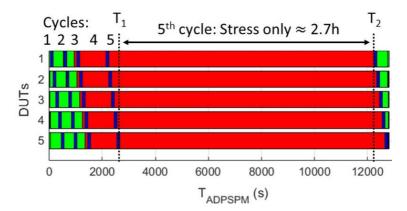

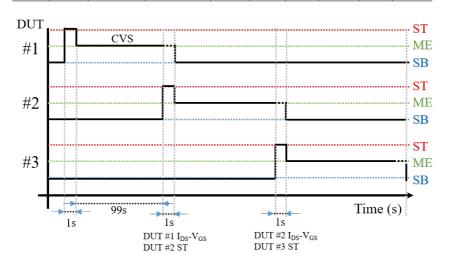

|   |     | 2.2.1                                                                                          | HCI parallel test example with 3 devices                                | 57  |

|---|-----|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|

|   | 2.3 | Conclu                                                                                         | usions                                                                  | 59  |

| 3 |     |                                                                                                | framework for the characterization of TZV and nomena in array-based ICs | 61  |

|   | 3.1 |                                                                                                | all DUT Parallel Stress Pipeline Measurements (ADP-methodology          | 62  |

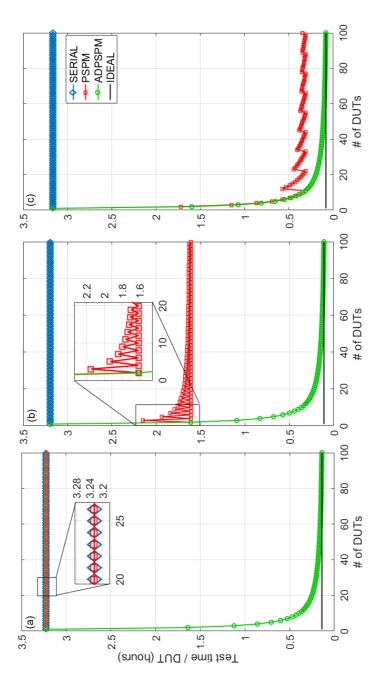

|   |     | 3.1.1                                                                                          | ADPSPM: a time complexity study                                         | 66  |

|   | 3.2 | TARS                                                                                           | software architecture for MOSFET characterization                       | 68  |

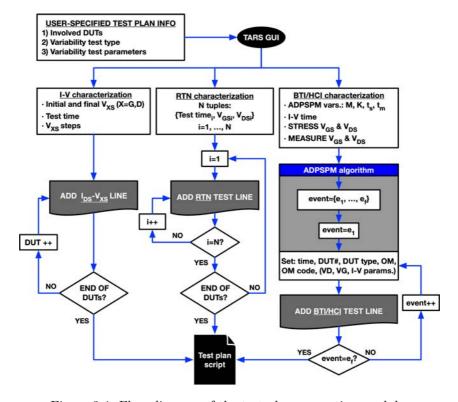

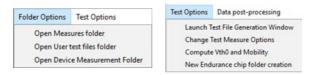

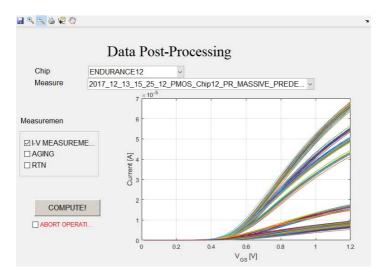

|   |     | 3.2.1                                                                                          | Test plan generation module                                             | 69  |

|   |     | 3.2.2                                                                                          | Elementary test instructions generation module                          | 73  |

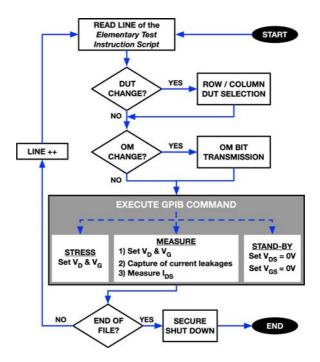

|   |     | 3.2.3                                                                                          | Test execution protocol and output test files                           | 75  |

|   | 3.3 | Hardw                                                                                          | vare characterization framework                                         | 79  |

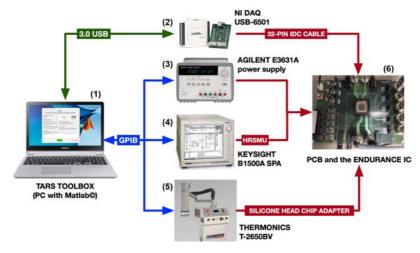

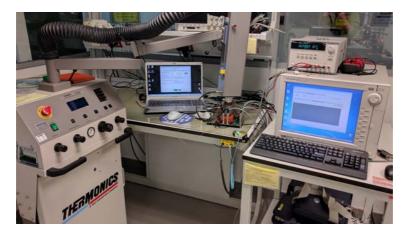

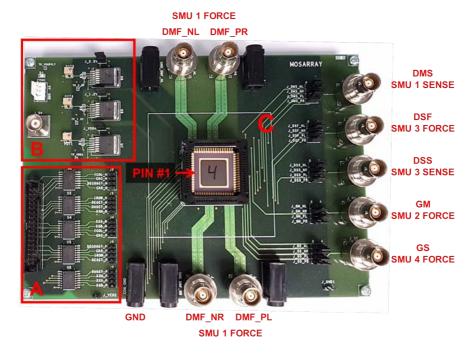

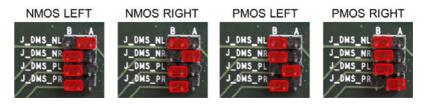

|   |     | 3.3.1                                                                                          | Printed circuit board for IC characterization                           | 81  |

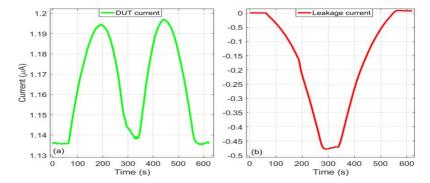

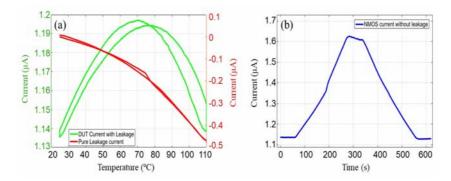

|   |     | 3.3.2                                                                                          | IC leakage current measurement                                          | 84  |

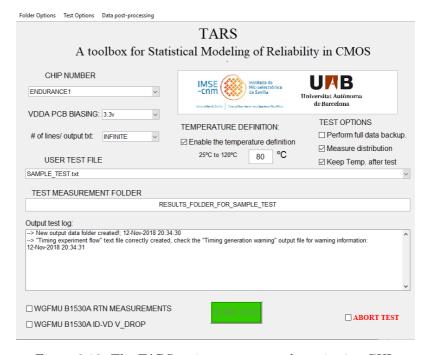

|   | 3.4 | TARS                                                                                           | software: graphical user interfaces                                     | 86  |

|   | 3.5 | Conclu                                                                                         | asions                                                                  | 91  |

| 4 | _   | pected MOSFET lifetime prediction and parameters ex-<br>action methodologies                   |                                                                         |     |

|   | 4.1 | Lifetime prediction based on time-zero and time-dependent statistical variability measurements |                                                                         |     |

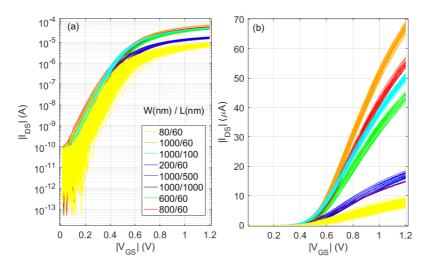

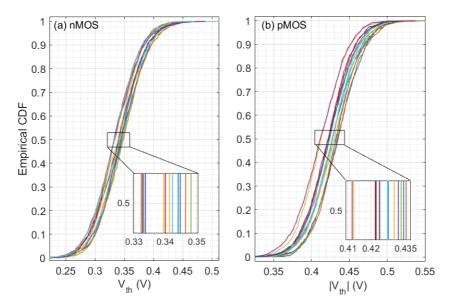

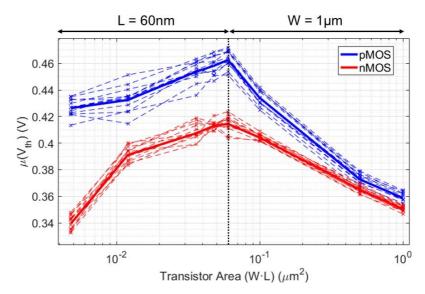

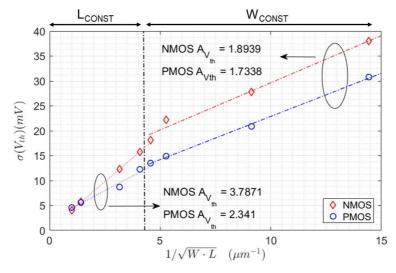

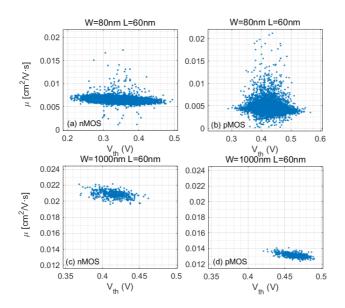

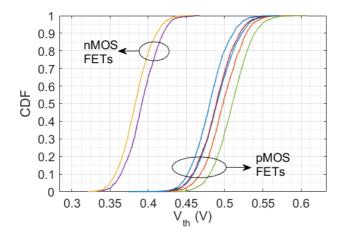

|   |     | 4.1.1                                                                                          | Time-zero variability measurements                                      | 94  |

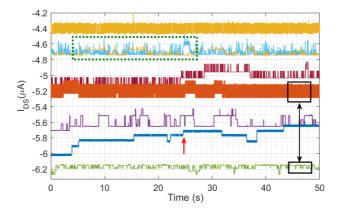

|   |     | 4.1.2                                                                                          | Random Telegraph Noise characterization                                 | 100 |

|   |     | 4.1.3                                                                                          | Bias Temperature Instability characterization                           | 103 |

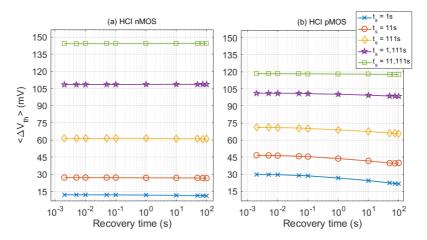

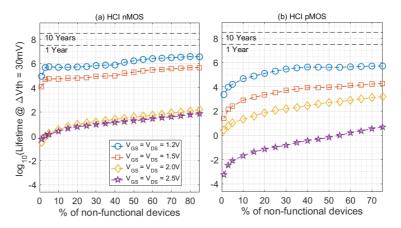

|       | 4.1.4                   | Hot Carrier Injection characterization                                         | 113 |

|-------|-------------------------|--------------------------------------------------------------------------------|-----|

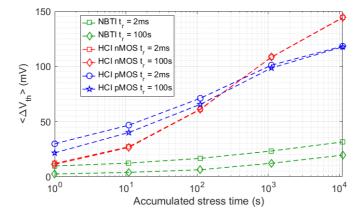

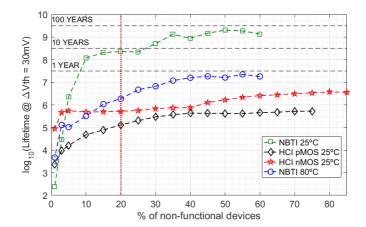

|       | 4.1.5                   | TDV lifetime comparison                                                        | 117 |

| 4.5   |                         | etion of MOSFET parameters for circuit reliability simu-                       | 119 |

|       | 4.2.1                   | A model parameter extraction methodology including time-dependent variability  | 120 |

|       | 4.2.2                   | A smart noise- and RTN-removal methodology for transistor parameter extraction | 126 |

|       | 4.2.3                   | BTI/HCI-aware circuit simulation using a GPU-based approach                    | 134 |

| 4.3   | 3 TZV a                 | and TDV tests using a 28-nm IMEC IC design                                     | 139 |

| 4.4   | 4 B1530                 | A Ultrafast device characterization                                            | 142 |

| 4.    | 5 Concl                 | usions                                                                         | 146 |

| Sumi  | Summary and conclusions |                                                                                |     |

| Bibli | Bibliography 1          |                                                                                |     |

## CHAPTER 1

# Variability and reliability phenomena in nanometer MOSFETs

Imperfections during transistor manufacturing process, causing variations of the fabricated devices, worsen with technology downscaling. Shifts of intrinsic transistor parameters, like threshold voltage  $(V_{th})$  or mobility  $(\mu)$  at the fabrication process, as well as their progressive variation during circuit operation over time, are major culprits behind fatal performance deviations that can negatively affect fabricated integrated circuits (IC) design and must be statistically characterized and modelled [1,2]. The combination of time-zero variability (TZV) and time-dependent variability (TDV) phenomena affects and compromises the reliability of the fabricated devices and circuits reducing, for instance, their intended lifetime.

In this scenario, the present chapter will briefly describe the most relevant sources of TZV and TDV phenomena affecting nowadays nanometer MOS-FETs. Moreover, the methodologies utilized to experimentally characterize devices under accelerated aging tests will be described. In the last sections of this chapter, a comparative analysis between conventional wafer-level and array-based IC transistor characterization is presented. Moreover, the hardware and software design requirements for a trustworthy array-based IC device characterization under aging phenomena will be described. In this sense, an analysis of the fulfilment of these demands in the most relevant array-based IC works presented in the recent literature is included. Finally, the objectives and contributions of this thesis are presented.

## 1.1 Time-zero variability

Time-zero variability (TZV), also known as process variability, consists in permanent deviations of the transistor parameters from their intended nominal values that occurs during the fabrication process. Typically, TZV is divided into stochastic and systematic variability. The stochastic group is defined as the local or intra-die process variability and the systematic component is defined as the global or inter-die process variability. On the one hand, local process variability causes parametric variations or mismatch between identically designed devices within the same die. On the other hand, global process variability causes die-to-die, wafer-to-wafer, or lot-to-lot variations between identical designed devices [3–5].

The main sources of TZV affecting CMOS device related to CMOS transistor manufacturing are: Random Dopant Fluctuations (RDF), Line-Edge Roughness (LER) and Line-Width Roughness (LWR) variations, Oxide Thickness Variations (OTV) effects and Poly-Si-Gate granularity. The randomness of the mentioned atomistic effects is uncorrelated from device-to-device converting each fabricated transistor in a unique device in terms of electrical parameters [6,7].

## 1.1.1 Random Dopant Fluctuations

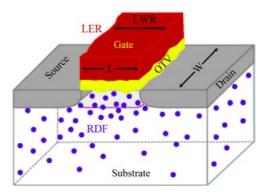

Random dopant fluctuations (RDF) are caused by stochastic variations in the number and location of the dopant atoms in the channel region of a MOSFET transistor. These dopant atoms are in charge of controlling, for example, the  $V_{th}$  of the fabricated devices. Thus, each transistor will have a unique doping profile that causes random variations in the transistor parameters like the  $V_{th}$  or the on-state current  $I_{ON}$ . Figure 1.1 shows a representative example where the major variability sources in a MOSFET device can be located. The RDF profile can be easily located inside the substrate region of the MOSFET (see Figure 1.1) where a random number of blue dots, featuring the Random Discrete Dopants, produces a unique atom doping profile [7, 8].

The effect of RDF increases with technology scaling. This is because the average number of dopant atoms in the transistor channel decreases exponentially with technology scaling. For instance, assuming a doping density of  $10^{18}/cm^3$ , the average number of dopant atoms in a hypothetic

channel with Width (W) of 70nm and Length (L) of 40nm is approximately 100. Thus, the variation of the electrical parameters between identically fabricated MOSFET devices depends on the low and discrete number of dopant atoms in devices [9].

In this scenario, it is necessary to statistically characterize and model the effects of RDF at the device and circuit levels to enhance reliability of digital and analog circuits in nanometer scale regimes. For instance, the mismatch produced by the RDF in the two cross-coupled inverters of a basic SRAM cell can result in significant variation in the delay of a the circuit, data loss or bit flip [8, 9].

### 1.1.2 Line-Edge and Line-Width Roughness

Other important source of transistor variability related to nanometric channel dimensions are the Line-Edge Roughness (LER) and Line-Width Roughness (LWR) effects. Both phenomena consist in imperfections or variations in the gate edges of devices that result in non-rectilinear shapes with respect to a perfect linear edge. Figure 1.1, shows an illustrative example of both LER and LWR effects in the gate region of a MOSFET device. The source of these imperfections is related to the lithography and etching processes during transistor fabrication [10, 11].

Figure 1.1: Example of LER/LWR, RDF and OTV in a MOSFET device [3].

LER and LWR effects do not scale according to the CMOS technology scale trend. In large transistors (channel length above 100nm) LER and LWR

were not a relevant source of variability since the edge roughness caused at the fabrication stage remains typically in the order of  $\approx$ 5-nm independently of the fabrication process. However, in current planar MOSFET, FinFET and multi-gate fabrication processes, at the sub-100-nm technology nodes, the contribution of LER/LWR is becoming a comparable fraction of the transistor gate L and W thus, the resulting variability is significantly increased [12, 13]. Moreover, LER/LWR variability effects on critical device parameters have revealed that the inclusion of this phenomena in variability simulations have resulted in  $V_{th}$  and  $I_{ON}/I_{OFF}$  variations close to the nominal distributions of the transistor parameters [14, 15].

Studies where RDF and LER/LWR effects have been simulated together, have concluded that the combined phenomena effects are statistically independent. Moreover, the effects of LER/LWR in the device parameters variations have a much more stronger effect for channel length below 20-nm than for devices with higher channel lengths where, the RDF become the dominant TZV source [12, 14, 15].

## 1.1.3 Oxide Thickness and Poly-Si-Gate granularity

In advanced technology nodes, device insulator thickness below 10nm are responsible for an important source of intrinsic parameter fluctuations such as the oxide thickness variations (OTV) and Poly-Si-Gate granularity.

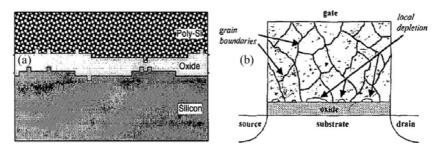

OTV are caused by imperfections or roughness in the silicon/insulator and the gate/insulator interfaces across the gate stack of transistors as shown in Figure 1.2 (a). The OTV cause variations in the  $V_{th}$ ,  $\mu$  [16] or gate current tunnelling [17] between identical fabricated devices.

The use of highly doped polycrystalline granular structures in the fabrication of Poly-Si gates of MOSFETs to obtain electrical properties close to metals, in combination with thin gate oxides, introduce another source of transistor parameter variability known as Poly-Si-Gate granularity. The Poly-Si-Gate granularity variability occurs when gate dopants do not diffuse optimally down to the gate/insulator interface. Then preferential dopant diffusion along grain boundaries results in non-uniform isolated doped regions in the transistor gate interface generating local gate depletion zones as shown in Figure 1.2 (b). This phenomenon results in an effective oxide thickness increase and introduces additional random dopant charge on the side of the

gate oxide opposite to the channel enhancing, for instance,  $V_{th}$  fluctuations from device to device [18]. Moreover, the introduction of High-k materials in the transistor insulator with the aim of reducing leakage currents due to technology scaling, also leads to localised variations in gate-to-channel interface potential that results in  $V_{th}$  variations between devices [19–21].

Figure 1.2: Oxide Thickness Variations in a MOSFET device in (a) and Poly-Si-Gate insulator granularity variability in (b) [16] showing Poly-Si gate boundaries and local gate depletion zones [18].

# 1.2 Time-dependent variability: the role of defects in CMOS technologies

One of the reasons for the increase of transistor TZV and TDV is the reduction of the transistor's gate area, that must be linked to gate insulator thickness  $(T_{OX})$  scaling, to mitigate the short channel effects of nanometric devices. It is well known that conventional thickness scaling of traditional  $SiO_2$  insulators became unfeasible at the 90nm technology node and below because of the intolerable high gate leakage current mainly produced by direct tunnelling through the gate insulator [22, 23].

In this scenario, the semiconductor industry has moved forward and started to manufacture transistors first utilizing Silicon Oxynitride (SiON) gate insulators. Later on, the introduction of High-K Metal gate insulators (HKMG) at the 45-nm and 28-nm node allowed the continued scaling of the device geometry without a significant increase of the gate leakage currents. Nevertheless, to control the increasing short channel effects at the 20-nm, 16-nm and 14-nm technology nodes, the industry has migrated from planar MOSFET to FinFET, FD-SOI FETs or Multi-Gate FETs [24–26].

With the rapidly CMOS scaling trend imposed to newer CMOS technology nodes, the influence of the previously described sources of device TZV in the shift of the intrinsic transistor parameters, must be completed with device transients and degradation phenomena during its operation over time. In this sense, the Random Telegraph Noise (RTN) transient phenomenon and the Bias Temperature Instability (BTI) and the Hot-Carrier Injection (HCI) aging phenomena [27, 28] have become critical issues in current ultrascaled technologies. These mechanisms consist in the stochastic charge trapping/detrapping in/from device defects located at the device insulator, bulk or at the interface. Moreover, the defects present in a CMOS device can be inherent to the manufacturing process or also generated during transistor operation as a consequence of BTI/HCI aging [29].

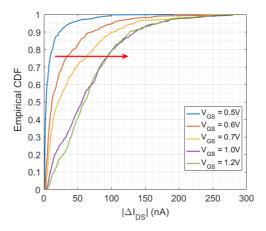

Defect charge trapping/detrapping may cause significant transistor parameters variations, for instance  $V_{th}$  or  $\mu$ , to shift from their as-fabricated values that can cause device mal-function or a permanent failure [30]. To account for the variability produced by the charge trapping/detrapping, three main parameters of individual defects should be statistically characterized: the capture time ( $\tau_c$ ) (the mean time needed to capture a charge by a defect), the emission time ( $\tau_e$ ) (the mean time needed to emit a charge by a defect) and the drain current shift ( $\Delta I_{DS}$ ) or, equivalently, the threshold voltage shift ( $\Delta V_{th}$ ) associated to each defect, typically known as eta ( $\eta$ ). The analysis of the three defect parameters revealed the following characteristics:

- 1. Both capture and emission time constants  $(\tau_c, \tau_e)$  are uncorrelated and bias and temperature dependent [31, 32].

- 2. Capture and emission defect time constants, can expand several decades in time thus, the selection of an appropriate measurement time window to characterize them is of high importance [33].

## 1.2.1 Transient effects: The Random Telegraph Noise

The Random Telegraph Noise (RTN) is characterized by a random switching of the  $I_{DS}$  between two or more levels along time and has been recognized as a significant variability source since it is responsible for device parameter variability, such as the  $\Delta V_{th}$  [33] at nominal operation conditions. These current fluctuations are related to the capture and emission of charge carriers by oxide and interface defects, showing a large dependence on device biasing and temperature conditions. Moreover, RTN variability phenomenon increases

inversely with area scaling negatively affecting, for instance, analog devices and digital logic circuits like flash memories due to the  $V_{th}$  variability [34,35]. Moreover, RTN is not only present in conventional MOSFET transistors, it can be detected in Resistive Random Access Memories (RRAM) utilized in the design of non-volatile memories [36], Fully Depleted FET (FD-SOI) [37], FinFET [38], Multigate FET [39,40], and nanowire FET [41] devices and digital circuits [42].

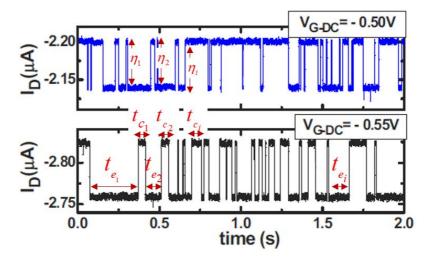

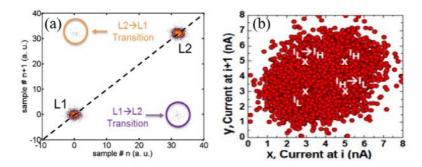

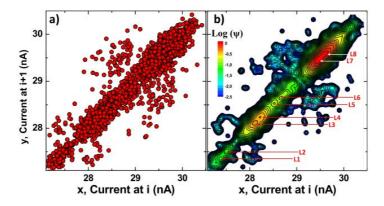

Standard RTN characterization, that consists of executing a continuous measurement of the  $I_{DS}$  while maintaining a constant  $V_{GS}$  and  $V_{DS}$  biases, permits the studying of the RTN active defects parameters, determine its location in the device and the defect energy depth below the conduction band of the dielectric [33, 43]. An accurate measurement is required since the current fluctuations can vary just a few nanoamps while the time required for the RTN characterization depends on the defect intrinsic capture/emission time constants, which may span several orders of magnitude in measurement time. For instance, Figure 1.3 shows two examples of typical RTN signals where the  $I_{DS}$  fluctuate between two different levels that correspond to the charge/discharge of a single active defect in a measurement time window of 2s each.

Figure 1.3: Example of two RTN signals showing the location of individual emission times  $t_{e_i}$ , capture times  $t_{c_i}$  and the current fluctuations amplitude  $(\eta_i)$  [44].

In this scenario, the RTN fluctuations originated from a single defect can be fully characterized by three parameters:  $\eta$ , that describes the average impact on the  $V_{th}$  or  $I_{DS}$  amplitude fluctuation, the  $\tau_c$  as the mean elapsed time before the system captures a charge carrier ( $\langle t_{c_i} \rangle$ ) and  $\tau_e$  as the mean elapsed time before the system emits a charge carrier ( $\langle t_{e_i} \rangle$ ) (see Figure 1.3 for individual  $t_{c_i}$  and  $t_{e_i}$  occurrence) [45].

## 1.2.2 Voltage and temperature dependence of $\tau_c$ and $\tau_e$

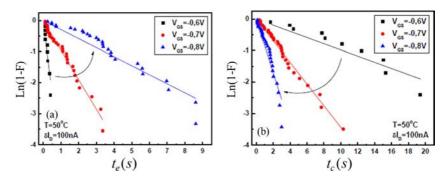

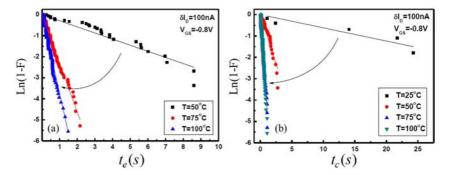

As already introduced in section 1.2, charging and discharging of device defects may produce  $I_{DS}$  device variations that are directly related to  $V_{th}$  fluctuations. This behaviour that compromises device reliability become the source of transient effects like RTN as well as TDV aging phenomena such as BTI and HCI [32]. In this sense, dependence with voltage and temperature conditions of the  $t_e, t_c$  times associated to those variations [32, 46, 47] will be shown. For instance, Figure 1.4 (a) and (b) shows the statistical distribution of  $t_e$  and  $t_c$  respectively, of an individual device defect from an RTN measurement with fixed  $V_{DS}$  and increasing  $V_{GS}$  conditions. In both Figures 1.4 (a) and (b),  $t_{c_i}$  and  $t_{e_i}$  parameters have been plotted assuming its exponential distribution where F, the accumulated distribution function, can be expressed by equation 1.1.

$$ln(1 - F(V,T)) = \frac{-t_{c,e}}{\langle t_{c,e}(V,T) \rangle}$$

(1.1)

As can be extracted from Figure 1.4 (a), for increasing  $V_{GS}$  voltage, the slope of the  $t_e$  distribution decreases, which means that the emission times  $t_e$  increase. On the contrary, the slope of the  $t_c$  in Figure 1.4 (b) increases with increasing  $V_{GS}$  meaning that the capture time  $t_c$  decreases [48].

Recent works have demonstrated that defect  $t_c$  and  $t_e$  times are reduced with high temperature revealing that the probability to charge or discharge a defect increases with temperature. For instance, Figure 1.5 (a) and (b) shows the statistical distributions of the  $t_e$  and  $t_c$ , respectively, of a single defect showing that a temperature increase produces a defect time constant reduction in both cases.

Figure 1.4: Statistical distributions of (a)  $t_e$  and (b)  $t_c$  for a  $\Delta I_{DS} = 50nA$  criterion and a fixed temperature of  $T = 50^{\circ}C$  at different  $V_{GS}$  device biasing. Lines correspond to the experimental fitting using equation 1.1 where the mean values of  $\langle t_{e_i} \rangle$  and  $\langle t_{c_i} \rangle$  can be obtained as the inverse of the fitting slopes respectively [49].

Figure 1.5: Statistical distributions of the (a)  $t_e$  and (b)  $t_c$  of a single device defect that produces a  $\Delta I_{DS} \approx 100 nA$  for different temperatures [49]

## 1.3 Time-dependent variability: Aging

A progressive degradation of the intrinsic device parameters takes place after long periods of time (months or years) working at nominal operation conditions due to aging mechanisms like the Bias Temperature Instabilities and the Hot Carrier Injection phenomena. These are sources of TDV affecting the transistor parameters over time. In this scenario, it becomes practically unfeasible to characterize BTI/HCI TDV aging at the nominal operation conditions such long times.

Typical aging characterization methods are based in the execution of accelerated aging tests, in which temperature and/or the drain and/or the gate voltages are raised above their nominal operation values over a much shorter period of time. Thus, transistor parameters degradation is produced in significantly reduced time. High voltages and/or temperatures are referred to as the stress conditions while, after the stress, devices are measured close to the nominal operation conditions to compute transistor parameter shifts, if present, without introducing significant damage to the device. For instance, degradation of  $V_{th}$  is one of the essential parameters to determine MOSFET degradation metrics and serves as an effective indicator when evaluating device variability and reliability [23].

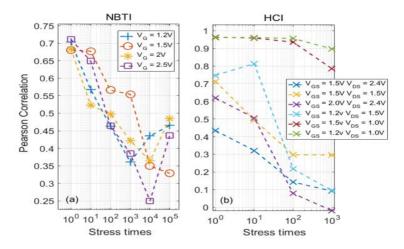

### 1.3.1 The Bias Temperature Instability phenomenon

The Bias Temperature Instability is one of the most relevant reliability concerns for the nanometric semiconductor industry known by academia and industry for more than 50 years. BTI degradation is known for pMOS devices as Negative BTI (NBTI) and occurs when the gate of a transistor is negatively biased resulting in a build-up of positive charge in the gate insulator. NBTI phenomena progressive degrades intrinsic device parameters such as the linear  $(\Delta I_{DLIN})$  and saturation  $(\Delta I_{DSAT})$  drain current, the threshold voltage  $(\Delta V_{th})$ , transconductance  $(\Delta gm)$ , among others. For the nMOS devices, the BTI is known as Positive BTI (PBTI) and appears when a positive bias is applied to the gate of the device while all the other terminals are grounded. PBTI causes an accumulation of negative charge in the gate insulator that results in a positive shift of, for instance, the device  $V_{th}$  [50, 51].

NBTI was first observed in devices based on Silicon Dioxide  $(SiO_2)$  insulators. Nevertheless, it also continues as an important concern with the introduction of new insulators like Silicon Oxynitride (SiON) [52] around the year 2000 [53] where NBTI was the predominant source of transistor degradation. PBTI has remained less predominant for nMOSFETs with  $SiO_2$  and SiON gate stacks until the introduction of newer High-K Metal Gate dielectrics (HKMG) [54] and advance devices such as FinFETs [55,56].

An intrinsic feature of the BTI phenomena, caused by the charge and discharge of device defects, is that after the application of stress, where device defects can be charged, the shift of the absolute positive parameters, like  $\Delta V_{th}$  or  $\Delta \mu$ , exhibit a recovery behaviour that tends to reach its non-degraded

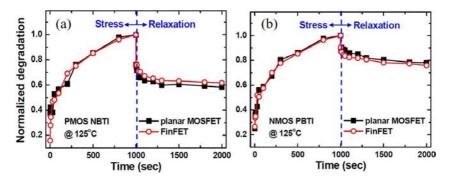

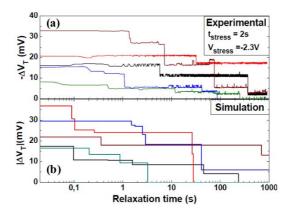

values immediately after the stress removal. This process is also known as BTI recovery or relaxation and can be prolonged for several decades in terms of measurement time. For instance, Figure 1.6 shows an example of the described stress-recovery BTI aging behaviour where the  $\Delta V_{th}$  parameter is shown for pMOS and nMOS HKMG devices in Figure 1.6 (a) and (b) respectively [55]. A  $|\Delta V_{th}|$  occurs for both pMOS and nMOS devices during the stress phase under BTI aging.

After the removal of the stress conditions,  $|\Delta V_{th}|$  starts recovering its original value due to the discharge of previously charged defects [57]. It is important to remark that for the relaxation window of 1000s shown in Figure 1.6 (a) and (b), the total  $\Delta V_{th}$  parameter does not reach a total recovery, i.e.,  $\Delta V_{th} = 0V$  and a plateau appears as the BTI permanent component (P) [58, 59].

Figure 1.6: Example of the  $\Delta V_{th}$  shift behaviour during BTI stress and relaxation processes for 20-nm planar and 14-nm FinFET devices for pMOS devices in (a) and for nMOS devices in (b) [55].

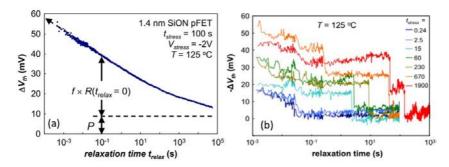

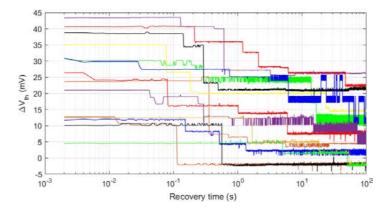

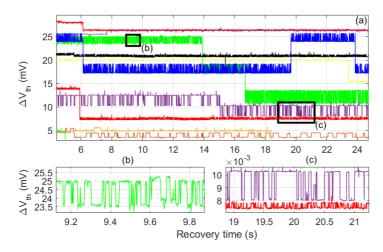

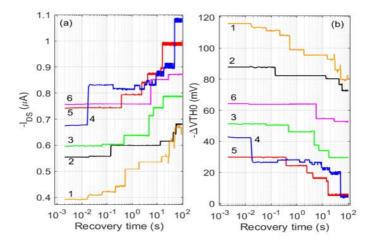

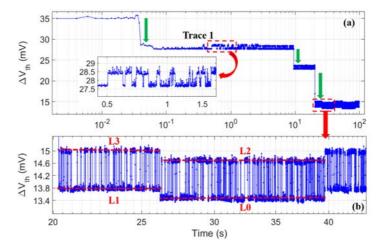

For long channel devices, i.e., channel lengths in the micrometer scale, BTI behaviour can be detected with a smooth recovery trend due the contribution of many device defect discharges as shown in Figure 1.7 (a). On the contrary, in modern deep scaled devices, i.e., channel lengths in the nanometer scale, BTI recovery behaves in discrete steps, as shown in Figure 1.7 (b), where abrupt  $-\Delta V_{th}$  defect discharges can be easily detected because only a few defects are present in the device and their contribution is much more severe. Moreover, BTI recovery starts immediately just after the stress biasing conditions are removed. Thus,  $\Delta V_{th}$  degradation is very sensitive to any measurement delay where, the higher the measurement delay after stress removal the lower the  $\Delta V_{th}$  can be captured.

Figure 1.7: (a) smooth  $\Delta V_{th}$  BTI recovery trace obtained from a pFET device with SiON dielectric and L between 0.13 $\mu m$  and 0.5  $\mu m$  and W = 10 $\mu m$  dimensions, after BTI stress of  $V_{GS}$  =-2V [60]. (b) 7 BTI recovery traces showing discrete  $-\Delta V_{th}$  variations due to defect discharges for a pFET device (L = 70nm, W = 90nm) and HfO<sub>2</sub> based dielectric [50]

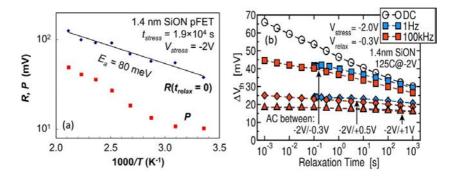

Defects responsible for BTI degradation are voltage and temperature dependent as well as frequency dependent. From a temperature point of view, BTI degradation increases for elevated temperatures. Moreover, defects that contribute to BTI degradation, show individual activation energy  $E_A$  for capture and emission time constants following the Arrhenius law [61]. In this regard, Figure 1.8 (a) shows an example of the temperature dependence of both the recoverable and the permanent BTI components when increasing the temperature from 25°C to 200°C revealing the temperature dependence of the  $<\Delta V_{th}>$  parameter. Newer NBTI characterization techniques have emerged in recent literature maximizing the degradation/relaxation utilizing very high stress temperatures by means of controllable poly-heaters [62] to assess the long-term BTI phenomena in the shortest time possible [63, 64].

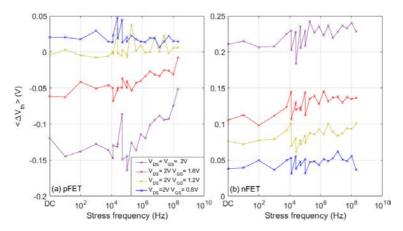

In terms of BTI frequency dependence, several works have been published in the literature reporting AC-BTI weak frequency dependence [65, 66] while other studies have demonstrated a frequency-dependent contribution of BTI [67,68] which exemplifies that the AC-BTI dependence is subject of controversy. For instance, Figure 1.8 (b) shows a comparison of the recovery behaviour between a previous DC stress of 1ks with  $V_{G-stress} = -2V$  and  $V_{G-relax} = -0.3V$  (open circles) and two AC stress waveforms during 2ks with  $f_{AC1} = 1$ Hz (blue squares) and  $f_{AC2} = 100$ kHz (red squares). If the AC on/off waveforms oscillate between  $V_{G-stress}/V_{G-relax}$  (-2V/-0.3V), the  $\Delta V_{th}$  for DC and AC stress merges only at the end of the recovery window while at the beginning circles and squares are clearly separated. This behaviour demonstrates a

frequency dependence of the BTI recoverable component while the permanent component is not. Nevertheless, if a more positive AC-off value is used, (-2V/+0.5 and -2V/+1V), the frequency dependence is mitigated (see diamonds and triangles in Figure 1.8 (b)) [67].

Figure 1.8: Example of the temperature dependence of BTI phenomena of both the recoverable (R) and the permanent (P) component under DC stress in (a) [60] while (b) shows the BTI aging frequency dependence due to AC stress [67]

The following considerations about BTI phenomena behaviour are well accepted [32,69-71]:

- 1. Even for short stress times (< 1s), emission and capture time events show a wide range of characteristic time scales, ranging from  $\mu s$  time scale to several decades in terms of logarithmic experimental window.

- 2. Both  $\tau_c$  and  $\tau_e$  times of each defect are determined by its energy level  $(E_T)$ , the defect depth into the gate stack and gate bias  $(V_{GS})$ . Moreover, the capture and emission events of each defect are stochastic and exponentially distributed.

- 3. BTI defects are considered the same defects that originates the RTN switching phenomenon. Thus, the difference between BTI and RTN phenomena defect behaviour is that in an RTN experiment, a limited number of defects with capture and emission time constants within the experimental window are visible. On the contrary, due to the bias dependence of the capture time constant, more defects contribute to BTI because of a previous device stress that allows charging more defects than in an RTN experiment.

#### 1.3.2 The Hot Carrier Injection phenomenon

The HCI aging phenomenon has been known for nearly five decades and consists of a degradation mechanism where carriers along the transistor channel are accelerated because of the imposed lateral electric field,  $(V_{GS}, V_{DS}) > 0V$ . This makes the carriers to gain sufficient energy to create insulator defects altering permanently the electrical properties of the device [72, 73].

Early in the 1970s-1980s, the positive supply voltage (VDD) in the CMOS industry was fixed while transistor area began to scale, resulting in a strong increase of the device vertical/lateral electric fields and thus, turning HCI aging the most relevant transistor reliability issue. In the 1990s, VDD was reduced with each technology node as well as the electric fields, attenuating the HCI effects in the device/circuit reliability. Nevertheless, nowadays below the 100-nm node, the VDD biasing values are saturating around  $\approx 1$ V, increasing the vertical and lateral transistor electric fields and, therefore, HCI aging phenomena is becoming a more severe aging mechanism again [74–76].

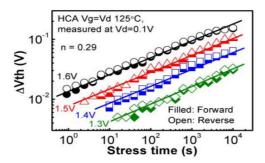

The HCI degradation can be observed as a quasi-permanent shift in the device intrinsic parameter such as  $V_{th}$ , a reduction of the saturation current  $I_{DSAT}$ , between others. In contrast to nanometer-scale devices where the worse bias combination for HCI damage is  $V_{GS} = V_{DS}$ , early in the 1980s the critical biasing condition used to occur at  $V_{GS} = V_{DS}/2$  [77–79]. In this sense, Figure 1.9 shows an example of the  $\Delta V_{th}$  degradation suffered by planar nMOS devices with L = 27nm and W = 90nm. As shown in Figure 1.9,  $\Delta V_{th}$  degradation under stress conditions reveal high degradation for increasing stress voltage.

Figure 1.9: HCI degradation showing  $\Delta V_{th}$  shift after 4  $V_{GS} = V_{DS}$  stress voltages and measurements carried out at  $V_{DS} = 0.1V$ ,  $V_{GS} \approx V_{th}$  [78].

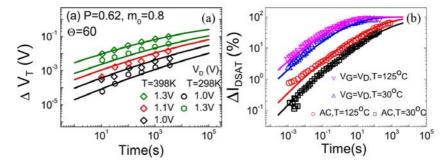

HCI phenomenon is also frequency and temperature dependent. In this sense, Figure 1.10 (a) and (b) shows two examples of device parameter degradation due to HCI accelerated degradation under different temperature conditions and AC/DC stress respectively. Figure 1.10 (a) depicts the  $\Delta V_{th}$  degradation for various  $V_{DS}/T$  stress conditions showing that under high temperature (T=398K), HCI degradation is larger than at low temperatures (T=298K). On the other hand, Figure 1.10(b) shows the  $\Delta I_{DSAT}$  at two different temperatures under AC and DC stress conditions. The results reveal a lower degradation when stressing with AC waveforms for the two temperatures than for DC stress [80].

Figure 1.10: Intrinsic device parameters degradation under HCI aging phenomenon showing in (a) the  $\Delta V_{th}$  for different  $V_{DS}$  and temperature conditions and in (b) the  $\Delta I_{DS}$  for AC and DC stress at different temperatures [80].

To describe HCI degradation effects, the traditional Lucky Electron model (LEM) [81] based on direct electron excitation was widely accepted for long channel devices. As LEM postulates, the cause for HCI degradation involves defects generated by electrons  $(e^-)$  or holes  $(h^+)$  that impact into the device interface thanks to the high electric lateral fields in the device.

For nanometric devices, the LEM model predicts a very low effect of the HCI phenomena because electric fields are reduced due to low supply voltages. Nevertheless, recent literature shows that HCI degradation remains significant for ultra-scaled MOSFETs and therefore new models are needed. In contrast to the conventional field-driven LEM, recent literature proposed novel energy-driven theories [82,83] to describe HCI phenomenon and accurately explain and model the mechanism of carrier induced degradation and to overcome the limitation imposed by the traditional LEM [79,82,84].

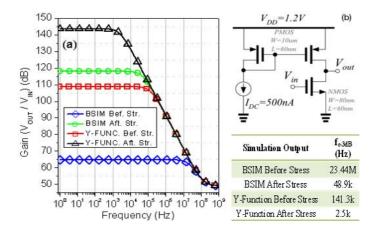

#### 1.3.3 BTI and HCI effects in circuit operation

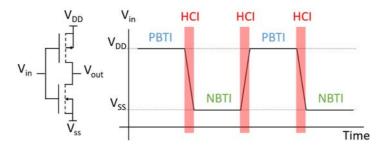

In real circuit operation, BTI and HCI aging degradation can coexist degrading devices and circuits while reducing the intended reliability of the overall circuit. In this sense, Figure 1.11 shows an explanatory example where a simple CMOS inverter designed with a pMOS and a nMOS transistor, connected in series between VDD and VSS biased using a rail-to-rail, i.e., from VDD to VSS, square signal. The following situations can occur during circuit functionality:

Figure 1.11: Schematic representation of a CMOS inverter under a typical square input signal showing BTI and HCI reliability phenomena.

- 1. Logical '1' input  $(V_{in} = \text{VDD})$ : the nMOS transistor is in on-state because  $V_{GS} = V_{GB} = \text{VDD}$ , while the pMOS transistor remains in off-state due to  $V_{GS} = V_{GB} = 0V$ . In this scenario, the PBTI phenomena appears in the nMOS transistor (PBTI blue label in Figure 1.11) degrading the nMOS device. Moreover, the pMOS transistor experiences the so called Off State Stress (OSS) [85,86] because of the high  $|V_{DS}| = \text{VDD}$  while  $|V_{GS}| = 0V$ .

- 2. Logical '0' input ( $V_{in} = \text{VSS}$ ): in this case, the reverse situation can be observed in the inverter. NBTI phenomenon appears in the pMOS transistor because of the  $|V_{GS}| = |V_{GB}| = \text{VDD}$  biasing (NBTI green label in Figure 1.11), and the nMOS transistor suffers from OSS because of the high lateral electric field when  $V_{DS} = \text{VDD}$  and  $V_{GS} = 0\text{V}$ .

- 3. HCI device stress occurs during the dynamic switching periods of the square signal when the  $V_{GS}$  and the  $V_{DS}$  voltages are high enough and there is current flowing through the devices. In this situation, when the input signal changes from VDD to VSS or vice versa, HCI degradation appears in the nMOS and the pMOS transistors (se red rectangles in Figure 1.11).

The impact of TDV phenomena including transient and aging effects in transistor and circuit reliability, have achieved an important relevance in current advanced technology nodes. TDV aging modelling techniques and advanced characterization methodologies have been proposed in the literature to understand and mitigate degradation effects in the fabricated transistors that will be briefly described in the next sections of this chapter.

#### 1.3.4 Aging phenomena modelling

To accurately model the effects of aging phenomena related to BTI/HCI aging mechanisms, several physical models have been proposed in the literature to extrapolate to the nominal operation voltages, the accelerated degradation suffered by devices under aging tests. Nevertheless, experimental results have demonstrated that initial models, like the original Reaction-Diffusion model [87], that was latter improved by the works in [88–90], are not suitable to completely describe the aging phenomena in nanometer devices [50, 91]. In this sense, newer models can be found in the literature to describe the defect behaviour during BTI/HCI and RTN trapping/detrapping related phenomena: the Two-Stage Model [92, 93], the Two-energy-well model [94], the Non-radiative two-stage Multi-Phonon (NMP) model [95] or the four-state NMP model [96].

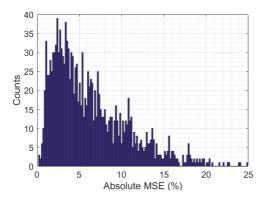

Despite the fact that NMP models provide an accurate physical description of aging variability phenomena, they typically require computational intense TCAD simulations with numerous physical model parameters. In this sense, reaction-limited models such as the capture/emission time map (CET) model [97] or the Probabilistic Defect Occupancy (PDO) model [98], which will be described hereinafter, were proposed in recent literature as efficient alternatives because they use a limited number of parameters and provide a physical approximation for the NMP models [95].

In the context of accurate device and circuit modelling, this thesis will provide statistically accurate parameters to feed the PDO model because its simplicity to be used with experimental device measurement without scarfing accuracy when reproducing aging degradation compared with other models [99].

#### 1.3.5 The Probabilistic Defect Occupancy model

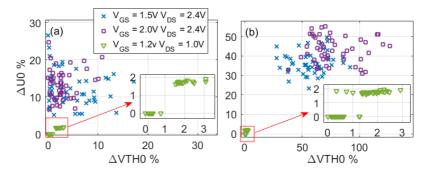

The PDO model allows describing the  $V_{th}$  variability produced by BTI and HCI aging phenomena. Moreover, the model permits obtaining  $V_{th}$  variability under arbitrary  $V_{GS}$  biasing conditions and is based on the stochastic properties of the individual defects localized in MOSFET devices. It assumes that each individual device has a finite number of active defects (N) that can be charged or discharged. This behaviour will produce different  $V_{th}$  variations in the device due to the contribution of each defect. In this scenario, an active defect can capture a charge producing a decrease of the  $I_{DS}$  device current or if a defect releases a charge, an increase of the  $I_{DS}$  current is observed [52].

The PDO model permits the evaluation of the  $\Delta V_{th}$  by analysing the state (charged or discharged) of each defect as defined by equation 1.2. For a given stress time  $t_s$  and recovery time  $t_r$  considering (i) the defect distribution  $(D(\tau_e, \tau_c))$  of the device in the  $(\tau_e, \tau_c)$  space and (ii) the occupancy probability of a defect,  $P_{occ}$ , defined by the probability if a defect is charge or discharged. The  $P_{occ}$  depends on the MOSFET device operation conditions and the  $(\tau_e, \tau_c)$  values, the number of defects (N) and the mean defect impact in the  $< \Delta V_{th} > (\eta)$

$$\Delta V_{th}\left(t_{s},t_{r}\right)=N<\eta>\int_{0}^{\infty}\int_{0}^{\infty}D\left(\tau_{e},\tau_{c}\right)\cdot P_{occ}\left(\tau_{e},\tau_{c},t_{s},t_{r}\right)\partial\tau_{e}\partial\tau_{c}+P_{p}$$

$$(1.2)$$

By using the PDO model a log-normal bivariate distribution is utilized for simplicity, as the device defect distribution, which is defined by the mean values of  $\tau_c$  and  $\tau_e$  times,  $<\tau_c>$  and  $<\tau_e>$ , their standard deviations  $\sigma_{\tau_c}$  and  $\sigma_{\tau_e}$  and a correlation coefficient  $\rho$  between  $\sigma_{\tau_c}$  and  $\sigma_{\tau_e}$ . The  $D(\tau_e, \tau_c)$  can be analytically obtained with the equation 1.3.

$$D\left(\tau_{e}, \tau_{c}\right) = \frac{1}{2\pi\sigma_{<\tau_{c}>}\sigma_{<\tau_{e}>}\sqrt{1-\rho^{2}}} \cdot exp\left[-\frac{1}{2\left(1-\rho^{2}\right)} \cdot \left[\left(\frac{\tau_{c}-<\tau_{c}>}{\sigma_{<\tau_{c}>}}\right)^{2} \left(\frac{\tau_{e}-<\tau_{e}>}{\sigma_{<\tau_{e}>}}\right)^{2} - 2\rho\left(\frac{\tau_{c}-<\tau_{c}>}{\sigma_{<\tau_{c}>}}\right) \left(\frac{\tau_{e}-<\tau_{e}>}{\sigma_{<\tau_{e}>}}\right)\right]\right]$$

$$(1.3)$$

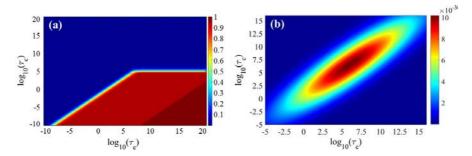

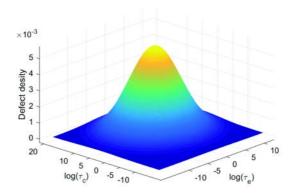

For instance, Figure 1.12 (a) shows the occupancy probability  $(P_{occ})$  together with an example of a 2-dimension representation of a particular defect distribution  $D(\tau_e, \tau_c)$  in the  $(\tau_e, \tau_c)$  space analytically calculated with equation 1.3 for an nMOS transistor.

Figure 1.12: (a) shows an example of the occupancy probability as a function of  $\tau_c$  and  $\tau_e$  at DC stress [98], and (b) shows an example of the defect distribution  $D(\tau_e, \tau_c)$  graph at  $V_{GS} = 1.2$ V,  $V_{DS} = 0$ V at 25°C.

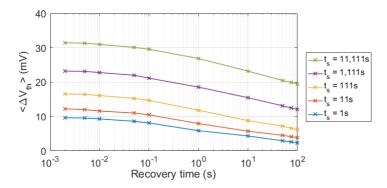

Using the proposed distribution of defects  $D(\tau_e, \tau_c)$  and the occupancy probability  $P_{occ}$ , the  $\Delta V_{th}$  induced variability can be determined for a particular transistor size and a particular stress time  $(t_s)$  and recovery time  $(t_r)$ . All defect transitions captured inside the product of  $D(\tau_e, \tau_c)$  and  $P_{occ}$  will contribute to the  $\Delta V_{th}$  for the experimental  $t_s$  and  $t_r$ . For instance, Figure 1.13 (a) shows an example of BTI measured recovery traces and the resulting PDO simulated traces in  $\Delta V_{th}$  in Figure 1.13 (b) on a pMOS transistor with a single stress/recovery aging cycle.

An important consideration regarding the  $D(\tau_e, \tau_c)$  shown in Figure 1.12 (b) must be extracted. The  $(\tau_c, \tau_e)$  space expands several orders of magnitude in time that cannot be fully covered experimentally. Conventional experimental windows used to characterize aging phenomena cover up to  $log_{10}(\tau_e)$  from 0 to 4 and  $log_{10}(\tau_c)$  from -3 to 2, thus, the experimental achieved portion of the  $D(\tau_e, \tau_c)$  is small. To overcome this limitation, large number of devices should be measured to achieve sufficient statistical data to reproduce the complete defect distribution. In this sense, the next section will describe the typical characterization procedures for aging testing introducing the new Enhanced Stress-Measurement methodology developed in this thesis for accurate BTI/HCI aging characterization.

Figure 1.13: (a) Experimental recovery traces in pFETs with abrupt defect discharge events. (b) Simulated recovery traces obtained using the PDO model using the same conditions of stress and recovery than in (a) [98].

# 1.4 BTI/HCI aging advanced characterization

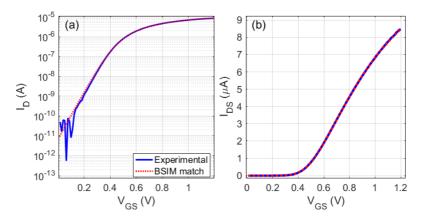

To obtain the electrical transistor parameter shifts under BTI/HCI aging degradation, the Measurement-Stress-Measurement (MSM) technique has become the most widely used methodology for device characterization. The MSM technique consists in concatenating a device pre-stress measurement period, followed by a stress period and, finally, a device post-stress measurement period. To accelerate aging process, an over-than-nominal  $V_{GS}$  and/or  $V_{DS}$  voltages should be applied, e.g., 2x or 3x the technology VDD. Moreover, during the pre- and post-stress measurement periods,  $I_{DS}-V_{GS}$  curve characteristics are commonly used to account for the device degradation. Finally, the MSM sequence is repeated sequentially, increasing the stress time to further extrapolate the device degradation to the nominal operation conditions. For instance, the stress time increase ratio can be defined exponentially (1s, 10s, 1,000s, 10,000s...) but this increase rate can be of any kind depending on the research needs.

Nevertheless, for BTI tests, the conventional MSM technique suffers from unwanted loss of measurement data, because a big portion of the accelerated degradation during stress starts recovering, without being measured, towards their non-stressed values immediately after the stress removal [100, 101]. To try to overcome this issue, several techniques have been proposed in the literature for aging characterization: the ultra-fast MSM (UF-MSM) [102],

the Ultra-Fast On-the-Fly (UF-OTF) [103,104], and the One Spot Drop Down (OSDD) methods [23].

The main issues related to the conventional MSM and UF-MSM characterization techniques is that they are prone to suffer from initial recovery data loss because of the time required to compute an  $I_{DS}$ - $V_{GS}$  curve after the stress. Moreover, the use of  $I_{DS}$ - $V_{GS}$  curves sweeps can mask the step-like behaviour of the recovery trend (see Figure 1.7).

In the UF-OTF case, the  $I_{DLIN}$  degradation is measured utilizing a small gate pulse around the  $V_{G-STRESS}$  value to account for the transconductance  $(g_m)$  change that results in  $\Delta V_{th} = \Delta I_{DLIN}/g_m$ . The main disadvantage of this technique is that it assumes that the total degradation in the  $I_{DLIN}$ is caused only by  $V_{th}$  degradation without incorporating the degradation of the  $\mu$  which, in fact, suffers from degradation, what can impact the accuracy of the method [105]. Finally, the OSDD methodology where the  $I_{DS}-t$  is characterized at the nominal biasing conditions after stress has become one of the best candidates to characterize the step-like behaviour of the measurement periods in aging tests. Nevertheless, the OSDD technique is prone to suffer from unwanted recovery data loss because of the time gap required to change from stress to measurement biasing conditions when measuring at wafer level. In this regard, the present section will describe in detail an experimental aging characterization methodology entirely developed in this thesis based on the classical MSM and OSDD methodologies enhanced to minimize recovery data loss and increasing accuracy of the measurement periods after stress.

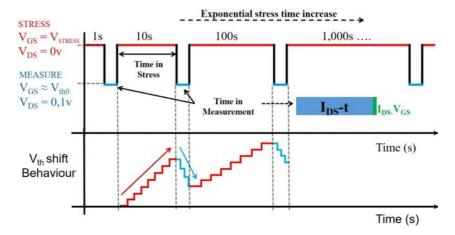

# 1.4.1 The Enhanced Stress-Measurement aging characterization methodology

The Enhanced SM method (eSM), based in the MSM and an the OSDD test techniques, utilizes a unique  $I_{DS}$ – $V_{GS}$  initial measurement period to account for the non-degraded device parameters followed by multiple stress-measurement (SM) cycles executed sequentially in order to account for the accelerated device parameters shifts. Two critical requirements should be considered during the execution of the eSM during aging characterization:

1. Accurate device terminal biasing: in order to guarantee a precise voltage biasing avoiding voltage drops due to cables, connectors or metal lines present in array-based IC designs, it is of much importance to use a

- Force-&-Sense voltage biasing system. The functionality principles of the Force-&-Sense system will be explained in Section 1.5.3.

- 2. The time gap between switching from stress to measurement periods should be as short as possible to not loss critical device measurement data at the very beginning of the measurement period. Moreover, it is important that the timing and duration of all stress and measurement phases should be the same for each device and precisely controlled. Otherwise, the data post-processing would get unnecessarily complex and less information would be collected.

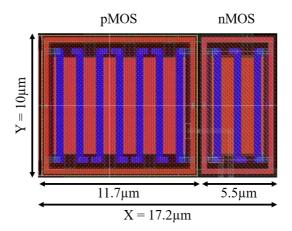

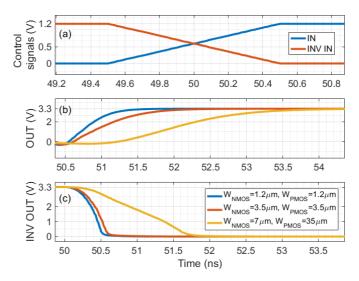

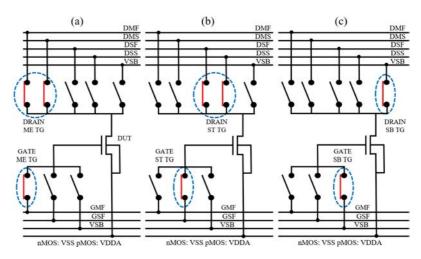

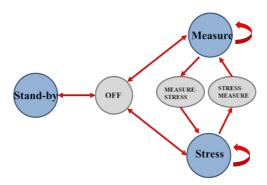

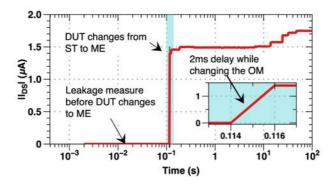

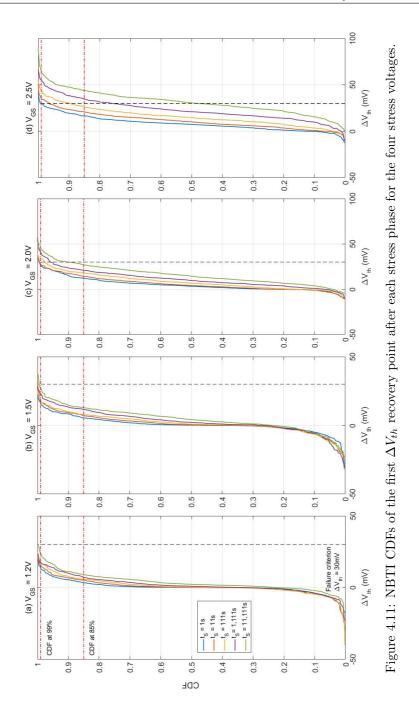

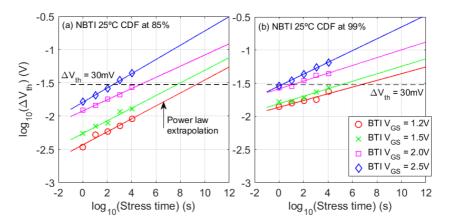

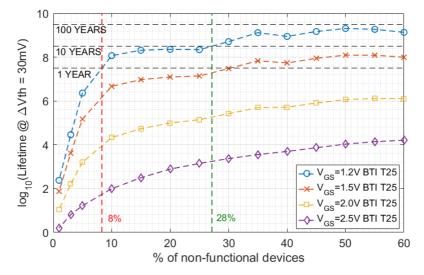

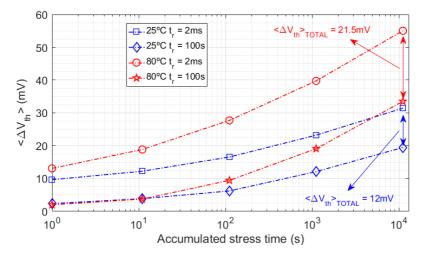

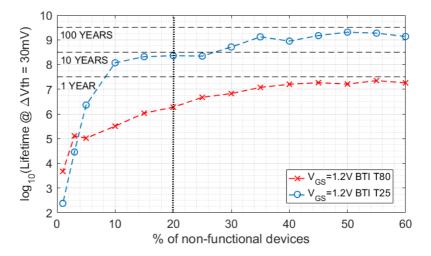

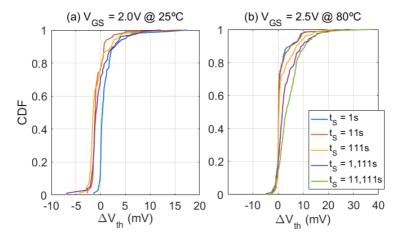

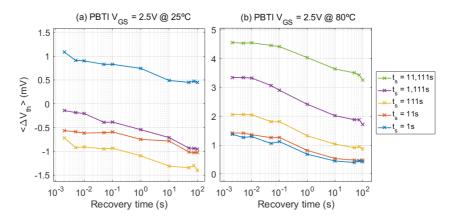

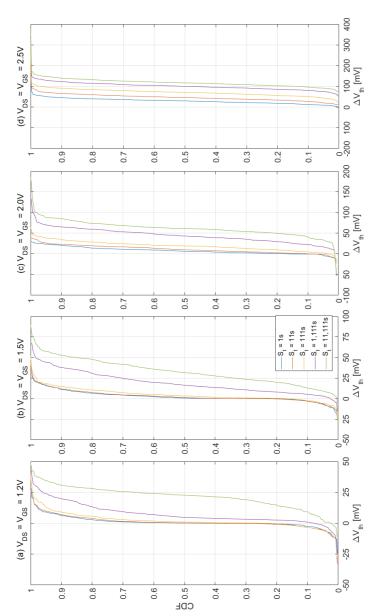

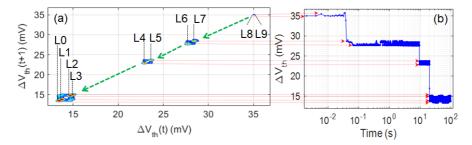

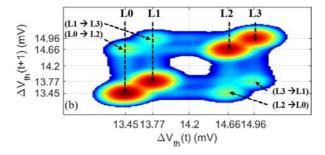

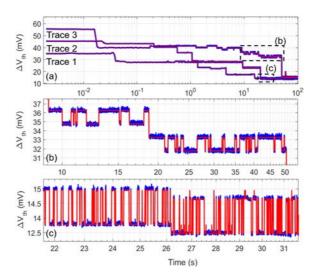

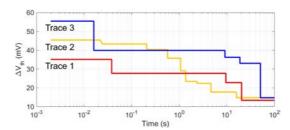

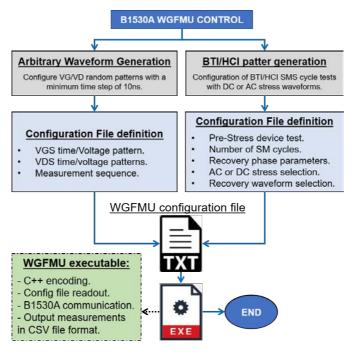

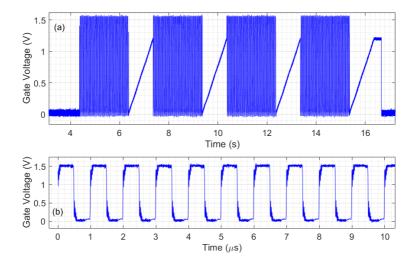

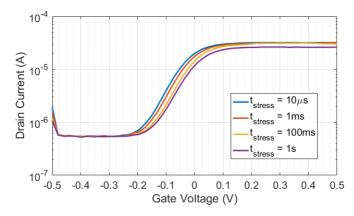

Figure 1.14 shows an illustrative example of the eSM methodology executing an accelerated BTI aging test scheme. In the example, four SM cycles are executed sequentially with red and blue colour lines respectively. The initial  $I_{DS} - V_{GS}$  curve characteristic utilized to account for the non-degraded device parameters is not shown in Figure 1.14. The eSM technique is conducted, for a single device, with the following the SM repeatable sequence: