# HIGH-PERFORMANCE AND ENERGY-EFFICIENT IRREGULAR GRAPH PROCESSING ON GPU ARCHITECTURES

Albert Segura Salvador

Doctor of Philosophy Department of Computer Architecture Universitat Politècnica de Catalunya

> Advisors: Jose-Maria Arnau Antonio González

> > July, 2020

### Abstract

Graph processing is an established and prominent domain that is the foundation of new emerging applications in areas such as Data Analytics, Big Data and Machine Learning. Applications such as road navigational systems, recommendation systems, social networks, Automatic Speech Recognition (ASR) and many others are illustrative cases of graph-based datasets and workloads. Demand for higher processing of large graph-based workloads is expected to rise due to nowadays trends towards increased data generation and gathering, higher inter-connectivity and inter-linkage, and in general a further knowledge-based society. An increased demand that poses challenges to current and future graph processing architectures.

To effectively perform graph processing, the large amount of data employed in these domains requires high throughput architectures such as GPGPU. Although the processing of large graph-based workloads exhibits a high degree of parallelism, the memory access patterns tend to be highly irregular, leading to poor GPGPU efficiency due to memory divergence. Graph datasets are sparse, highly unpredictable and unstructured which causes the irregular access patterns and low computation per data ratio, further lowering GPU utilization. The purpose of this thesis is to characterize the bottlenecks and limitations of irregular graph processing on GPGPU architectures in order to propose architectural improvements and extensions that deliver improved performance, energy efficiency and overall increased GPGPU efficiency and utilization.

In order to ameliorate these issues, GPGPU graph applications perform stream compaction operations which process the subset of active nodes/edges so subsequent steps work on compacted dataset. Although this optimization is effective, we show that GPGPU architectures are inefficient at performing stream compaction due to the data movements it entails, and end up representing a significant part of the execution time. After identifying these issues, we propose to offload this task to a programmable Stream Compaction Unit (SCU) hardware extension tailored to the requirements of these operations, while the remaining steps of the graph-based algorithm are efficiently executed on the GPU cores. The SCU is a small unit tightly integrated in the GPU that efficiently gathers the active nodes/edges into a compacted array in memory. We further extend the SCU to perform pre-processing of the data by filtering and reordering elements processed. Besides the benefits achieved with offloading, this pre-processed SCU-prepared data improves GPU efficiency by reducing workload and achieving larger memory coalescing. We evaluate our SCU design with a wide variety of state-of-the-art graph applications and extended GPGPU architectures. The results show that for High-Performance and for Low-Power GPU systems the SCU achieves speedups of 1.37x and 2.32x, 84.7% and 69% energy savings, at the cost of a small area increase of 3.3% and 4.1% respectively.

Memory divergence remains an important downside for irregular applications which struggle to fully exploit GPGPU performance. Although memory divergence can be improved by carefully considering architecture features and devoting significant programmer effort to modify algorithms with complex optimization techniques, it is far from an ideal solution which in the end shifts programmers priorities. We show that in graph-based GPGPU irregular applications these inefficiencies prevail, yet we find that it is possible to relax the strict relationship between thread and data processed to empower new optimizations. Based on this key idea, we propose the Irregular accesses Reorder Unit (IRU). The IRU is a novel hardware extension tightly integrated in the GPGPU pipeline that reorders data processed by the threads on irregular accesses which significantly improves memory coalescing. Additionally, the IRU is capable of filtering and merging duplicated irregular accesses which reduces the application workload. These optimizations improve overall memory hierarchy and deliver increased performance and energy efficiency. Programmers can easily utilize the IRU with a simple API, or compiler optimized generated code with the extended ISA instructions provided. We evaluate our proposal for a wide variety of state-of-the-art graph-based algorithms. The IRU achieves a memory coalescing improvement of 1.32x and a 46% reduction in the overall traffic in the memory hierarchy, which results in 1.33x and 13% improvement in performance and energy consumption respectively, while incurring in a 5.6% area overhead.

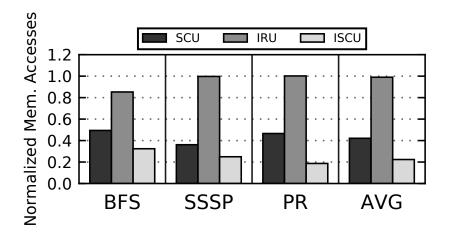

The increased need for greater data processing efficiency establishes high-throughput architectures, such as GPGPUs, as crucial devices in order enable efficient graph processing. Although efficient GPGPU graph processing faces many challenges, in our previous contributions we separately explore stream compaction offloading and improved coalescing of irregular access to ameliorate graph-based workload efficiency. While the SCU achieves significant speedups and large energy savings, it incurs in high contention in the Network-on-Chip (NoC). On the other hand, the IRU achieves more modest energy savings, but its optimizations are highly efficient at reducing contention in the NoC, showing up to a factor of 46% lower NoC traffic. We find that it is possible to leverage the strengths of both approaches to achieve synergistic performance improvements and higher graph processing efficiency. We do so by proposing a new unit, the IRU-enhanced SCU (ISCU). The ISCU employs the efficient mechanisms of the IRU to improve SCU stream compaction efficiency and throughput limitations. We first characterize the bottlenecks of our SCU contribution concluding that its major limitation is the large NoC traffic due to the pre-processing operations, i.e. filtering and grouping. With this insight we realize we can leverage the IRU hardware utilizing its strengths to efficiently perform the pre-processing. Consequently, the ISCU leverages both the powerful stream compaction offloading achieved by the SCU and the efficient filtering mechanism of the IRU employed to deliver pre-processing optimizations. We evaluate the ISCU for a wide variety of state-of-the-art graph-based algorithms and applications. Our final proposal achieves a 2.2x performance improvement and 90% energy savings which enable a 10x increase in energy-efficiency, improvements derived from a high reduction of 78% memory accesses, while incurring in 8.5% area overhead.

## Keywords

GPGPU, GPU, Graph Processing, Graph Exploration, Graph Applications, Data Analytics, Stream Compaction, Stream Compaction Unit, SCU, Energy-Efficient, High-Performance, Irregular Applications, Irregular Accesses, Irregular Graph Processing, GPGPU Graph Processing, Irregular accesses Reorder Unit, IRU, ISCU, IRU-Enhanced SCU, Workload Filtering, Reordering, Accelerator, Hardware Accelerator, Custom Hardware, Tailored Hardware, Programmability, Memory Divergence, Memory Coalescing, Memory Contention, Sparse Accesses, Branch Divergence, Control-Flow Divergence, Graphics Processing Unit, Computer Architecture.

## Acknowledgements

First and foremost, I would like to thank my advisors Professor Antonio González and Dr. Jose-Maria Arnau for their invaluable guidance through out my PhD study and research, their patience, motivation and many teachings. I would like to recognize their invaluable assistance, feedback and their involvement in my day-to-day work, for which I feel very grateful.

I would like to thank my defense committee; Tor M. Aamodt, Jordi Tubella Murgadas and Julio Sahuquillo Borrás, for their valuable feedback and comments. It is an honor to have such prestigious committee.

I wish to thank all the members and lab-mates of ARCO (the "The D6ers") which I was lucky enough to share many moments during my PhD and be part of this amazing group of people. Special thanks to Gem Dot, Enrique de Lucas, Martí Torrents, Josue Quiroga with whom I shared the beggining of my PhD. I was lucky to share the majority of my stay at ARCO with Hamid Tabani, Reza Yazdani, Martí Anglada, Marc Riera, Franyell Silfa and Syeda Azmath thank you for all the good moments that we shared at UPC. Finally, I would like to wish good luck to the newcomers Dennis Pinto, Diya Joseph, Pedro Exenberger, Jorge Sierra, Raúl Taranco and Mehdi Hassanpour, I am sure will do an amazing work.

I would also like to thank university colleagues, campus mates and friends with whom I shared many years, projects, difficulties and successes over the course of my stay in the University. Special thanks to Pedro Benedicte, Constantino Gomez, Cristóbal Ortega and David Trilla (the "Cache Miss" group) for the many experiences shared. And thanks to the many others with which I have cross path during this endeavor.

Finally, I would like to thank close friends and my family for their unconditional support and encouragement. To my parents for their love and support enabling me from the very beginning to pursue my passion for computers, electronics and education. To my brother and sister for the encouragement and for enduring me. And to my grandparents and extended family for their love, support and endorsement that has undoubtedly led me to where I am today. Finally, the last words I have saved for my partner with whom I closely shared many joys over the duration of this thesis, but also without doubt her love, encouragement and support have helped me overcome the inescapable periods of hardship that a PhD thesis entails.

## Declaration

I declare that the work contained in this thesis has not been submitted for any other degree or professional qualification except as specified. Some of the proposed techniques and results presented in this thesis has been published in the following papers:

- "SCU: A GPU Stream Compaction Unit for Graph Processing". Albert Segura, Jose-Maria Arnau, and Antonio González. International Symposium on Computer Architecture, June 2019 (ISCA '19). DOI: https://doi.org/10.1145/3307650.3322254

- "Irregular Accesses Reorder Unit: Improving GPGPU Memory Coalescing for Graph-Based Workloads".

Albert Segura, Jose-Maria Arnau, and Antonio González.

This work has been submitted for publication.

- "Energy-Efficient Stream Compaction Through Filtering and Coalescing Accesses in GPGPU Memory Partitions".

Albert Segura, Jose-Maria Arnau, and Antonio González.

This work has been submitted for publication.

Albert Segura Salvador

# Contents

| 1 | Intr | oducti | ion                                                             | <b>21</b> |

|---|------|--------|-----------------------------------------------------------------|-----------|

|   | 1.1  | Curren | nt Trends                                                       | 21        |

|   |      | 1.1.1  | GPGPU Popularization                                            | 25        |

|   |      | 1.1.2  | GPGPU Graph Processing                                          | 26        |

|   | 1.2  | Proble | em Statement                                                    | 28        |

|   |      | 1.2.1  | Memory Divergence                                               | 28        |

|   |      | 1.2.2  | Workload Duplication                                            | 30        |

|   | 1.3  | State- | of-the-art in GPGPU Irregular and Graph workloads               | 31        |

|   |      | 1.3.1  | Memory Divergence                                               | 32        |

|   |      | 1.3.2  | Memory Contention                                               | 32        |

|   |      | 1.3.3  | Stream Compaction                                               | 33        |

|   |      | 1.3.4  | Graph Processing                                                | 34        |

|   | 1.4  | Thesis | Overview and Contributions                                      | 36        |

|   |      | 1.4.1  | Energy-Efficient Graph Processing by Boosting Stream Compaction | 37        |

|   |      | 1.4.2  | Improving Graph Processing Divergence-Induced Memory Contention | 38        |

|   |      | 1.4.3  | Combining Strengths of SCU and IRU                              | 41        |

|   | 1.5  | Thesis | Organization                                                    | 42        |

| 2 | Bac  | kgrou  | nd                                                              | 45        |

|   | 2.1  | GPGF   | PU Architecture                                                 | 45        |

|   |      | 2.1.1  | Overview                                                        | 45        |

|   |      | 2.1.2  | Streaming Multiprocessor (SM)                                   | 46        |

|   |      |        |                                                                 |           |

|   |     | 2.1.3  | Caches and Memory Hierarchy                            | 48 |

|---|-----|--------|--------------------------------------------------------|----|

|   |     | 2.1.4  | Programmability                                        | 49 |

|   | 2.2 | High I | Performance GPGPU Code and Common Bottlenecks          | 52 |

|   |     | 2.2.1  | High Performance GPGPU Code                            | 52 |

|   |     | 2.2.2  | GPGPU Bottlenecks                                      | 52 |

|   |     | 2.2.3  | Ameliorating Performance Inefficiencies                | 53 |

|   | 2.3 | Graph  | processing algorithms on GPGPU architectures           | 54 |

|   |     | 2.3.1  | Breadth First Search (BFS)                             | 56 |

|   |     | 2.3.2  | Single Source Shortest Path (SSSP)                     | 57 |

|   |     | 2.3.3  | PageRank (PR)                                          | 58 |

| 3 | Exp | perime | ntal Methodology                                       | 61 |

| 0 | 3.1 |        | ation Systems Integration                              |    |

|   | 0.1 | 3.1.1  | Stream Compaction Unit (SCU)                           |    |

|   |     | 3.1.2  | Irregular accesses Reorder Unit (IRU)                  |    |

|   |     | 3.1.3  | IRU-enhanced SCU (ISCU)                                |    |

|   | 3.2 | Hardw  | vare Modeling and Evaluation                           |    |

|   |     | 3.2.1  | Stream Compaction Unit (SCU)                           | 64 |

|   |     | 3.2.2  | Irregular accesses Reorder Unit (IRU)                  | 66 |

|   |     | 3.2.3  | IRU-enhanced SCU (ISCU)                                | 66 |

|   | 3.3 | Graph  | Processing Datasets                                    | 67 |

|   |     | 3.3.1  | Graph Processing Algorithms                            | 67 |

|   |     | 3.3.2  | Graph Datasets                                         | 67 |

|   | Б   |        |                                                        |    |

| 4 |     | 00     | ficient Graph Processing by Boosting Stream Compaction | 69 |

|   | 4.1 |        | uction                                                 | 69 |

|   | 4.2 |        | n Compaction Unit                                      |    |

|   |     | 4.2.1  | SCU Compaction Operations                              |    |

|   |     | 4.2.2  | Hardware Pipeline                                      | 73 |

#### CONTENTS

|   |                          | 4.2.3                                                                                       | Breadth-First Search with the SCU                                                                                                                                                                                                                                                                      | 74                                                                                                                      |

|---|--------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|   |                          | 4.2.4                                                                                       | Single-Source Shortest Paths with the SCU                                                                                                                                                                                                                                                              | 75                                                                                                                      |

|   |                          | 4.2.5                                                                                       | PageRank with the SCU                                                                                                                                                                                                                                                                                  | 76                                                                                                                      |

|   | 4.3                      | Filteri                                                                                     | ng and Grouping                                                                                                                                                                                                                                                                                        | 77                                                                                                                      |

|   |                          | 4.3.1                                                                                       | Filtering/Grouping Unit                                                                                                                                                                                                                                                                                | 77                                                                                                                      |

|   |                          | 4.3.2                                                                                       | Filtering Operation                                                                                                                                                                                                                                                                                    | 78                                                                                                                      |

|   |                          | 4.3.3                                                                                       | Grouping Operation                                                                                                                                                                                                                                                                                     | 79                                                                                                                      |

|   |                          | 4.3.4                                                                                       | Breadth-First Search with the Enhanced SCU                                                                                                                                                                                                                                                             | 79                                                                                                                      |

|   |                          | 4.3.5                                                                                       | Single-Source Shortest Paths with the Enhanced SCU                                                                                                                                                                                                                                                     | 80                                                                                                                      |

|   |                          | 4.3.6                                                                                       | PageRank with the Enhanced SCU                                                                                                                                                                                                                                                                         | 81                                                                                                                      |

|   | 4.4                      | Exper                                                                                       | imental Results                                                                                                                                                                                                                                                                                        | 82                                                                                                                      |

|   |                          | 4.4.1                                                                                       | Energy Evaluation                                                                                                                                                                                                                                                                                      | 82                                                                                                                      |

|   |                          | 4.4.2                                                                                       | Performance Evaluation                                                                                                                                                                                                                                                                                 | 82                                                                                                                      |

|   |                          | 4.4.3                                                                                       | Enhanced SCU Results                                                                                                                                                                                                                                                                                   | 84                                                                                                                      |

|   |                          |                                                                                             |                                                                                                                                                                                                                                                                                                        |                                                                                                                         |

|   |                          | 4.4.4                                                                                       | Area Evaluation                                                                                                                                                                                                                                                                                        | 86                                                                                                                      |

|   | 4.5                      |                                                                                             | Area Evaluation                                                                                                                                                                                                                                                                                        | 86<br>86                                                                                                                |

| F |                          | Conclu                                                                                      | isions                                                                                                                                                                                                                                                                                                 | 86                                                                                                                      |

| 5 | Imp                      | Conclu<br>proving                                                                           | sions                                                                                                                                                                                                                                                                                                  | 86<br><b>89</b>                                                                                                         |

| 5 | <b>Im</b> p<br>5.1       | Conclu<br>proving<br>Introd                                                                 | uction                                                                                                                                                                                                                                                                                                 | 86<br><b>89</b><br>89                                                                                                   |

| 5 | Imp                      | Conclu<br>oroving<br>Introd<br>Irregu                                                       | usions                                                                                                                                                                                                                                                                                                 | 86<br><b>89</b><br>89<br>91                                                                                             |

| 5 | <b>Im</b> p<br>5.1       | Conclu<br>oroving<br>Introd<br>Irregu<br>5.2.1                                              | usions       Graph Processing Divergence-Induced Memory Contention         uction       uction         lar accesses Reorder Unit       uction         GPU Integration       uction                                                                                                                     | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> </ul>                                                              |

| 5 | <b>Im</b> p<br>5.1       | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2                                     | Isions                                                                                                                                                                                                                                                                                                 | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> </ul>                                                  |

| 5 | <b>Imp</b><br>5.1<br>5.2 | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2<br>5.2.3                            | Isions       Graph Processing Divergence-Induced Memory Contention         uction       Integration         Iar accesses Reorder Unit       Integration         GPU Integration       Integration         Hardware Overview and Processing       Integration         Reordering Hash       Integration | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> <li>97</li> </ul>                                      |

| 5 | <b>Im</b> p<br>5.1       | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2<br>5.2.3<br>IRU P                   | Isions       Graph Processing Divergence-Induced Memory Contention         uction       Integration         Iar accesses Reorder Unit       Integration         GPU Integration       Integration         Hardware Overview and Processing       Integration         Reordering Hash       Integration | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> <li>97</li> <li>98</li> </ul>                          |

| 5 | <b>Imp</b><br>5.1<br>5.2 | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2<br>5.2.3<br>IRU F<br>5.3.1          | Isions                                                                                                                                                                                                                                                                                                 | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> <li>97</li> <li>98</li> <li>99</li> </ul>              |

| 5 | <b>Imp</b><br>5.1<br>5.2 | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2<br>5.2.3<br>IRU F<br>5.3.1<br>Exper | Isions                                                                                                                                                                                                                                                                                                 | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> <li>97</li> <li>98</li> <li>99</li> <li>102</li> </ul> |

| 5 | <b>Imp</b><br>5.1<br>5.2 | Conclu<br>proving<br>Introd<br>Irregu<br>5.2.1<br>5.2.2<br>5.2.3<br>IRU F<br>5.3.1          | Isions                                                                                                                                                                                                                                                                                                 | <ul> <li>86</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> <li>97</li> <li>98</li> <li>99</li> <li>102</li> </ul> |

#### CONTENTS

|   |     | 5.4.3   | Performance Evaluation           | . 105 |

|---|-----|---------|----------------------------------|-------|

|   |     | 5.4.4   | Energy Evaluation                | . 105 |

|   |     | 5.4.5   | Area Evaluation                  | . 106 |

|   | 5.5 | Conclu  | isions                           | . 106 |

| 6 | Con | nbining | g Strengths of the SCU and IRU   | 109   |

|   | 6.1 | Introd  | uction                           | . 109 |

|   | 6.2 | IRU-ei  | nhanced SCU (ISCU)               | . 111 |

|   |     | 6.2.1   | Hardware Modifications           | . 113 |

|   |     | 6.2.2   | Detailed Processing              | . 114 |

|   | 6.3 | ISCU    | Programmability                  | . 115 |

|   |     | 6.3.1   | Graph Processing Instrumentation | . 116 |

|   | 6.4 | Experi  | imental Results                  | . 117 |

|   |     | 6.4.1   | Energy Evaluation                | . 117 |

|   |     | 6.4.2   | Performance Evaluation           | . 118 |

|   |     | 6.4.3   | Comparison with SCU and IRU      | . 119 |

|   |     | 6.4.4   | Memory Improvements Evaluation   | . 121 |

|   |     | 6.4.5   | Area Overhead Evaluation         | . 121 |

|   | 6.5 | Conclu  | isions                           | . 121 |

| 7 | Con | clusio  | ns and Future Work               | 123   |

|   | 7.1 | Conclu  | usions                           | . 123 |

|   | 7.2 | Contri  | butions                          | . 125 |

|   | 7.3 | Open-   | Research Areas                   | . 126 |

|   |     |         |                                  |       |

# List of Figures

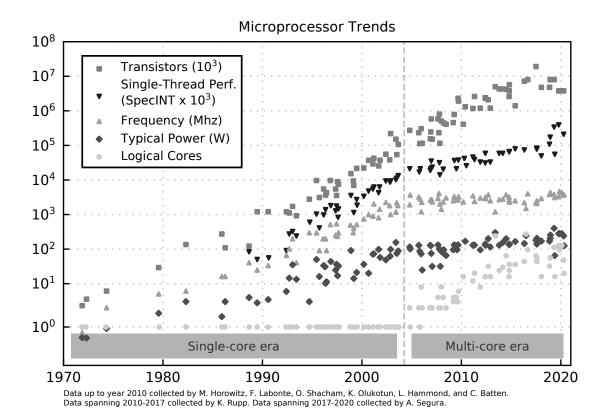

| 1.1 | Trends in Microprocessor characteristics over the last decades [131]. Until the 2000s decade microprocessors transistors, single-thread performance (SpecINT), frequency and power increased steadily following Moore's Law and Dennard Scaling. Mid 2000s decade sees a clear shift in trends as increasing instruction-level parallelism (ILP) gets diminishing returns; frequency and power increase is halted while the increasing transistors numbers is dedicated to increase number of cores. Single-thread performance increase is reduced while systems provide higher performance by leveraging multi-threading. | 22 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

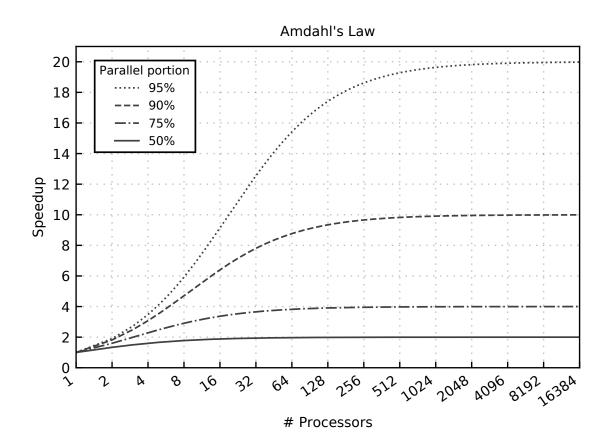

| 1.2 | Maximum achievable performance speedup of a parallel application in increasingly parallel systems dictated by Amdahl's law [3, 59]. To achieve high speedup by means of parallel execution, a very high percentage of a program has to be parallel: even a high 95% parallel application maximum speedup does not exceed 20x. This clearly showcases the limitations of improving architecture performance by means of increased number of processors.                                                                                                                                                                     | 24 |

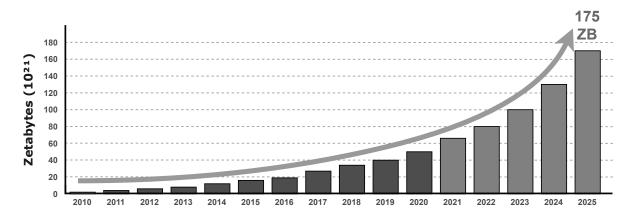

| 1.3 | Global worldwide growth of data predicted by the IDC over the next years [124]. The depicted trend indicates that the increase in worldwide data is exponential, consequently as capacity increases we will need higher performance systems to be able to use the data to process and analyze it                                                                                                                                                                                                                                                                                                                           | 27 |

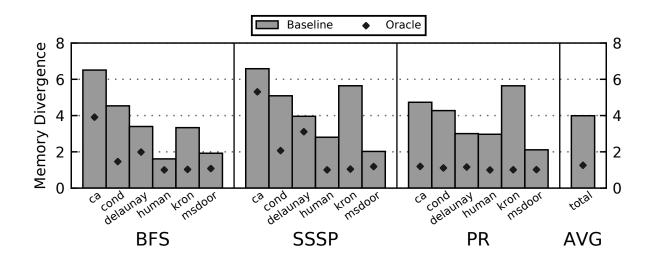

| 1.4 | Memory coalescing over different benchmarks and applications for the Baseline<br>and an Oracle. The memory coalescing is measured as the number of L1 cache<br>accesses per warp-level memory instruction, the higher this value the worse the<br>memory coalescing an application has. It ranges from 32 accesses to 1 access per<br>warp instruction. The measured coalescing is represented by the Baseline, while<br>the Oracle shows potential memory coalescing                                                                                                                                                      | 29 |

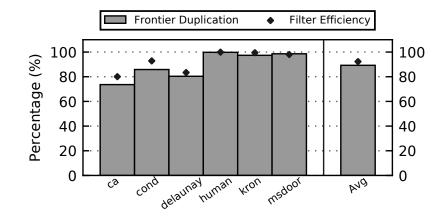

| 1.5 | Frontier workload duplication and software filtering efficiency for BFS algorithm. The frontier duplication indicates the amount of duplicated elements within the frontiers, averaging a 89% for BFS. Meanwhile the filtering efficiency, which averages 92% for BFS, indicates the percentage of workload eliminated either because of detected duplication within the frontier, or due to elements that had already been processed previously. Filtering efficiency is higher due to this suppression of workload across frontiers (i.e. already processed elements).                                                   | 31 |

#### LIST OF FIGURES

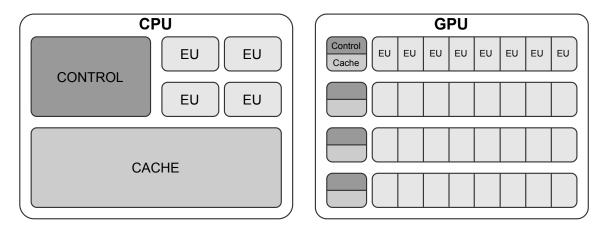

| 2.1 | Diagram of the transistor area distribution of a CPU versus a GPU architecture, showcasing the design principles of each architecture. CPU designs dedicate comparatively more area to improved control logic and caching, whereas GPUs rely on simpler control logic and caches while featuring much more execution units [76].                                                                                                                                                                                                             | 46 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

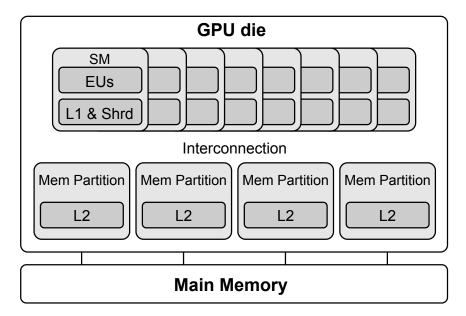

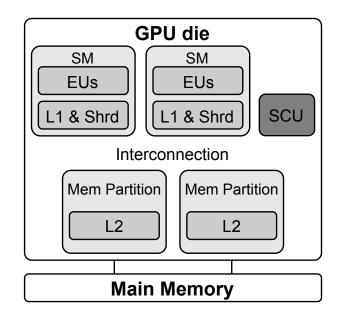

| 2.2 | Overview of a GPGPU architecture showing the GPU die with 16 Streaming Multiprocessors (SM) interconnected with 4 Memory Partitions (MP) and the main memory located outside of the die. The most relevant internal components are showcased, for the SM are the Execution Units (EUs), L1 data cache and shared memory, whereas for the MP is the L2 data cache.                                                                                                                                                                            | 47 |

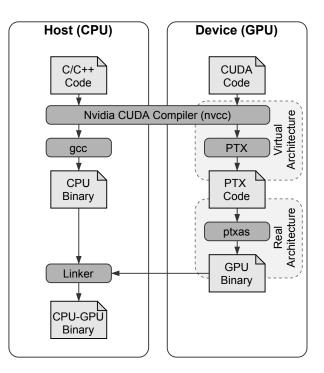

| 2.3 | Simplified compilation diagram showcasing the process to generate and integrate<br>a GPU kernel with a CPU application with a CUDA toolkit. The CUDA code<br>is compiled with the nvcc into generic Parallel Thread Execution (PTX) [118]<br>assembler code, that is later processed into GPU binary Streaming Assembler<br>(SASS) assembler code. The same process compiles the regular CPU code and<br>integrates both binaries in a final FAT binary that can contain multiple SASS<br>versions to execute on different GPU architectures | 50 |

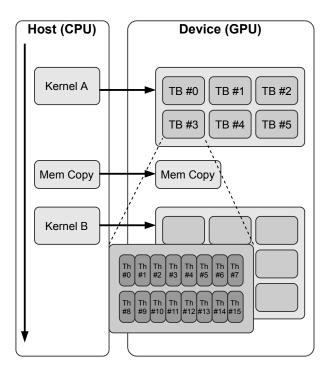

| 2.4 | Interaction between a Host (CPU) and the Device (GPU). The CPU is responsible to perform data movements to the GPU memory, configure the parameters and initiate the launch of the GPU Kernel.                                                                                                                                                                                                                                                                                                                                               | 51 |

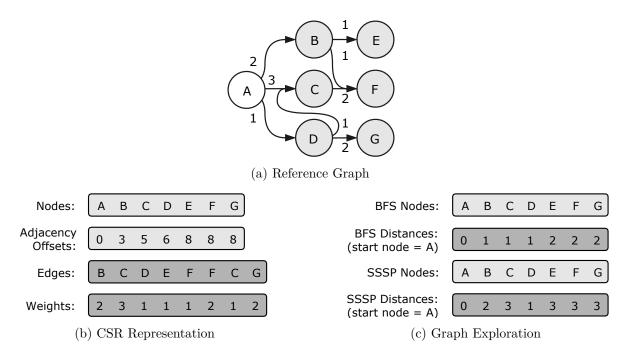

| 2.5 | Graph example (a) with its corresponding CSR representation (b) and the exploration results (i.e. computation result per node) when using BFS and SSSP on the starting node A (c). Graph (a) shows each node inside a circle with its corresponding label and each edge (arrow) with their corresponding weight. The CSR representation (b) contains the nodes and edges arrays, while it indicates with the adjacency offsets for each node the corresponding edges (with their corresponding weight value).                                | 55 |

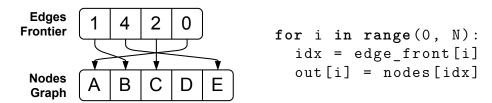

| 2.6 | Example of a graph application processing an edge frontier and its irregular accesses generated when accessing the nodes in the graph. A pseudo-code example showcases the particular irregular access performed.                                                                                                                                                                                                                                                                                                                            | 55 |

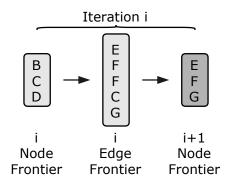

| 2.7 | Execution of a given iteration of BFS on the graph in Figure 2.5a. The input node frontier generates an edge frontier which is evaluated and creates the next node frontier to process.                                                                                                                                                                                                                                                                                                                                                      | 56 |

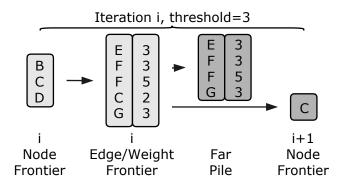

| 2.8 | Execution of a given iteration of SSSP with a threshold=3 on the graph in Figure 2.5a. The input node frontier generates an edges/weight frontier which is broken down based on the threshold into two structures: the Far Pile and the next node frontier to process. This distinction improves SSSP performance on GPU architectures                                                                                                                                                                                                       | 57 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

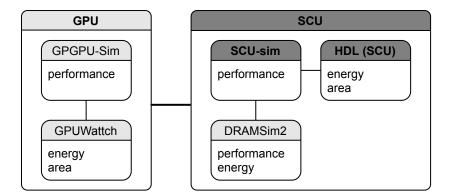

| 3.1 | SCU complete simulation system comprising GPU simulation and SCU simulation to obtain performance, energy and area of the entire system. The darker color shows our contributions to the simulation system.                                                                                                                               | 62 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

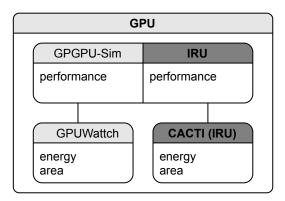

| 3.2 | IRU simulation system extending the GPGPU-Sim simulator to obtain perfor-<br>mance, energy and area of the IRU contribution. The darker color shows our<br>contributions to the simulation system                                                                                                                                         | 63 |

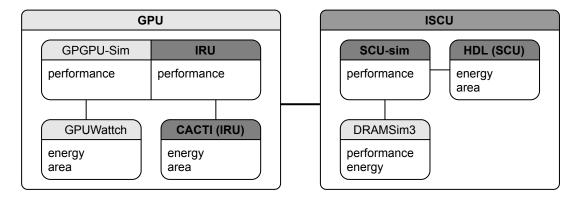

| 3.3 | ISCU complete simulation system comprising IRU-extended GPU simulation and SCU simulation to obtain performance, energy and area of the entire system. The darker color shows our contributions to the simulation system.                                                                                                                 | 64 |

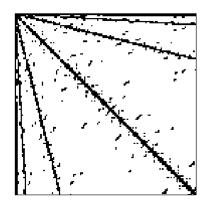

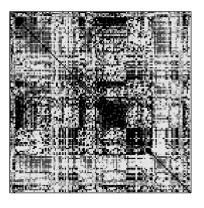

| 3.4 | Sparsity plots showcasing inter-connections between the nodes of the graphs introduced in Table 3.5 and gathered from the graph repository [30]. The gray-scale indicates the degree of connectivity of each of the nodes on the graph. The sparsity plots help to understand the high diversity in locality and structure of the graphs. | 68 |

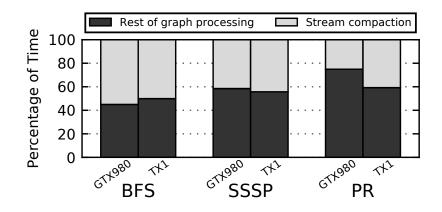

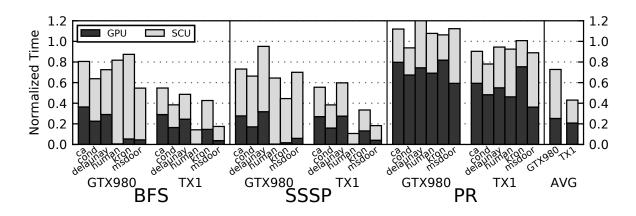

| 4.1 | Breakdown of the average execution time for several applications (Table 3.5) and three graph primitives (BFS, SSSP and PR). Measured on an NVIDIA GTX 980 and NVIDIA Tegra X1. Darker color indicates execution time spent on graph processing, while lighter color highlights time performing stream compaction operations.              | 70 |

| 4.2 | Overview of a GPGPU architecture featuring a SCU attached to the interconnection. The depicted GPU shows 2 SM similar to an NVIDIA Tegra X1                                                                                                                                                                                               | 72 |

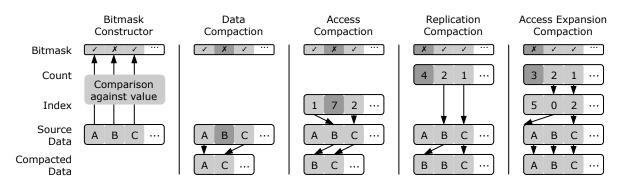

| 4.3 | SCU operations required to implement stream compaction capabilities, illustrated with the data that each operation uses and generates. Arrow direction indicates flow of data.                                                                                                                                                            | 72 |

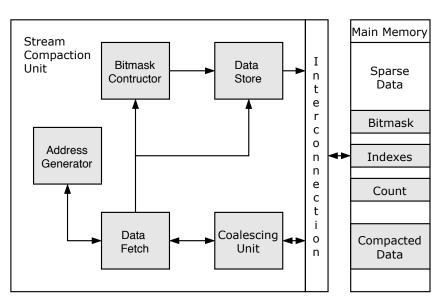

| 4.4 | Overview of the baseline pipelined architecture of the Stream Compaction Unit<br>with the connection of the different components as well as its interconnection<br>to the main memory. The rightmost column shows the data used for the SCU<br>operations allocated in Main Memory.                                                       | 73 |

| 4.5 | Pseudo-code of GPGPU BFS program modified to use the SCU to offload stream compaction operations.                                                                                                                                                                                                                                         | 74 |

| 4.6 | Pseudo-code of GPGPU SSSP program modified to use the SCU to offload stream compaction operations.                                                                                                                                                                                                                                        | 75 |

| 4.7 | Pseudo-code of GPGPU PR program modified to use the SCU to offload stream compaction operations                                                                                                                                                                                                                                           | 76 |

#### LIST OF FIGURES

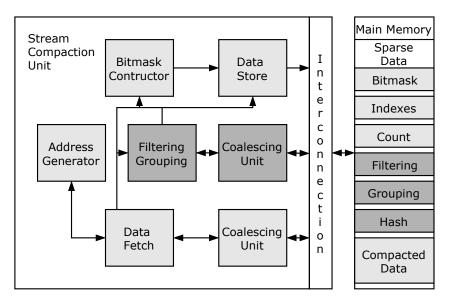

| 4.8  | Improved pipelined architecture of the SCU. The darker color highlights the exten-<br>sion additions of the filtering and grouping hardware enabling their corresponding<br>operations, as well as an extra coalescing unit. The rightmost column includes<br>the additional data which is allocated in Main Memory and is required for the<br>SCU pre-processing operations featuring the filtering/grouping vectors and the<br>in-memory hash. | 77 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Pseudo-code of the additional operations for a GPGPU BFS program to use the enhanced SCU.                                                                                                                                                                                                                                                                                                                                                        | 80 |

| 4.10 | Pseudo-code of the additional operations for a GPGPU SSSP program to use the enhanced SCU.                                                                                                                                                                                                                                                                                                                                                       | 81 |

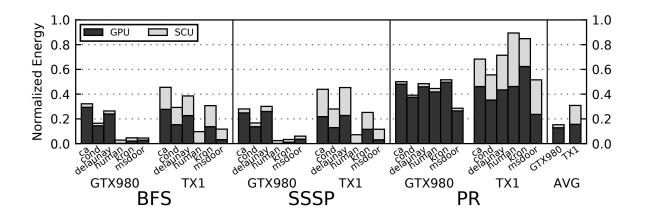

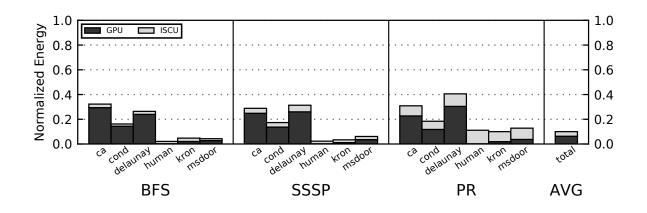

| 4.11 | Normalized energy for BFS, SSSP and PR primitives on several datasets and<br>in our two GPU systems using the proposed SCU. Baseline configuration is the<br>corresponding GPU system (GTX980 or TX1) without the SCU. The figure also<br>shows the split between GPU and SCU energy consumption.                                                                                                                                                | 83 |

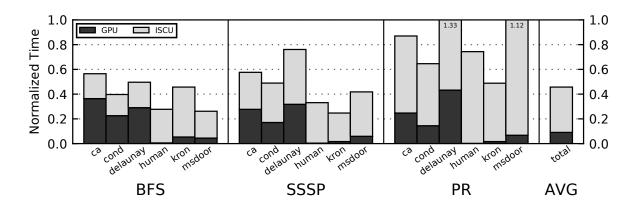

| 4.12 | Normalized execution time for BFS, SSSP and PR primitives on several datasets<br>and in our two GPU systems using the proposed SCU. Baseline configuration is<br>the corresponding GPU system (GTX980 or TX1) without the SCU. The figure<br>also shows the split between GPU and SCU execution time                                                                                                                                             | 83 |

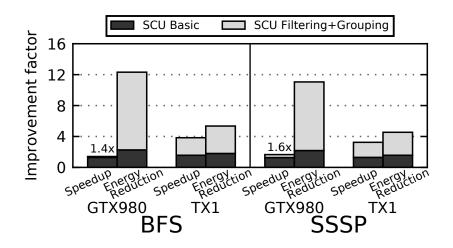

| 4.13 | Speedup and Energy Reduction breakdown, showing separately the improvements due to the Basic SCU and the Enhanced SCU in both GTX980 and TX1 architectures. The Enhanced SCU achieves important energy reductions on the GTX980, whereas it delivers higher speedups on the TX1                                                                                                                                                                  | 84 |

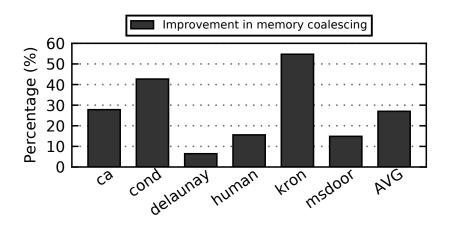

| 4.14 | Improvement of the memory coalescing when using the grouping operation, for<br>the SSSP algorithm on the TX1 GPU. The baseline configuration is SCU using<br>only the filtering operations                                                                                                                                                                                                                                                       | 85 |

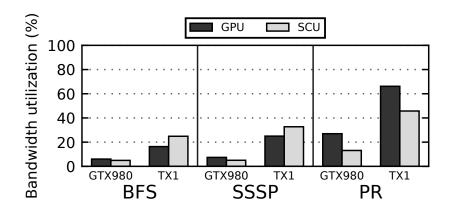

| 4.15 | Memory bandwidth utilization for the graph applications running on a Baseline GPU system and on a GPU system incorporating the SCU. Note that each GPU system has a different bandwidth and the figure indicates utilization of peak bandwidth.                                                                                                                                                                                                  | 86 |

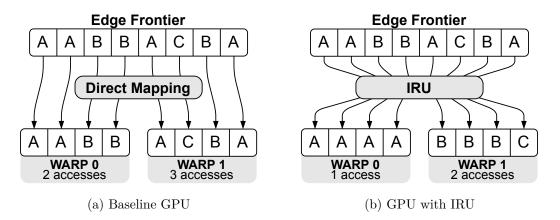

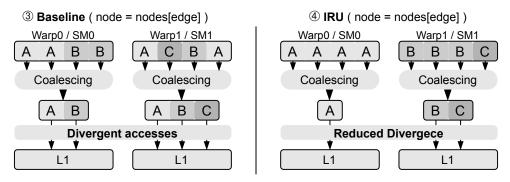

| 5.1  | Memory Coalescing improvement achieved by employing the IRU (5.1b) to reorder data elements that generate irregular accesses versus a Baseline GPU (5.1a) execution.                                                                                                                                                                                                                                                                             | 90 |

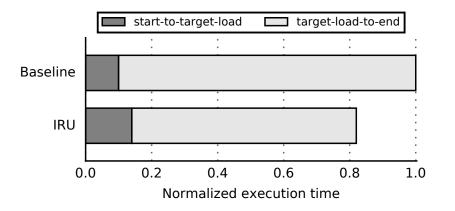

| 5.2  | Warp average normalized execution with and without IRU. The dark bar indicates execution time until the target load is serviced, and the light bar from service to finalization. The IRU achieves speedups despite the overhead introduced                                                                                                                                                                                                       | 92 |

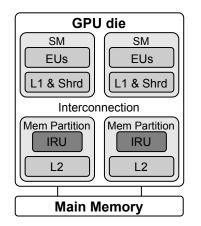

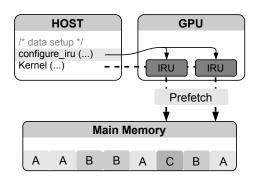

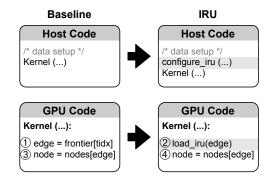

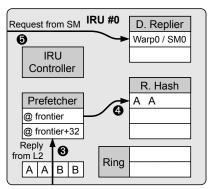

| 5.3  | IRU integration with the GPU at different levels: architectural (a), program model (b) and execution (c,d,e). The execution showcases how the program (b) works on the Baseline and the IRU, operating with the two warps and data from Figure 5.1.                                                                                                                                                                                              | 93 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |

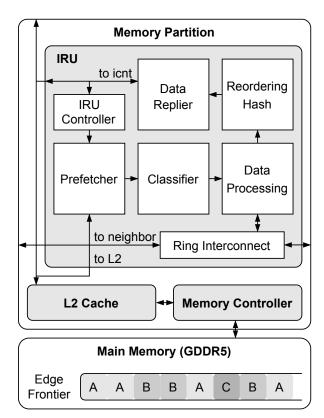

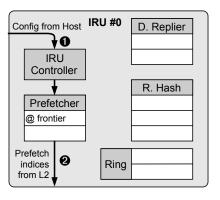

| 5.4  | Architecture and the internal processing performed by the IRU. The indices in memory (from Figure 5.1) are processed by two IRU partitions (IRU 0 shown), which is later replied to a request coming from Warp 0 in SM 0 95                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

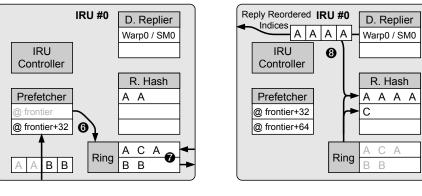

| 5.5  | Hash insertion diagram showcasing how an element is used for the hashing function<br>and how it is stored in the hash data of the <i>Reordering Hash.</i>                                                                                                                                          |

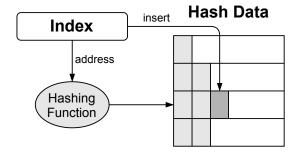

| 5.6  | IRU processing of two arrays with filtering enabled. The "edges" is the indexing array, while the "weight" is the secondary array. The filtering operation is an addition                                                                                                                          |

| 5.7  | API additional functions. Multiple definitions used due to optional parameters 100                                                                                                                                                                                                                 |

| 5.8  | Simple instrumentation of the BFS algorithm Kernel using the API of the IRU 100                                                                                                                                                                                                                    |

| 5.9  | Simple instrumentation of the SSSP algorithm Kernel using the API of the IRU.<br>The <i>load_iru</i> operation is using all the parameters. The variables <i>edge</i> and <i>weight</i> are reordered together while <i>pos</i> retrieves their original position in the array which is later used |

| 5.10 | Simple instrumentation of the PR algorithm Kernel using the API of the IRU.<br>The <i>load_iru</i> operation is used with all parameters, and additionally, filtering deactivates threads with is noted by the <i>active_thread</i> variable 101                                                   |

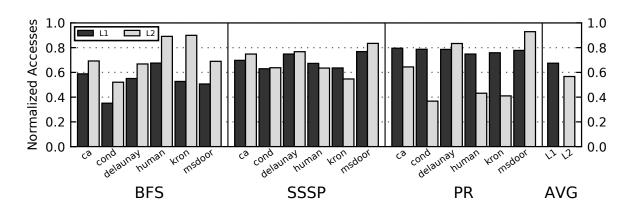

| 5.11 | Normalized accesses to L1 and L2 caches of the IRU enabled GPU system against<br>the Baseline GPU system. Significant reductions are achieved across BFS, SSSP<br>and PR graph algorithms and every dataset                                                                                        |

| 5.12 | Normalized interconnection traffic between SM and MP of the IRU enabled GPU system against the Baseline GPU system. Significant reductions are achieved across BFS, SSSP and PR graph algorithms and every dataset 103                                                                             |

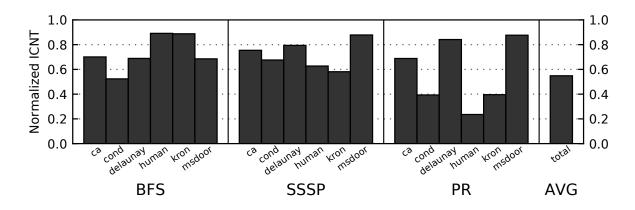

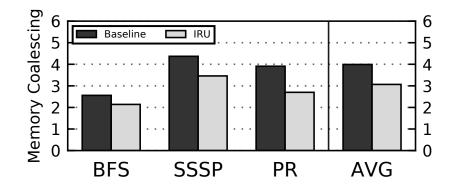

| 5.13 | Improvement in memory coalescing achieved with the IRU over the Baseline GPU system. Vertical axis shows the number of memory requests sent to the L1 cache on average per each memory instruction, i.e. how many memory requests are required to serve the 32 threads in a warp                   |

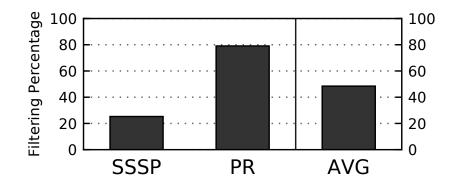

| 5.14 | Filtered percentage of elements processed by the IRU in our IRU enabled GPU system. The IRU achieves significant filtering effectiveness for different graph algorithms                                                                                                                            |

| 5.15 | Normalized execution time and normalized energy consumption achieved by the IRU enabled GPU with respect to the baseline GPU system. The IRU shows consistent speedups and energy savings achieved across BFS, SSSP and PR graph algorithms and all the different datasets                         |

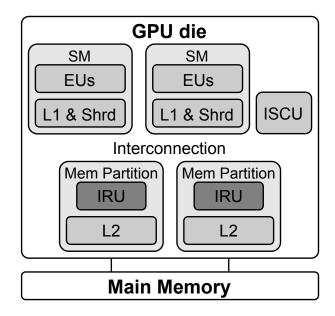

| 6.1  | Overview of a GPGPU architecture featuring the ISCU attached to the intercon-<br>nection as well as the IRU located in the Memory Partitions                                                                                                                                                       |

#### LIST OF FIGURES

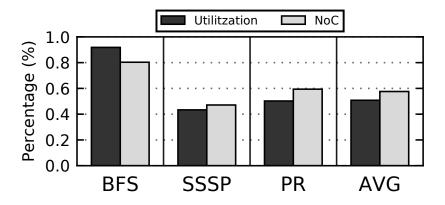

| 6.2 | Utilization of the SCU pre-processing component (i.e. filtering/grouping unit) and the percentage of NoC traffic devoted to filtering/grouping operations. The utilization is the percentage of cycles that the filtering/grouping unit is active over total execution. The SCU invests a large number of cycles and NoC transactions in the data pre-processing operations. | 113 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

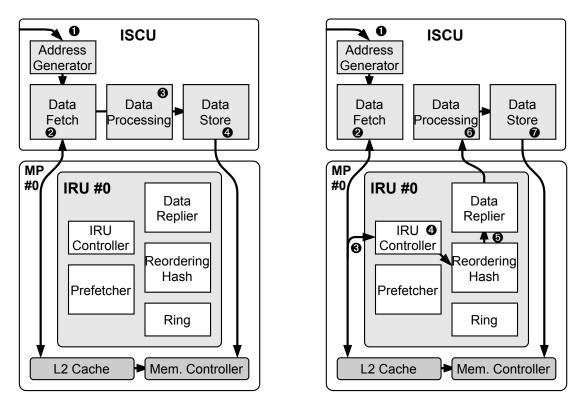

| 6.3 | Overview of the behavior and data-flow for the different ISCU operations per-<br>formed on the ISCU hardware extension together with its interactions with the<br>IRU extension                                                                                                                                                                                              | 115 |

| 6.4 | Pseudo-code of the additional operations for a GPGPU PR program to use the ISCU.                                                                                                                                                                                                                                                                                             | 117 |

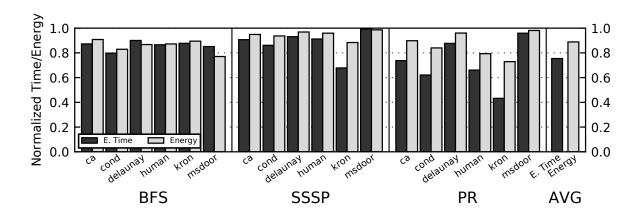

| 6.5 | Normalized energy consumption of the ISCU enabled GPU with respect to the baseline GPU system (GTX 980), showing the split between GPU and ISCU energy consumption. Significant energy savings are achieved across BFS, SSSP and PR graph algorithms and every dataset                                                                                                       | 118 |

| 6.6 | Normalized execution time of the ISCU enabled GPU with respect to the baseline GPU system, showing the split between GPU and ISCU execution time. Significant speedups are achieved across BFS, SSSP and PR graph algorithms and the majority of the datasets.                                                                                                               | 118 |

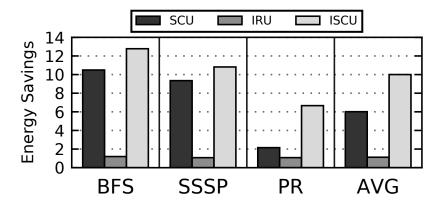

| 6.7 | Energy savings of the SCU, IRU and ISCU with respect to the baseline GPU system. The ISCU synergetically improves energy savings achieved with SCU and IRU.                                                                                                                                                                                                                  | 119 |

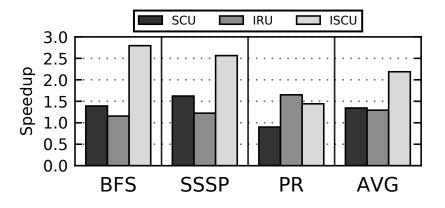

| 6.8 | Speedup of the SCU, IRU and ISCU with respect to the baseline GPU system.<br>The ISCU synergetically improves speedups achieved with SCU and IRU. The<br>ISCU is able to overcome the SCU overheads which slowed down PR, delivering<br>significant speedups.                                                                                                                | 120 |

| 6.9 | Normalized memory accesses of the SCU, IRU and ISCU with respect to the baseline GPU system. The ISCU synergetically improves the memory reduction achieved with SCU and IRU due to the optimizations which significantly reduce memory traffic.                                                                                                                             | 120 |

|     |                                                                                                                                                                                                                                                                                                                                                                              |     |

# List of Tables

| 3.1 | GPGPU-Sim and GPUWattch configuration parameters to model the High-<br>Performance GTX980 and Low-Power Tegra X1 GPU systems                                              | 62 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | SCU hardware parameters.                                                                                                                                                  | 65 |

| 3.3 | SCU scalability parameters selection for the GTX980 and TX1 GPU                                                                                                           | 65 |

| 3.4 | IRU hardware requirements per partition                                                                                                                                   | 66 |

| 3.5 | Benchmark graph datasets collected from well-known research repositories $[30, 33]$ .                                                                                     | 67 |

| 6.1 | Comparison between SCU, IRU and ISCU hardware extensions for Graph Process-<br>ing on GPGPU architectures, showcasing their main functionality and performance<br>metrics | 11 |

# Introduction

This chapter reviews GPU architectures strengths and introduces current trends and challenges of graph processing on modern GPU architectures, thus establishing the motivation behind this work. It also explores the specific problems addressed in this thesis, reviews how they are approached by state-of-the-art works and finally introduces the novel proposals and contributions of this work.

#### 1.1 Current Trends

Over the last decade, Graphic Processing Units (GPU) have produced a dramatic change in computer systems steaming from the increased demand for higher performance. Current GPU prevalence is mainly fueled by emerging workloads that exhibit high data parallelism. Big Data analytics [129], Neural Networks [57] and Deep Learning [82, 135, 168] are clear examples of extremely popular applications that benefit from the high degree of parallelism offered by GPUs. Other applications include the adoption of newer, more demanding video decoding and multimedia standards (i.e 4K and 8K resolutions [156]), the increased demand for graphics fidelity coming from the gaming industry as seen for Virtual Reality systems (VR) [158] and image detection [78], speech recognition [22] and, finally, the automotive industry with self-driving cars [16, 71]. These examples, among many other applications, have hugely increased the demand for high processing throughput and huge amounts of parallelism, both of which GPU systems have been able to provide by leveraging many simpler and lower frequency core counts, in contrast with single or few high performance core counts of traditional CPU systems. This approach has established GPUs as an essential and very successful component of modern computing systems.

Figure 1.1: Trends in Microprocessor characteristics over the last decades [131]. Until the 2000s decade microprocessors transistors, single-thread performance (SpecINT), frequency and power increased steadily following Moore's Law and Dennard Scaling. Mid 2000s decade sees a clear shift in trends as increasing instruction-level parallelism (ILP) gets diminishing returns; frequency and power increase is halted while the increasing transistors numbers is dedicated to increase number of cores. Single-thread performance increase is reduced while systems provide higher performance by leveraging multi-threading.

Up to the 2000 decade, shrinking transistor technology nodes was a big contribution to delivering new computer systems with increased single core performance. Moore's Law, formalized by 1965 [101] and reformulated by 1975 [102], predicted the doubling of transistor density in new semiconductor systems every two years. Meanwhile, Dennard scaling [32], formulated by 1974, predicted power density to stay constant with new transistor nodes: by halving area, every new iteration would allow for 30% reduced circuit delays and reduced voltages, which would result in equal power dissipation with double the number of transistors yet allowing a 1.4x increase in frequency. Combined, Moore's Law and Dennard scaling would doubled computer chip performance every 18 months, a rule which drove industry forward for many decades.

In practice, many factors limited the scaling down of area, circuit delays and voltages. Area reductions where constrained due to issue logic and caches not scaling linearly with area in addition to the increase number of wires of newer computer designs [49]. Circuit delays reductions were not as aggressive as predicted by Dennard scaling, in part due to the increased number of wires [60]. Finally, voltages did not scale accordingly to Dennard scaling instead decreasing by 15% every two years [49], consequently increasing power density. Overall, the performance increase observed up to the 2000 decade as seen in Figure 1.1 was not solely achieved by technology node scaling but in addition to computer architecture innovations. Novel innovations such as new deeper pipelines, improved branch predictors, out-of-order execution, new instruction set architecture (ISA), and improved memory organizations among many others were a huge contribution in performance improvements by reducing latency and improving instruction-level parallelism (ILP). Meanwhile, many new power-aware techniques such as clock gating [163], power gating [65] and the inclusion of dark silicon [36] reduced the amount of switching transistors which kept power density constrained [49].

By mid 2000's decade, architectural improvements reached a point of diminishing returns as increased frequencies drove power leakage up, thus increasing overall power dissipation. Consequently, the steady frequency increase on newer systems was halted, yet transistor counts kept increasing every year, as it can be seen in Figure 1.1. This meant that computer architects had at their hands more transistors without any way to fully utilize them all on single core systems. This disparity prompted the exploitation of thread-level parallelism (TLP) techniques, driving industry to design multi-core and multi-threaded systems with increasing CPU core and thread counts, while relying on parallelization to deliver performance improvements [150]. Nonetheless, parallelization is a complex problem. Amdahl's law [3, 59] dictates the maximum performance speedup achievable in relation with the parallelizable section of a program, thus revealing that to achieve significant speedups a large portion of the application has to be parallelizable, as depicted in Figure 1.2. Additionally, CPUs were not primarily optimized for parallelization. CPU systems were mainly optimized for single thread performance with complex execution units and pipeline optimizations, and low latency execution thanks to an extensive cache hierarchy. The end of single thread performance ILP scaling ushered in the popularization of programmable GPU architectures, or General Purpose GPU (GPGPU) [46], which in contrast to CPUs heavily focused on parallelization by providing huge core counts with lower performance, leveraging aggressive multi-threading (i.e. TLP) to tolerate main memory latency.

Meanwhile, the memory system had a different evolution. Technology improvements brought higher DRAM density thus facilitating capacity increases at a similar pace to Moore's Law [143]. nonetheless memory performance did not scale accordingly. Despite technology scaling facilitating frequency increases, DRAM memory latency was largely dominated by wire delays; as such latency reductions depend on scaling down circuit delays, reductions which felt short on the Dennard scaling predictions, as discussed previously. Consequently, an increasing disparity emerged between computing and memory performance scaling, this disparity lead to the increased relevance of memory latency as the principal system performance limitation which had computers hitting the Memory Wall [165]. Over the years, architectural and technological innovations have persistently attempted to close this disparity and thus push the memory wall further into the future, despite the fundamental technology scaling limitations. More sophisticated caches and prefetchers, latency hiding techniques, deeper memory hierarchies, improved memory controllers, and 3D stacking [123] together with processing in memory [103] are among the constant stream of architectural innovations limiting memory latency negative performance impact. While multi-core CPU designs have invested significantly on these increasingly sophisticated memory improvements, GPGPU architectures leverage their vast core counts and unparalleled TLP to hide memory latency, thus pushing forward the memory wall performance limitations.

Figure 1.2: Maximum achievable performance speedup of a parallel application in increasingly parallel systems dictated by Amdahl's law [3, 59]. To achieve high speedup by means of parallel execution, a very high percentage of a program has to be parallel: even a high 95% parallel application maximum speedup does not exceed 20x. This clearly showcases the limitations of improving architecture performance by means of increased number of processors.

Over the last decade Moore's Law has started to slow down [155, 31]; industry manufacturers have been experiencing recurrent delays [64] of their production of newer technology nodes due to complexity, unreliability and overall increased cost of already few atoms-wide transistors. Further increased costs and complexity required to improve performance by shrinking the technology will put further pressure on computer architects to come up with new architectures and increasingly specialized hardware [31] as means to deliver performance improvements. The multi-core era and the GPGPU specialization ended up being very effective to drive further computer system performance increases; many GPGPU parallel applications [97] significantly outperform counterpart applications in traditional CPU systems which has facilitated new research domains and applications such as Deep Learning [100] and Autonomous Driving [15]. The prevalence of GPGPU has transformed traditional systems in more heterogeneous and specialized computing systems. A shift, which GPGPU architectures started, that has paved the way towards more diverse and specialized hardware, with the current inclusion of accelerators for specific applications and future widespread specialized hardware.

#### 1.1.1 GPGPU Popularization

GPGPU architectures have managed to achieve broad adoption in the last decade despite being novel architectures which require considerable knowledge of the underlying hardware and new programming models to achieve high performance. It is interesting to take a look at their evolution over the years to understand the design choices and trade-offs that led to current GPGPU architectures.

Early GPU or video cards go way back in time to the beginning of the computer architecture, with contemporary designs first appearing in the 1990 decade. Early GPUs consisted of fixed function units for graphic operations which provided hardware acceleration to render 2D and 3D graphics for games and graphical tools. Prominent examples can be found in the console gaming industry, such as the Reality Coprocessor (RCP) of the Nintendo 64 [104] and the Sony GPU for the PlayStation [120], which first coined the term. On the other hand, the 3dfx Voodoo video card [1] is an example of early GPU in the PC market. The beginning of the 2000 decade saw the appearance of programmable GPUs together with graphical pipeline toolkits such as OpenGL [114] and DirectX [34]. In turn, this enabled the GPU to perform linear algebra, crudely implemented before by mapping data into textures and applying shader programs [79]. At the time, GPUs featured hardware acceleration closely correlated with the different stages of the rendering pipeline with the notable addition of programmable pixel and vertex shader units first introduced by the NVIDIA GeForce 3 NV20 [43]. This early programmability allowed simple pre-processing of pixels and vertices, but computer architects had to carefully balance the execution time and bottlenecks of the different stages of the graphics pipeline. The inclusion of newer stages in the DirectX and OpenGL pipelines marked a dead end of this fixed-function pipeline approach [133].

NVIDIA released its first contemporary GPGPU system by late 2006 with the Tesla microarchitecture, the first release of their programmable unified shader architecture [153]. It was first featured in the NVIDIA 8800 GTX (Tesla G80) [44] which introduced a redesigned SIMT pipeline which is the base design of today NVIDIA GPGPU architectures. Similar unified shader architecture was promptly adopted by competitors such as the ATI Radeon HD 2000 [122] by 2007. This programmable unified shader replaced previous stages as it was capable of processing vertex, fragments and geometry kernels alike. Additionally, the first release of the Compute Unified Device Architecture (CUDA) [25] toolkit facilitated programmability for general purpose applications, enabling computing on an impressive 96 unified shader (Executing Units or Cores in NVIDIA terminology), specially compared to poor parallelism of CPUs at the time.

NVIDIA SIMT architecture consists of a number of Streaming Multiprocessors (SM) with a private L1 data cache and a scratchpad memory (Shared Memory), while the SMs in a GPU share an L2 cache. Each SM includes a number of cores (i.e. execution units), typically in multiples of 32, and execute instructions in lock-step in groups of 32 threads, i.e. a warp in NVIDIA terminology. GPGPU SM are typically clocked at a lower frequency and are less complex than counterpart CPU designs since they are designed with simpler in-order instruction execution pipeline. GPGPU architectures leverage thread-level parallelism (TLP) and memory-level parallelism (MLP) which are provided by the cores and the huge memory bandwidth of the architecture and the memory respectively, and counter the lower performing cores and higher memory latency.

#### **CHAPTER 1. INTRODUCTION**

GPGPU architectures specific design choices and reliance on thread and memory level parallelism limits the set of applications fit for GPGPU acceleration and reveal some inefficiencies of the architecture in particular scenarios. Since warp's threads are executed in lock-step, they progress simultaneously through the pipeline and execution units. Consequently to implement branch behaviour, threads in a warp can be activated and deactivated with the use of predication registers and a divergence SIMT stack. Thread deactivation becomes an important source of inefficiencies referenced as branch divergence issues which limits the TLP . Divergence on performing memory accesses are another major source of inefficiencies that arise as the consequence of un-collocated memory accesses performed by the threads in a warp which limits both thread and memory level parallelism.

Over the 2010 decade GPGPU architectures have increased performance and energy efficiency without deviating significantly from the SIMT unified shader pipeline, while incrementally incorporating new features in each new architecture. One of the initial additions was the upgrade to 32-bit executing units from previous 24-bit ones, a relic of a past as 24-bit were enough to process RGB pixels. Over time, half, single and double floating point made its way into the cores, as well as improved atomic operations with the aim to support more complex and general purpose applications. More recently, the addition of Tensor Cores have allowed fast Matrix Multiply and Accumulate operations for Neural Network applications. Overall, each new architecture has brought improved performance and energy efficiency while accommodating higher number of cores and parallelism, reaching 4608 CUDA cores for the NVIDIA Titan RTX [42] released late 2018.

GPGPU adoption has been very broad from personal computers, to gaming consoles, data centers, high-performance computing (HPC), supercomputers, as well as mobile platforms and self-driving cars. Functionality additions such as floating point operations allowed GPGPUs to be used for algebra computations and science field computations such as fluid dynamics[55], particle docking [97] and others [10, 87]. By November 2019, nearly 40% of the total compute performance of the TOP500 supercomputers list (626 petaflops) came from GPU-accelerated systems [72]. The high parallelism delivered has improved processing of Big Data applications, data base operations[7], and large graph processing[161] as well as Neural Networks [57] and Deep Learning models [82, 135]. The latter addition of Tensor Cores greatly improves training and inference of deep learning applications and neural networks, in turn improving image, vision and speech recognition [125], for applications such as image classification [35], automatic speech recognition (ASR) [136] or audio de-noising [110]. Finally GPGPU architectures have also found a place in mobile systems such as the Nintendo Switch [105] with a NVIDIA Tegra X1 [111] or in self-driving cars such as the NVIDIA Tegra X2 [111] and Pascal GPGPU found, up to 2014, in Model S cars[108, 154] from the Tesla manufacturer.

#### 1.1.2 GPGPU Graph Processing

World data generation and total global data size is increasing exponentially. The International Data Group (IDG) [66] predicts a total of 175 ZB for 2025, an increase of 3.5x in five years [124], which is likely to continue in the future. In today's and future knowledge-based and highly interconnected society, a huge range of devices and new technologies are likely to generate this data. The advent of Internet-of-Things (IoT) [5], and the new implementation of 5G mobile

Figure 1.3: Global worldwide growth of data predicted by the IDC over the next years [124]. The depicted trend indicates that the increase in worldwide data is exponential, consequently as capacity increases we will need higher performance systems to be able to use the data to process and analyze it.