## On the use of multilayer hexagonal boron nitride as dielectric in micro/nano-electronic devices

Yuan Bin

**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (**www.tdx.cat**) i a través del Dipòsit Digital de la UB (**diposit.ub.edu**) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX ni al Dipòsit Digital de la UB. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX o al Dipòsit Digital de la UB (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (**www.tdx.cat**) y a través del Repositorio Digital de la UB (**diposit.ub.edu**) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR o al Repositorio Digital de la UB. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR o al Repositorio Digital de la UB (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (**www.tdx.cat**) service and by the UB Digital Repository (**diposit.ub.edu**) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized nor its spreading and availability from a site foreign to the TDX service or to the UB Digital Repository. Introducing its content in a window or frame foreign to the TDX service or to the UB Digital Repository is not authorized (framing). Those rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

PhD thesis dissertation

## On the use of multilayer hexagonal boron nitride as dielectric in micro/nano-electronic devices

Author: Mr. Bin Yuan Director: Dr. Mario Lanza

# On the use of multilayer hexagonal boron nitride as dielectric in micro/nano-electronic devices

Memoria presentada para optar al grado de doctor por la

Universidad de Barcelona

Programa de doctorado en Nanociencias

Bin Wan Total

Autor: Mr. Bin Yuan Director: Dr. Mario Lanza Tutor: Dr. Albert Cirera Hernandez

UNIVERSITAT DE BARCELONA

To my family,

#### Acknowledgments

First, I would like to thank my supervisor, Professor Mario Lanza, for his help and contribution while pursuing my PhD. There is no doubt that Prof. Mario spent a lot of energy and time on my research design and discussion. During that period, he taught me how to be a qualified researcher and good working habits. After studying and experimenting, I learned more about two-dimensional materials and their application in the electronic field. I am proud to say that my PhD process was great and enjoyable. The memory of this period would be a treasure in my life.

I am grateful to my fellow group members who supported me during my PhD studies. Dr. Tingting Han, Dr. Kaichen Zhu, Ms. Yaqing Shen, Ms. Wenwen Zheng, Ms. Yue Ping, Ms. Yue Yuan, Dr. Jonas Weber, and Dr. Sebastian Pazos significantly helped my research. I am grateful for Dr. Marco Antonio Villena's review of a part of my thesis and for his valuable suggestions. Their hard work and study attitude positively impacted me and motivated me to work hard in the future.

Sincere gratitude should also go to my tutor, Professor Albert Cirera Hernandez, for his guidance, Professor Juan Marcos Fernandez, and Prof. Jordi Colomer Farrarons for providing valuable feedback. I am also thankful to the advising advisory committee members, Dr. Cèsar Ferrater, Dr. Anna Vila, and Dr. Estela Martín, for reviewing my annual report and making useful suggestions.

I also would like to thank the University of Barcelona and the Institute of Functional Nano and Soft Materials (FUNSOM) of Soochow University for providing the environment and platform for my research work. I appreciate the help and advice provided by the laboratory. They are professional in their position and kindly to provide help. The administration staff are also appreciated for their work and help. Finally, many thanks go to my family, especially my wife Huiting Chen, who always supports and encourages me.

## Index

### Contents

| Abstract 1                                                                   | 1 - |

|------------------------------------------------------------------------------|-----|

| Chapter 1: General introduction                                              | 3 - |

| 1.1. Introduction                                                            | 3 - |

| 1.1.1. Introduction of dielectric materials                                  | 3 - |

| 1.1.2. Application of dielectric materials in electronic devices             | 5 - |

| 1.1.3. 2D materials for next-generation electronic devices                   | 7 - |

| 1.1.4. Introduction of h-BN 11                                               | 1 - |

| 1.1.5. h-BN production 12                                                    | 2 - |

| 1.1.6. h-BN application in electronic devices                                | 5 - |

| <b>1.2. Main contribution of the thesis</b> 19                               | 9 - |

| 1.2.1. Objectives of the Thesis 19                                           | 9 - |

| 1.2.2. Key findings 20                                                       | 0 - |

| 1.2.3. Thesis Outline 21                                                     | 1 - |

| 1.3. List of publications 21                                                 | 1 - |

| Chapter 2: Device fabrication methods 23                                     | 3 - |

| 2.1. Mechanical exfoliation method 23                                        | 3 - |

| 2.2. Dry transfer of 2D materials 24                                         | 4 - |

| 2.3. Wet transfer method for CVD-grown 2D materials 27                       | 7 - |

| 2.4. Device electrode fabrication 29                                         | 9 - |

| 2.4.1. Photolithography for micro-scale device electrode 29                  | 9 - |

| 2.4.2. Electron beam lithography for nano-scale device electrode 32          | 2 - |

| 2.4.3. Metal deposition for electrode 34                                     | 4 - |

| <b>2.5. Summary</b> 35                                                       | 5 - |

| Chapter 3: Dielectric breakdown of exfoliated h-BN in micro-scale devices 37 | 7 - |

| <b>3.1. Introduction</b> 37                                                  | 7 - |

| <b>3.2. Experiments</b> 38                                                   | 8 - |

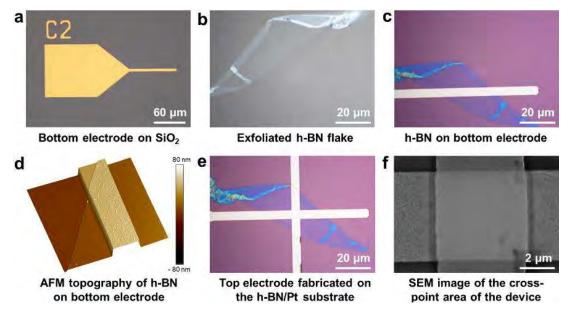

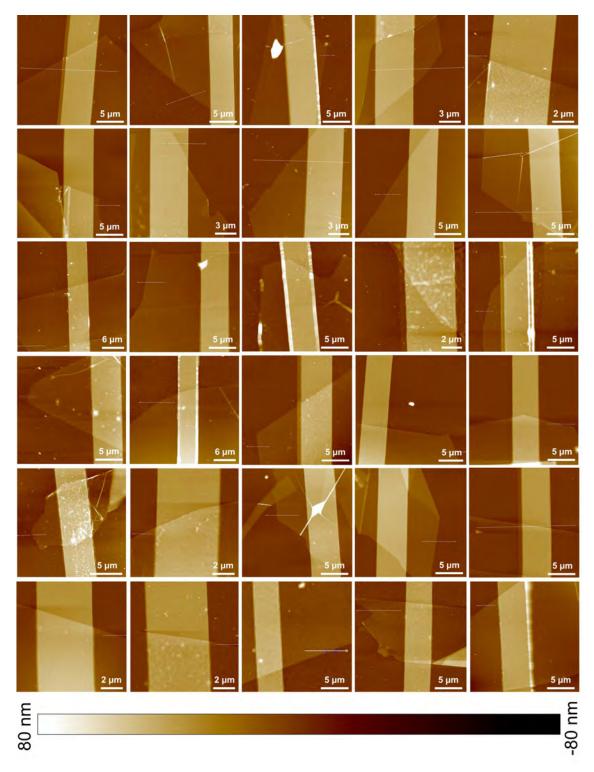

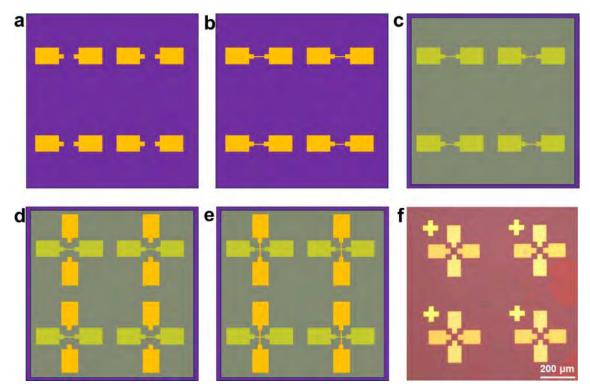

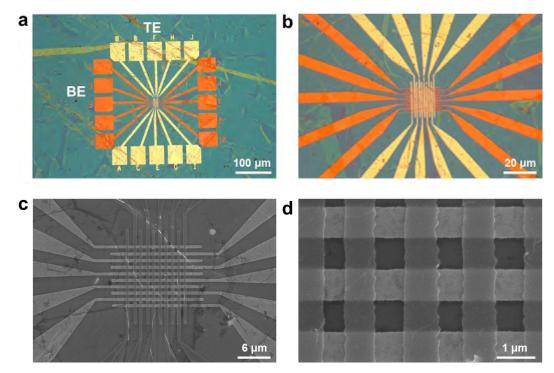

| 3.2.1. Cross-point micro-scale device fabrication process 38                 | 8 - |

| <b>3.2.2.</b> Characterization of materials and devices 40                   | 0 - |

| 3.3. Result and discussion 41                                                | 1 - |

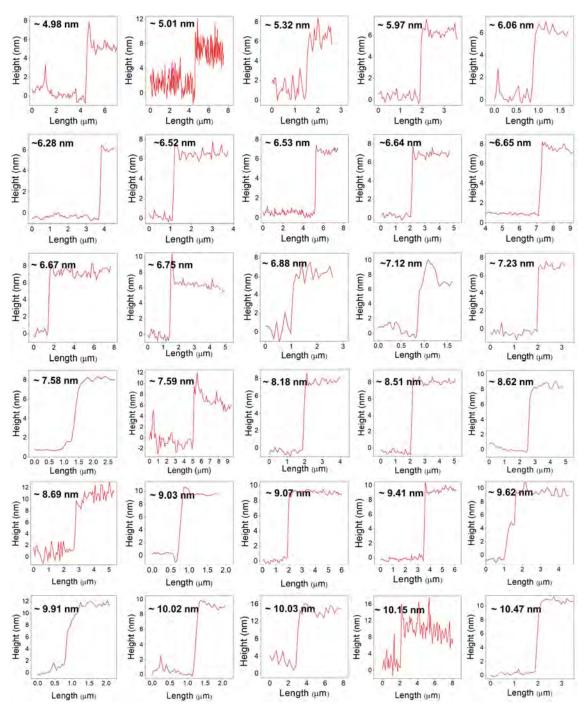

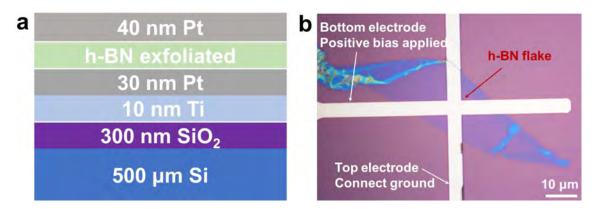

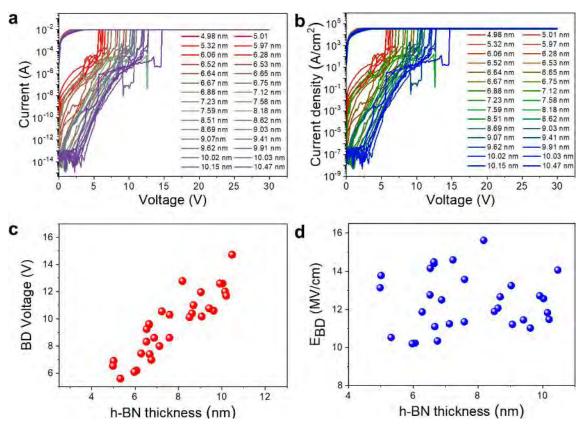

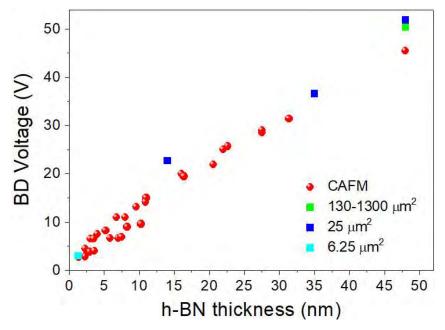

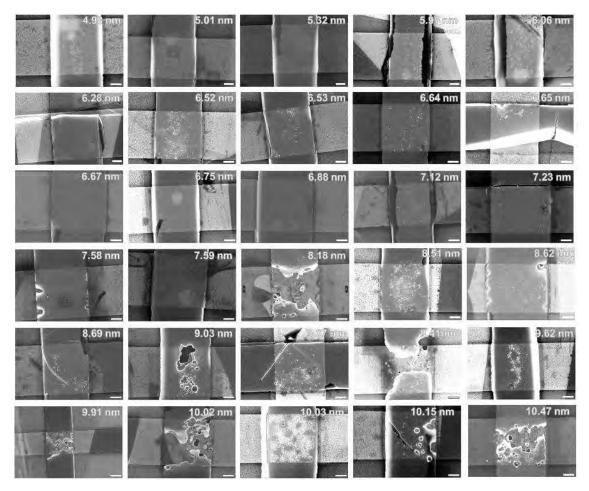

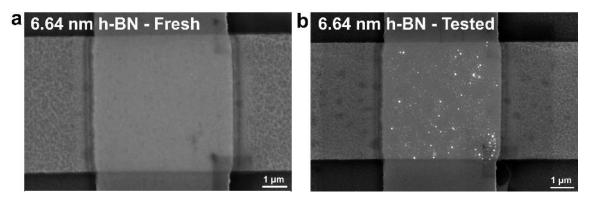

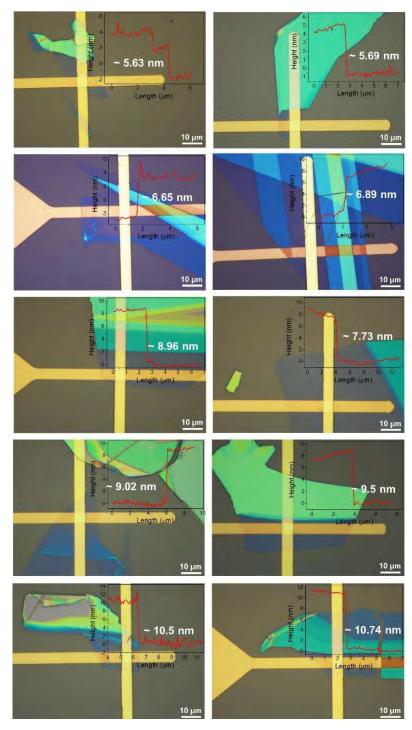

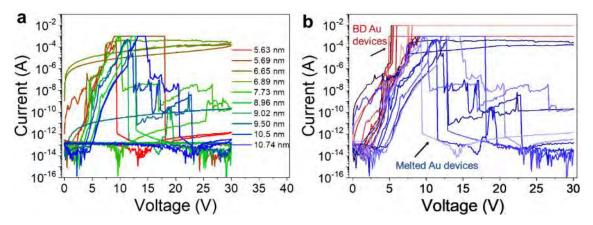

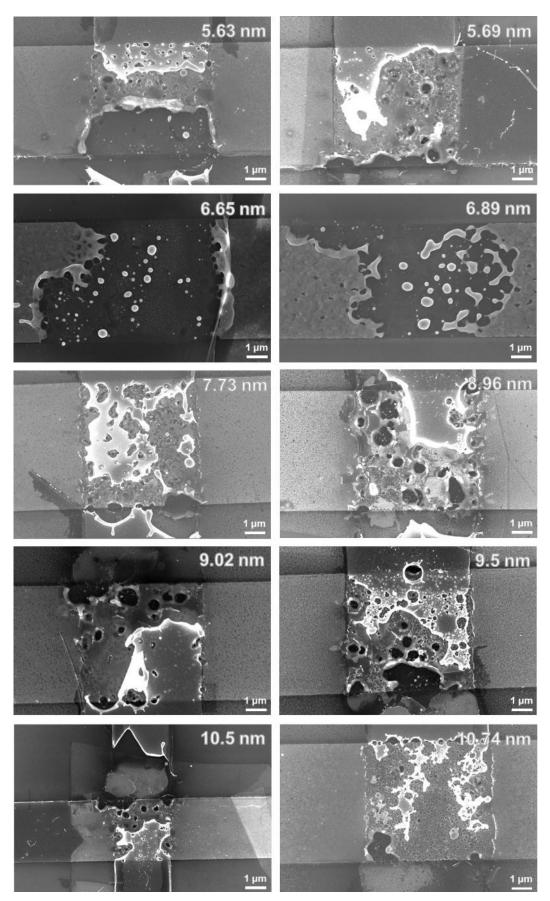

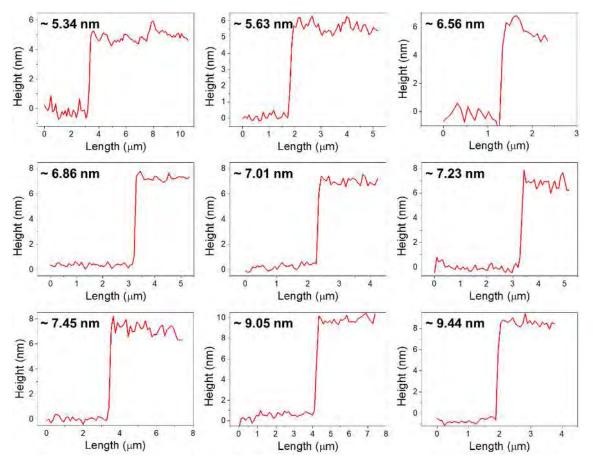

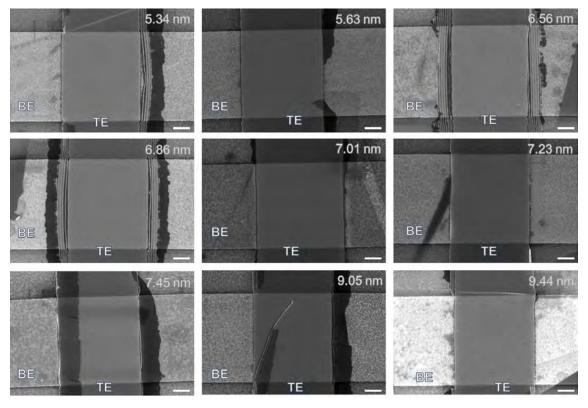

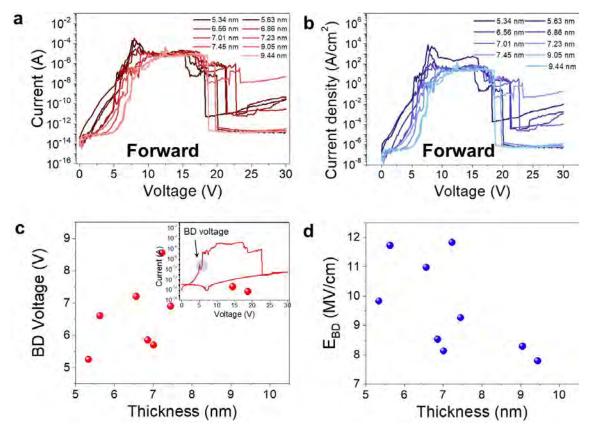

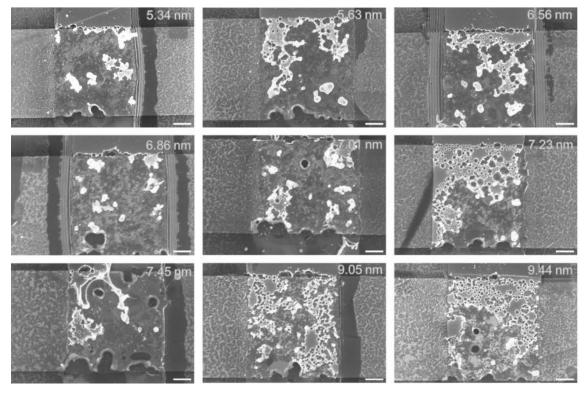

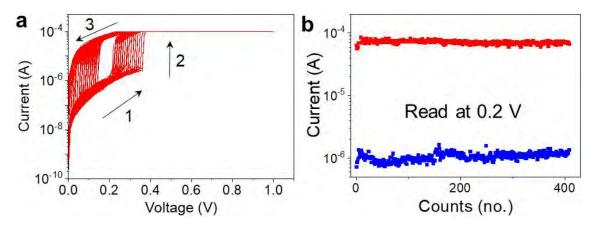

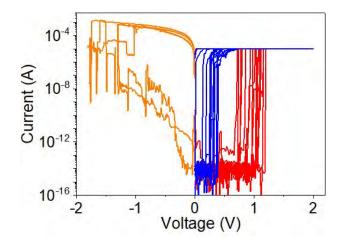

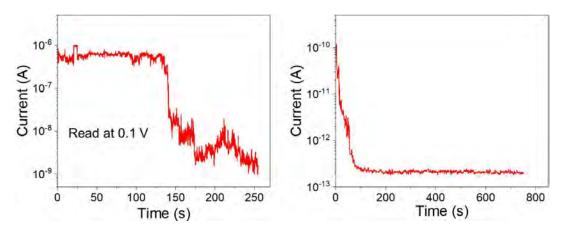

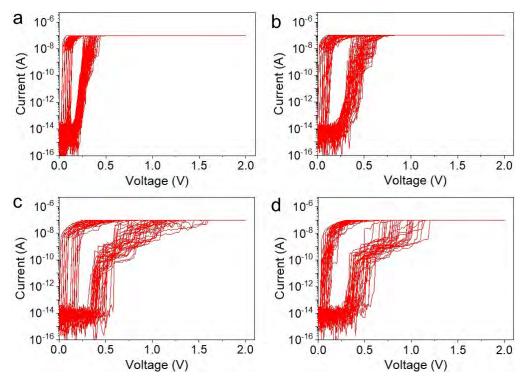

| 3.3.1. Electrical characterization of Pt/ME h-BN/Pt devices 42               | 1 - |

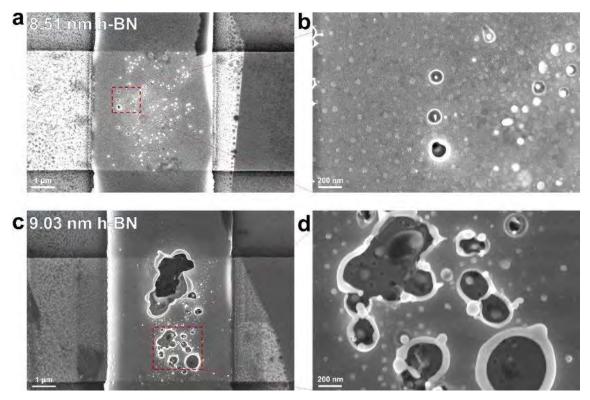

| 3.3.2. Electrical characterization of Au/ME h-BN/Au devices 51 -            |

|-----------------------------------------------------------------------------|

| <b>3.3.3. Transfer Au/ME h-BN/Au devices</b> 61 -                           |

| 3.3.4. Electric characterization of Au/Ti/ME h-BN/Au devices 66 -           |

| <b>3.4.</b> Conclusion 71 -                                                 |

| Chapter 4: Dielectric breakdown of CVD h-BN in nano-scale devices 73 -      |

| <b>4.1. Introduction</b> 73 -                                               |

| <b>4.2. Experiments</b> 75 -                                                |

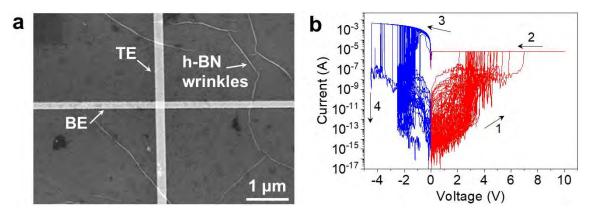

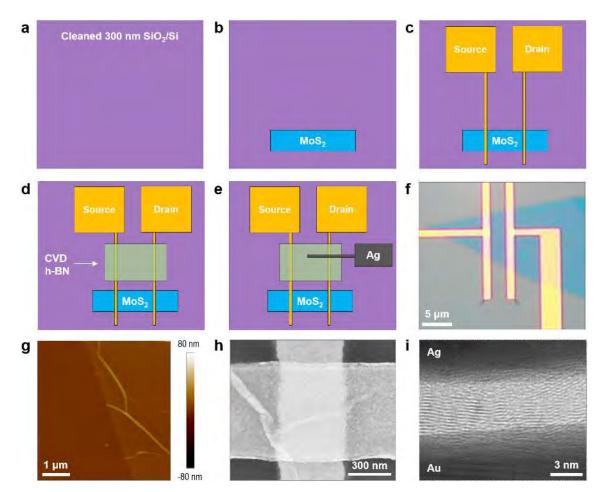

| 4.2.1. Fabrication of nano-scale devices based on CVD-grown h-BN 75 -       |

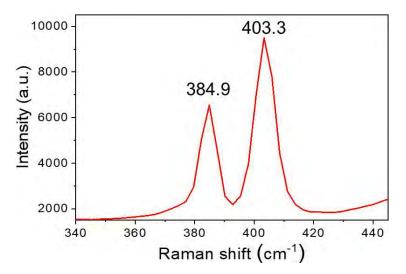

| 4.2.2. Characterization of CVD-grown h-BN after wet transfer 75 -           |

| 4.3. Results and discussion 76 -                                            |

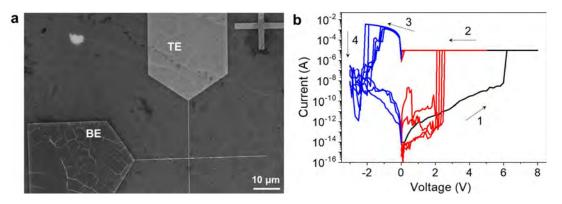

| <b>4.3.1.</b> Topography characterization of Au/Ag/monolayer h-BN/Au 76 -   |

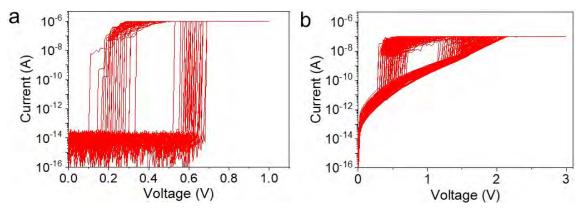

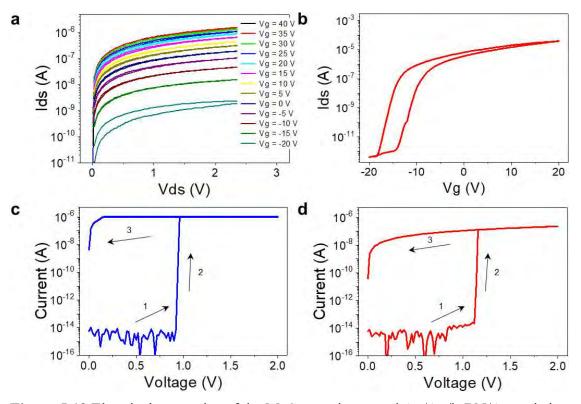

| 4.3.2. Electrical characterization of Au/Ag/monolayer h-BN/Au 77 -          |

| 4.3.3. Electrical characterization of Au/Ti/monolayer h-BN/Au 78 -          |

| 4.3.4. Au/Ag/multilayer h-BN/Au devices characterization 80 -               |

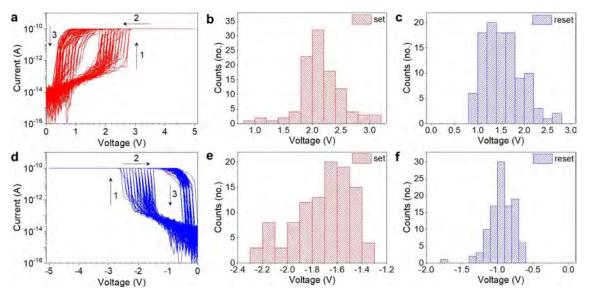

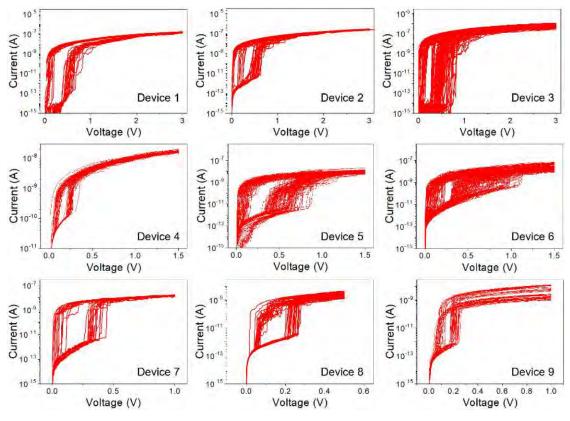

| 4.3.5. Crossbar array of Au/Ag/multilayer h-BN/Au devices 85 -              |

| 4.3.6. Au/Ti/multilayer h-BN/Au devices 88 -                                |

| 4.3.7. Au/multilayer h-BN/Au devices 89 -                                   |

| <b>4.4. Conclusion</b> 90 -                                                 |

| Chapter 5: Limited breakdown in one-transistor-one-memristor cell 91 -      |

| <b>5.1. Introduction</b> 91 -                                               |

| 5.2. Transistor and memristor candidate for 1T1M cell 92 -                  |

| 5.2.1. Fabrication of MoS <sub>2</sub> transistor92 -                       |

| 5.2.2. Materials and devices characterization                               |

| 5.2.3. Characterization of the transistor with transferred source/drain-96- |

| 5.2.4. Transistors fabricated using EBL method                              |

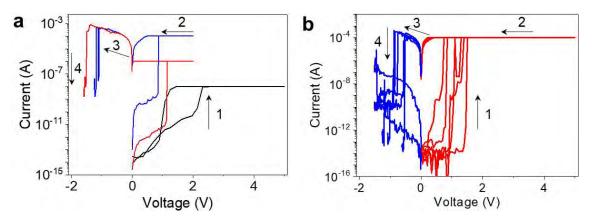

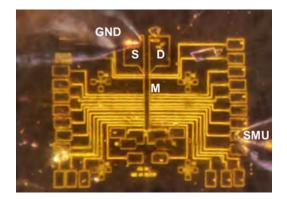

| 5.3. 1T1M cell 102 -                                                        |

| 5.3.1. Characterization of 1T1M cell 102 -                                  |

| 5.4. Conclusion 110 -                                                       |

| Chapter 6: Conclusion and perspectives 111 -                                |

| References 113 -                                                            |

| Appendix A: Scientific curriculum vitae 142 -                               |

| Appendix B: Summary in official language 145 -                              |

| Appendix C: List of acronyms 148 -                                          |

### Abstract

Electronic devices are becoming increasingly essential for our work and life. The downscaling process of electronic devices, as well as the development of new devices for artificial intelligence and internet of things, are boosting the demand of advanced electronic devices. In this context, dielectric materials are essential building blocks of many electronic devices, as they enable key functionalities like capacitance and memristive effect.

Currently, the dielectric materials most employed by the semiconductor industry (such as high-k materials) face performance and reliability challenges that endanger the correct development of future memory and computing devices. For this reason, a new generation of dielectric materials is desired to overcome the current demands. Two-dimensional (2D) materials are considered promising candidates for next-generation electronic devices. In particular, hexagonal boron nitride (h-BN) is a 2D layered material with one of the largest band gaps (5.9 eV), which enables its use as gate insulator of a transistor or a resistive switching layer in memristors.

In this work, we study the dielectric performance of multilayer mechanically exfoliated h-BN stacks in several types of devices. First, we explore the performance of defect-free mechanically exfoliated multilayer h-BN as gate dielectric material. Second, we explore the performance of defect-rich multilayer h-BN stacks, produced via chemical vapor deposition (CVD), as resistive switching layer in memristors with vertical metal-insulator-metal (MIM) structure. And third, we have explored the performance of one-transistor-one-memristor (1T1M) cells – the building block of memristive circuits for information storage and computation – fabricated by connecting a molybdenum disulfide (MoS<sub>2</sub>) transistor to a h-BN memristor.

In this doctoral thesis, we present valuable data to understand the properties of h-BN, as well as its potential for applications in the field of micro/nano-electronics. The data contained in this document may be of great help of other researchers and engineers devoted to the development of post-silicon electronics, and they should contribute to a faster development of such technologies for the benefit of mankind.

## Abstract in the official language

Els dispositius electrònics són cada cop més essencials per a la nostra feina i la nostra vida. El procés de miniaturització dels dispositius electrònics, així com el desenvolupament de nous dispositius per a la intel·ligència artificial i l'internet de les coses, estan augmentant la demanda de dispositius electrònics avançats. En aquest context, els materials dielèctrics són components essencials de molts dispositius electrònics, ja que permeten funcionalitats clau com la capacitat i l'efecte memristiu.

Actualment, els materials dielèctrics més utilitzats per la indústria dels semiconductors (com els materials d'alta permitivitat) s'enfronten a reptes de rendiment i fiabilitat que posen en perill el desenvolupament correcte de futurs dispositius de memòria i informàtica. Per aquest motiu, es necessita una nova generació de materials dielèctrics per superar les exigències actuals. Els materials bidimensionals (2D) es consideren candidats prometedors per a dispositius electrònics de nova generació. En particular, el nitrur de bor hexagonal (h-BN) és un material en capes 2D amb una de les bandes prohibides més grans (5,9 eV), que permet el seu ús com a aïllant de porta d'un transistor o una capa de aïllant resistiva en memristors.

En aquest treball, estudio el rendiment dielèctric de multicapes de h-BN exfoliades mecànicament en diversos tipus de dispositius. En primer lloc, explorem el rendiment del h-BN multicapa exfoliat mecànicament sense defectes com a material dielèctric de la porta. En segon lloc, explorem el rendiment de les piles h-BN multicapa riques en defectes, produïdes mitjançant deposició química de vapor (CVD), com a capa de commutació resistent en memristors amb estructura vertical metall-aïllant-metall (MIM). I en tercer lloc, hem explorat el rendiment de les cèl·lules d'un transistor-un-memristor (1T1M), el bloc més empleat per a la construcció dels circuits memristius per a l'emmagatzematge i la computació d'informació de dades, fabricades connectant un transistor molibden disulfur (MoS<sub>2</sub>) a un memristor h-BN. En aquesta tesi doctoral presentem dades valuoses per entendre les propietats de l'h-BN, així com el seu potencial d'aplicacions en el camp de la micro/nanoelectrònica.

Les dades contingudes en aquest document poden ser de gran ajuda per a altres investigadors i enginyers dedicats al desenvolupament de l'electrònica post-silici, i haurien de contribuir a un desenvolupament més ràpid d'aquestes tecnologies en benefici de la humanitat.

### **Chapter 1: General introduction**

#### **1.1. Introduction**

#### 1.1.1. Introduction of dielectric materials

Materials are categorized into conductors, semiconductors, and insulators based on their electrical conductivity characteristics. A dielectric material is a specific type of insulator that, while non-conductive, becomes polarized when exposed to an external electric field [1]. The attributes of dielectric materials encompass electric susceptibility, dielectric polarization, electric dipole moment, electronic polarization, relaxation time, dielectric dispersion, and dielectric breakdown [1]. When selecting an appropriate dielectric, several parameters should be taken into account, such as a favorable dielectric constant, high dielectric strength, a low loss factor, stability at elevated temperatures, long-term storage stability, responsive frequency characteristics, and compatibility with industrial manufacturing processes [2].

Dielectric materials can be broadly classified into three categories based on their physical states: solid, liquid, and gaseous dielectrics. Regardless of their form, each type of dielectric material possesses distinct applications and properties. For instance, glass, a solid dielectric, was utilized in the creation of the Leyden jar, which is considered the first capacitor [3]. This pioneering development spurred further exploration and discovery of new dielectric materials and their potential uses. Solid dielectric materials, such as mica [4,5], various polymers [6,7], and oxides including perovskite oxides, silicon dioxide (SiO<sub>2</sub>), aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), and hafnium dioxide (HfO<sub>2</sub>), are integral components in the construction of transistors, capacitors, and dielectric layers within a wide array of electronic devices [8-11]. Liquid dielectric materials, including mineral oils and deionized water, are valued for their insulating capabilities and are commonly employed in high-voltage electrical equipment [12-14]. Dry air, a fundamental gaseous dielectric, serves as a dielectric medium in capacitors [15]. The versatility of dielectric materials in their solid, liquid, and gaseous forms underscores their indispensable role across various technological applications, highlighting the significance of ongoing research and innovation in this field.

Among the dielectric properties, dielectric constant and dielectric strength are the most used parameters to evaluate the materials' dielectric property. Dielectric constant reflects the ability of materials to store charges and also can express the ability to hold electric flux in it. The dielectric constant formula is:

$$\mathbf{K} = \varepsilon/\varepsilon_0$$

K is the dielectric constant;  $\varepsilon$  is the permittivity of substance;  $\varepsilon_0$  is the permittivity of free space [16].

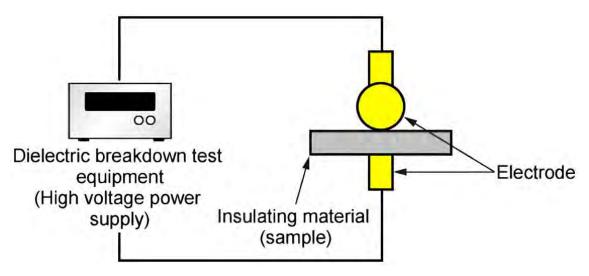

Figure 1.1 Dielectric strength measurement illustration [17].

Dielectric strength refers to the maximum voltage that a dielectric material can withstand before experiencing dielectric breakdown. The assessment of this property is conducted through a specific testing procedure where the dielectric material is positioned between two electrodes in an ambient air environment, as depicted in Figure 1.1. The process involves the incremental application of voltage across the electrodes. The voltage applied gradual increase continues until a point is reached where there is a sudden and significant surge in current flow. The precise voltage level at which this dramatic current increase occurs is designated as the breakdown voltage. This critical threshold is a crucial metric in evaluating the performance and reliability of dielectric materials in electrical insulation applications. The dielectric strength is calculated via the following equation:

$$D = E/d$$

D is the dielectric strength; E is the breakdown voltage; d is the thickness of dielectric materials [17].

Dielectric materials, renowned for their distinctive electrical properties, are extensively utilized across a multitude of industries. They are frequently employed in electronic devices, notably as components of capacitors [18-20], and in the construction of radio frequency transmission lines [21]. Mineral oils, a type of dielectric material, serve dual purposes as insulators and cooling agents within transformers [22] and data centers [23]. Additionally, dielectric materials find applications in resonators [24], tunable microwave devices [25, 26], and liquid crystal displays [27], showcasing their versatility and significance in modern technology.

#### 1.1.2. Application of dielectric materials in electronic devices

Dielectric materials play a crucial role in the construction and functionality of a variety of electronic devices. Polymers [28-30], inorganic substances [31-33], hybrid composites [34,35], and a range of other dielectric materials are harnessed to fabricate these technological components. Among their many applications, dielectrics are particularly crucial in capacitors, and transistors. These uses underscore the indispensable nature of dielectric materials in the realm of electronics, highlighting their contribution to the performance and reliability of modern electronic devices.

A dielectric capacitor consists of two conductive metal electrodes that are insulated from each other by a dielectric layer. Charging occurs when an external voltage induces polarization within the dielectric layer, causing dipoles to align with the electric field and leading to charge accumulation on the electrode surfaces. The energy storage capacity of these capacitors is determined by the polarization and capacitance of the dielectric material, as well as the magnitude of the applied electric field, with these factors collectively impacting the capacitor's performance and energy-storing efficiency [36].

Dielectric capacitors are renowned for their exceptional high-power density, which can reach up to the megawatt range, and their swift response times, typically less than 100 microseconds. This performance is attributed to their unique method of energy storage, which involves the creation and utilization of electrostatic fields through the processes of dielectric polarization and depolarization [37-42]. In addition to their impressive power capabilities, dielectric capacitors also offer several other distinct advantages. These include a straightforward design, the ability to operate at high voltages exceeding thousands of volts, a broad operating temperature range, an allsolid-state construction, enhanced safety features, and an extended cycle life. These attributes have positioned dielectric capacitors as a versatile solution across a variety of sectors and applications. Notably, they are increasingly being utilized in smart power transmission systems, pulsed electronics, emerging energy technologies, hybrid electric vehicles, and advanced military equipment, meeting a diverse array of requirements in these fields [43-52].

The transistor exemplifies a prevalent application for dielectric materials, particularly in the form of a gate dielectric.  $SiO_2$  has been a foundational dielectric in silicon-based electronic devices from the early stages [53], favored for its exceptional attributes such as seamless integration with silicon, straightforward manufacturing processes, and affordability [54]. Nonetheless, the relatively low dielectric constant of  $SiO_2$  poses limitations in its use within transistors. For instance, at the 90 nm node of transistor technology, a  $SiO_2$  layer as thin as 1.2 nm is employed as the dielectric [55]. The trend toward device miniaturization necessitates even thinner dielectric layers, which, in turn, can lead to an increase in leakage current [55].

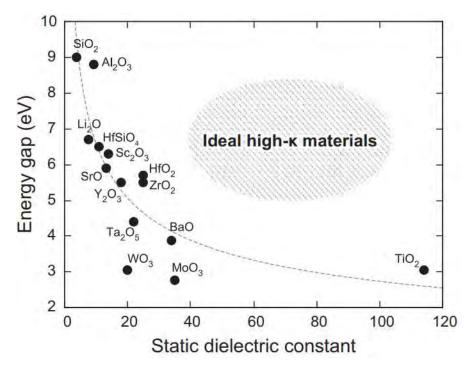

To address this challenge without compromising the miniaturization of transistors, the industry has turned to novel dielectric materials with a dielectric constant exceeding that of SiO<sub>2</sub> (k  $\approx$  3.9). These advanced materials, known as high-k materials, encompass a variety of compositions such as metal oxides [56,57], nitrides [58], perovskites [59], and organic dielectrics [60]. Figure 1.2 illustrates the ideal characteristics for high-k materials, with a selection of prominent oxides charted according to their dielectric constant and energy bandgap, offering a visual representation of their properties for comparison and selection in transistor design.

Among the array of high-k materials,  $HfO_2$  emerged as the choice for the first generation of complementary metal oxide semiconductor (CMOS) technology [62], favored for its elevated dielectric constant (k  $\approx$  19) and its capacity to mitigate leakage current [63]. Despite these advantages, the transition from SiO<sub>2</sub> to high-k materials still has some challenges [64,65]. Key issues include: i) An increase in material defects during the metal oxide deposition process, which can compromise the stability of device performance; ii) The potential for reaction with the silicon substrate, leading to the formation of an additional SiO<sub>2</sub> layer; iii) A reduction in carrier mobility due to phonon scattering in the channel region; iv) The risk of poly crystallization, which can degrade homogeneity and increase variability.

As CMOS technology continues to evolve, there is a growing demand for dielectric materials that can surpass the performance limitations of even high-k materials, offering enhanced stability, reduced defects, and improved compatibility with existing semiconductor processes.

Figure 1.2 Experimental dielectric constant and bandgap for well-known oxides [61].

Dielectric materials play an important role in the construction of capacitors within memory devices, particularly in dynamic random-access memory (DRAM) [66]. In emerging memory devices, dielectric materials can also be used as a switching medium layer in two-terminal memory devices called memristors [67,68]. For example, the typical high-k materials, HfO<sub>2</sub>, can work as a switching layer in memory devices [69-71] with impressive performance.

#### 1.1.3. 2D materials for next-generation electronic devices

The development of the semiconductor industry and increasing demand for highperformance hardware for emerging data-based industries (such as deep learning, the Internet of Things (IoT), and in-memory computing [72,73]), requires Si-based CMOS technology enhanced performance, which are often related to device miniaturization. This generates challenges like short channel effects, leakage current increasing, highpower consumption, and high contact resistance [74,75]. When the thickness of the semiconductor decreases to 5 nm due to the surface dangling bonds and high roughness, the scattering of internal charges increases, leading to a sharp decrease in mobility ( $\mu$ ) [76,77]. In memory devices, defects will be uncontrolled when the metal oxide dielectrics thickness is reduced to 3 nm [78]. Novel materials and devices are required when the Si-based integrated circuit (IC) industry reaches its physical limitation [79].

After the discovery of graphene in 2004 [80], a new kind of material called 2D) materials attract interest for their application in the electronic region due to their unique structure, physical and electric properties. For example, 2D materials are layered structures connected via the weak van der Waals force, indicating that 2D materials can approach single atomic thin sheets in the application of vertical and planner electronic devices [81]. This characteristic aligns perfectly with the demand for the progressive miniaturization of next-generation electronic devices, particularly in terms of their thickness dimensions [82]. Other unique properties such as dangling free of the atomically flat surface, easy stacking on other materials, high transparency [83], and excellent electric performance [84-87] make 2D materials a promising candidate for the application of next-generation electronic devices.

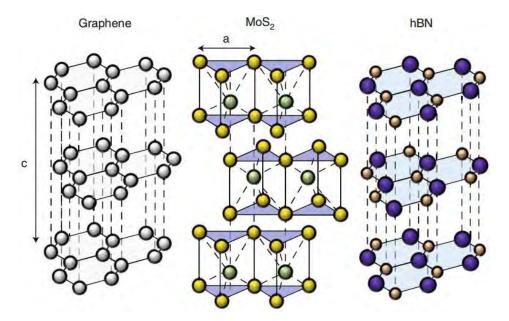

Figure 1.3 Example of metallic, semiconducting, and insulating 2D materials from left to right [88].

2D materials exhibit a spectrum of conductive properties, which can be neatly divided into three categories: conductors, semiconductors, and insulators. This classification is visually represented in Figure 1.3, progressing from left to right.

Graphene stands out as a quintessential example of a conductive 2D material, characterized by its lack of a bandgap [89]. This unique trait positions graphene as an ideal candidate for conductive electrodes, offering a compelling alternative to traditional metal electrodes [90]. The exploration of 2D materials extends to metallic transition metal dichalcogenides (TMDs), which display intriguing metallic properties. For instance, Zhao et al. employed the CVD technique to grow 2D niobium disulfide (NbS<sub>2</sub>) on a h-BN substrate, revealing that NbS<sub>2</sub> retains its metallic nature even when reduced to just three layers [91]. A comprehensive review delves into a broader range of 2D metallic TMDs and their metallic characteristics, shedding light on their potential applications and properties [92].

Semiconductor 2D materials include most TMDs materials, such as MoS<sub>2</sub> [93,94], tungsten disulfide (WS<sub>2</sub>) [95], and tungsten diselenide (WS<sub>2</sub>) [96], etc. TMDs materials present a unique combination of properties, including atomic-scale thickness, direct bandgap, and electronic features that make them attractive to the field of electronic devices [97]. The most widely studied application of semiconductor TMDs in the electronics region is their use in transistors as channel materials due to their suitable bandgap [98]. MoS<sub>2</sub> is the most studied TMD material due to its robustness and the availability of raw materials in nature [97]. For example, a MoS<sub>2</sub>-based transistor with a 1 nm wide gate electrode displays a sub-threshold swing (SS) of approximately 65 mV/decade and a large current on/off ratio of approximately  $10^6$  [99]. Tian et al. fabricated a side-wall transistor where the thickness of the monolayer MoS<sub>2</sub> serves as the channel length. These transistors, with an atomic scale channel length, exhibit a current on/off ratio of about  $1.02 \times 10^5$  and a subthreshold swing of around 117 mV/dec [100].

Ultimately, h-BN stands out as the most extensively studied insulating material within the realm of 2D materials. Recognized for its role as a stable dielectric, coupled with its atomically flat surface and lack of dangling bonds, h-BN is exceptionally well-suited for use as either a substrate or a protective layer in electronic devices that incorporate other 2D materials. The combination of its insulating nature and its ability to provide an atomically smooth surface ensures compatibility and enhances the performance when paired with other 2D materials.

For instance, employing h-BN as a substrate in graphene-based electronics significantly boosts electron mobility, increasing from 10,000 cm<sup>2</sup>/Vs when on SiO<sub>2</sub>substrates [101] to an impressive 60,000 cm<sup>2</sup>/Vs [102]. This enhancement, along

with the observed improvement in carrier inhomogeneities [103], underscores the material's potential to refine electronic properties. Further encapsulation of CVD-grown graphene between h-BN layers—a technique that sandwiches the graphene between two h-BN flakes—yields even more remarkable results, with electron mobility soaring to 350,000 cm<sup>2</sup>/Vs [104] and an astounding 500,000 cm<sup>2</sup>/Vs [105]. These advancements not only showcase the effectiveness of this optimization approach but also highlight the reliability of h-BN as an encapsulating material.

Similar improvements in device performance are mirrored in the case of encapsulated MoS<sub>2</sub> transistors. Here, the mobility of the transistors is observed to increase to 34,000 cm<sup>2</sup>/Vs at low temperatures [106], with a concurrent enhancement in performance stability [107]. These findings underscore the broad applicability of h-BN as a means to optimize and stabilize the performance of various 2D material-based electronic devices

h-BN can also work as a functional material, such as switching layer in memristors to enhance storage density [108], or construct oscillatory neural network to solve optimization problems [109].

In addition to h-BN, some novel insulating 2D materials, such as calcium fluoride (CaF<sub>2</sub>), strontium titanate (SrTiO<sub>3</sub>), and bismuth selenite (Bi<sub>2</sub>SeO<sub>5</sub>) are studied and display inspired dielectric performance. CaF<sub>2</sub> is used as gate dielectric in MoS<sub>2</sub> field effect transistor (FET) and the FET exhibits low leakage current, low subthreshold swing (90 mV/dec), high on/off ratio (10<sup>7</sup>), and small hysteresis [110]. SrTiO<sub>3</sub> as a well-known perovskite oxide material with good insulation and high dielectric constant is used as the gate dielectric in tin dioxide (SnO<sub>2</sub>) thin film transistors presenting low operation voltage [111]. Encapsulation with Bi<sub>2</sub>SeO<sub>5</sub> significantly improve the Hall mobility of bismuth oxyselenide (Bi<sub>2</sub>O<sub>2</sub>Se) nanosheets device from 43,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> to 470,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at 1.8 K [112].

All thin-film transistors utilizing 2D materials have been masterfully demonstrated by Das and colleagues. In their construction, they employed monolayer graphene for metal electrodes, 3-4 layered h-BN as the dielectric material, and bilayer WSe<sub>2</sub> as the channel material. This all-2D-based transistor showcases a remarkably high on/off ratio of 10<sup>7</sup> and an impressively low subthreshold swing of 90 mV/dec [113]. This all 2Dbased transistor demonstrates that 2D materials have vast potential in electronic devices.

Aside from the electric properties of 2D materials, the physical property such as high mechanical strength, flexible and transparent features make 2D materials promising in flexile and wearable electronic devices. For example, monolayer  $MoS_2$  is used to fabricate flexible transistors with low channel length (~60 nm) and exhibits high ~470  $\mu$ A/ $\mu$ m at low source/drain voltage (1 V) [114]. Wearable electronic devices based on 2D materials such as energy harvesting and biomedical sensors are discussed in [115] and [116], respectively.

2D materials can act as any role in the IC industry, including conductors, semiconductors and insulators and their impressive performance in traditional and novel electronic devices indicates that 2D materials are promising candidates to fabricate next-generation electronic devices.

#### 1.1.4. Introduction of h-BN

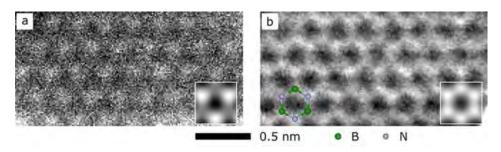

The h-BN structure is shown in Figure 1.3, and its experimental annular dark-field (ADF) phase images are presented in Figure 1.4 with high resolution. The ADF image exhibits the different intensities of boron (B) and nitrogen (N) atoms (bright points are N atoms, dark points are B atoms), and the phase image displays the hexagonal structure of the monolayer h-BN. In this structure, the hexagons consisting of boron and nitrogen atoms are clearly exhibited. This hexagonal structure is similar to that of graphene. The lattice mismatch between graphene and h-BN is low, at approximately 1.7% [118], indicating that h-BN can be an excellent substrate for graphene. Each layer of h-BN is composed of boron and nitrogen atoms, which are interconnected through robust covalent bonds. Despite this strong intralayer bonding, the interlayer forces in h-BN are comparatively weak, which allows for the existence of h-BN in the form of individual layers that are only atomically thin. The thickness of each layer of h-BN is around 0.33 nm, which is beneficial for minimizing the size of electronic devices in the vertical direction.

Figure 1.4 Experimental ADF and phase images of monolayer h-BN [117].

Among 2D materials, h-BN is recognized as an insulating material with an extensive bandgap of approximately 5.9 eV [119,120]. The dielectric constant of h-BN is around 3, which varies depending on the direction (in-plane or out-of-plane) and the number of layers [121]. In terms of dielectric breakdown strength, CVD-grown h-BN and exfoliated h-BN exhibit values of 1.5 MV/cm [122] and 12 MV/cm [123], respectively. Owing to h-BN's distinctive attributes, including its wide bandgap, atomically flat surfaces, and the absence of dangling bonds, h-BN layers are well-suited to serve as substrates in electronic devices and/or as encapsulating layers [124,125] for devices based on 2D materials.

Additional physical properties of 2D h-BN, such as its mechanical strength [126], high thermal conductivity [127], temperature stability [128], flexibility [129,130], and high transparency [131], further expand its potential applications in functional coatings, composite materials [132], and wearable electronic devices [133]. h-BN also finds use as a reinforcing agent [134] or as a gas barrier filler [135] in polymer composites. Its utility in electronic devices is further highlighted by its role as a dielectric material in capacitors [136], a gate dielectric in planar graphene-based photodetectors [137], an insulator in memristors [138-140], and as a medium layer in resistive switching devices [141]. With its unique features, 2D layered h-BN holds substantial promise for a variety of innovative applications.

#### 1.1.5. h-BN production

Due to its exceptional performance in electronic devices, the production of h-BN is a critical aspect of its practical application. Traditionally, the fabrication of 2D materials can be achieved through either a top-down or bottom-up approach. The process of extracting 2D materials from bulk precursors is referred to as the top-down method. This methodology encompasses techniques such as mechanical exfoliation (ME), liquid-phase exfoliation (LPE), and chemical etching, among others. In contrast, the bottom-up method involves the synthesis of 2D materials by assembling them from atomic or molecular building blocks into layered structures. Common bottom-up techniques include CVD, physical vapor deposition (PVD), and molecular beam epitaxy (MBE).

Initially, we will discuss the top-down approach, detailing various strategies for procuring h-BN materials. This involves the exfoliation of h-BN flakes or nanosheets

from bulk boron nitride materials, leveraging methods that allow for the transition from a three-dimensional bulk material to a two-dimensional material with desirable electronic properties.

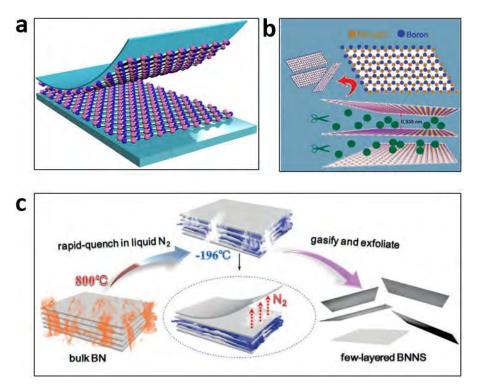

The first top-down method we will introduce is mechanical exfoliation, which is the method that found graphene and initiated 2D materials research. As Figure 1.5a shows, the material is peeled off through the tape, and ultimately, a few or single layers of h-BN will be obtained on the tape [142]. The drawback is that there is no standard way to achieve accurate thickness with low yields, time-consuming processes, and small-area h-BN (several nanometer thicknesses and hundreds of micrometers in size) [143]. However, the h-BN exfoliated has the best quality with fewer native defects [144] than that of h-BN obtained from other methods. The mechanically exfoliated h-BN flakes can be transferred to a precise location via a dry transfer.

Figure 1.5 Exfoliation of h-BN from bulk to layers (a) Mechanical exfoliation with tape [142]. (b) Liquid-phase exfoliation using sonication and centrifugation in IPA (green spheres) [146]. (c) Gas exfoliation method [148].

Liquid-phase exfoliation is another extensively utilized technique for the production of 2D nanosheets. This method offers greater efficiency compared to mechanical exfoliation [145], and the process is depicted in Figure 1.5b. Bulk h-BN

crystals are transformed into 2D nanosheets through a combination of sonication and centrifugation within isopropanol (IPA) [146]. Zhu et al. have illustrated that h-BN layers exfoliated through liquid-phase processes exhibit high capacitance and minimal current leakage. These characteristics enable the achievement of an impressive mobility of 7,100 cm<sup>2</sup>/Vs in graphene transistors that employ h-BN as a gate insulator [147]. Furthermore, Zhu et al. have also employed a gas exfoliation method to produce thin h-BN flakes, as showcased in Figure 1.5c. This approach primarily yields 1-5 layered nanosheets with lateral dimensions ranging from 50 to 500 nm [148].

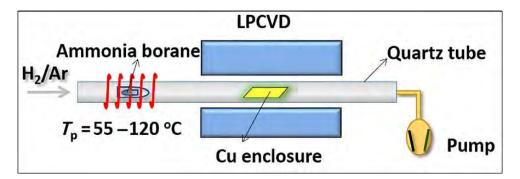

Following a bottom-up approach, we can also synthesize h-BN films via CVD. Copper (Cu) foil [149-153] is the mostly used substrate in CVD-grown of h-BN because of its catalyst, feasible surfaces, low cost and available for mass production, although other metal substrates are also being investigated, such as nickel (Ni) [154-156], platinum (Pt) [157,158], and iron (Fe) [159]. The CVD process is illustrated in Figure 1.6. Ammonia borane (NH<sub>3</sub>BH<sub>3</sub>) is used as the precursor and decomposes by heating it at 55-120 °C. Then, the decomposed precursor flows into the chamber with a mixed hydrogen/argon (H<sub>2</sub>/Ar) gas and reacts on the Cu foil, previously heated at 1000 °C, to form a h-BN layer [160]. However, the metal-assisted CVD growth can potentially limit the thickness of h-BN due to the catalytic metal being isolated from the first or few layers of h-BN [161]. Some publications describe the synthesis of h-BN directly on a dielectric substrate, like amorphous quartz [162], sapphire [163], and silicon carbide (SiC) [164], without the assist of metal. Other growth methods, such as metal-organic chemical vapor deposition (MOCVD) [165,166] and MBE [167-169] are also under study, but their high costs make them currently less effective for practical applications. More efforts are needed to explore the synthesis of h-BN via the CVD method to achieve large scale production with uniform and controllable quality.

Figure 1.6 CVD synthesis of h-BN on Cu foil [160].

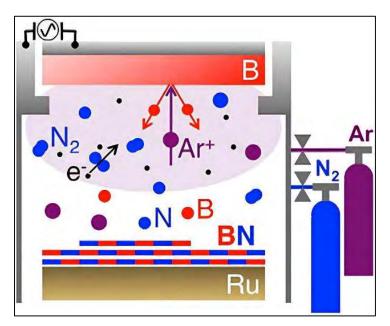

PVD is an additional method employed for the growth of h-BN. Techniques such as magnetron sputtering [170] and ion beam sputtering [171,172] are typical PVD approaches to fabricate h-BN films. The operational principle of the sputtering process is illustrated in Figure 1.7. Initially, a high-vacuum environment is essential to prevent contamination during the deposition process. Ar is introduced into the chamber as the sputtering gas and is ionized by an electric field to generate plasma. N<sub>2</sub> is also introduced into the chamber as a reactive gas, facilitating the formation of the h-BN film. The argon ions are accelerated towards a negatively biased boron target. These energetic argon ions impact the boron target, transferring momentum through collisions and dislodging atoms from the surface. Prior to reaching the substrate, the sputtered boron atoms react with nitrogen, yielding a boron nitride film on the substrate's surface. This process, which includes the reaction between boron and nitrogen, is known as reactive magnetron sputtering.

Figure 1.7 PVD method to fabricate h-BN films [170].

#### 1.1.6. h-BN application in electronic devices

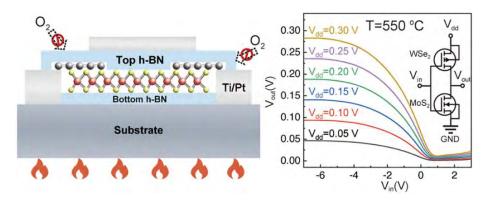

The dielectric property of h-BN is studied via a conductive atomic force microscope (CAFM) and at the device level, demonstrating its reliability as a dielectric material without issues such as charge trapping and de-trapping, stress-induced leakage current, and premature dielectric breakdown [173]. h-BN can be used as a gate dielectric in transistors. As shown in Figure 1.8, Zou et al. used h-BN as both the gate

dielectric and encapsulation layer in MoS<sub>2</sub> transistors, and the devices can survive at a much higher temperature (550°C) than ever reported [174]. In a h-BN/graphene/h-BN heterostructure field-effect transistor, the h-BN also serves as an encapsulation layer and gate dielectric, with the charge carrier mobility in the range of 30,000 to 36,000 cm<sup>2</sup>/Vs at room temperature [175]. Since the carrier mobility is enhanced when a 2D semiconductor is placed on an h-BN layer, Liao et al. designed a hybrid top gate dielectric, an h-BN/HfO<sub>2</sub> stack, for a MoS<sub>2</sub> transistor [176]. The fabricated devices with this hybrid dielectric exhibit enhanced mobility and superior gate control. The carrier scattering induced by the underlying substrate is also suppressed by the h-BN/HfO<sub>2</sub> dielectric.

Figure 1.8 h-BN as gate dielectric and encapsulation layer in MoS<sub>2</sub> transistor [174].

In addition, h-BN can also be used in some emerging electric applications, such as resistive switching (RS) devices [177], random telegraph noise (RTN) devices [178-181], heterostructure devices [182-185], and so on.

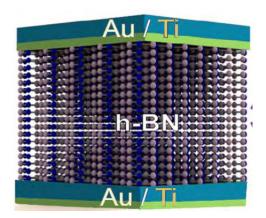

Figure 1.9 Schematic of typical resistive switching devices based on multilayer h-BN. Materials from top to bottom are Au/Ti/h-BN/Ti/Au [186].

RS devices typically exhibit a MIM structure, wherein insulating materials serve as the switching layer sandwiched between two conductive electrodes (as depicted in Figure 1.9 [186]). These devices have garnered significant interest due to their potential application as memristors [187]. Within RS devices, the resistance can be modulated reversibly between a high resistance state (HRS) and a low resistance state (LRS), contingent upon the application of an appropriate bias [188]. The HRS and LRS are analogous to digital 0 and 1, respectively, suggesting that RS devices are well-suited for information storage [189] and for utilization in in-memory computing devices [190].

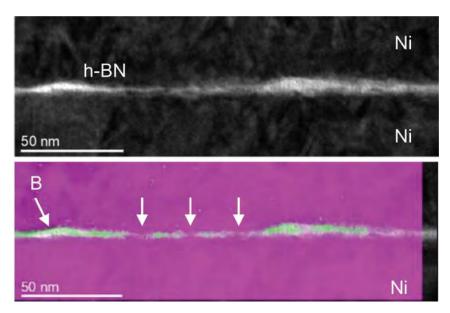

**Figure 1.10** TEM image of a Ni/h-BN/Ni memristor in a permanent LRS state. The top display the Ni/h-BN/Ni structure. The bottom is the EFTEM image of the top TEM image. Purple and green represent Ni and B element, respectively. The arrows indicate the contacted top and bottom Ni by diffusion [194].

Filament formation and rupture are posited as reliable mechanisms underlying resistive switching in metal oxide-based RS devices [191,192], as well as in h-BN-based RS devices [193,194]. Pan et al. discovered the concurrent presence of bipolar and threshold RS behaviors in metal/h-BN/metal structures. This coexistence is attributed to the formation of conductive filaments at grain boundaries and the facilitation of RS by metal ions migrating through the h-BN [193]. Figure 1.10 displays a transmission electron microscope (TEM) image extracted from a Ni/h-BN/Ni memristor in the LRS state. The underlying energy-filtered transmission electron microscopy (EFTEM) image illustrates the diffusion of Ni. The researchers hypothesize

that both Ni ion diffusion and conductive filament formation occur predominantly at grain boundaries [194], aligning with the findings reported in [193]. Moreover, defects within h-BN are identified as playing a pivotal role in h-BN-based RS mechanisms [144,194]. Given the significance of the conductive filament mechanism in RS devices, h-BN, particularly when grown using the CVD method, emerges as an apt choice for the resistive layer. The presence of defects and grain boundaries in the h-BN layer facilitates the formation of conductive filaments, thereby enhancing the device's RS performance [195].

h-BN serves as a versatile material for the construction of both volatile and nonvolatile memory devices in RS technology. For instance, Akinwande et al. have successfully demonstrated bipolar and unipolar non-volatile RS characteristics in a monolayer h-BN-based memristor. This device exhibits an exceptionally high on/off ratio of 10<sup>7</sup>, rapid switching times of 15 ns, and eliminates the need for a forming process [196]. Furthermore, Shi et al. have crafted an electronic synapse utilizing a metal/h-BN/metal cell, which intriguingly displays both volatile and non-volatile RS behaviors. The power consumption of this synapse is remarkably low, with values as low as 0.1 fW in standby mode and 600 pW per transition in the volatile regime [197].

**Figure 1.11** High-angle annular dark-field (HAADF) cross-sectional scanning transmission electron microscope (STEM) image of a 1T1M cell in the crossbar array. The inset shows the Au/Ti/h-BN/W memristor on the via [198].

Moreover, devices based on h-BN can be integrated with commercial electronic components to realize enhanced performance. Zhu et al. discovered that integrating an h-BN-based memristor with a conventional CMOS transistor to form a 1T1M cell can yield exceptional endurance, surpassing 2.5 million cycles. Figure 1.11 presents a TEM image of the 1T1M cell, with the Au/Ti/h-BN/W memristor distinctly visible at the top-left corner [198]. Collectively, these studies underscore the viability of h-BN as a 2D material for electronic device applications and suggest its potential for future expanded utilization.

#### 1.2. Main contribution of the thesis

#### 1.2.1. Objectives of the Thesis

The main goal of this thesis is to study the metal-insulator-metal structure electronic devices based on dielectric multilayer h-BN and explore their electric performance. The task can be divided into the following sections:

1) The dielectric performance of mechanical exfoliated multilayer h-BN has been investigated. The leakage current and dielectric breakdown field is explored. These types of devices contain very few atomic defects and they are very useful to understand the limit of the material in terms of electronic performance, despite their usability in real applications is poor due to the non-scalable fabrication process.

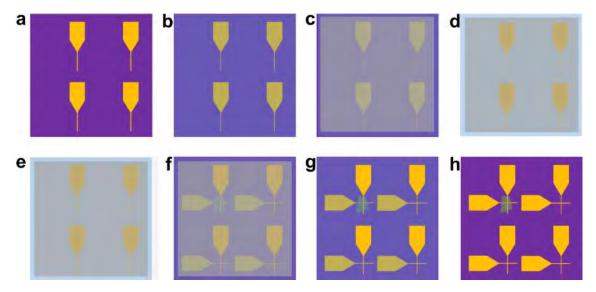

2) Nano-scale memristors based on h-BN are fabricated using only industrycompatible methods. The goal is to understand their potential for real memory and inmemory computing applications. The h-BN is synthesized via CVD. The device size is quite competitive in some cases, it approaches to 120 nm  $\times$  250 nm, as they are fabricated using electron beam lithography (EBL). The role played by the type of top electrode (Ag, Ti and Au) is also investigated.

3) We further improve the endurance of the CVD-grown nanomemristor by connecting a transistor in series (leading to 1T1M cells). This is done to avoid current overshoots during memristors set process. The type of transistor used is also made of a 2D material, which is semiconducting MoS<sub>2</sub>. This allows us to observe an enhanced performance at the nanoscale memristors.

#### 1.2.2. Key findings

In this work, we focused on studying one insulating 2D dielectric material named h-BN, and its application in micro- and nano-scale electronic devices with MIM structure. We obtained the following results.

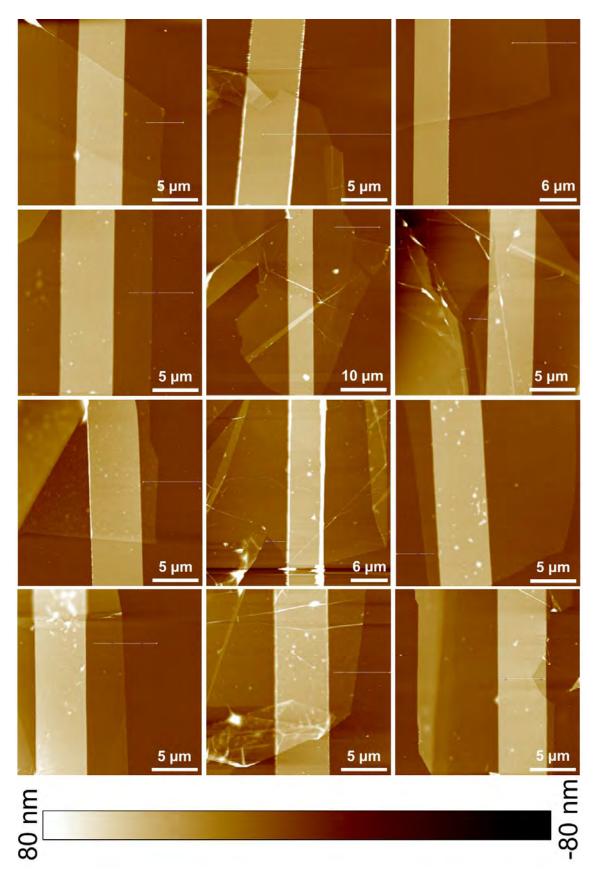

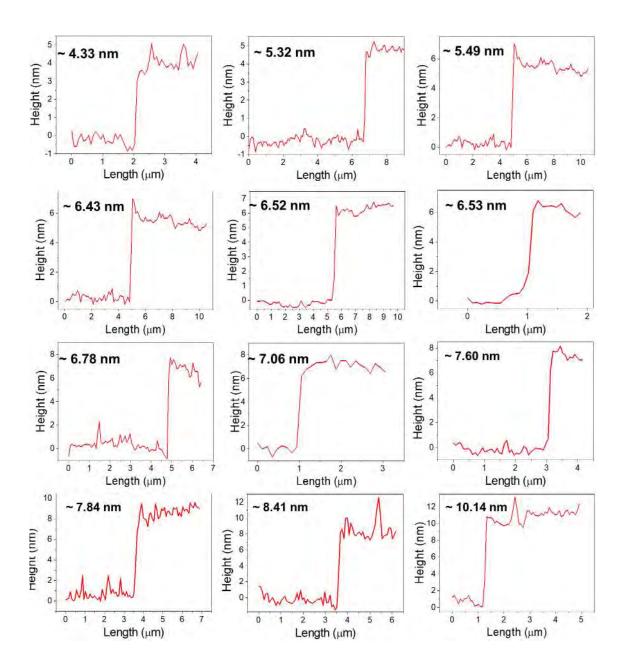

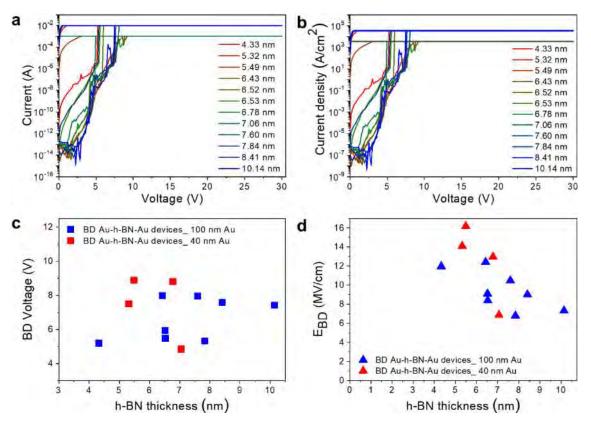

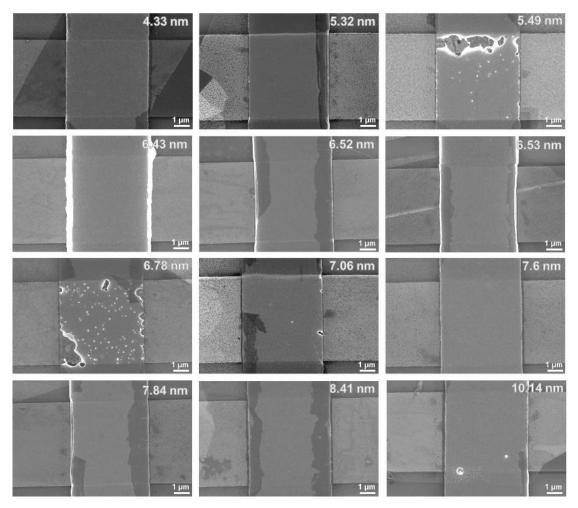

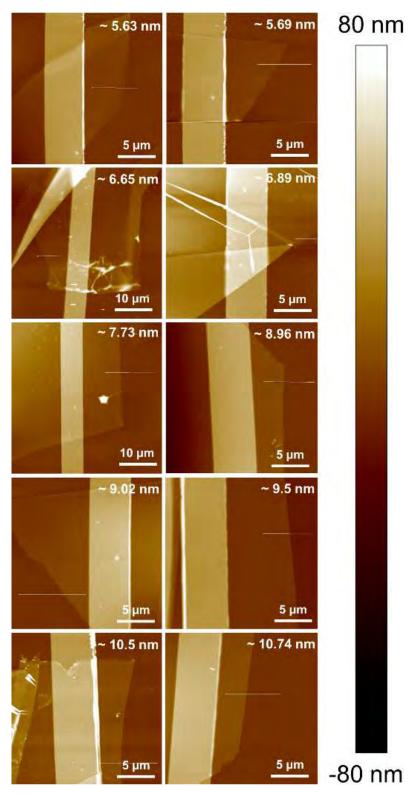

First, we present the micro-scale electronic devices based on mechanically exfoliated h-BN layers. The mechanically exfoliated h-BN flakes with MIM structure have been fabricated to study the dielectric breakdown behavior of h-BN. In addition, each h-BN flake is characterized by optical techniques and atomic force microscope (AFM) to ensure their quality. Pt/h-BN/Pt devices show a uniform hard breakdown phenomenon at a ramp voltage stress from 0 to 30 V with a current limitation of 10<sup>-2</sup> A, resulting a dielectric breakdown strength around 12 MV/cm. Au/h-BN/Au devices show nonlinear relationship between the breakdown voltage and h-BN thickness, leading to a median value of the dielectric breakdown strength of 10 MV/cm. Ti/h-BN/Au devices melt during the breakdown process and the median value of the dielectric breakdown strength is 9 MV/cm. The electrode diffusion ability affects the dielectric breakdown strength measured in h-BN. The excellent insulating properties of mechanically exfoliated h-BN are demonstrated, and the dielectric breakdown strength obtained from Pt/h-BN/Pt devices corresponds to previous work demonstrating a stable insulate quality of h-BN flakes.

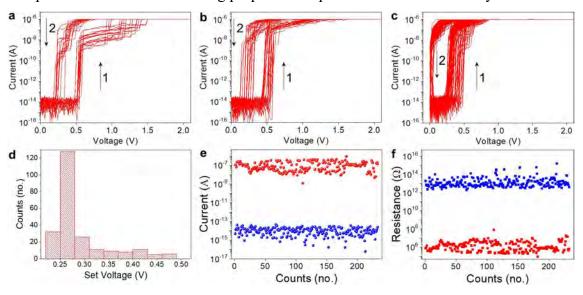

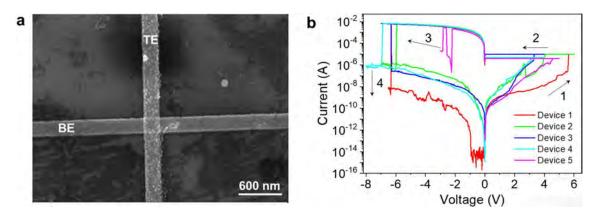

Then, we fabricated memristors based on monolayer and multilayer h-BN grown by the CVD method, which has the potential for large-scale devices fabrication. The nanoscale size of these memristors can be down to 120 nm  $\times$  250 nm, which is the limitation of the resolution of the EBL in the lab. These memristors present non-volatile or volatile resistive switching behavior depending on the top metal electrodes utilized. Memristors with Ag electrodes present stable threshold resistive switching, and Ti and Au based memristors present non-volatile resistive switching. CVD growth h-BN is more suitable for memristors because the existence of native defects (mainly lattice distortions in the h-BN crystalline structure) can reduce the energy to form conductive filaments, allowing them to be later partially disrupted to produce the resistive switching effect.

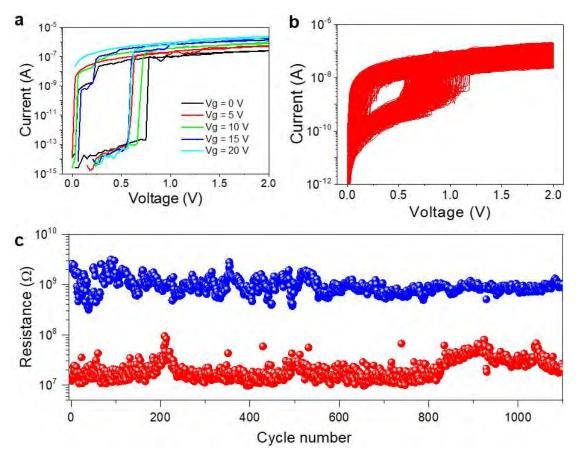

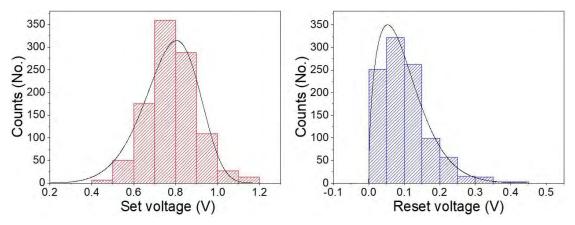

We also do some work to modify the threshold resistive switching in Au/Ag/h-BN/Au memristors with a back-gate transistor based on mechanical exfoliated MoS<sub>2</sub>. The on-state current of the MoS<sub>2</sub> transistor is around  $10^{-7}$  A, which is an appropriate current limitation for the Au/Ag/h-BN/Au memristors. More than 1000 cycles are achieved in the 1T1M cell, in which the memristor size is  $500 \text{ nm} \times 600 \text{ nm}$ .

#### 1.2.3. Thesis Outline

This thesis consists of five parts: <u>Chapter 1</u> presents the dissertation outline and introduction of the thesis. <u>Chapter 2</u> presents the device fabrication method used in the thesis. <u>Chapter 3</u> investigates the dielectric performance of mechanically exfoliated h-BN flakes with different metal electrodes. <u>Chapter 4</u> studies the resistive switching behavior in the nano-scale memristors made of chemical vapor deposition grown h-BN. In <u>Chapter 5</u>, we investigate the one-transistor-one-memristor cells based on  $MoS_2$  transistors and nano-scale h-BN memristors and characterize the threshold resistive switching in the cell. Finally, we summarize the thesis and perspective in <u>Chapter 6</u>.

#### **1.3.** List of publications

Only the publications included below shall be considered for the evaluation of this PhD Dissertation. A reproduction of each publication can be accessed by the information indicated below. A complete list of the author's publications (updated on May 29<sup>th</sup>, 2024) is included in the scientific curriculum vitae (Appendix A).

Article 1: Bin Yuan, Kaichen Zhu, Tingting Han, Sebastian Pazos, Mario Lanza\*, "All-2D materials-based 1T1M cells with threshold switching for electronic neurons," *Microelectronic Engineering*, revised.

\* The author's contribution: methodology, investigation, writing draft, visualization.

Article S1: Mario Lanza\*, Felix Palumbo\*, Yuanyuan Shi, Fernando Aguirre, Santiago Boyeras, Bin Yuan, Eilam Yalon, Enrique Moreno, Tianru Wu, Juan B. Roldan, "Temperature of Conductive Nanofilaments in Hexagonal Boron Nitride Based Memristors Showing Threshold Resistive Switching," *Advanced Electronic Materials*, 2100580, 2021.

\* The author's contribution: perform parts of the experiments.

Article S2: Tingting Han, Fernando Aguirre, Kaichen Zhu, Bin Yuan, Sebastian Pazos, Sui-Dong Wang, Shaojuan Li, Mario Lanza\*, "Fully two-dimensional materials-based resistive switching circuits for advanced data encryption," under review.

\* The author's contribution: review and suggestion.

Article S3: Wenwen Zheng, Bin Yuan, Kaichen Zhu, Sebastian Pazos, Yaqing Shen, Yue

Yuan, Yue Ping, Chen Liu, Xiaowen Zhang, Xixiang Zhang, Mario Lanza\*,

"Ultralow defect density metal evaporation on 2D materials," under review.

\* The author's contribution: perform parts of the experiments.

## **Chapter 2: Device fabrication methods**

This research employs various fabrication techniques to create micro/nano-scale electronic devices, utilizing h-BN as an insulating material. In this chapter, we elucidate the specific fabrication methods, parameters, and processes employed in our study.

#### 2.1. Mechanical exfoliation method

Following the discovery of graphene in 2004 [80], the ME method saw extensive application. Over the years, with substantial development by researchers in the field of 2D materials, the ME method has undergone numerous modifications and enhancements. For instance, the original Scotch tape used in [80] was found to be excessively adhesive, resulting in polymer residues on the substrate after transfer. In our study, we opted for a different tape, SPV 224 from Nitto, which has a weaker adhesive force. This choice is motivated by the tape's reduced tendency to leave polymer residues on the substrate during the mechanical exfoliation process.

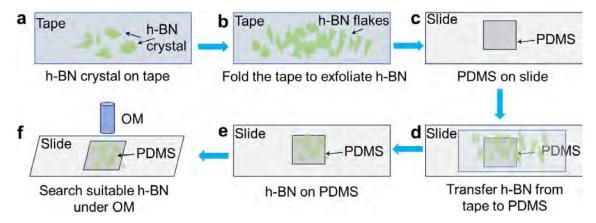

Figure 2.1 Mechanical exfoliation process of h-BN. (a) Crystal h-BN on tape. (b)h-BN flakes on tape after exfoliating several times. (c) A suitable piece of PDMS on a slide. (d) Soft press the tape to transfer the h-BN flakes to PMDS on the slide. (e)PDMS with h-BN flakes. (f) Search for thin h-BN flakes under an optical microscope.

In Figure 2.1, we illustrate the mechanical exfoliation process of h-BN. High-purity single-crystal h-BN is grown under high-temperature and high-pressure conditions [199]. Initially, we fix the tape (model SPV 224 from Nitto) onto the table and place

some h-BN particles on the tape (Figure 2.1a). We then use a new tape to exfoliate the h-BN particles on the fixed tape, repeating this step several times to obtain smaller h-BN flakes, as depicted in Figure 2.1b.

In some literature, the flakes are commonly transferred from the tape to a substrate, such as a SiO<sub>2</sub>/Si wafer [200,201]. However, we opt for the dry transfer method to move the 2D materials to our desired location. To facilitate this, we cut a piece of polydimethylsiloxane (PDMS, 6 mil thick from Gel-pak) to cover the flakes and place it on a clean slide (see Figure 2.1c). During this placement, it is crucial to avoid bubbles between the slide and PDMS, as they make it difficult to focus under an optical microscope and can affect the subsequent dry transfer process.

Once we have confirmed that the PDMS is flat on the slide, we place the tape with h-BN flakes on top of the PDMS and gently press the tape using a cotton bud to transfer as many h-BN flakes as possible to the PDMS (Figure 2.1d). After slowly lifting the tape from the PDMS, we are left with some h-BN flakes on the PDMS, as shown in Figure 2.1e. Subsequently, we employ an optical microscope (OM, model LV 100N POL from Nikon) in reflection mode to locate the transferred h-BN flakes on the PDMS (Figure 2.1f). We might need to repeat the steps from Figure 2.1c to Figure 2.1f several times to identify the desired exfoliated flakes.

Furthermore, we have mechanically exfoliated h-BN flakes by following the same procedure outlined in Figure 2.1. After identifying the location of the flakes on the PDMS and capturing optical images for documentation, we store the slide in a protective case. This allows for the dry transfer process to be conducted at a later time when required.

#### 2.2. Dry transfer of 2D materials

For mechanically exfoliated 2D materials, a precision transfer method is essential in the device fabrication process. Since the exfoliated materials typically have small dimensions—ranging from several micrometers to hundreds of micrometers, depending on the thickness and material—we require accurate transfer to the designated locations for the devices. A transfer stage and the dry transfer method are widely utilized for mechanically exfoliated 2D materials to achieve this objective

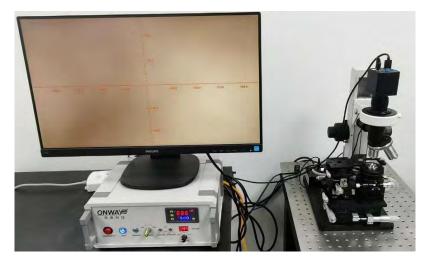

Figure 2.2 Transfer stage for the dry transfer of mechanically exfoliated 2D materials.

Figure 2.2 illustrates the transfer stage utilized in this research. Originating from Shanghai Onway Technology, the stage comprises an optical microscope, a removable stage for 2D materials, a heating mode, and a screen. Typically, the stage is mounted on an anti-vibration platform to minimize vibrations during the transfer process. On the screen, coordinate axes (as shown in Figure 2.2) serve as a reference for aligning the 2D materials with the target substrate.

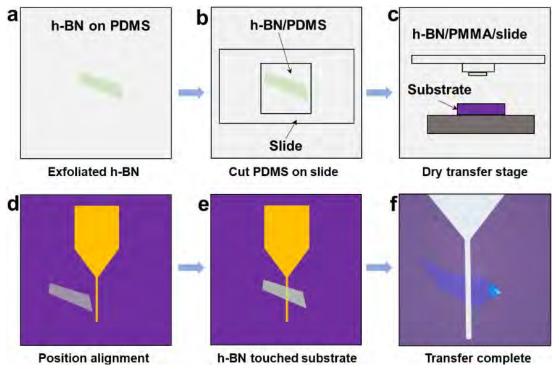

The transfer process is depicted in Figure 2.3.

- i) First, we prepare the 2D materials for transfer. Here, we use h-BN obtained through mechanical exfoliation, as shown in Figure 2.1.

- ii) Based on the size of the h-BN on the PDMS, we use a scalpel to cut the PDMS as small as possible (Figure 2.3b) without damaging the h-BN. A smaller PDMS piece will facilitate more precise placement of the h-BN at the selected location during the dry transfer process.

- iii) Then, we adjust the transfer stage to correctly align the slide with the 2D materials and the target substrate, as shown in Figure 2.3c. Using the optical microscope, it is possible to locate the 2D material and fine-tune the position until the material overlaps with the target on the substrate (Figure 2.3d).

- iv) Finally, we slowly lower the slide until the h-BN on the PDMS touches the substrate (Figure 2.3e). This process must be very gradual. As the slide and substrate approach each other closely, we need to precisely adjust the position of the 2D material to ensure a correct transfer. Typically, we heat the sample plate to 50°C for 3 to 5 min (for h-BN, these parameters can be

optimized depending on the material used). Since the PDMS is a thermal release tape, heating reduces the adhesion between the 2D materials and PDMS, promoting transfer from the PDMS to the target substrate.

v) Carefully lift the slide to release the PDMS from the target substrate. This step is very delicate and should be executed with caution. If the material remains on the PDMS, it indicates that the force between the material and PDMS is greater than the van der Waals force between the substrate and 2D materials. Additional heating time may be required to weaken the adhesion force on the PDMS.

Lastly, the h-BN flake is successfully transferred to the bottom electrode on the substrate, and an optical microscope image is shown in Figure 2.3f.

Figure 2.3 Dry transfer process. (a) h-BN flake is prepared to transfer. (b) Cut the PDMS smaller. (c) Fix the slide and substrate on the transfer stage. (d) Modify the position of the h-BN to the top of the bottom electrode on the substrate. (e) PDMS touches the substrate. (f) Image of real sample after transfer.

The process outlined above represents the standard dry transfer operation for the 2D materials utilized in this thesis. Following the transfer, the 2D material underwent characterization using an optical microscope and an AFM to verify its integrity and

confirm that it remained undamaged and intact. The transfer stage and the employed dry transfer methodology have proven to be sufficiently adept for meeting our device fabrication specifications.

# 2.3. Wet transfer method for CVD-grown 2D materials

CVD-grown 2D materials are typically synthesized on metal foils, as these metals can facilitate the decomposition of precursors due to their lower energy barriers and catalytic activity [202]. Graphene, for instance, is commonly grown on Cu foil [203] or Pt substrates [204]. While it is possible to synthesize some 2D materials directly on the target substrate [205], challenges remain inherent to this approach.

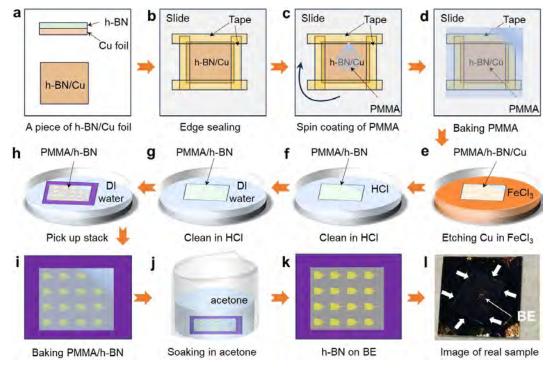

**Figure 2.4** Wet transfer process (a) A piece of Cu foil with h-BN grown by CVD. (b) h-BN/Cu foil piece sealed and fixed on a slide by tape. (c) Spin coating of PMMA on the

surface of h-BN. (d) Soft baking on a hot plate to remove liquid in PMMA. (e) PMMA/h-BN/Cu foil in saturation FeCl<sub>3</sub> solution. (f) PMMA/h-BN stack in 2wt% HCl solution. (g) PMMA/h-BN stack in DI water. (h) Transfer the PMMA/h-BN stack onto the target substrate. (i) Baking the water in the devices. (j) Soaking the sample in acetone to remove PMMA. (k) h-BN transferred on substrate with BE. (i) Image of a real h-BN transferred sample. For the h-BN used in this thesis, we purchased it from Graphene Supermarket Co., where the h-BN is synthesized on a Cu foil. We employed a widely recognized wet transfer method [197] to facilitate the transfer of h-BN onto our desired substrate.

The wet transfer process steps are presented in Figure 2.4.

- First, we cut a piece of Cu foil with h-BN on the surface (Figure 2.4a), which is large enough to cover the bottom electrode on the target substrate.

Since both sides of the Cu foil have h-BN, the supplier marks the side with better quality. We always use this side to achieve the best performance.

- Then, we need to flatten the h-BN on a slide with another slide using clean paper to protect the h-BN piece. Tape is used to secure the h-BN onto the slide and seal all edges (Figure 2.4b) to prevent the polymethyl methacrylate (PMMA) from seeping into the back side during the spin coating process. If not sealed properly, it will be difficult to etch the Cu foil in the following steps.

- Next, spin coating of PMMA (950 K, A4, from Kayaku) on the surface of the h-BN. The parameters are set to 500 rpm for 6s and 3,500 rpm for 30 s, respectively (Figure 2.4c).

- iv) We then bake the sample with PMMA at 100 °C for 3 min on a hot plate to form a stable PMMA layer to support the h-BN layers in the next steps.

- v) After removing the tape around the edges, we re-flattened the foil and put the h-BN foil covered by the PMMA into saturated ferric chloride (FeCl<sub>3</sub>) solution to etch the Cu foil, as shown in Figure 2.4e. The side of the substrate devoid of PMMA should be immersed face-down in the FeCl<sub>3</sub> solution. This process will take several hours (more than 8 hours in our research) until the PMMA/h-BN stack becomes transparent.

- vi) Once the Cu foil is etched, we transfer the PMMA/h-BN stack to 2 wt% hydrochloric acid (HCl) solution for 2 min to clean the stack (Figure 2.4f).

- vii) Subsequently, we move the PMMA/h-BN stack to deionized (DI) water for 20 min for cleaning (Figure 2.4g).

- viii) Then we transfer the PMMA/h-BN stack to the substrate with the bottom electrode, as presented in Figure 2.4h, and bake the sample at 50 °C for 5 min to remove water and achieve better van der Waals contact between the h-BN and substrate (Figure 2.4i).

- ix) We then soak the PMMA/h-BN/substrate in acetone for 12 hours to remove the PMMA (Figure 2.4j).

- x) Finally, after annealing at 50 °C for 30 min, the h-BN is successfully transferred to the substrate. as shown in Figure 2.4k. A real transfer completed sample image is presented in Figure 2.4l we can observe that the bottom electrode (BE) is covered by the h-BN (area pointed by the wide white arrows) by naked eyes.

#### 2.4. Device electrode fabrication

The conductive electrode is an important part of electrical characterization during the device fabrication process. In this research, we fabricate the metal electrode in two ways for micro and nano-scale devices, respectively. For micro-scale devices, we use photolithography to transfer the pattern to the substrate, and for nano-devices, we use electron beam lithography to conduct the pattern transfer work.

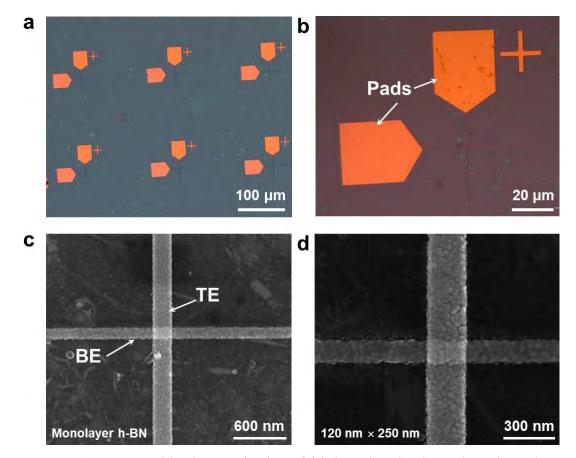

#### 2.4.1. Photolithography for micro-scale device electrode

Photolithography stands as an exceedingly mature fabrication technique within the pattern transfer process, widely recognized and utilized in both academia and industry. Mask aligners are categorized based on the wavelength of ultraviolet (UV) light they employ, which includes ultraviolet (UV), deep ultraviolet (DUV), and extreme ultraviolet (EUV) [206]. It is well known that DUV and EUV technologies are predominantly utilized in the industry for the production of high-resolution chips, ranging from tens of nanometers down to a few nanometers. In contrast, UV photolithography is more prevalent in laboratory research settings.

In our research, we employ a UV mask aligner, the model MJB4 from SUSS Micro Tec. This equipment is capable of achieving a highest resolution of 2  $\mu$ m, although this level of precision has become challenging to attain due to the age of the machine. For the electrodes in our devices, we have opted for a resolution of 5  $\mu$ m, considering the optimal balance between stable quality and yield.

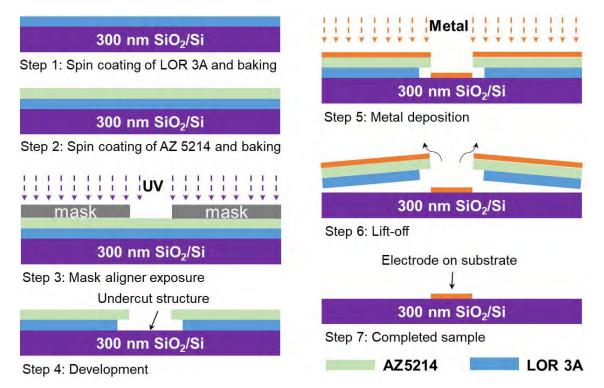

We utilize the bilayer method, which involves two distinct layers of photoresist, to achieve an undercut structure as illustrated in Figure 2.5 (step 4). An undercut structure is created when the etching process removes material from the sides of the photoresist pattern, resulting in an angled sidewall that is wider at the bottom than at the top. This structure allows us to fabricate electrodes with flat edges, which is particularly beneficial for subsequent AFM characterization.

Initially, we design the photomask using Tanner software, a tool for pattern design, which is then manufactured by Suzhou Photomask Company. The photomask is typically made from soda glass, measuring 3 inches in diameter. One side of the mask is coated with chromium (Cr), except for the pattern areas, while the other side remains uncoated. This type of photomask is known as a positive mask, where the pattern region allows light transmission. The positive mask is used in conjunction with a positive photoresist; light passes through the transparent pattern region and reacts with the photoresist to break the molecular bonds within it. Subsequently, during the development process, the exposed and reacted regions (the pattern) are removed with specialized chemicals known as developers, leaving the desired pattern intact on the substrate. This selective removal means that we can add films or perform etching only in the patterned areas, as the other areas remain protected by the photoresist.

Figure 2.5 Photolithography process using bilayer method.

The photolithography process, as outlined in Figure 2.5, is detailed in the following steps:

Step 1: Initially, we apply a layer of LOR 3A (a non-light-sensitive resist from Micro Chem) as the bottom layer of our bilayer lift-off technique on a substrate (300 nm SiO<sub>2</sub>/Si). The application is performed using a spin coater set at 6,000 rpm for 30 s, followed by a soft bake at 150°C for 3 min. The LOR 3A resist, though not sensitive to light, dissolves more rapidly in a special developer than the subsequent layer of photoresist (AZ5214).

Step 2: Subsequently, we spin coat a second layer of positive-tone photoresist (model AZ5214 from Micro Chem) with the following parameters: 4,000 rpm for 30 s, and a soft bake at 95°C for 90 s.

Step 3: We then secure the photomask onto the mask aligner in contact with the substrate bearing the photoresist layers. Employing a soft contact mode ensures that the mask gently touches the sample. Exposure is followed by UV light passing through the transparent patterned areas of the mask, initiating a reaction with the photoresist that alters its structure, thereby facilitating its removal during development.

Step 4: The sample is immersed in a developer solution, tetramethylammonium hydroxide (TMAH) at 2.38% concentration, for 45 s, then rinsed in DI water. During this phase, the LOR 3A dissolves more quickly than the AZ5214 that has been exposed, resulting in an undercut structure of the pattern sidewalls as illustrated in step 4 of Figure 2.5.

Step 5: Subsequently, metal deposition is carried out on the sample, as indicated in Figure 2.5. The metal in the patterned area does not make contact with the metal in other areas.

Step 6: The subsequent phase involves the lift-off process, which removes the unwanted metal from the substrate, preserving only the patterned region. This is accomplished by immersing the sample in a specialized remover. For our bilayer lift-off process, we utilize n-methylpyrrolidone (NMP) as the remover. The sample is placed in a beaker filled with NMP and both are immersed in a water bath at 60°C for a duration exceeding 90 min.

Step 7: Ultimately, the electrode is successfully fabricated on the substrate, as represented in the figure.

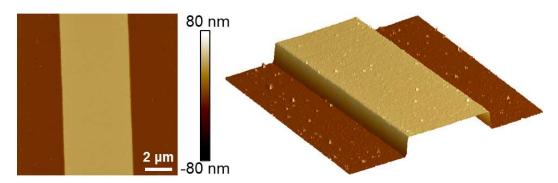

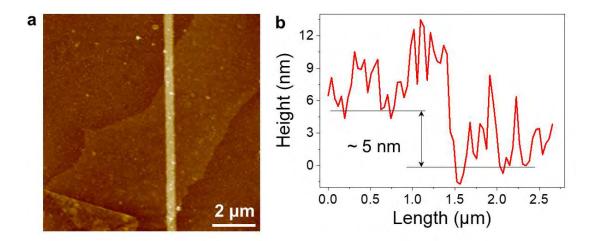

The AFM topography map presented in Figure 2.6 illustrates the bottom electrode fabricated using the bilayer lift-off technique. This electrode has a thickness of 40 nm.

The left-hand image clearly demonstrates that the surface of the bottom electrode is smooth and free of contaminants. Upon examining the three-dimensional (3D) view depicted in the right-hand figure, only a minimal number of particles are discernible, which are likely to be dust particles. The sharply defined edge of the bottom electrode suggests that the transferred h-BN can adhere precisely to the electrode's surface. This characteristic will prove particularly advantageous during the subsequent characterization of the h-BN's thickness after transfer.

**Figure 2.6** AFM topography map of electrode for micro-scale devices. The electrode has a sharp edge which is friendly to 2D materials transfer and characterization.

# 2.4.2. Electron beam lithography for nano-scale device electrode

In laboratory research, EBL is the predominant method for fabricating devices at the nano-scale. Within the EBL system, the electron beam is directed by a pattern generator to inscribe the desired pattern directly onto a substrate coated with PMMA, which serves as a photoresist in the EBL process. The sample, once written, is immersed in a developer and then stoper solution to dissolve the PMMA exposed by the electron beam, thereby leaving the pattern onto the substrate for following operations.

The advantages of EBL are manifold: i) It eliminates the need for physical masks, enabling the testing of numerous patterns without the associated mask fabrication costs and time investment. ii) EBL is capable of producing nano-scale features that are challenging for other fabrication techniques to achieve. iii) It does not necessitate the use of a yellow room or a cleanroom environment for the fabrication process.

However, a key limitation of EBL stems from its operational principles, resulting in a relatively low yield.

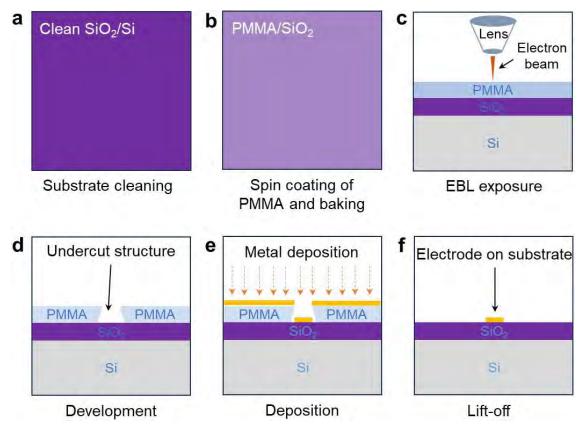

Figure 2.7 Fabrication of bottom electrode using EBL.

The EBL system we utilized consists of a pattern generator from Raith (model Elphy VII from Raith) in conjunction with a scanning electron microscope (model Quanta 200 FEG from FEI). The entire EBL process can be divided into the following steps, as presented in Figure 2.7:

a) The substrate is cleaned using ultrasonic cleaner with acetone, ethanol, and DI water.

b) Spin coating PMMA (950K, A4, from Kayaku) on the substrate. The parameters are 3,500 rpm for 60 s, then baking at 180 °C for 90 s.

c) Subsequently, the exposure is conducted in a vacuum chamber (<  $2 \times 10^{-3}$  Torr). The pre-designed pattern is directly written onto the PMMA layer at 20 kV and with suitable parameters.

d) After the patterning of the electrodes, the development process is carried out in a solution (isopropanol: methyl isobutyl ketone = 3:1) for 2 min, then soaked in a stopper (IPA) for 30 s. After development, we typically use an optical microscope to verify that the correct pattern has been produced by the EBL. Additionally, due to electron scattering at the base of the PMMA, an undercut structure is formed, as shown in Figure

2.7d. This undercut structure facilitates the lift-off process, resulting in a sharp edge of the pattern, as mentioned in the bilayer lift-off section.

e) Following development, metal is deposited onto the sample, and an illustration is presented in Figure 2.7e. Owing to the undercut structure, the deposited metal will not form a continuous film from the PMMA surface to the pattern. Such samples will be easier to process for the removal of unwanted metal during the lift-off step.

f) Finally, the fabrication of the bottom electrode via EBL, metal deposition, and lift-off is completed.

# 2.4.3. Metal deposition for electrode

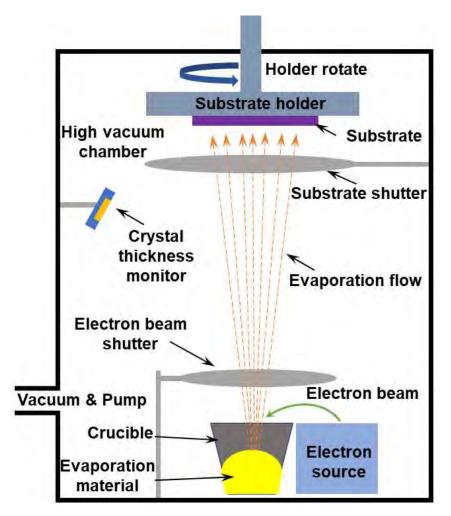

Figure 2.8 Schematic of electron beam evaporation.

The electrode patterns for the devices can be fabricated using either photolithography or the EBL method. In terms of metal deposition, we exclusively utilize electron beam evaporation. This is because the evaporation temperature is lower than that of thermal evaporation, which is advantageous during the lift-off step for removing the photoresist in photolithography or the PMMA in EBL fabricated devices. High temperatures during the metal deposition process would cause the photoresist or PMMA to solidify, thereby making them difficult to remove during the lift-off process.

Magnetron sputtering can deposit metals without temperature concerns. However, the sputtered atoms possess higher energy compared to evaporated atoms, and these high-energy atoms could potentially damage the layered materials.

The schematic representation of the electron beam evaporation process is depicted in Figure 2.8. Samples are secured to the sample plate using heat-resistant tape. A highenergy electron beam, generated by the electron gun, is directed onto the material contained within the crucible. This beam heats and vaporizes the material. Subsequently, the metals, now in a gaseous state, traverse the chamber and undergo condensation upon contact with the substrate. The substrate is equipped with a rotational mechanism that operates at an adjustable speed, ensuring the formation of a uniformly thick film. An electron beam shutter is employed to meticulously control the precise thickness and to maintain a consistent film quality, alongside a stable deposition rate. The electron beam shutter remains closed until the evaporation rate stabilizes. The substrate shutter is activated post the opening of the electron beam shutter, allowing the vaporized metal to condense on the substrate.

The thickness of the deposited film is monitored in real-time using a crystal thickness monitor. Once the measured thickness reaches the predetermined value, the substrate shutter is closed to conclude the evaporation process

The model of the electron beam evaporation system we use is the PVD 75 from Kurt J. Lesker Company. The chamber vacuum can achieve 10<sup>-5</sup> Torr after pumping. The machine is equipped with four distinct sources that facilitate the sequential deposition of various metals, all without the need to vent the chamber or replace the crucibles.

## 2.5. Summary

This chapter provides an overview of the primary techniques employed for device fabrication in this research endeavor. It delves into the working principles and procedural intricacies of mechanical exfoliation, dry transfer, wet transfer, photolithography, EBL, and electron beam evaporation. Additionally, it enumerates the specific parameters utilized throughout the fabrication process.

In summary, this chapter compiles the majority of the data and pertinent details concerning device fabrication, thereby eliminating the need to reiterate certain fabrication specifics in subsequent chapters. It is designed to enhance the reader's comprehension of the entire thesis, particularly the segment dedicated to device fabrication.

# Chapter 3: Dielectric breakdown of exfoliated h-BN in micro-scale devices

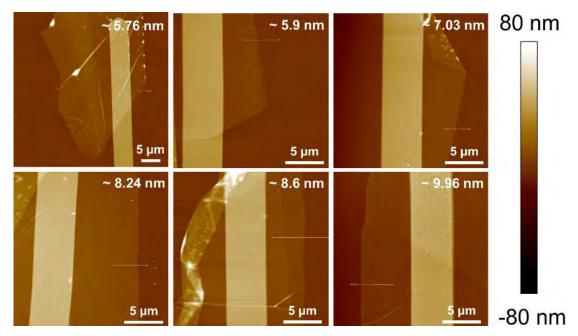

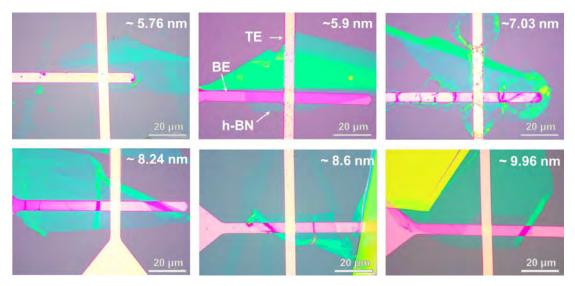

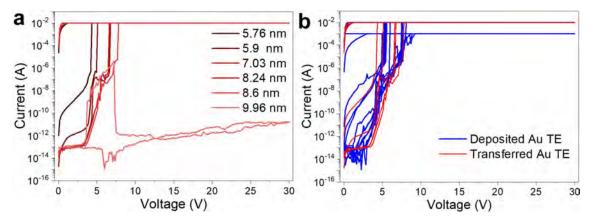

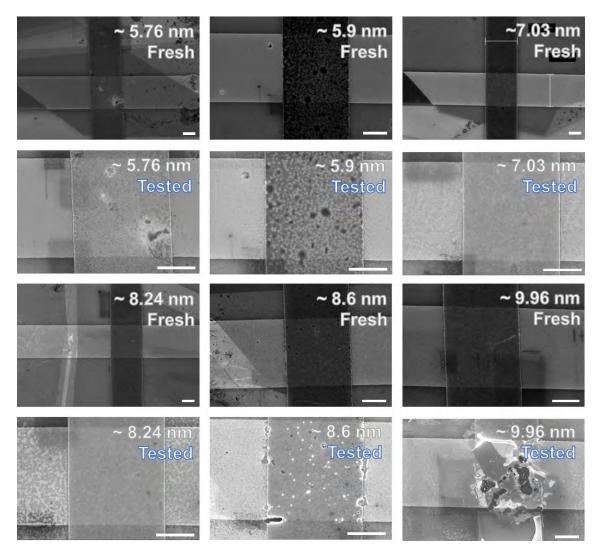

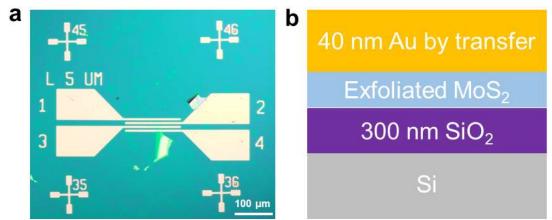

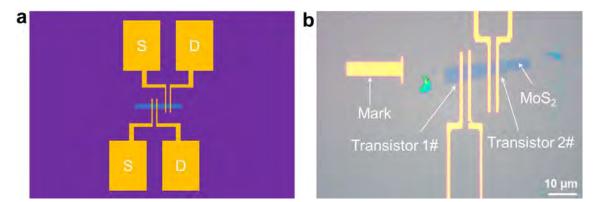

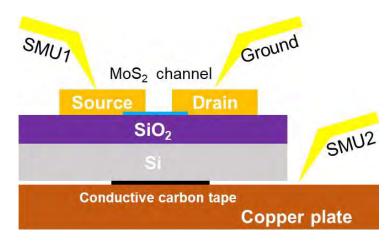

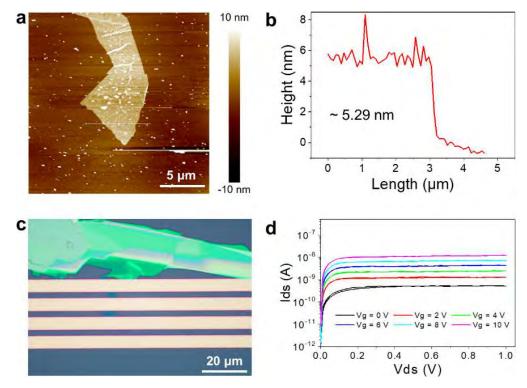

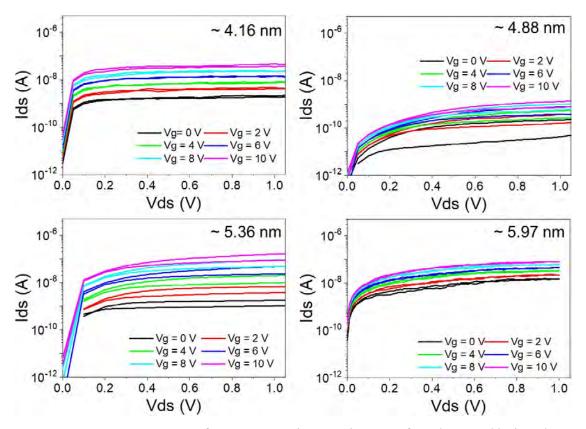

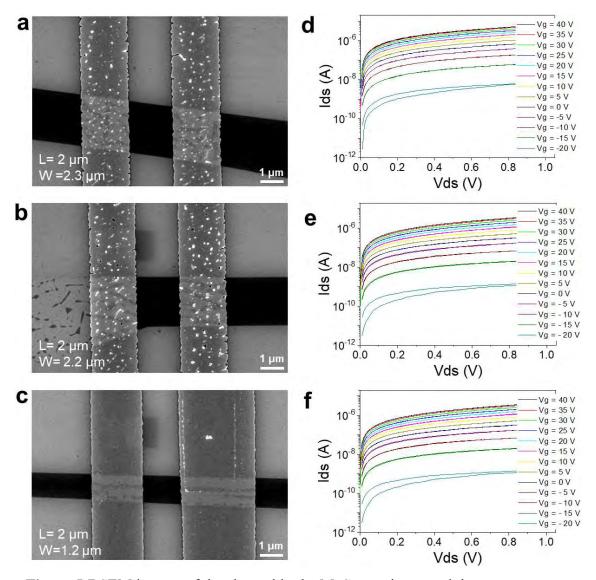

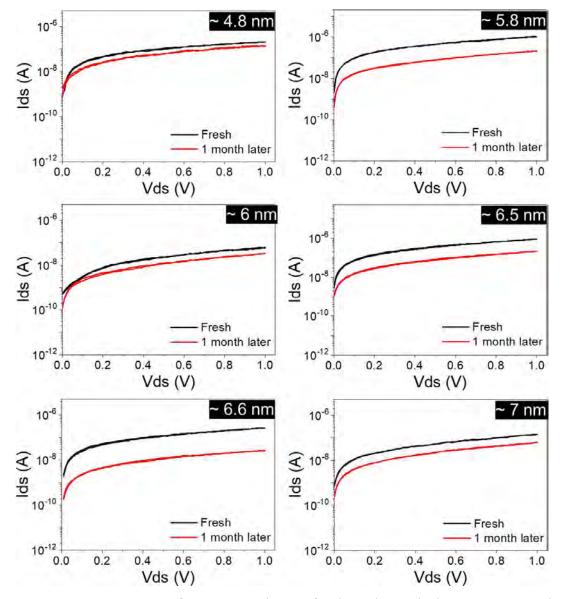

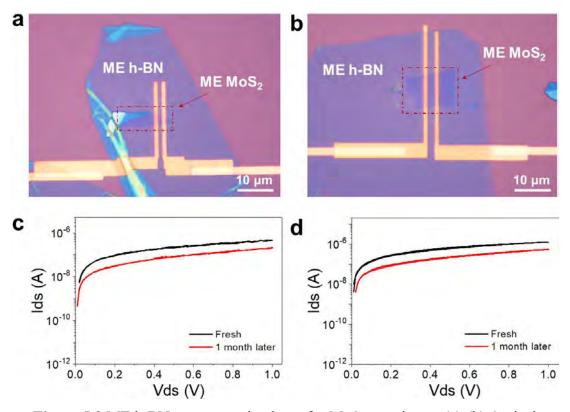

# 3.1. Introduction