**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

Department of Signal Theory and Communications Universitat Politècnica de Catalunya

# Computing Resource Management in Software-Defined and Cognitive Radios

DISSERTATION

Vuk Marojevic

Dr. Antoni Gelonch (Ph.D. Supervisor)

Barcelona, July 2009

I would like to thank the Radio Communications Research Group of the UPC for supporting my Ph.D. studies, which led to the elaboration of this thesis. I also thank the Mobile and Portable Radio Research Group of Virginia Tech for their support during my short term visiting scholar in 2007.

This work has been supported by the CICYT (Spanish National Science Council) under grants TIC2003-08609 and TEC2006-09109, which are partially financed from the European Community through the FEDER program, and the AGAUR agency of the Catalonian Government.

# Summary

Our research aims at contributing to the evolution of modern wireless communications and to the development of software-defined radio (SDR) and cognitive radio, in particular. It promotes a general resource management framework that facilitates the integration of computing and radio resource management. This dissertation discusses the need for computing resource management in software-defined and cognitive radios and introduces an SDR computing resource management framework with cognitive capabilities. The hard real-time computing requirements of software-defined digital signal processing chains (SDR applications), the associated radio propagation and quality of service (QoS) implications, and heterogeneous multiprocessor platforms with limited computing resources (SDR platforms) define the context of these studies.

We examine heterogeneous computing techniques, multiprocessor mapping and scheduling in particular, and elaborate a flexible framework for the dynamic allocation and reallocation of computing resources for wireless communications. The framework should facilitate partial reconfigurations of SDR platforms, dynamic switches between radio access technologies (RATs), and service and QoS level adjustments as a function of the environmental conditions. It, therefore, assumes the facilities of the *platform and hardware abstraction layer operating environment* (P-HAL-OE).

We suggest a modular framework, distinguishing between the computing system modeling and the computing resource management. Our modeling proposal is based on two computing resource management techniques, which facilitate managing the strict timing constraints of real-time systems. It is scalable and can account for many different hardware architectures and computing resource types. This work focuses on processing and interprocessor bandwidth resources and processing and data flow requirements.

Our computing resource management approach consists of a general-purpose mapping algorithm and a cost function. The independence between the algorithm and the cost function facilitates implementing many different computing resource management policies. We introduce a dynamic programming based algorithm, the  $t_w$ -mapping, where w controls the decision window. We present a general and parametric cost function, which guides the mapping process under the given resource constraints. An instance of it facilitates finding a mapping that meets all processing and data flow requirements of SDR applications with the available processing and bandwidth resources of SDR platforms. Several SDR reconfiguration scenarios and analyses based on simulations demonstrate the suitability and potentials of our framework for a flexible computing resource management.

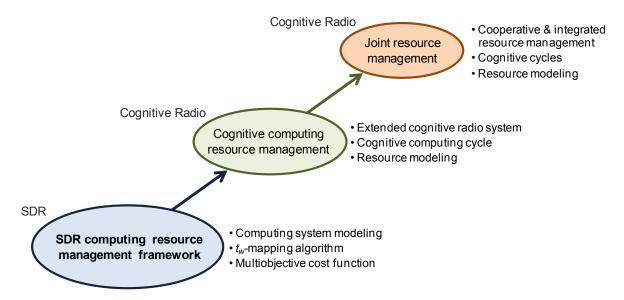

We extend our SDR computing resource management concepts to the cognitive radio context. The two primary objectives of cognitive radio are *highly reliable communications whenever and wherever needed* and *the efficient use of the radio spectrum*. We formulate a third objective as *the efficient use of computing resources*. We analyze the cognitive capabilities of our framework—the cognitive radio's interface to SDR platforms—and indicate the potentials of our *cognitive computing resource management* proposal.

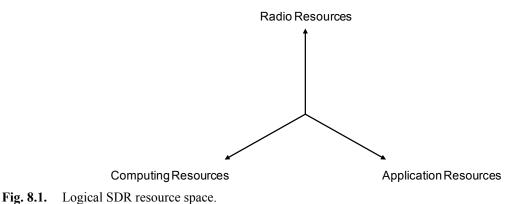

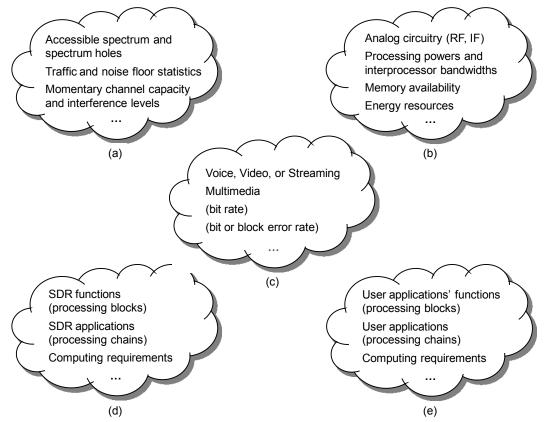

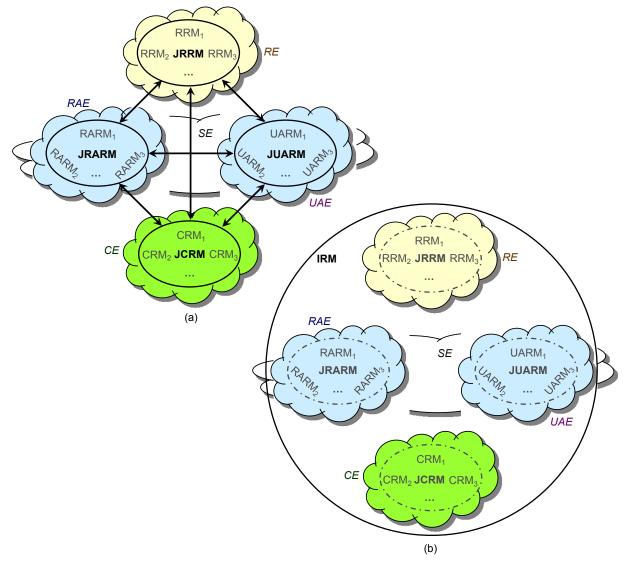

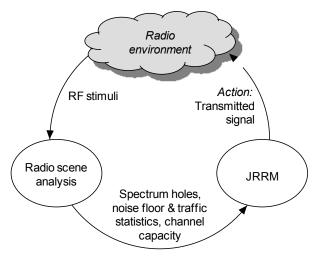

The cognitive computing resource management needs to be coordinated with the radio resource management. We, therefore, introduce the *joint resource management* concept for cognitive radios. We present three cognitive cycles and discuss several interrelations between the radio, computing, and application resources, where application resources refer to the available SDR and user applications. Our approach potentiates flexibility and facilitates radio against computing resource tradeoffs. It promotes cognition at all layers of the wireless system for a cooperative or integrated resource management that may increase the performance and efficiency of wireless communications.

# Resumen

El objetivo de las investigaciones que se están llevando a cabo dentro del grupo de investigación es contribuir a la evolución de las radiocomunicaciones modernas y, en particular, al desarrollo de los conceptos software radio (SDR) y cognitive radio. El planteamiento general es el de extender la flexibilidad global del sistema de comunicaciones planteando la definición y desarrollo de un entorno en el que pudiesen explorarse las relaciones entre la computación y las prestaciones del sistema de comunicaciones móviles facilitando la integración de los recursos de computación con los recursos radio.

Dentro de este marco, la presente tesis plantea la discusión de la necesidad de la gestión de los recursos de computación en entornos SDR y cognitive radio y define un entorno de operación que asume las características especificas del concepto SDR a la vez que incorpora capacidades cognitivas en la gestión de los recursos de computación de las plataformas que den soporte a las nuevas generaciones de sistemas móviles. Los estrictos requerimientos de procesado en tiempo real de las cadenas de procesado digital de la señal definidas por software (aplicaciones SDR), las implicaciones asociadas con la propagación radio y el concepto de calidad de servicio (QoS) y plataformas heterogéneas de múltiples procesadores con recursos de computo limitados (plataformas SDR) definen el contexto de estos estudios.

Se examinan técnicas de cómputo de propósito general para definir un entorno de operación que fuese capaz de asignar de forma flexible y dinámica los recursos de cómputo necesarios para facilitar las radiocomunicaciones a los niveles de QoS deseados. Ello debería facilitar los cambios dinámicos de una tecnología de acceso radio a otra, permitiendo el ajuste del tipo de servicio o calidad de servicio en función de las preferencias de los usuarios y las condiciones del entorno. Dicho entorno de operación asume las potencialidades del *platform and hardware abstraction layer operating environment* (P-HAL-OE).

La estructura del entorno de operación se define de forma modular y consiste en un modelado genérico y flexible de las plataformas de computación SDR y en una gestión de recursos de computación abierta y capaz de ajustarse a diferentes objetivos y políticas. En el trabajo se exponen dos técnicas de gestión que pretenden asegurar la consecución estricta de los límites temporales típicos de los sistemas en tiempo real. En cuanto al modelado, este es escalable y capaz de capturar un amplio abanico de arquitecturas hardware y recursos de computación. En el presente trabajo nos centramos en los recursos y requerimientos del procesado y transferencia de datos.

Se introduce un algoritmo de mapeo genérico e independiente de la función de coste. La independencia entre el algoritmo y la función de coste facilita la implementación de diferentes políticas de gestión de recursos computacionales. El  $t_w$ -mapping es un algoritmo basado en *dynamic programming*, donde *w* controla la ventana de decisión. Se presenta una función de coste genérica y parametrizable que permite guiar el proceso de gestión de los recursos. Una instancia de ella facilita encontrar una solución al proceso de asignación de recursos que cumpla todos los requerimientos de procesado y trasferencia de datos de las aplicaciones SDR con los recursos disponibles de las plataformas SDR. Diferentes escenarios y varios análisis basados en simulaciones demuestran la adecuación del entorno de trabajo definido y desarrollado, así como sus potencialidades para una gestión flexible de los recursos de cómputo. Se extienden los conceptos mencionados previamente para entornos cognitive radio. Los principales objetivos del concepto cognitive radio son la disponibilidad de comunicaciones altamente robustas en cualquier lugar y momento en que sean necesarias y el uso eficiente del espectro. Como tercer objetivo formulamos *el uso eficiente de los recursos de cómputo*. Analizamos las capacidades cognitivas de nuestro entorno de operación—la interfaz del sistema cognitive radio a las plataformas SDR—y resaltamos las potencialidades de nuestra propuesta de *gestión cognitiva de los recursos computacionales*.

Dicha gestión cognitiva de los recursos computacionales plantea una integración con la gestión de los recursos radio. Para ello introducimos el concepto de *gestión de recursos conjunta* para entornos cognitive radio. Se presentan tres ciclos cognitivos y se discuten algunas interrelaciones entre los recursos radio, de cómputo y de aplicación, donde los recursos de aplicación se refieren a las aplicaciones SDR y de usuario disponibles. Nuestra propuesta de gestión de recursos conjunta potencia la flexibilidad y facilita los inter-cambios entre recursos radio y de computación.

# Contents

| Ał | brevi                      | iations                                        | xiii |

|----|----------------------------|------------------------------------------------|------|

| 1  | Intro                      | oduction                                       | 1    |

|    | 1.1                        | Modern Radio Communications                    | 1    |

|    | 1.2 Software-Defined Radio |                                                | 2    |

|    | 1.3                        | Cognitive Radio                                | 3    |

|    | 1.4                        | Resource Management in SDR and Cognitive Radio | 4    |

|    |                            | 1.4.1 Radio Resource Management                |      |

|    |                            | 1.4.2 Computing Resource Management            | 7    |

|    | 1.5                        | Contribution and Outline                       | 10   |

| 2  | SDF                        | R Computing Resource Management Context        | 13   |

|    | 2.1                        | Introduction                                   |      |

|    | 2.2                        | SDR Frameworks                                 | 13   |

|    |                            | 2.2.1 SCA                                      | 13   |

|    |                            | 2.2.2 Q-SCA                                    | 16   |

|    |                            | 2.2.3 P-HAL-OE                                 | 17   |

|    |                            | 2.2.4 Other SDR Frameworks                     | 20   |

|    | 2.3                        | SDR Computing Resource Management Problem      | 21   |

|    |                            | 2.3.1 SDR Computing Environment                | 21   |

|    |                            | 2.3.2 Problem Formulation                      | 22   |

|    |                            | 2.3.3 Scope and Assumptions                    | 22   |

|    | 2.4                        | Related Work                                   | 23   |

|    |                            | 2.4.1 Maximizing Speedup                       | 24   |

|    |                            | 2.4.2 Meeting Real-Time Deadlines              | 25   |

|    |                            | 2.4.3 Following Other or Multiple Objectives   | 25   |

|    | 2.5                        | Conclusions                                    |      |

| 3 | SDF | R Computing System Modeling                             | 29 |

|---|-----|---------------------------------------------------------|----|

|   | 3.1 | Introduction                                            | 29 |

|   | 3.2 | Computing Resource Management Facilities                |    |

|   |     | 3.2.1 Metrics                                           |    |

|   |     | 3.2.2 Time Slots and Pipelining                         |    |

|   | 3.3 | Modeling                                                |    |

|   |     | 3.3.1 Platform Modeling                                 |    |

|   |     | 3.3.2 Application Modeling                              |    |

|   | 3.4 | Meeting the SDR Computing Constraints                   |    |

|   | 3.5 | Modeling Examples                                       |    |

|   | 3.6 | Additional Modeling Features and Extensions             |    |

|   |     | 3.6.1 Dividing and Merging of Platforms or Applications |    |

|   |     | 3.6.2 Hierarchical Modeling                             | 48 |

|   | 3.7 | Summary                                                 | 49 |

| 4 | SDI | R Computing Resource Management                         | 51 |

|   | 4.1 | Introduction                                            | 51 |

|   | 4.2 | Mapping Algorithms                                      |    |

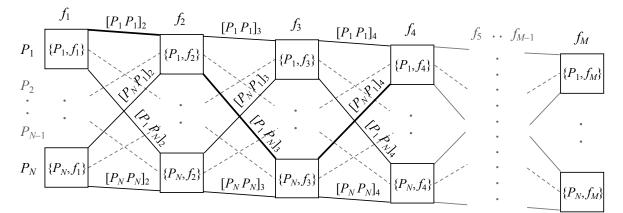

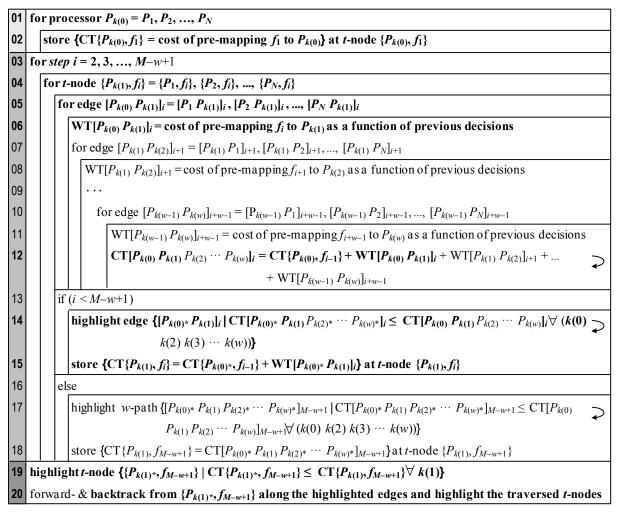

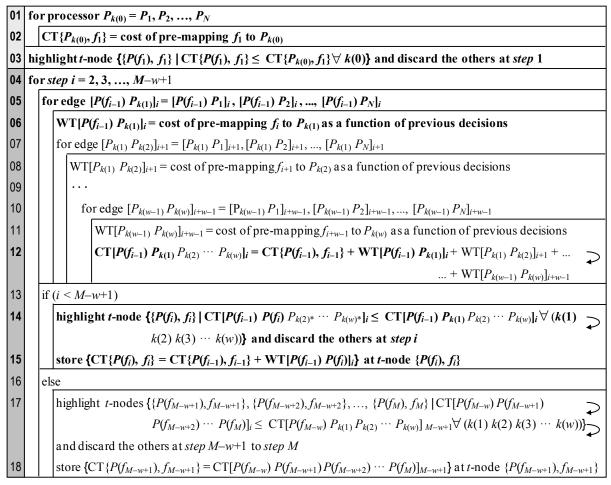

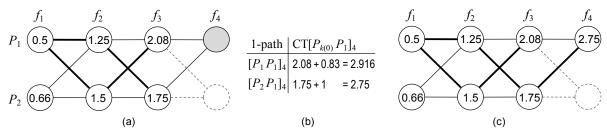

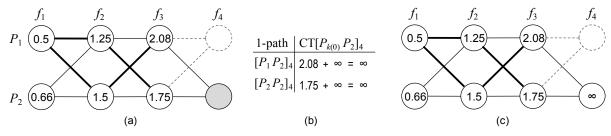

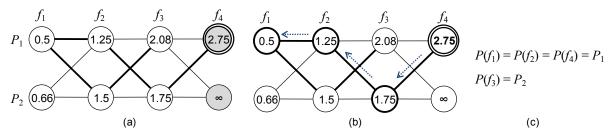

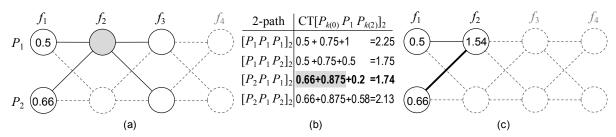

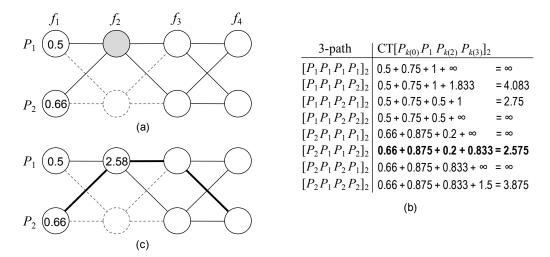

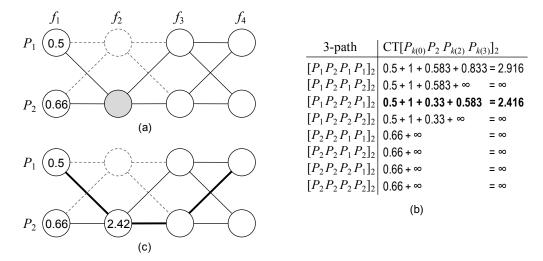

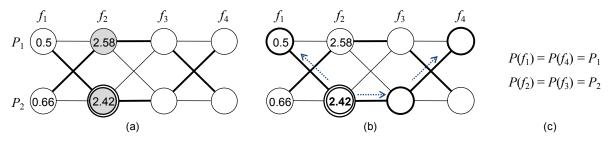

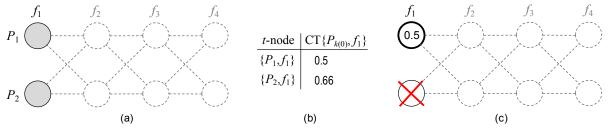

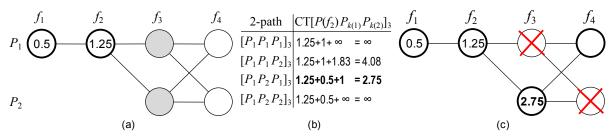

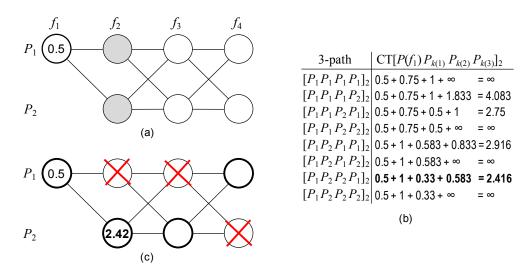

|   |     | 4.2.1 The $t_w$ -mapping                                | 53 |

|   |     | 4.2.2 The $g_w$ -mapping                                | 55 |

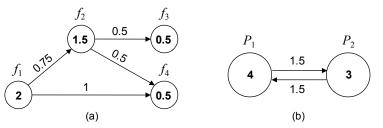

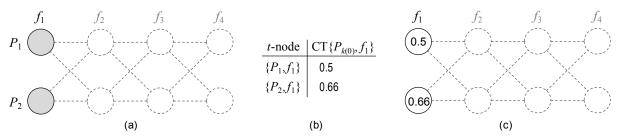

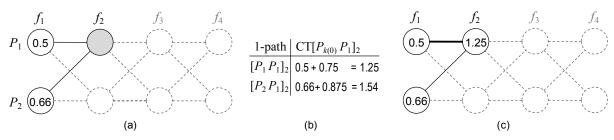

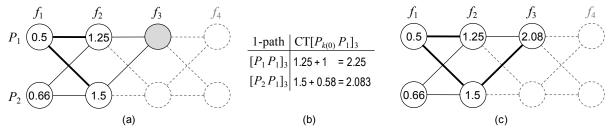

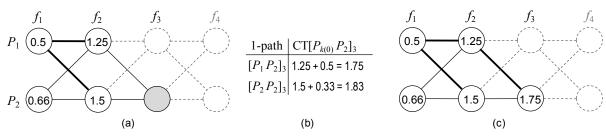

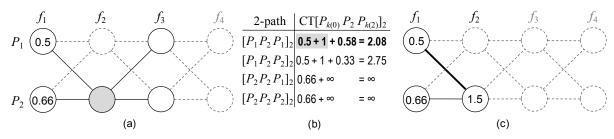

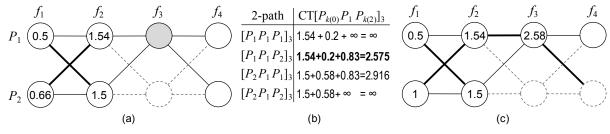

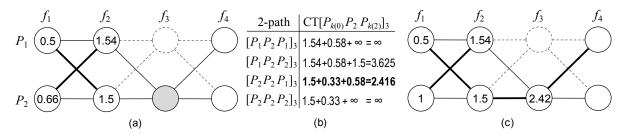

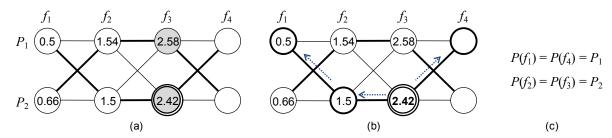

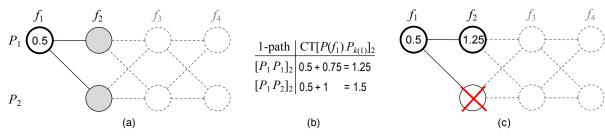

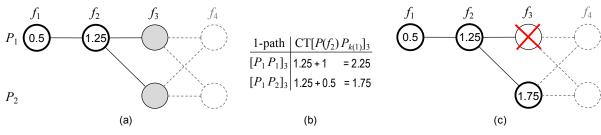

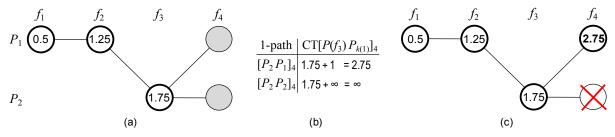

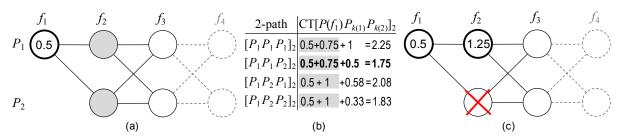

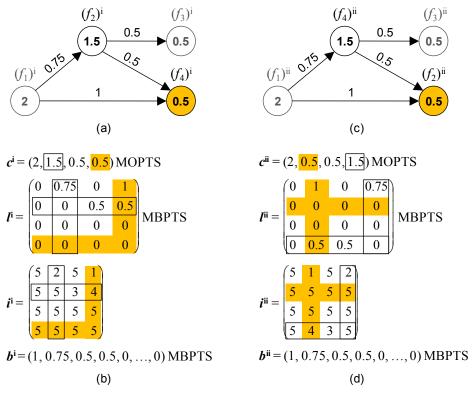

|   |     | 4.2.3 Exemplifying the $t_w$ - and $g_w$ -mapping       |    |

|   | 4.3 | Cost Function                                           | 62 |

|   |     | 4.3.1 Cost Function Template                            | 63 |

|   |     | 4.3.2 Cost Function Instance                            | 63 |

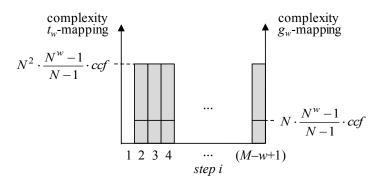

|   | 4.4 | Complexity Analysis                                     | 65 |

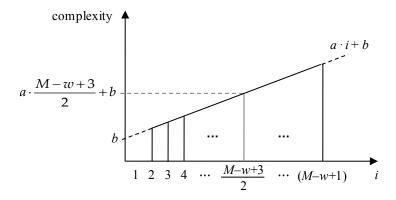

|   |     | 4.4.1 General Complexity Formulation                    |    |

|   |     | 4.4.2 Specific Complexity Formulation                   | 66 |

|   |     | 4.4.3 General versus Specific Complexity Formulation    |    |

|   | 4.5 | SDR Computing Resource Management Example               |    |

|   | 4.6 | Summary                                                 | 72 |

| 5 | SDF | R Scenarios and Simulations                             | 73 |

|   | 5.1 | Introduction                                            | 73 |

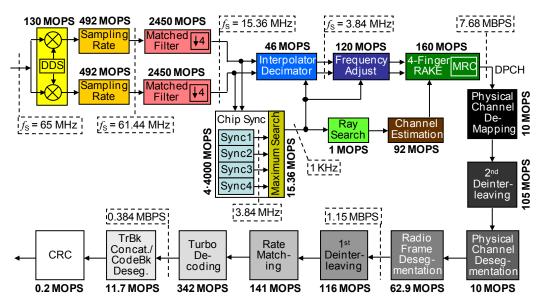

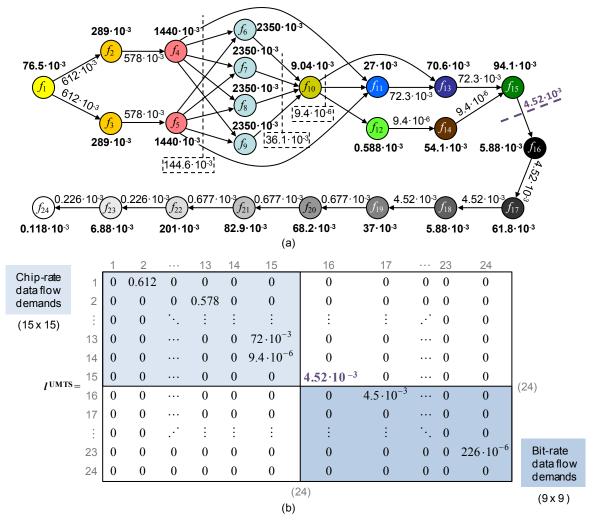

|   | 5.2 | UMTS Task Graph                                         | 73 |

|   |     | 5.2.1 Scenario – Simulation Setup                       | 73 |

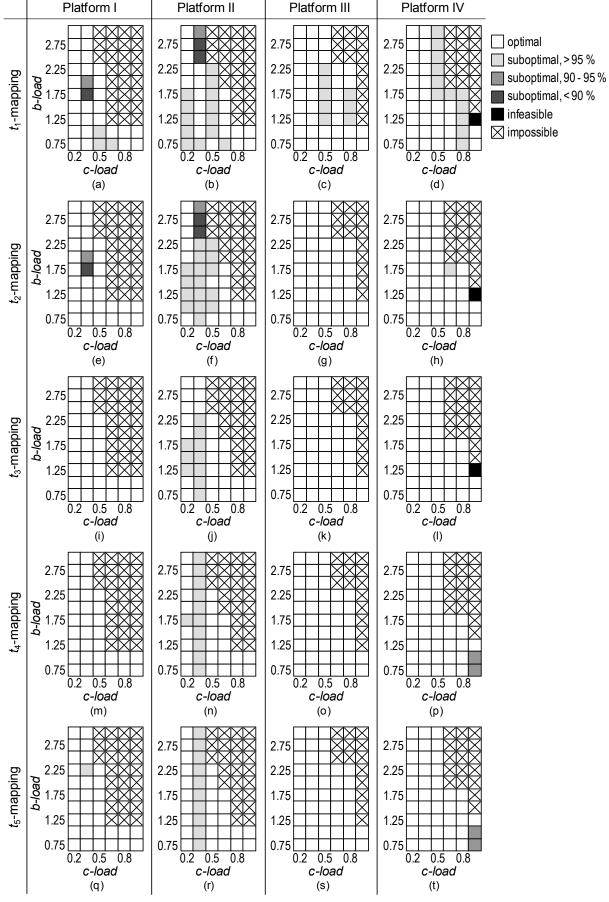

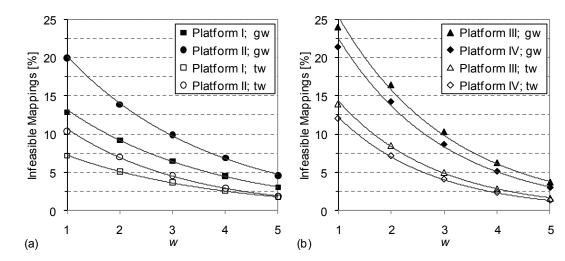

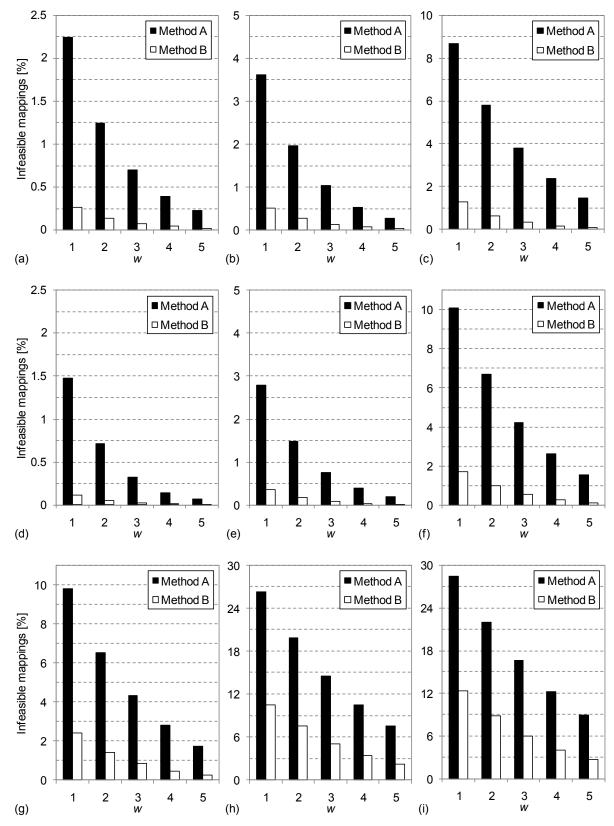

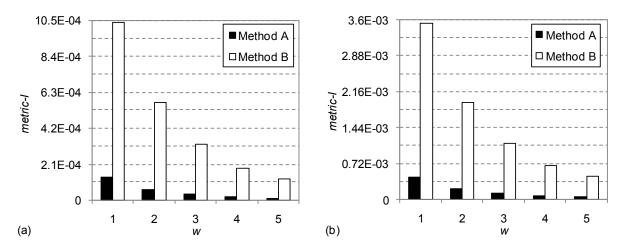

|   |     | 5.2.2 Simulation Results                                | 74 |

|   |     | 5.2.3 Practical versus Theoretical Complexities         | 74 |

|   | 5.3 | Random Task Graphs                                      |    |

|   |     | 5.3.1 Scenario – Simulation Setup                       | 78 |

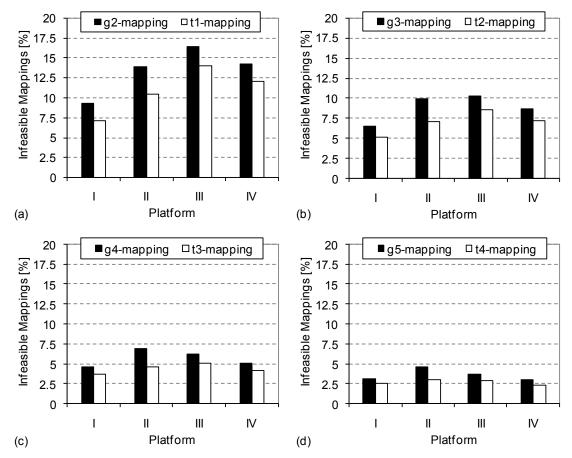

|   |     | 5.3.2 Simulation Results                                |    |

|   | 5.4 | Summary                                                 | 81 |

| 6 | Con | nputing Resource Management Analyses                    |    |

|   | 6.1 | Introduction                                            |    |

|   |     |                                                         |    |

|   | 6.2  | Mapping Order                                     |     |  |  |

|---|------|---------------------------------------------------|-----|--|--|

|   |      | 6.2.1 Motivation and Scope                        |     |  |  |

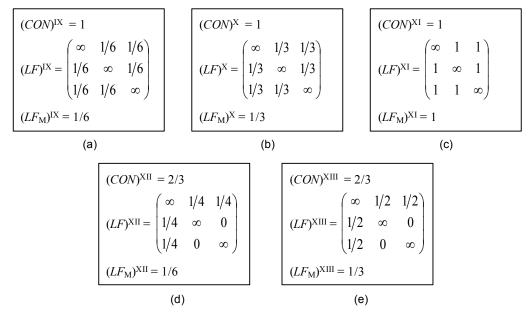

|   |      | 6.2.2 Modeling Support                            | 84  |  |  |

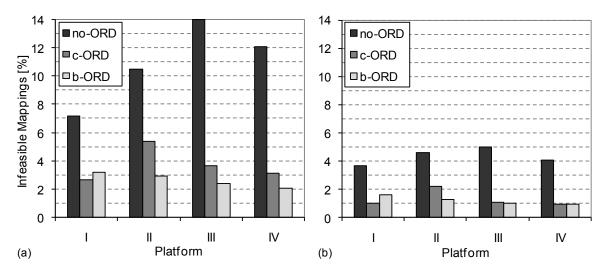

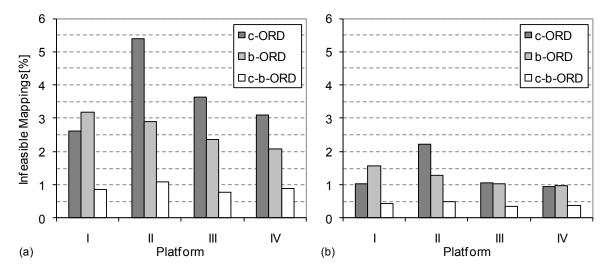

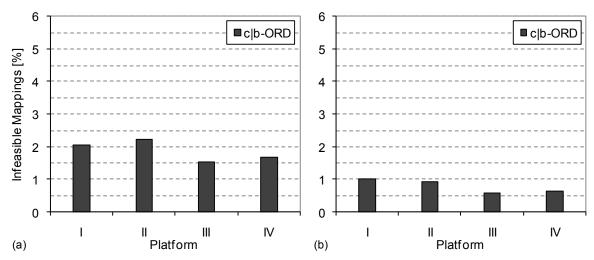

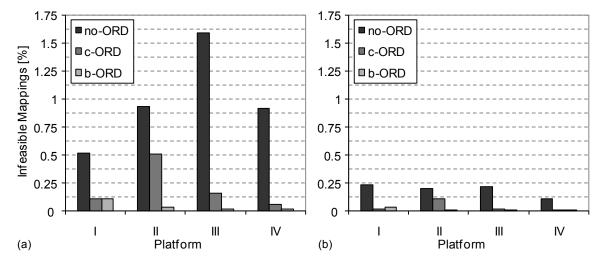

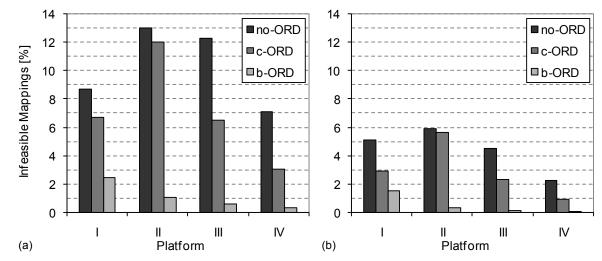

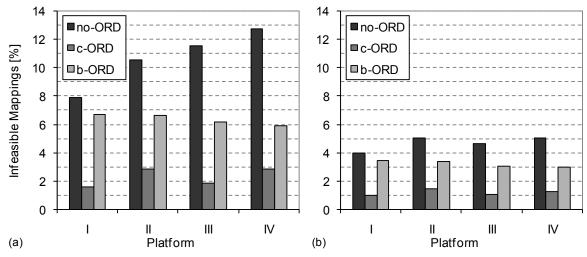

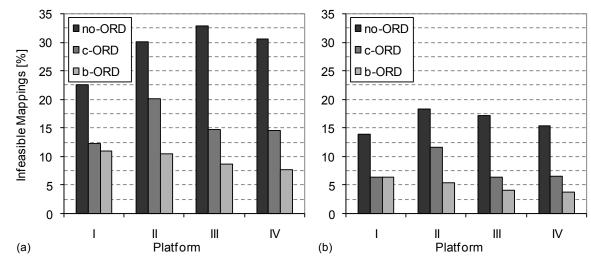

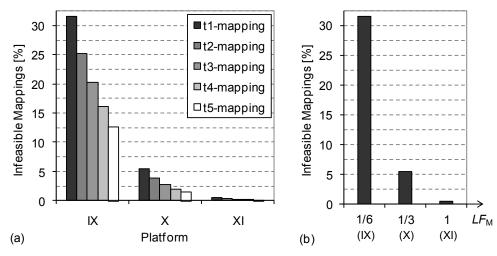

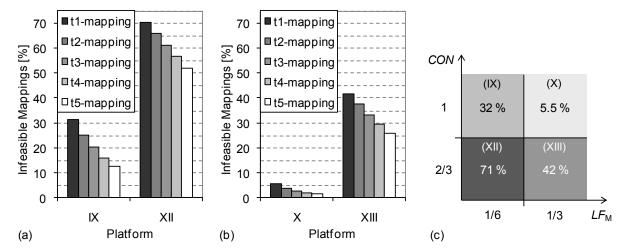

|   |      | 6.2.3 Scenario and Results, Part I                | 85  |  |  |

|   |      | 6.2.4 Scenario and Results, Part II               |     |  |  |

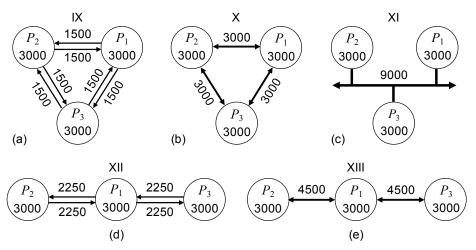

|   | 6.3  | Hardware Architecture                             |     |  |  |

|   |      | 6.3.1 Motivation and Scope                        |     |  |  |

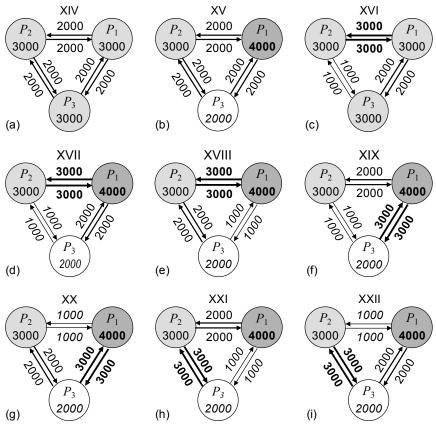

|   |      | 6.3.2 Connectivity and Communication Flexibility  |     |  |  |

|   |      | 6.3.3 Distribution of Computing Resources         |     |  |  |

|   | 6.4  | Window Size versus Cost Function Parameter        | 96  |  |  |

|   |      | 6.4.1 Motivation and Scope                        | 96  |  |  |

|   |      | 6.4.2 Scenario and Methods                        | 97  |  |  |

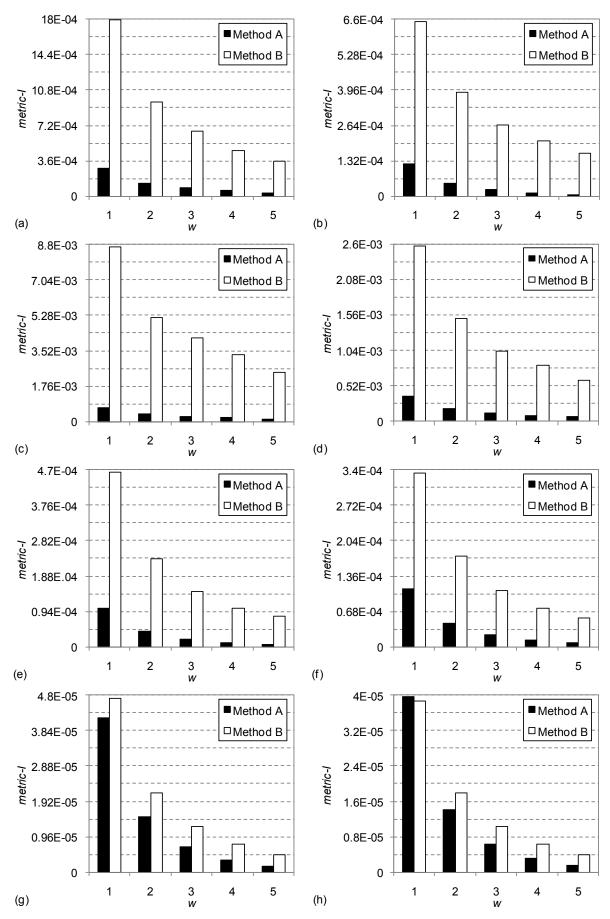

|   |      | 6.4.3 Simulation Results                          | 97  |  |  |

|   |      | 6.4.4 Performance versus Complexity Analysis      | 97  |  |  |

|   | 6.5  | Summary                                           |     |  |  |

| 7 | Car  | mutin a Descurse Management in Cognitive Dedia    | 102 |  |  |

| 7 |      | nputing Resource Management in Cognitive Radio    |     |  |  |

|   | 7.1  | Introduction                                      |     |  |  |

|   | 7.2  | Related Work                                      |     |  |  |

|   | 7.3  | Cognitive Computing Resource Management           |     |  |  |

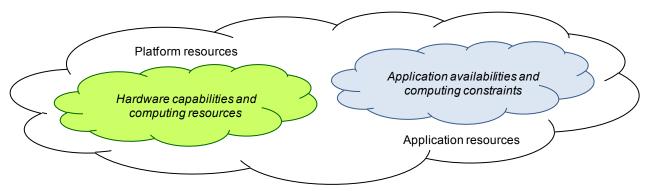

|   |      | 7.3.1 Extended Computing Environment              |     |  |  |

|   |      | 7.3.2 Extended Cognitive Radio System             |     |  |  |

|   |      | 7.3.3 Cognitive Computing Cycle                   |     |  |  |

|   |      | 7.3.4 Computing System Modeling                   |     |  |  |

|   | 7.4  | Proof of Concept                                  |     |  |  |

|   |      | 7.4.1 Basic Scenarios                             |     |  |  |

|   |      | 7.4.2 Simulations                                 |     |  |  |

|   | 7.5  | Summary                                           | 116 |  |  |

| 8 | Join | t Resource Management for Cognitive Radios        | 117 |  |  |

|   | 8.1  | Introduction                                      | 117 |  |  |

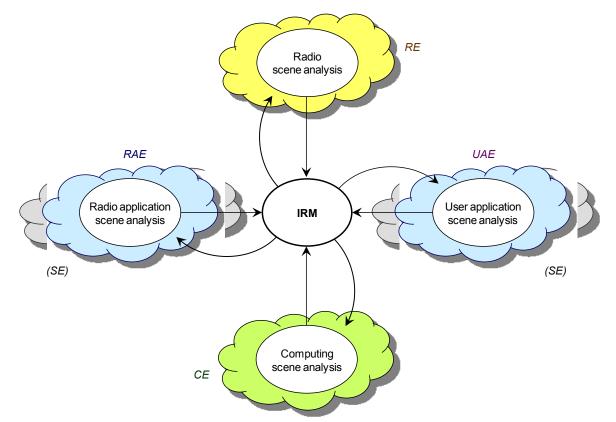

|   | 8.2  | Environments and Resources                        | 118 |  |  |

|   | 8.3  | Cooperative versus Integrated Resource Management | 119 |  |  |

|   | 8.4  | 8.4 Cognitive Cycles                              |     |  |  |

|   |      | 8.4.1 Radio Cycle                                 | 121 |  |  |

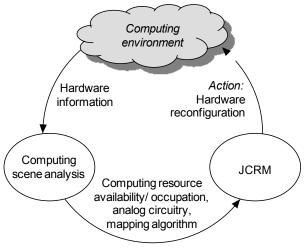

|   |      | 8.4.2 Computing Cycle                             |     |  |  |

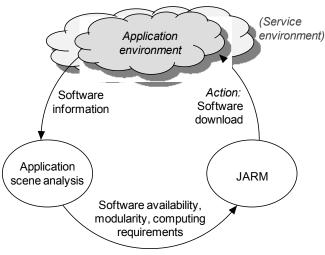

|   |      | 8.4.3 Application Cycle                           |     |  |  |

|   |      | 8.4.4 Joint Resource Management Implications      | 124 |  |  |

|   | 8.5  | Proof of Concept                                  |     |  |  |

|   |      | 8.5.1 Discussion                                  |     |  |  |

|   |      | 8.5.2 Simulations                                 |     |  |  |

|   | 8.6  | Summary                                           |     |  |  |

# CONTENTS

| 9  | Conclusions      | 131 |

|----|------------------|-----|

|    | 9.1 Contribution |     |

|    | 9.2 Future Work  | 132 |

| Re | eferences        | 133 |

# Abbreviations

| 2G    | Second generation wireless systems          |

|-------|---------------------------------------------|

| 3G    | Third generation wireless systems           |

| 3GPP  | 3rd Generation Partnership Project          |

| 4G    | Fourth generation wireless systems          |

| ADC   | Analog-to-digital converter                 |

| AE    | Application environment                     |

| ALOE  | Abstraction layer and operating environment |

| API   | Application programming interface           |

| ASIC  | Application-specific integrated circuit     |

| B3G   | Beyond 3G                                   |

| BER   | Bit error rate                              |

| BSLA  | Baseline algorithm                          |

| CCC   | Communication-to-computation correlation    |

| CCR   | Communication-to-computation ratio          |

| CE    | Computing environment                       |

| CF    | Core framework                              |

| COMM  | Communication                               |

| COMP  | Computation                                 |

| CORBA | Common object request broker architecture   |

| COTS  | Common of-the-shelf                         |

| СР    | Control processor                           |

| CPU   | Central processing unit                     |

| CRC   | Cyclic redundancy check                     |

| CRM   | Computing resource management               |

| CRRM  | Common radio resource management            |

| CU    | Computing unit                              |

| DAC   | Digital-to-analog converter                 |

| DAG   | Directed acyclic graph                      |

| DCA   | Dynamic channel allocation                  |

| DCP   | Dynamic critical-path                       |

| DLS   | Dynamic level scheduling                    |

| DPS   | Dynamic priority scheduling                 |

| DSA   | Dynamic spectrum allocation                 |

| DSP   | Digital signal processor                    |

| ЕТ    | Execution time                              |

| FD    | Full-duplex                                 |

| FFT   | Fast Fourier Transform                      |

| FIFO  | First-in-first-out                          |

| FISC  | Flexible integrated system capability       |

|       |                                             |

| FlowNote         | Flovible wireless systems and networks                                  |

|------------------|-------------------------------------------------------------------------|

| FlexNets<br>FPGA | Flexible wireless systems and networks<br>Field-programmable gate array |

| GB               | Gigabyte                                                                |

| GPP              | General-purpose processor                                               |

| GPRS             | General packet radio system                                             |

| GSM              | Global system for mobile communications                                 |

| HD               | Half-duplex                                                             |

| HIPERLAN         | High performance radio LAN                                              |

| HLFET            | Highest level first with estimated times                                |

| HSDPA            | High speed downlink packet access                                       |

| IDL              | Interface definition language                                           |

| IEEE             | Institute of electrical and electronics engineers                       |

| IF               | Intermediate frequency                                                  |

| IRM              | Integrated resource management                                          |

| IRMA             | Integrated resource management algorithm                                |

| ITU              | International Telecommunication Union                                   |

| JARM             | Joint application resource management                                   |

| JCRM             | Joint computing resource management                                     |

| JRARM            | Joint radio application resource management                             |

| JRRM             | Joint radio resource management                                         |

| JUARM            | Joint user application resource management                              |

| JTRS             | Joint Tactical Radio System                                             |

| kbps<br>KUAR     | Kilo bits per second<br>Kansas University Agile Radio                   |

| LAN              | Local area network                                                      |

| LGDF             | Large grain data flow                                                   |

| MAIL             | Maximum allowable increase in load                                      |

| MAC              | Multiply accumulate (operation)                                         |

| MB               | Megabyte                                                                |

| Mbps             | Mega bits per second                                                    |

| MBPTS            | Megabits per time slot                                                  |

| МСР              | Modified critical path                                                  |

| MOPS             | Million operations per second                                           |

| MOPTS            | Million operations per time slot                                        |

| MPRG             | Mobile and Portable Radio Research Group                                |

| MP-SoC           | Multiprocessor system on a chip                                         |

| MT               | Mobile terminal                                                         |

| mWPS             | Milliwatt per second                                                    |

| NoC              | Network on a chip                                                       |

| Node B           | 3GPP term for a base station                                            |

| NP               | Nondeterministic polynomial time                                        |

| OE<br>OFDM       | Operating environment<br>Orthogonal frequency division multiplexing     |

| ONG              | Object management group                                                 |

| ORB              | Object request broker                                                   |

| OS               | Operating system                                                        |

| OSI              | Open system interconnection                                             |

| OSSIE            | Open source SCA implementation embedded                                 |

| PE               | Processing element                                                      |

| PHAL             | Platform and hardware abstraction layer                                 |

| P-HAL-OE         | PHAL operating environment                                              |

| POSIX            | Portable operating system interface                                     |

| P-SCH            | Primary synchronization channel                                         |

| QoS              | Quality of service                                                      |

| Q-SCA            | QoS-enabled SCA                                                         |

| RAE              | Radio application environment                                           |

| RAN              | Radio access network                                                    |

| RARM             | Radio application resource management                                   |

| RAT              | Radio access technology                                                 |

| RE               | Radio environment                                                       |

| RF<br>RKRL<br>RRM | Radio frequency<br>Radio Knowledge Representation Language<br>Radio resource management |

|-------------------|-----------------------------------------------------------------------------------------|

| RT-CORBA          | Real-time CORBA                                                                         |

| RTOS              | Real-time operating system                                                              |

| SAD               | Software assembly descriptor                                                            |

| SCA               | Software communications architecture                                                    |

| SCD               | Software component descriptor                                                           |

| SE                | Service environment                                                                     |

| SDF               | Synchronous data flow                                                                   |

| SDR               | Software-defined radio                                                                  |

| SDR-BS            | SDR base station                                                                        |

| SDR-MT            | SDR mobile terminal                                                                     |

| SNR               | Signal-to-noise ratio                                                                   |

| SoC               | System on a chip                                                                        |

| SPD               | Software package descriptor                                                             |

| SPTS              | Seconds per time slot                                                                   |

| TANH              | TDS algorithm for network of heterogeneous systems                                      |

| TDS               | Task duplication based scheduling                                                       |

| TS                | Time slot                                                                               |

| UAE               | User application environment                                                            |

| UARM              | User application resource management                                                    |

| UE                | User equipment                                                                          |

| UMTS              | Universal mobile telecommunications system                                              |

| USB               | Universal serial bus                                                                    |

| USRP              | Universal Software Radio Peripheral                                                     |

| UTRAN             | UMTS terrestrial radio access network                                                   |

| VM                | Virtual machine                                                                         |

| WiMAX             | Worldwide interoperability for microwave access                                         |

| WCDMA             | Wideband code division multiple access                                                  |

| WLAN              | Wireless local area network                                                             |

| WPAN              | Wireless personal area network                                                          |

| XML               | Extensible markup language                                                              |

|                   |                                                                                         |

# Introduction

# 1.1 Modern Radio Communications

Except for the word *radio* in *radio communications*, today's wireless communications have little in common with the radio introduced by Marconi more than a century ago. Wireless communications are nowadays part of our professional and private life. Their manifold utility ranges from providing basic communications services to interactive multimedia entertainment. Universities and companies, including telecommunications specialist as well as computer scientists, steadily strive for evolving wireless communications. We approach a wireless world that, in many senses, increases our quality of life.

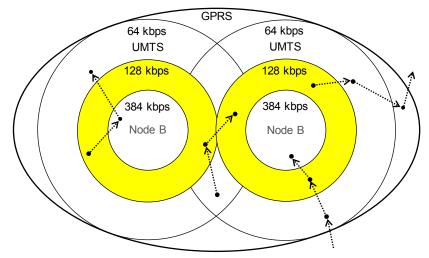

The coexistence of radio access technologies (RATs) characterizes modern wireless communications. The emerging 3G systems, for example, neither pretend to substitute the worldwide available access to 2G services nor directly compete with wireless local or personal area networks (WLANs or WPANs). These RATs rather complement each other: 2G systems, such as the global system for mobile communications (GSM) and the general packet radio system (GPRS), offer worldwide roaming for carrying voice traffic and low-volume data. 3G systems—the universal mobile telecommunication system (UMTS) and its American and Asian predecessors or derivatives—offer higher data rates for many classes of (multimedia) services. WLANs locally offer very high data rates at lower cost for accessing global information, whereas WPANs wirelessly interconnect personal devices. This view of cooperative rather than competitive radio access networks (RANs) facilitates providing personalized services and a ubiquitous wireless access [1].

Beyond 3G (B3G) is the common term that describes today's coexistence of RATs. It characterizes a heterogeneous radio environment where the user, and not the radio, takes the central stage. That is, the traditionally RAT-driven wireless communications become service-driven and personalized wireless communications with quality of service (QoS) differentiations. As RATs evolve over time, today's state-of-the-art RATs may become obsolete some day. The trend, however, indicates that only few RATs will actually be replaced so that the radio environment will remain or become even more heterogeneous.

The latest radio standards increase the spectral efficiency and facilitate a more flexible use of radio resources. UMTS, for example, allows for more flexible channel allocations than 2G systems. This makes variable data rates and bandwidth-on-demand possible. Streams with different bit rates can, moreover, be multiplexed and transmitted together. Flexible bit rates efficiently support multimedia applications, possibly consisting of voice, video, and file transfer components [11]. The high speed downlink packet access (HSDPA) and the worldwide interoperability for microwave access (WiMAX), the successors of UMTS and WLAN, add additional features for increasing the spectral efficiency and service diversity.

As new radio standards emerge, the radio operators desire reusing existing radio infrastructure. Similarly, the introduction of a new user service cannot imply the need for a new mobile terminal. Designing multipurpose infrastructure and mobile terminals for integrating existing and future radio standards is challenging. Multimode hardware designs may be economically feasible today, but will soon become obsolete because of their limited flexibility. A software solution should then be considered, where software at least partly defines the radio transmission and reception modes of radio equipment. This is known as software-defined radio (SDR). Apart from the flexibility of using one or another air interface and providing one or another service, SDR facilitates infrastructure or hardware upgrades and signal processing or software updates.

SDR introduces flexibility to wireless communications, whereas cognitive radio adds intelligence. Cognitive radio facilitates a situation dependent allocation and use of resources for wireless communications. It can automate the reconfiguration process of SDR equipment for optimally using the available resources at a given place and time. SDR and cognitive radio together offer the required flexibility and intelligence for the personalized and omnipresent service provisioning. The rest of this chapter briefly reviews both concepts and indicates the current SDR and cognitive radio research, focusing on resource management.

# **1.2 Software-Defined Radio**

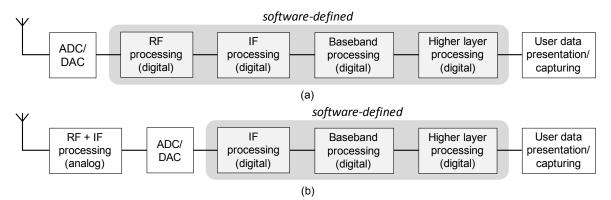

In the early 90s Mitola envisaged radio transmitters and receivers (transceivers) that implement the entire signal processing chain in software (Fig. 1.1a). He coined this vision *software radio* [3], [4]. Software radio describes multistandard, multiservice, and multiband radio systems, which are software-reconfigurable or reprogrammable. It promises to become a pragmatic solution to the variety of available and incompatible radio standards [6]. The technological difficulty for digitalizing radio frequency (RF) signals [7], [8], [9] led to the introduction of SDR [10]. SDR may be considered as a generalization of software radio. It characterizes a transceiver that implements one or more signal processing blocks in software. Since digitalization usually takes place at the intermediate frequency (IF) stage (Fig. 1.1b), part of the IF, baseband, and higher layer processing can then be implemented in software [11].

SDR introduces flexibility to wireless systems: It permits adjusting or switching a terminal's RAT implementation for adapting to changes in the heterogeneous radio environment. As opposed to traditional radio communications, the software that runs on an SDR platform defines its radio functionality. SDR platform stands for a software-programmable computing equipment, including handset transceivers, base stations, and core networks. SDR application or waveform refers to (part of) a RAT-specific digital signal processing chain. Reconfiguring an SDR platform to execute another SDR application could then change the deployed radio standard for establishing a radio communications link. Dynamic RAT switches or modifications during communications sessions are also envisaged.

For about a decade, SDR-related research along the whole line between the mobile terminal transceiver and the core network has been ongoing [12], [13], [14], [15]. It is motivated by the evolution of information technology: The introduction of new RATs, such as UMTS or the IEEE 802.11 family of WLANs, the required compatibility with the existing RATs, including GSM and GPRS, and the increasing demand for new and differentiated user services call for flexible transceiver solutions. Therefore, the flexibility of general purpose processors (GPPs), digital signal processors (DSPs), field-programmable gate arrays (FPGAs), picoArrays [25], networks on a chip (NoCs) [26], or multiprocessor systems on a chip (MP-SoCs) [27] is becoming more important than the energy efficiency of application-specific integrated circuits (ASICs) [28], [29], [30]. Today's reconfigurable devices offer high computing capacities at moderate

Fig. 1.1. Conceptual software radio (a) and software-defined radio (b) transceivers.

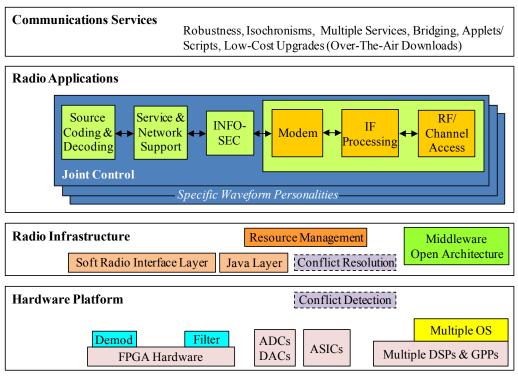

Fig. 1.2. Layered software radio architecture [5].

power consumptions. As a result, we observe a tendency of expanding the digital and reconfigurable radio part while reducing the analog and nonreconfigurable circuits.

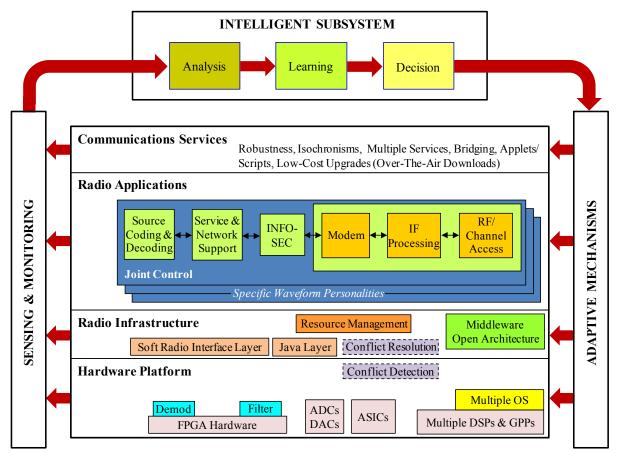

Fig. 1.2 shows Mitola's *layered software radio architecture* [5]. It does not specify a particular SDR implementation, but, rather, a general framework for SDR communications. Its four layers are independent to some extent. The *communications services* range from simple phone calls to interactive multimedia services. They are steadily redefined or extended as a function of user demands and market success. *Radio applications* stand for SDR applications or waveforms. They define the signal processing and overthe-air transmission modes for adequate service and QoS provisioning. The *radio infrastructure* is the abstract execution environment for radio applications. It may feature middlewares, virtual machines (VMs), resource managers, and conflict solvers. The *hardware platform* typically consists of a set of heterogeneous processors, data converters, and operating systems (OSs).

The figure indicates that radio applications and hardware platforms are heterogeneous. That is, a radio application consists of several modules that provide different functionalities. These modules assemble the waveform, but each one of them may be more or less complex and, thus, require more or less computing resources. Hardware platforms correspondingly consist of different types of processing elements (PEs), ranging from ASICs to GPPs. To flexibly support dynamic software and hardware environments, the resource management module needs to be independent from a particular radio application and from a certain hardware platform. It is therefore located within the platform and application-independent radio infrastructure (Fig. 1.2).

# **1.3 Cognitive Radio**

In the late 90s and less than a decade after introducing software radio, Mitola coined *cognitive radio* [114]. His dissertation [115] initiated worldwide cognitive radio research [116], [117], [118], [119] and led to many different interpretations of the cognitive radio concept. A cognitive radio system is commonly considered as an intelligent wireless communication system aiming at the efficient usage of radio resources [116], [118]. It is, however, a much broader and more powerful concept [115], [133]. Mitola defines it as "a goal-driven framework in which the radio autonomously observes the radio environment, infers contexts, assesses alternatives, generates plans, supervises multimedia services, and learns from its mistakes" [137]. We suggest the following, similar definition:

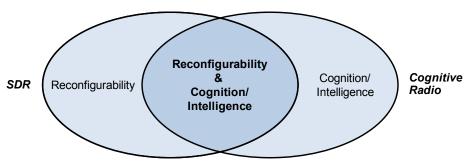

Fig. 1.3. Software-defined versus cognitive radio.

# **Definition 1** A cognitive radio system is an ambient-aware wireless communications system that can intelligently adjust itself to its operating environment. The system can particularly modify the radio transmission modes or parameters as a function of the resource availabilities, end-to-end QoS requirements, business models, or the like.

Cognitive radio evolved from SDR [137] although it does not necessarily require a reconfigurable hardware environment (Fig. 1.3). Multimode radio terminals, whose reconfiguration capabilities are limited to mode switches between a limited set of modes, are apt for cognitive radios. The flexibility of software implementations, however, increases the potential of environmentally stimulated radio adjustments: Cognitive radio can, as an intelligent management layer on top of an SDR system, automate and optimize the reconfiguration of SDR equipment. It is *the* application for SDRs.

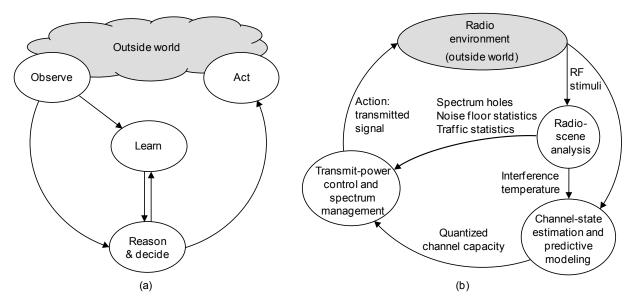

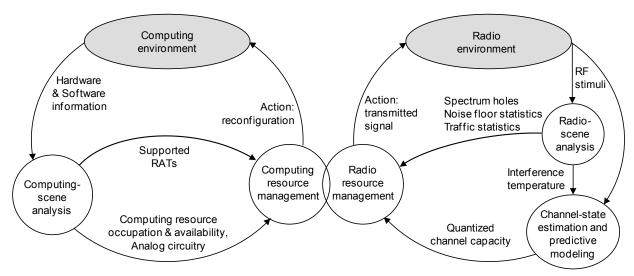

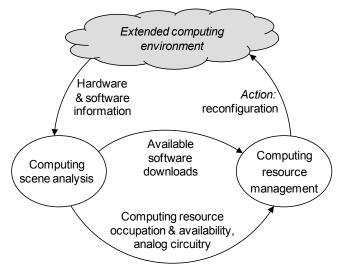

Fig. 1.4a sketches a simplified interpretation of Mitola's cognition cycle [114], [137]. It consists of the *observe, reason and decide, learn*, and *act* phases. The environment is observed and analyzed. Decisions are made as a function of these observations and the available knowledge. These decisions are executed and evaluated. This observe-think-act cycle runs continuously. The system gains experience during operation. The general objective is optimizing the use of resources for wireless communications at any time while satisfying the users' service requests and increasing the operators' revenues. Cognitive radio can take advantage of the versatility of the B3G context.

Haykin [116] concretizes Mitola's cognition cycle, considering it for solving radio resource management (RRM) issues. The *basic cognitive cycle* of Fig. 1.4b essentially consists of the *radio-scene analysis* and the *channel-state estimation and predictive modeling* blocks, which process the RF stimuli for the *transmit-power control and spectrum management*. The corresponding actions may affect the radio environment and lead to new RF stimuli [116].

# **1.4 Resource Management in SDR and Cognitive Radio**

Resource management is an important topic of SDR and cognitive radio research. This Section provides a brief overview of some advanced RRM techniques, which are investigated in cognitive radio. We then discuss the need for computing resource management in software-defined and cognitive radios. After examining the related work, we present our resource management outlook as a motivation for this dissertation. We, particularly, indicate some challenges and possibilities of our research and its possible impact on future radio communications as a whole.

## 1.4.1 Radio Resource Management

Spectrum for radio communications is a limited physical resource. Physical and technological limits restrain the RF carriers to frequencies that range from approximately 0.25 MHz to 6 GHz [137], although the use of higher frequencies is recently explored. The steadily growing bandwidth demand thus creates contention for radio spectrum, a precious radio resource. Spectrum is internationally regulated by the ITU and nationally by governmental agencies [120], [121]. It has traditionally been leased to operators, gaining them exclusive rights to spectrum portions for specific usage. The operators are responsible for efficiently using the acquired radio resources while complying with the specifications imposed by the regulation bodies.

Fig. 1.4. Simplified cognition cycle (a) and Haykin's [116] basic cognitive cycle (b).

RRM is an essential topic in modern wireless communications, which leverage diversity and flexibility and facilitate a higher spectral efficiency. Spectral efficiency is related to system capacity and revenues. This explains the importance of an efficient usage of radio resources.

The basic RRM concept, where each operator manages the radio resources individually for each RAT, has been extended with the introduction of 3G and its coexistence with other radio standards. Common or joint RRM (CRRM or JRRM), for example, refers to the management of radio resources pertaining to different RATs of a single operator [132], whereas dynamic spectrum access implies a more flexible spectrum allocation and management [133]. These techniques are widely investigated in the 3G, B3G, and cognitive radio contexts. We sketch them below.

#### *A) RRM in 3G and B3G*

The spectrum auctions for UMTS licenses in Europe have revealed the importance of RRM. (UMTS is the most widely adopted 3G system, which is standardized by the 3GPP [2].) As opposed to 2G systems, the UMTS terrestrial radio access network (UTRAN) can achieve higher spectral efficiencies through advanced coding and multiple access techniques, diversity schemes, and so forth. The wideband code division multiple access (WCDMA) technique, which UTRAN employs, implicitly calls for interference or radio resource management, because many users concurrently transmit over the same frequency channel with possibly different data rates. Manufacturers then have to introduce more sophisticated RRM strategies than those that were used in the past. Service differentiations, the QoS concept, and the possibility of dynamically adapting the resource allocations to the given channel conditions make RRM more powerful but also more challenging [122].

We have already mentioned that the usable spectrum for wireless communications is rigorously divided into frequency bands, which are assigned to different user groups for specific usage. The UMTS spectrum auctions followed this concept. Despite the fixed frequency allocations, a UMTS operator needs to manage various transmission bands and other related radio resources, such as transmission power.

The coexistence of radio standards in B3G leverages the flexibility of choosing a RAT while introducing new RRM challenges. The major challenge consists in introducing advanced RRM strategies or algorithms that operate from a common rather than technology or operator-driven perspective. The sporadic and geographically varying use of spectrum, with some frequency bands being more heavily used than others [142], further argues for inter-frequency and inter-operator RRM.

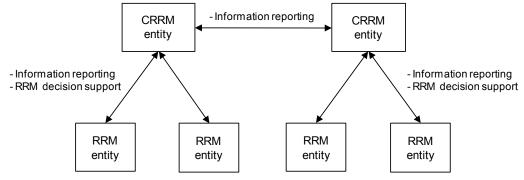

CRRM or JRRM refers to the management of radio resources of various RATs of a single operator. The CRRM entity therefore coordinates the use of radio resources of different RATs (Fig. 1.5). The 3GPP suggests dividing the radio resources that pertain to an operator into radio resource pools. A radio resource pool contains the available radio resources that pertain to a single RAT within a set of cells. An RRM entity of Fig. 1.5 manages the radio resources of one radio resource pool, whereas the CRRM entity coordinates the management of several resource pools [132].

Fig. 1.5. CRRM functional model [132].

#### B) Dynamic Spectrum Access

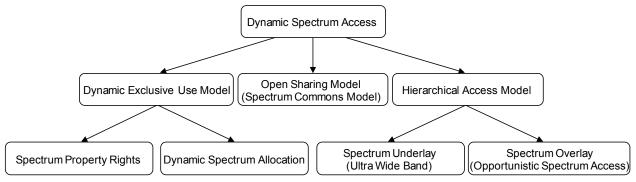

*Dynamic spectrum access* stands for the opposite of the current spectrum regulation and management policies. Zhao and Sadler [133] try to capture its broad significance, providing a taxonomy of dynamic spectrum access, which Fig. 1.6 reproduces. The *dynamic exclusive use model* assumes the fixed spectrum regulation structure that we have today. It though allows to sell and trade spectrum and to freely choose technology (*spectrum property rights* [134]) or to dynamically assign spectrum by exploiting the spatial and temporal traffic statistics of different services (*dynamic spectrum allocation* [135]). The *open sharing* or *spectrum commons model* refers to sharing spectral regions among peer users [136]. The *hierarchical access model* adopts a hierarchical access structure with primary and secondary users. It allows secondary users to access licensed spectrum while not affecting primary user communications. Secondary users can either transmit below the noise floor of primary users (*spectrum underlay*) or occupy temporally unoccupied spectrum (*spectrum overlay*).

Despite these differentiations, the above concepts are closely related. The dynamic spectrum allocation (DSA) and spectrum overlay techniques, for example, try to assign spectrum portions that are momentarily unused (spectrum holes or white spaces) to primary and secondary users, respectively. These methods are appropriate for cognitive radios and are briefly discusses in continuation.

#### **Dynamic Spectrum Allocation**

While a static spectrum allocation, which is simple to regulate and manage, was appropriate for wireless communications in the past, it is inefficient for modern wireless communications: The traditionally independent RANs are merging into composite radio networks, basic communication services are replaced by advanced and personalized multimedia services, and a steadily increasing number of users desire an any-where and anytime wireless connectivity. The time and regional variations of the service and traffic demands reflect another shortcoming of a fixed spectrum allocation. DSA was introduced to overcome these and other inefficiencies and to exploit the potentials of wireless technology [126].

DSA covers a range of research fields, such as *dynamic channel allocation* (DCA), *frequency assignment, unlicensed spectrum access*, and *spectrum coexistence*. DCA refers to sharing the radio resources of a single RAN [127], whereas frequency assignments are mostly related to assigning frequencies to base stations as a function of the interference and coexistence constrains [128]. The unlicensed spectrum access approach treats spectrum as an open source that any conforming equipment can use [129]. Spectrum coexistence finally implies different networks using the same frequency bands, such as digital and analog TV.

Fig. 1.6. A taxonomy of dynamic spectrum access [133].

| Band     | RF <sub>min</sub> (MHz) | RF <sub>max</sub> (MHz) | W <sub>c</sub> | Remarks                         |

|----------|-------------------------|-------------------------|----------------|---------------------------------|

| Very Low | 26.9                    | 399.9                   | 315.21         | Long range vehicular traffic    |

| Low      | 404                     | 960                     | 533.5          | Cellular                        |

| Mid      | 1390                    | 2483                    | 930            | Personal communication services |

| High     | 2483                    | 5900                    | 1068.5         | Indoor and RF LANs              |

**Table 1.1**Mobile spectrum pools [137].

DSA is more general than DCA and frequency planning but more organized than the unlicensed access or coexistence methods. It aims at a dynamic spectrum allocation across RANs, facilitating spectrum sharing over space and time. More precisely, the DSA establishes that spectrum is locally and exclusively allocated to services for a limited time. Spectrum can then be allocated as needed, increasing the overall spectral efficiency.

*Contiguous* and *fragmented DSA* are studied as two practical implementations of DSA, where guard bands separate the spectrum blocks allocated to different RANs [126]. Contiguous DSA implies that, to allocate more bandwidth to one RAN, its spectral neighbors need to release bandwidth. In the fragmented DSA scenario, on the other hand, RANs can occupy any available spectrum hole.

#### **Spectrum Pooling**

An opportunistic spectrum access (OSA) includes the opportunity identification, its exploitation and regulation. The opportunity identification process recognizes underused spectrum bands. The opportunity exploitation process then decides if and how the transmission should occur in these bands following some regulation policy, which defines the basic etiquette for secondary users to ensure compatibility with legacy systems. The radio etiquette would, for example, specify that secondary users change bands when primary users enter the bands. The overall objective is exploiting spectrum silent times (in which spectrum portions are underexplored or idle) for secondary usage while protecting primary users and their privilege to access radio resource whenever desired [133].

Spectrum pooling is an OSA technique that was introduced by Mitola [137] and explored by Weiss and Jondral [131]. It refers to short-time spectrum leases that are managed by the cognitive radio itself and priced by the market. Therefore, spectral ranges from different owners are merged into a common pool. Mitola [137] suggested the four spectrum pools of Table 1.1, where  $W_c$  is the total bandwidth that could participate in the spectrum pool excluding those bands that are not suitable for pooling, such as satellite, aircraft, and radio navigation bands.

Weiss and Jondral [131] identify OFDM as a candidate modulation for spectrum pooling, because it eases the realization of spectral coexistence between primary and secondary users. In OFDM, a high-rate data stream is divided into multiple low-rate substreams, each modulated on a single subcarrier. Through proper subcarrier spacing, precise synchronization, and rectangular pulse shaping, subcarriers are orthogonal to one another [139]. This facilitates flexible and dynamic allocations of spectrum holes of different bandwidths.

Spectrum pooling as well as other dynamic spectrum access techniques pragmatically approaches a more efficient use of spectrum. The corresponding research results show the advantages of a dynamic spectrum regulation, which is currently evaluated by the regulation authorities. In the long term, this may lead to an open spectrum access [140].

## 1.4.2 Computing Resource Management

Computing resource management is not a traditional radio communications issue. Traditional radios are designed for accessing a single or a few air interfaces or channels. During the design time of a *hardware-defined radio*, computing resources are assigned to perform specific tasks. During operation, there is little or no need for computing resource management. This is different in SDR, where some computing resources, demapping one software piece and mapping another. This implicitly calls for computing resource management.

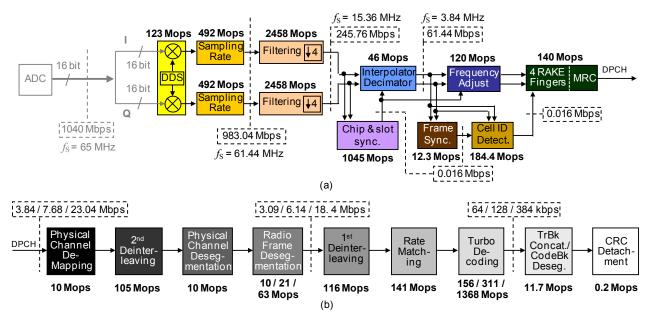

SDR facilitates the independent design of software and hardware for wireless communications. Sophisticated real-time services, high data rates, and complex signal processing algorithms entail elevated computing requirements. Software-defined UMTS transceiver implementations, in particular, require high amounts of memory and processing resources [11], [17]. Multiprocessor execution environments are therefore envisaged for executing even a single-user SDR transceiver [9], [17].

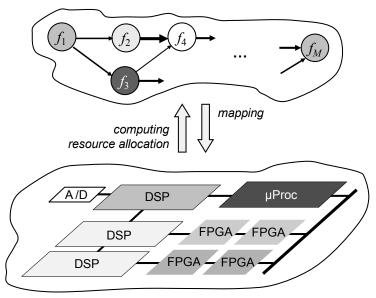

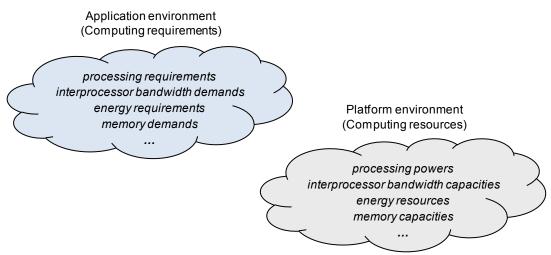

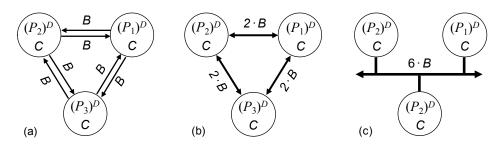

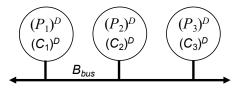

Multiprocessing is a timely research topic and several recent industry success examples, such as the picoArray [31] and the Cell multiprocessor [32], indicate the trend in processing technology for, but not limited to, wireless communications. The modules of an SDR application—essentially the digital signal processing blocks and the data flows between them—then need to be mapped to the distributed and limited computing resources of heterogeneous multiprocessor platforms (Fig. 1.7).

# A) Related Work

Several radio standards have been at least partly implemented in software and executed on generalpurpose hardware. SDR research has also addressed the partitioning of waveforms for their distributed execution on multiprocessor platforms. Most of these efforts address the mapping of a specific waveform to a particular platform, including the mapping of

- an OFDM baseband processing implementation to a multiprocessor platform [98],

- an OFDM receiver to a MP-SoC [99],

- a WCDMA receiver to a DSP with attached reconfigurable logic [100],

- a HIPERLAN/2 implementation to the MONTIUM processor tile [101],

- a UMTS base station to four PC101 picoArrays using 740 processors [25], and

- the H.264 encoding algorithm to the Cell multiprocessor [102].

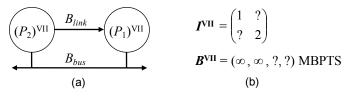

Rhiemeier's dissertation [54], on the other hand, studies the processor allocation problem from a rather general perspective. He applies operational research techniques to partition task graphs, which represent waveforms, for their scheduling on a multiprocessor platform. He considers a platform that consists of two identical DSPs connected through a bidirectional bus for studying the implications of bus bandwidth and partitioning algorithm on the execution time of waveforms [53], [54].

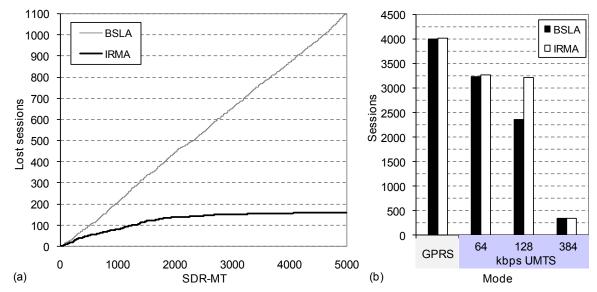

Current cognitive radio research focuses on RRM. Computing resource management has not been addressed in this context. Mitola [115], though, talks about self-awareness and introduces a high-level computational model that the system has of itself. The model provides the means for representing the types of processors and their capacities, among others. This information is used for controlling the execution time of the cognition cycle and for detecting software-software and software-hardware incompatibilities [115], although it could be used for computing resource management. Jondral [119] considers the "awareness of processing capabilities for the partitioning or the scheduling of processes" as a technology centric property of cognitive radios. Chapters 2 and 7 examine further related work on computing resource management in SDR and cognitive radio, respectively.

Fig. 1.7. Mapping versus computing resource management.

#### B) Outlook

The hard real-time computing constraints of SDR applications have implications on the design of SDR platforms and applications as well as on SDR middleware, abstraction layers, and computing resource management solutions. The first generation of SDR mobile terminals (SDR-MTs) will be limited in computing resources, including battery power, and will probably not be capable of supporting more than one RAT implementation at a time. The flexibility of these terminals will then be function of the capabilities of their reconfiguration managers. The computing resources of SDR base stations (SDR-BSs), on the other hand, will be less limited. Nevertheless, an optimization of computing resources would be highly desirable for reducing the operational cost of SDR-BSs. The potentially large number of users and the platforms' high degrees of flexibility, modularity, and reconfigurability make the computing resource management at SDR-BSs equally important though more complex than that at SDR-MTs.

The software challenges include designing efficient implementations of complex signal processing algorithms [8]. Furthermore, software needs to be portable, which has implications on the software design tools. If SDR software needs to be specifically tailored for each hardware platform, software-hardware but also software-software interoperability issues may arise, compromising flexibility. Many SDR solutions are proprietary and hardware or tool-specific software implementations, such as picoChip's SDR transceiver implementations [25], although open source software for programmable processors exist; GNU Radio [97] being the most popular example.

SDR research addresses these (software and hardware) issues and a few practical SDR execution environments have emerged throughout this decade. Theoretical SDR research has gained less attention. We understand an SDR application as a set of concurrent processes that continuously process and propagate real-time data. Such a processing chain is not specifically tailored, but, rather, executable on any generalpurpose platform with sufficient computing capacity. Because of the similarities between future SDR applications and platforms and today's general-purpose computing applications and platforms, we consider general-purpose computing methods practical for SDR systems. We particularly think that the introduction of appropriate mapping and scheduling techniques will leverage the design of SDR platforms and applications. *Mapping (matching* in heterogeneous computing literature [43]) describes the process of assigning software modules to hardware resources, whereas *scheduling* determines the execution times of these modules. We consider them as two complementary computing resource management methods.

Wireless or SDR systems, however, reveal specific aspects—essentially regarding flexibility and efficiency—which have not been jointly considered so far:

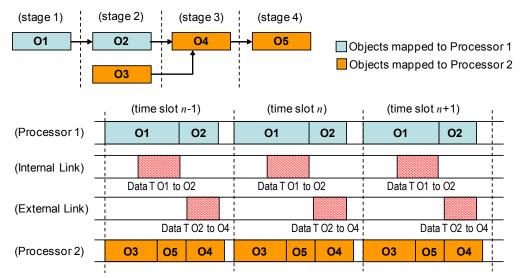

- 1. time slot based division of the transmission medium (radio time slot),

- 2. continuous data transmission and reception [34],

- 3. RAT-specific QoS targets,

- 4. real-time computing requirements and limited computing resources,

- 5. different computing constraints and loads for different RATs or radio conditions,

- 6. dynamic reconfigurations of the protocol stack, either partial or total, and

- 7. heterogeneous multiprocessor platforms.

These characteristics have implications on the design of the radio infrastructure, the interface between SDR applications and platforms. The system's reconfiguration flexibility and efficiency particularly depends on the computing resource management module. This module is the central part of the radio infrastructure, comparable to the central processing unit (CPU) scheduler within an OS. Its capability to dynamically assign computing resources to computing requirements facilitates the introduction of new (communications) services, the spread of advanced signal processing techniques, the incorporation of hardware extensions, and so forth. We therefore think that computing resource management is essential for the breakthrough of SDRs.

The possibility of dynamically reconfiguring an SDR platform provides full flexibility for adapting an SDR application to the momentary radio environment and QoS demands. SDR can thus be considered as a platform for cognitive radio and advanced RRM [124]. This requires extending current computing resources management approaches toward a framework that links the computing with the radio resources. A cognitive radio system that observes (momentarily) low radio traffic may then give a higher importance to

Fig. 1.8. Extended cognitive cycle.

the efficient use of computing resources, reducing the computing complexity and, consequently, power consumption. Similarly, if a non-real-time service would momentarily exhaust a platform's computing capacity, the cognitive radio system could schedule this service at some later time when the limiting conditions change, such as in the event of a battery recharge.

From the above discussion follows that radio resource monitoring and management are not the only issues in cognitive radio. Without the support of computing resources, many advanced RRM techniques cannot be realized. More computing resources are generally required to increase the spectral and transmission power efficiency, in particular. Moreover, future radio communications systems will consider extended models of the entire system and more complex algorithms for reaching higher levels of intelligent management. This evolution calls for more computing resources.

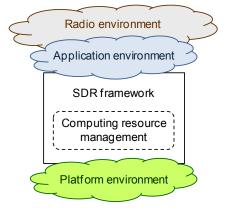

Instead of viewing computing resources and their management as an enabler for cognitive radio, we argue for a cooperative radio and computing resource management. We, therefore, extend the cognitive cycle of Fig. 1.4b, adding another cycle, which monitors and manages the computing resources (Fig. 1.8). This facilitates a synchronized management of the limited radio and computing resources.

Wireless communications is nowadays an integral part of computer engineering (sensor networks and pervasive computing, for example) and computing issues become the more important the further advanced the wireless communications. Our research therefore promotes a higher integration of computing issues in wireless communications and tries to establish the basis for flexible tradeoffs between computing and radio resources.

# **1.5** Contribution and Outline

Our research aims at contributing to the evolution of modern wireless communications and to the development of SDR and cognitive radio, in particular. It promotes a general resource management framework that facilitates the integration of computing and radio resource management. This dissertation discusses the need for computing resource management in software-defined and cognitive radios and introduces an SDR computing resource management framework with cognitive capabilities. The hard real-time computing requirements of SDR applications, the associated radio propagation and QoS implications, and heterogeneous multiprocessor platforms with limited computing resources define the context of these studies.

We examine heterogeneous computing techniques, multiprocessor mapping and scheduling in particular, and elaborate a flexible framework for the dynamic allocation and reallocation of computing resources for wireless communications. The framework should facilitate partial reconfigurations of SDR platforms, dynamic switches between RATs, and service and QoS level adjustments as a function of environmental conditions.

The context of this dissertation is the *platform and hardware abstraction layer operating environment* (P-HAL-OE), a specific SDR framework. An SDR framework behaves like an OS for radio communications. It has access to physical hardware resources and software repositories and provides an execution

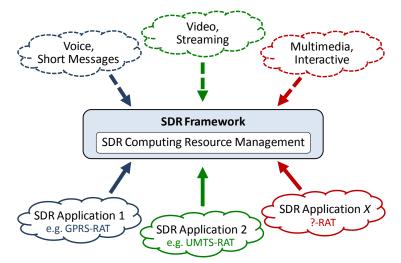

Fig. 1.9. SDR computing resource management context: dynamic mapping of waveforms for a flexible service provisioning.

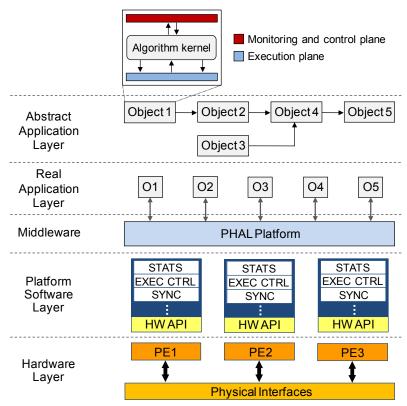

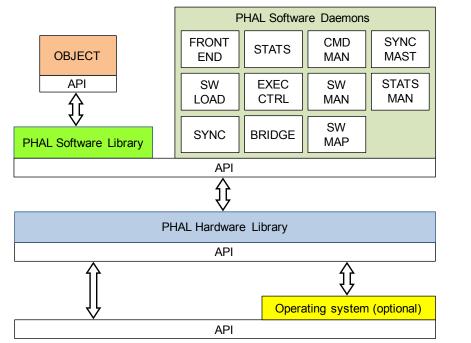

environment for SDR applications (Fig. 1.9). We review some important SDR frameworks and present the main features of the P-HAL-OE. Chapter 2 also specifies the computing resource management problem and examines the related work.

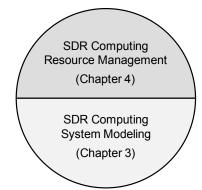

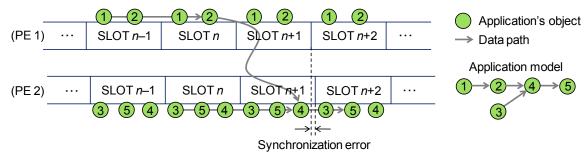

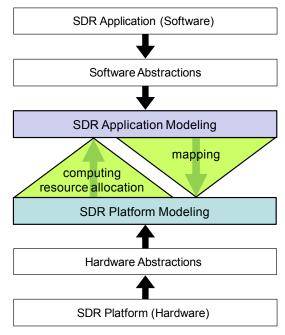

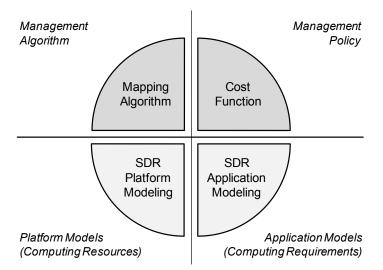

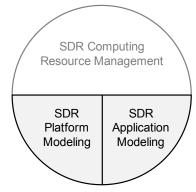

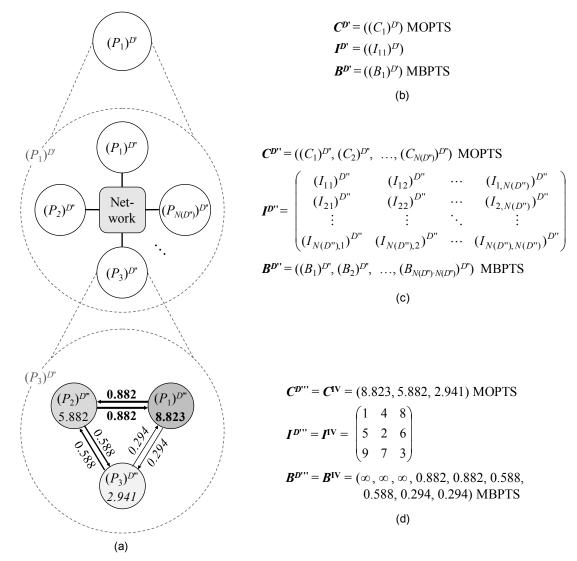

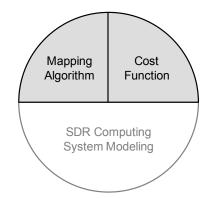

We suggest a modular framework and distinguish between the computing system modeling and the computing resource management. Fig. 1.10 indicates this modular design approach. The SDR computing system modeling is presented in Chapter 3. It models the computing resources and requirements based on two computing resource management techniques, which facilitate meeting the strict timing constraints of real-time systems. The modeling is scalable and can account for many different hardware architectures and computing resource types. This work focuses on processing and interprocessor bandwidth resources and processing and data flow requirements. Section 3 also introduces several modeling parameters for capturing specific platform and application features.

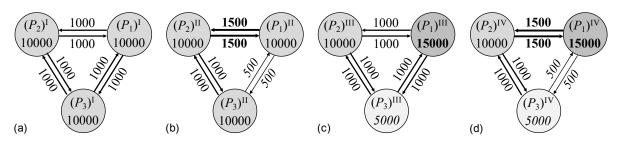

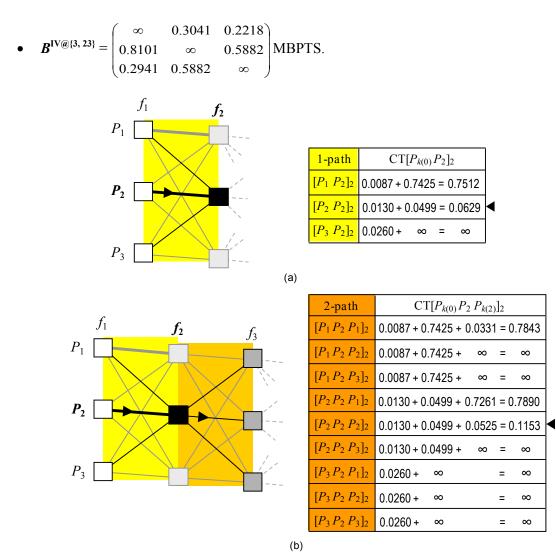

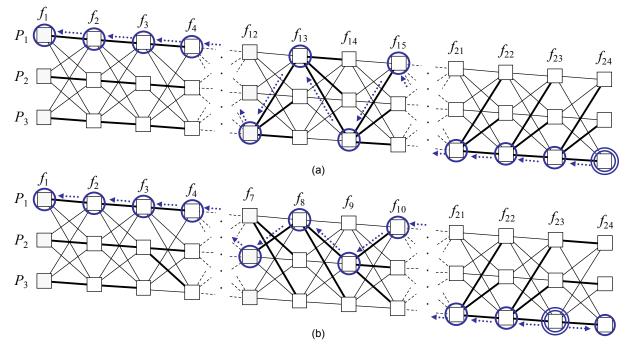

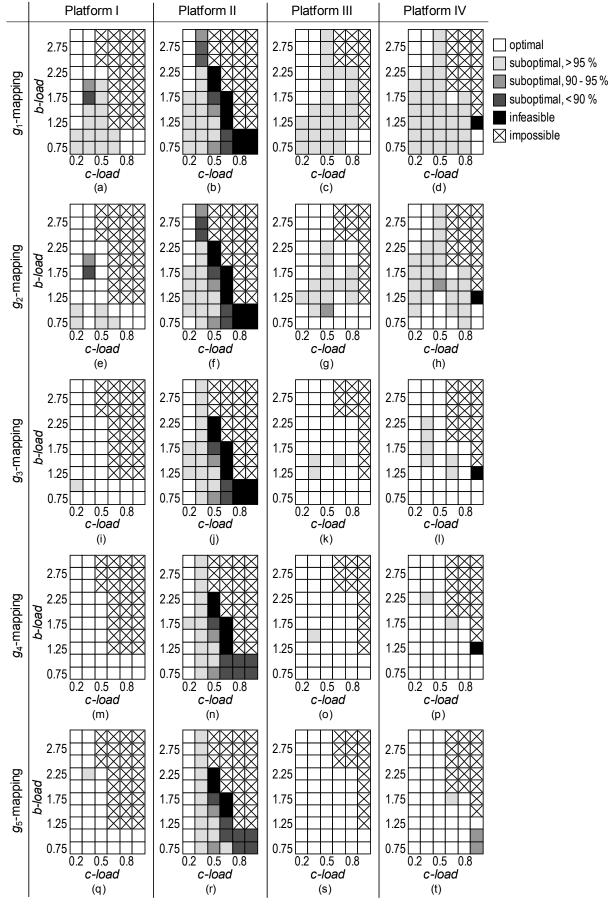

Chapter 4 presents our computing resource management approach, which consists of a generalpurpose mapping algorithm and a cost function. The independence between the algorithm and the cost function facilitates implementing many different computing resource management policies. We introduce a dynamic programming based algorithm, the  $t_w$ -mapping, where w controls the decision window. A general and parametric cost function guides the mapping process under the given resource constraints, whereas an instance of it facilitates finding a mapping that meets all processing and data flow requirements of SDR applications with the available processing and bandwidth resources of SDR platforms. This cost function assumes the SDR computing system models of Chapter 3. Chapters 5 and 6 simulate several SDR reconfiguration scenarios and analyze the suitability of our framework and its potentials for a flexible computing resource management.

We extend our SDR computing resource management concepts to the cognitive radio context. The two primary objectives of cognitive radio are *highly reliable communications whenever and wherever needed* and *the efficient use of the radio spectrum* [116]. We formulate a third objective as *the efficient use of*

Fig. 1.10. Modular SDR computing resource management framework.

*computing resources*. The *cognitive computing resource management* then correspondingly extends the currently investigated scope of cognitive radio. Chapter 7 examines the cognitive capabilities of our framework—the cognitive radio's interface to SDR platforms—and indicates the potentials of our proposal.

The cognitive computing resource management needs to be coordinated with the RRM. Chapter 8, therefore, introduces the *joint resource management* concept for cognitive radios. It proposes three cognitive cycles and discusses several interrelations between the radio, computing, and application resources, where application resources refer to the available SDR and user applications. Our approach potentiates flexibility and facilitates radio against computing resource tradeoffs. It promotes cognition at all layers of the wireless system for a cooperative or integrated resource management that may increase the performance and efficiency of wireless communications. Chapter 9 concludes the dissertation with a summary of its main contributions and a brief outlook on future research possibilities.

# 2

# SDR Computing Resource Management Context

# 2.1 Introduction

This chapter presents the context of our SDR computing resource management framework of Chapters 3 and 4. We first review some important SDR frameworks (Section 2.2). These frameworks abstract the hardware details of SDR platform and constitute the operating environment for SDR applications. We specify the SDR computing environment, formulate the problem, and discuss the scope and assumptions of our solution in Section 2.3. Section 2.4 examines the related work in the general context of heterogeneous computing. We can then concretize the main features that an SDR computing resource management framework should satisfy, while taking into account prior achievements (Section 2.5).

# 2.2 SDR Frameworks

An execution environment provides a platform for the execution of applications. It basically abstracts hardware resources and provides several functionalities to applications for a controlled use of these resources. Execution environments for general purpose computing platforms and applications include common OSs, such as UNIX or POSIX (portable operating system interface) [20], higher level abstractions or virtual machines (VMs) [20], object oriented architectures, such as the common object request broker architecture (CORBA) [21], and grid computing environments [23]. While conceptually appropriate for the SDR computing context, these environments do not specifically address digital signal processing issues and introduce timing, memory, and power overheads that make it difficult to meet the hard real-time computing constraints of SDRs. Therefore, general-purpose computing knowledge and experience has been adapted to the digital signal processing world and SDR frameworks emerged.

Several SDR frameworks exist. The Joint Tactical Radio System's (JTRS's) software communications architecture (SCA) [87], for example, is an SDR framework specification that is based on CORBA. Since SCA is the most widespread SDR research project, we may classify SDR frameworks as SCA and non-SCA based. This Section briefly reviews the SCA, the QoS-enabled SCA (Q-SCA), and the P-HAL-OE. We discuss the frameworks' principal characteristics and evaluate their computing resource management capabilities. Section 2.2.4 finally summarizes a few additional SDR frameworks; many more exist.

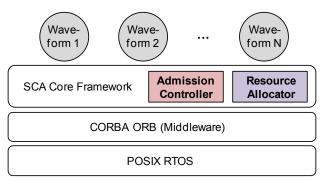

# 2.2.1 SCA

The JTRS is the US military software radio research program and the SCA is its baseline architecture [87]. The SDR Forum, industry, and academia are promoting, developing, and implementing the SCA. The

SDR Forum is an independent and nonprofit organization [15]. It is attempting to fill the role of a software radio standards body with the mission of fostering software radios in a flexible wireless market. Its members are companies, universities, and other associations with experience or interest in SDRs. The SDR Forum proposed its own SDR framework, which is based on the JTRS-SCA.

The Mobile and Portable Radio Research Group (MPRG) of Virginia Tech is developing the open source SDR framework *OSSIE* (*open source SCA implementation embedded*) [89]. OSSIE is primarily intended to enable research and education in SDR and wireless communications. The software package, which is downloadable from [89], includes an SDR core framework based on the JTRS-SCA, tools for rapid development of SDR components and waveforms, and an evolving library of pre-built applications.

Here we briefly present the SCA and its computing resource management capabilities, rather than examining the different SCA implementations. If not stated otherwise, we discuss the JTRS-SCA release 2.2 [88].

## A) Objectives

The SCA was introduced to reduce software manufacturing costs by reducing the development time through the reusability and portability of waveforms. The initial goals of the SCA were [14]:

- 1. function as a multiband multimode radio,

- 2. be interoperable with all JTRS domains (airborne, fixed/ maritime, vehicular, dismounted, and hand-held),

- 3. be compatible with legacy systems,

- 4. support the insertion of new technologies,

- 5. support advanced networking features, and

- 6. use primarily commercial off-the-shelf (COTS) components.

These objectives were generalized by the SDR Forum's approach, specifying

- 1. the domain independence across all commercial, civil, and military implementations, and

- 2. the support for commercial, civil, and military waveforms.

The SCA thus approaches a common architecture with clear interface definitions for easing the design of flexible and interoperable SDR execution environments and portable waveforms. It encourages the extensive use of object-oriented methodologies. It emphasizes on continuous validations, where the specifications are validated and refined during the research, prototyping, and implementation processes.

## B) Architecture

The basic architecture comprises a software and a hardware framework as well as rules that govern the software and hardware implementations. The software framework defines the software structure and the interactions between software components. The hardware framework describes the hardware classes and subclasses and not individual and domain-specific hardware choices. The rules relate to specific implementations. They specify interfaces, form factors, software development languages, and so forth. They particularly define specific software and hardware requirements that must be met for an implementation to be SCA compliant.

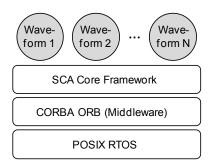

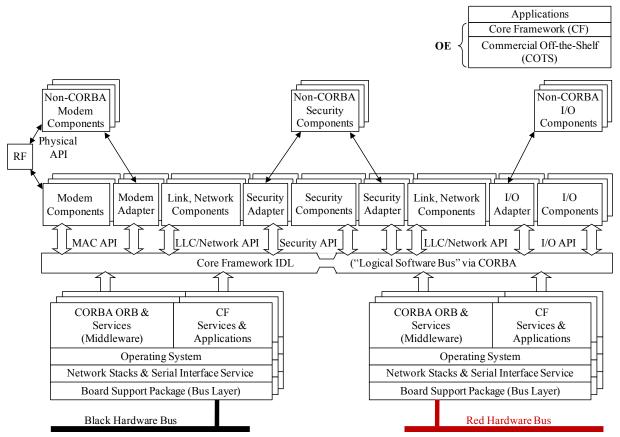

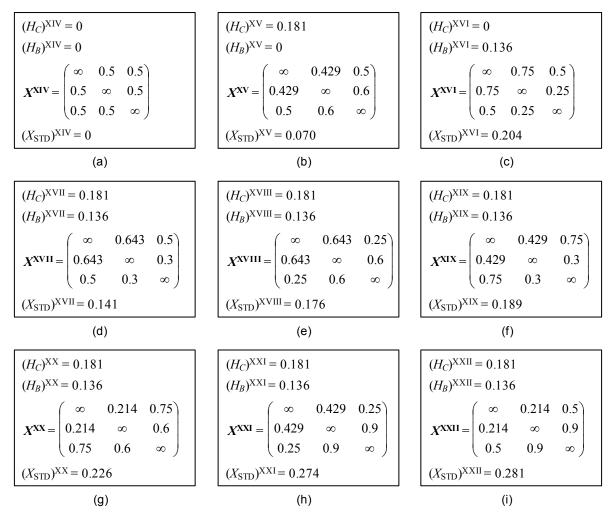

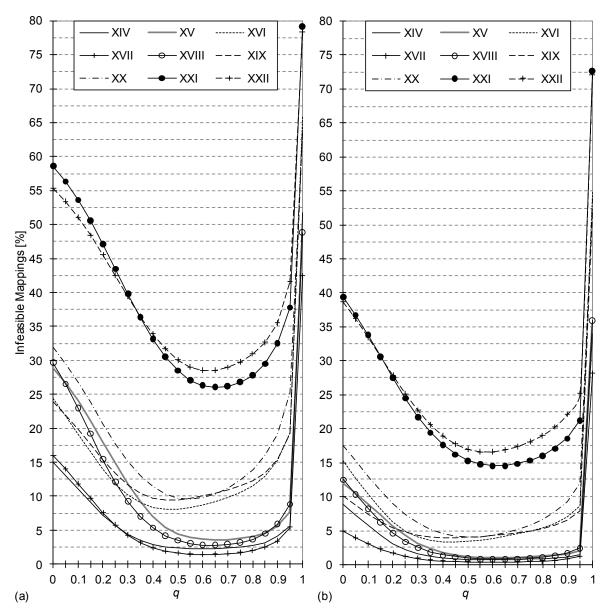

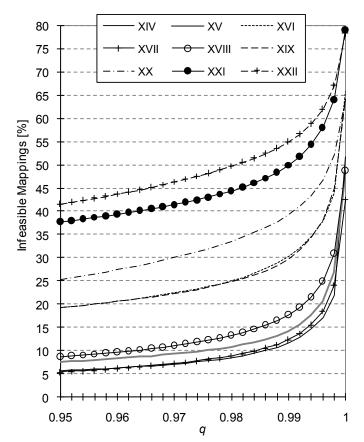

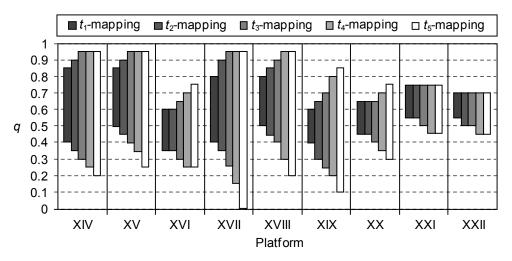

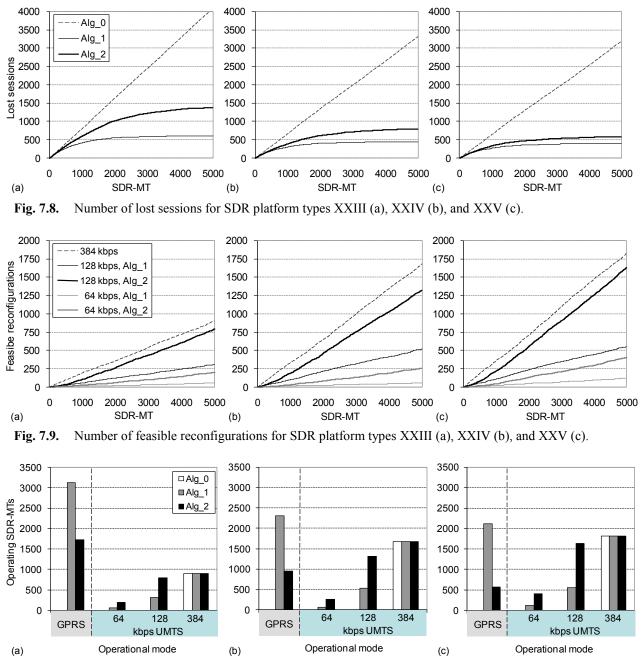

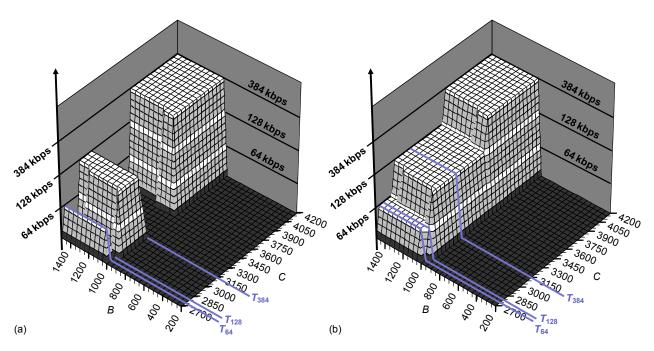

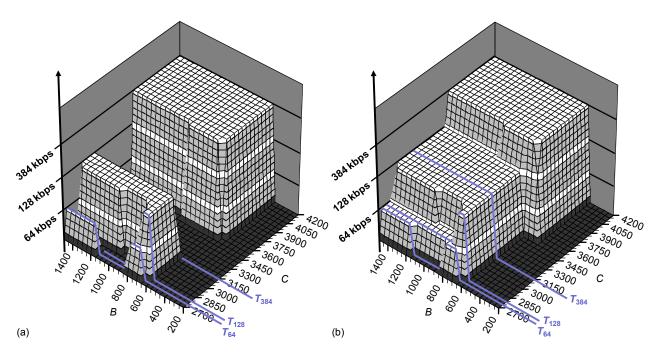

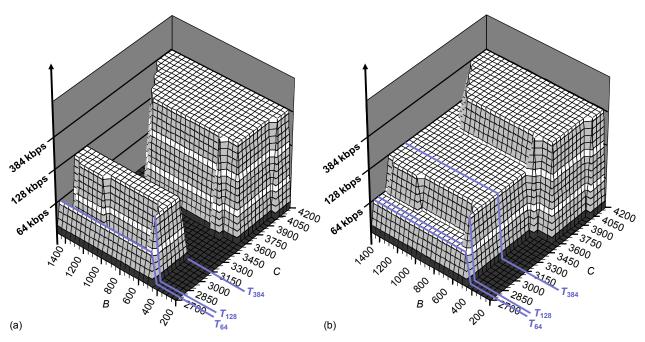

The general software stack of the SCA consists of the *core framework* (CF), the CORBA object request broker (ORB), and the POSIX-based real-time operating system (RTOS) (Fig. 2.1). The CF describes the interfaces. It provides an abstraction of the software and hardware layers for waveform developers. The CORBA ORB facilitates the communication between software objects. Therefore, each object must provide an interface written in the object management group (OMG) interface definition language (IDL). This encapsulates the actual functionality of a CORBA object behind its interface.