**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# Adaptive Memory Hierarchies for Next Generation Tiled Microarchitectures

# Enric Herrero Abellanas

Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

Advisors: José González González (Intel Barcelona) Ramon Canal Corretger (Universitat Politècnica de Catalunya)

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy / Doctor per la UPC

2011 July

## Acknowledgements

En primer lloc vull agraïr l'ajut que m'han donat durant aquests anys els meus directors de tesi, el Pepe i en Ramon. Durant aquests anys m'han iniciat en el món de la recerca. Gràcies a ells he pogut conèixer el que és investigar, que al cap i a la fi és aprendre contínuament i saber qüestionar el que s'aprèn. Són uns coneixements que de ben segur em serviran de molt en el futur.

També vull agraïr al Dean el suport que em va donar durant la meva estada a San Diego i que em va facilitar molt l'adaptació a un país que no coneixia. Thank you Dean. Els meus agraïments també per als membres del tribunal, els seus comentaris han ajudat molt a millorar la qualitat de la tesi. Gràcies també a l'Antonio per donar-me la oportunitat de treballar al grup ARCO i al Mats per introduïr-me en el món de l'arquitectura de computadors.

Vull agraïr als meus pares el suport que m'han donat sempre i sense el qual hagués estat impossible realitzar aquesta tesi. Des de petit m'han ensenyat el valor de la educació i m'han ajudat sempre que ha fet falta. Gràcies.

Un agraïment també al meu germà Guillem, a la famiglia, a la gent de Cardedeu i al sector euetibià que han aconseguit que pogués desconnectar de la feina quan feia falta.

I finalment també agraïr a tots els becaris de la sala C6-E208 (i altres sales...) per els bons moments que hem passat durant aquests anys tot fent un cafè o a fora de la universitat.

# Contents

| List of Figures |       |             |                                                    | vii |  |  |  |

|-----------------|-------|-------------|----------------------------------------------------|-----|--|--|--|

| Li              | st of | Tables      |                                                    | xi  |  |  |  |

| 1               | Intro | ntroduction |                                                    |     |  |  |  |

|                 | 1.1   | Memo        | ry Hierarchy Challenges                            | 2   |  |  |  |

|                 |       | 1.1.1       | Increasing number of processors                    | 2   |  |  |  |

|                 |       | 1.1.2       | Increased off-chip miss cost                       | 3   |  |  |  |

|                 |       | 1.1.3       | Limited power budget                               | 3   |  |  |  |

|                 |       | 1.1.4       | Multiprogrammed Environments                       | 4   |  |  |  |

|                 | 1.2   | Contri      | butions                                            | 4   |  |  |  |

|                 |       | 1.2.1       | Distributed Coherence Mechanism                    | 4   |  |  |  |

|                 |       | 1.2.2       | Dynamic and Distributed Cache Allocation           | 4   |  |  |  |

|                 |       | 1.2.3       | DRAM organization for multiprogrammed environments | 5   |  |  |  |

| 2               | Вас   | kgroun      | nd and Motivation                                  | 7   |  |  |  |

|                 | 2.1   | Introdu     | uction                                             | 7   |  |  |  |

|                 | 2.2   | Moder       | rn multiprocessors, from NUMA to NUCA              | 9   |  |  |  |

|                 | 2.3   | Cache       | e organizations in the multicore era               | 12  |  |  |  |

|                 |       | 2.3.1       | Static partitioning                                | 14  |  |  |  |

|                 |       | 2.3.2       | Dynamic partitioning                               | 15  |  |  |  |

|                 | 2.4   | Memo        | ry Controllers                                     | 18  |  |  |  |

|                 |       | 2.4.1       | Memory Organization                                | 19  |  |  |  |

|                 |       | 2.4.2       | Memory Controller structure                        | 21  |  |  |  |

|                 | 2.5   | DRAM        | Bank Schedulers for multicore processors           | 22  |  |  |  |

|                 |       | 2.5.1       | Memory Throughput Oriented Schedulers              | 23  |  |  |  |

|                 |       | 2.5.2       | Fairness Oriented Schedulers                       | 25  |  |  |  |

|                 |       | 2.5.3       | System Throughput Oriented Schedulers              | 26  |  |  |  |

#### CONTENTS

|   |      | 2.5.4   | Prefetch-Aware Schedulers                    | 27 |

|---|------|---------|----------------------------------------------|----|

|   |      | 2.5.5   | Power/Area-Aware Schedulers                  | 28 |

|   |      | 2.5.6   | Throughput-Fairness Trade-off                | 29 |

|   | 2.6  | Progre  | ess beyond the state-of-the-art              | 32 |

|   |      | 2.6.1   | Cache organization                           | 32 |

|   |      | 2.6.2   | DRAM management                              | 33 |

| 3 | Metl | hodolo  | gy                                           | 35 |

|   | 3.1  | Simula  | ation Infrastructure                         | 35 |

|   |      | 3.1.1   | Metrics                                      | 38 |

|   | 3.2  | Power   | Model                                        | 38 |

|   |      | 3.2.1   | Power Calculation Methods                    | 39 |

|   |      | 3.2.2   | Dynamic Power                                | 39 |

|   |      | 3.2.3   | Static Power                                 | 40 |

|   |      | 3.2.4   | Cache                                        | 41 |

|   |      | 3.2.5   | Network                                      | 41 |

|   | 3.3  | Bench   | marks and Characterization                   | 46 |

|   |      | 3.3.1   | SPEC OMP2001 and SPEC CPU2006                | 46 |

|   |      | 3.3.2   | Benchmark set 1                              | 47 |

|   |      | 3.3.3   | Prefetch Influence in memory access patterns | 51 |

|   |      | 3.3.4   | Benchmark set 2                              | 57 |

| 4 | Dist | ributed | d Cooperative Caching                        | 59 |

|   | 4.1  |         | round and Motivation                         | 59 |

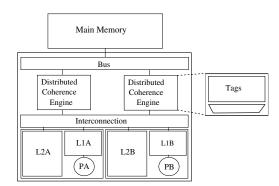

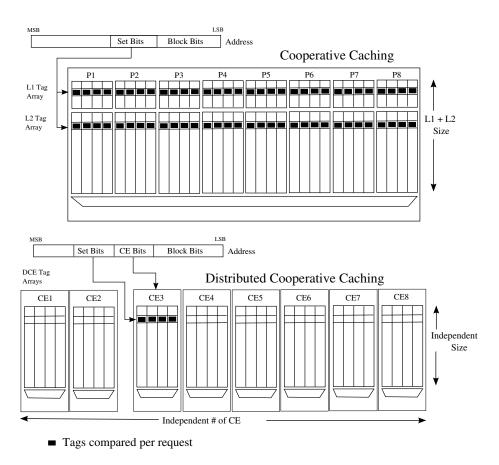

|   | 4.2  | -       | outed Cooperative Caching                    | 61 |

|   |      | 4.2.1   | Cooperative Caching                          | 61 |

|   |      | 4.2.2   | The Distributed Cooperative Caching scheme   | 62 |

|   |      | 4.2.3   | Differences between CC and DCC               | 67 |

|   | 4.3  | Power   | -Efficient Spilling Techniques               | 68 |

|   |      | 4.3.1   | Distance-Aware Spilling                      | 68 |

|   |      | 4.3.2   | Selective Spilling                           | 70 |

|   | 4.4  | Evalua  | ation                                        | 72 |

|   |      | 4.4.1   | Simulated Configurations                     | 72 |

|   |      | 4.4.2   | Single Multi-threaded Benchmarks Evaluation  | 74 |

|   |      | 4.4.3   | Benchmark Set 1 Evaluation                   | 83 |

|   |      | 4.4.4   | Benchmark Set 2 Evaluation                   | 87 |

#### CONTENTS

|    | 4.5    | Conclusions                          | 90  |

|----|--------|--------------------------------------|-----|

| 5  | Elas   | stic Cooperative Caching             | 91  |

|    | 5.1    | Background and Motivation            | 91  |

|    | 5.2    | Elastic Cooperative Caching          | 94  |

|    |        | 5.2.1 ElasticCC Structure            | 95  |

|    |        | 5.2.2 Cache Repartitioning Unit      | 96  |

|    |        | 5.2.3 Spilled Block Allocator        | 97  |

|    |        | 5.2.4 Adaptive Spilling mechanism    | 98  |

|    | 5.3    | Evaluation                           | 100 |

|    |        | 5.3.1 Simulated Configurations       | 100 |

|    |        | 5.3.2 Benchmark Set 1 Evaluation     | 102 |

|    |        | 5.3.3 Benchmark Set 2 Evaluation     | 106 |

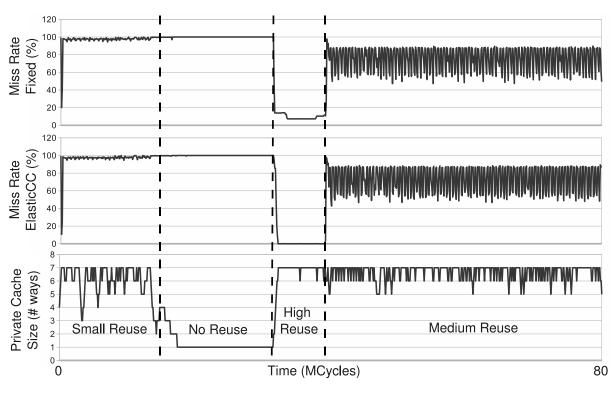

|    |        | 5.3.4 Temporal behavior of ElasticCC | 108 |

|    | 5.4    | Conclusions                          | 109 |

| 6  | Thre   | ead Row Buffers                      | 111 |

| •  | 6.1    | Background and Motivation            | 111 |

|    | 6.2    | Thread Row Buffers                   | 112 |

|    | 6.3    | Service Partitioning Scheduler       | 113 |

|    | 6.4    |                                      | 116 |

|    |        | 6.4.1 Simulated Configurations       | 116 |

|    |        |                                      | 117 |

|    |        | 6.4.3 Addition of extra banks        | 121 |

|    | 6.5    | Conclusions                          | 123 |

| 7  | Con    | nclusions                            | 125 |

|    | 7.1    | Thesis Contributions                 | 125 |

|    | 7.2    | Future Work                          | 126 |

| GI | ossa   | ary                                  | 129 |

|    |        |                                      |     |

| Re | eferei | nces                                 | 130 |

#### CONTENTS

# **List of Figures**

|      |                                                                               | -  |

|------|-------------------------------------------------------------------------------|----|

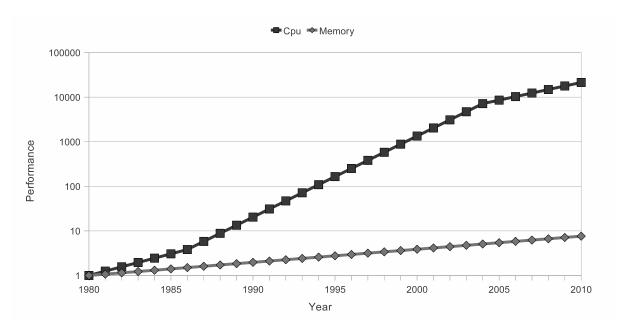

| 1.1  | Gap between memory and CPU performance.                                       | 2  |

| 2.1  | Article in the Datamation magazine presenting the first multiprocessor on     |    |

|      | March 1961                                                                    | 8  |

| 2.2  | CMP-NuRapid Memory Structure.                                                 | 14 |

| 2.3  | Adaptive Selective Replication Memory Structure.                              | 14 |

| 2.4  | CC Memory Structure.                                                          | 15 |

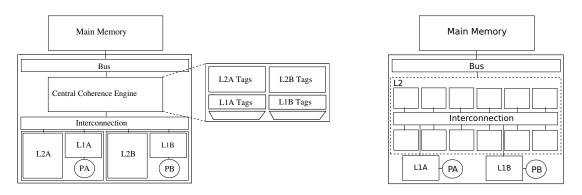

| 2.5  | NUCA Memory Structure                                                         | 15 |

| 2.6  | R-NUCA Memory Structure.                                                      | 16 |

| 2.7  | Adaptive Set Pinning Memory Structure                                         | 16 |

| 2.8  | Utility-Based Cache Partitioning Memory Structure                             | 17 |

| 2.9  | Adaptive Shared-Private NUCA Memory Structure.                                | 17 |

| 2.10 | Memory Organization and Mapping.                                              | 20 |

| 2.11 | Memory Controller Structure                                                   | 21 |

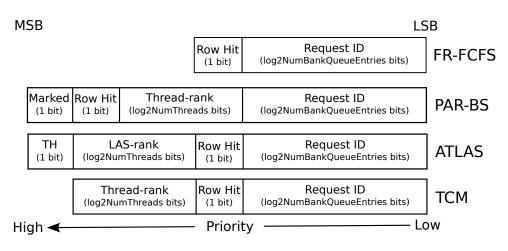

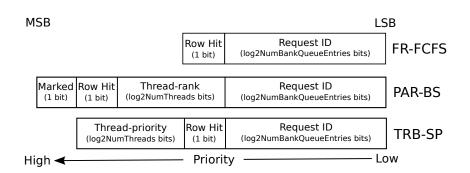

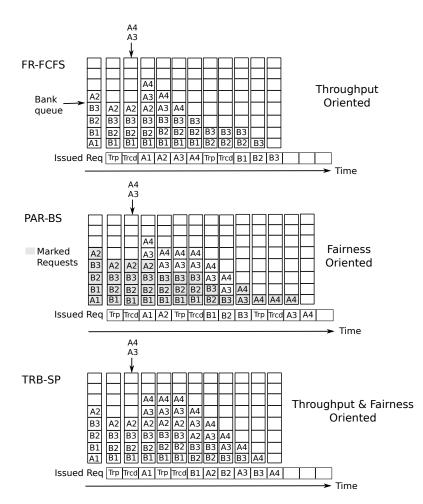

| 2.12 | Priority calculation for FR-FCFS, PAR-BS and TRB-SP                           | 30 |

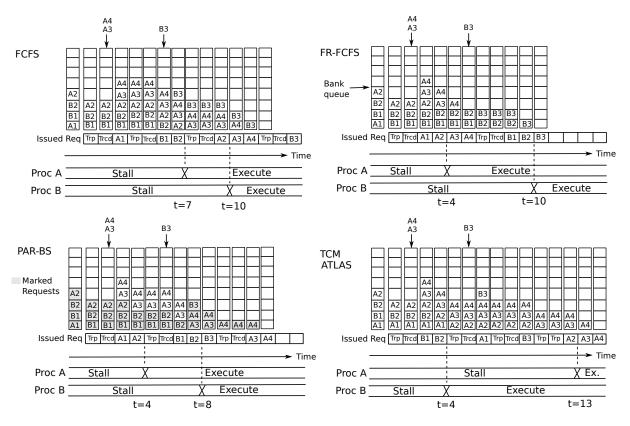

| 2.13 | Scheduling example.                                                           | 31 |

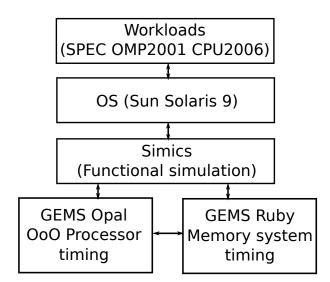

| 3.1  | Simulation infrastructure.                                                    | 35 |

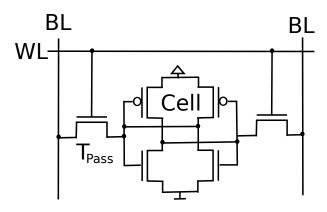

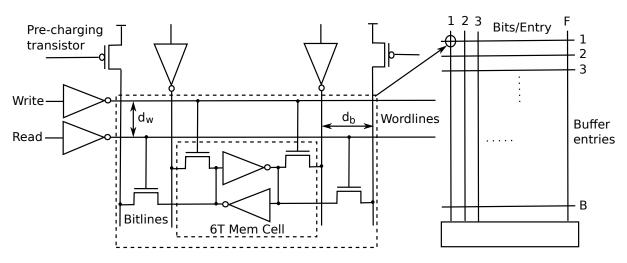

| 3.2  | Typical structure of a 6T Memory Cell.                                        | 41 |

| 3.3  | Buffer structure.                                                             | 42 |

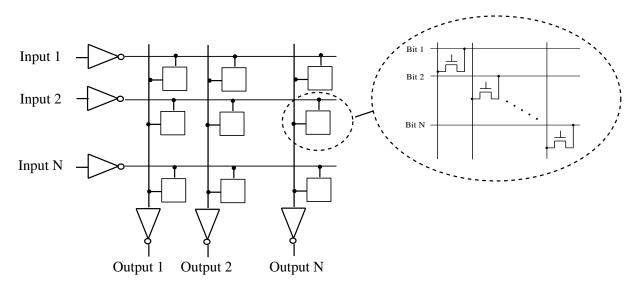

| 3.4  | Crossbar structure.                                                           | 43 |

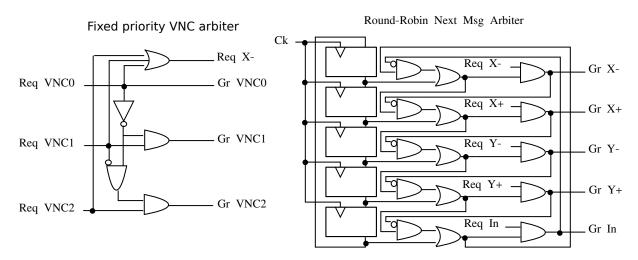

| 3.5  | Arbiter structure.                                                            | 44 |

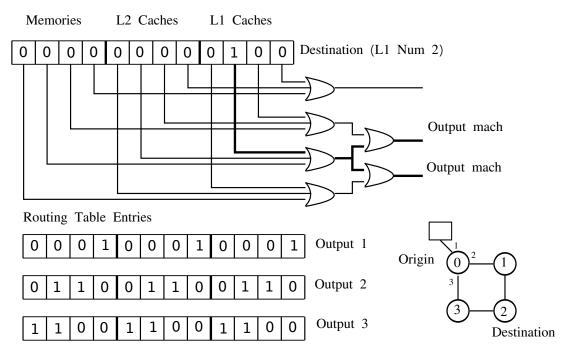

| 3.6  | Routing Table structure.                                                      | 45 |

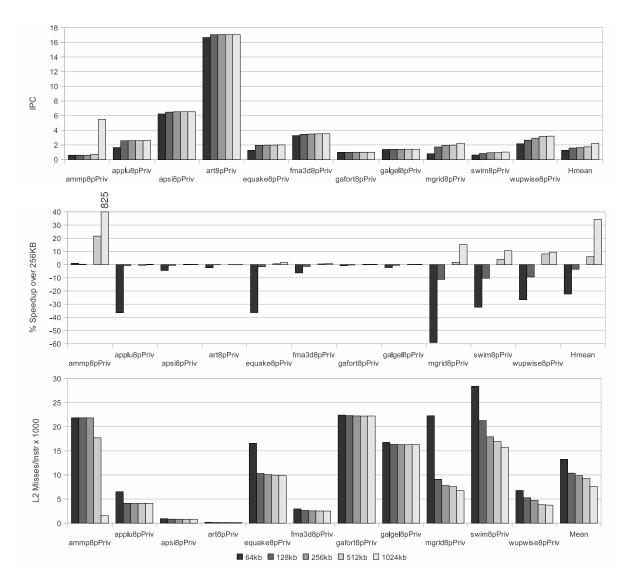

| 3.7  | SPEC OMP Characterization.                                                    | 49 |

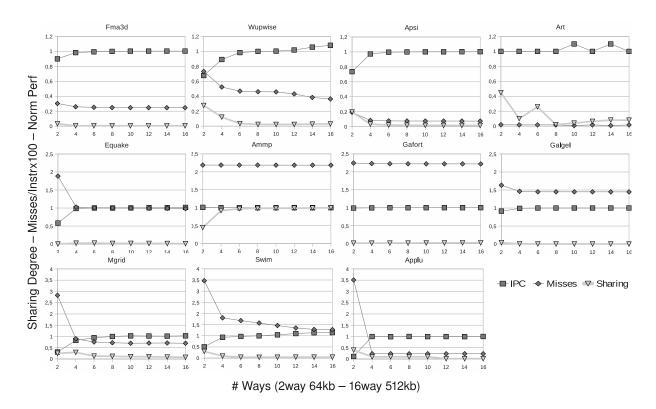

| 3.8  | Spec OMP 2001 benchmark characteristics for different L2 sizes/associativity. | 50 |

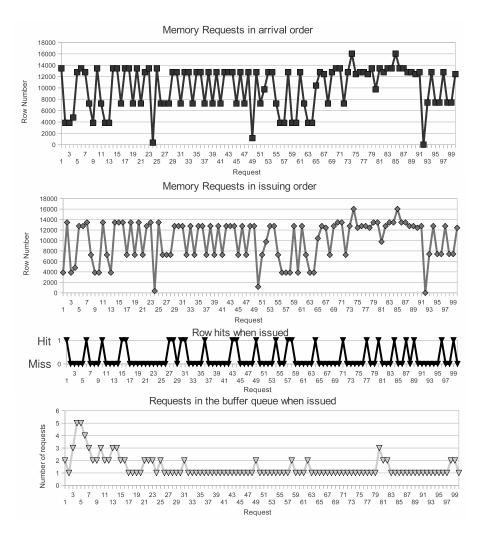

| 3.9  | Request Behavior in Bank 0 in a multiprogrammed environment                   | 52 |

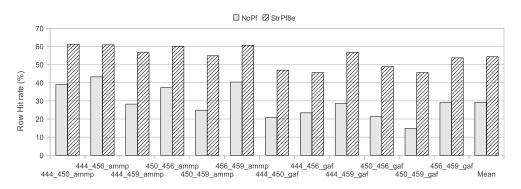

| 3.10 | Row hit rate with and without prefetch.                                       | 53 |

#### LIST OF FIGURES

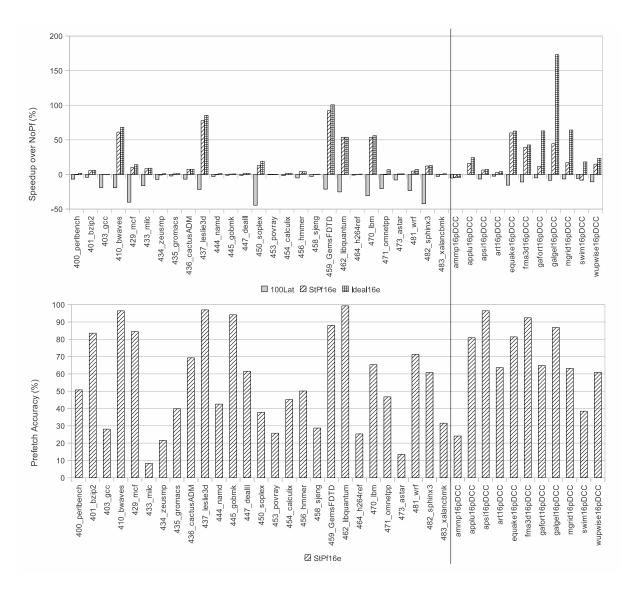

| 3.11 | Prefetch influence on performance (Speedup and accuracy)                      | 54        |

|------|-------------------------------------------------------------------------------|-----------|

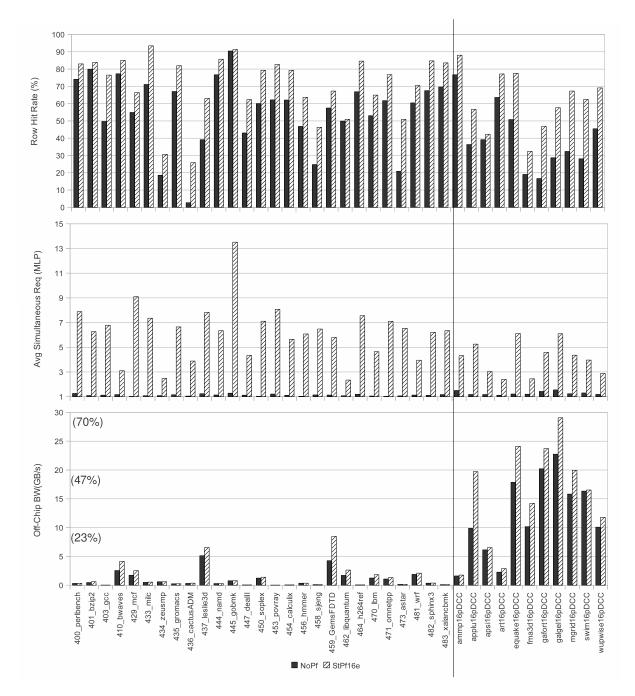

| 3.12 | Prefetch influence on performance (Row hit rate, MLP and off-chip bandwidth). | 55        |

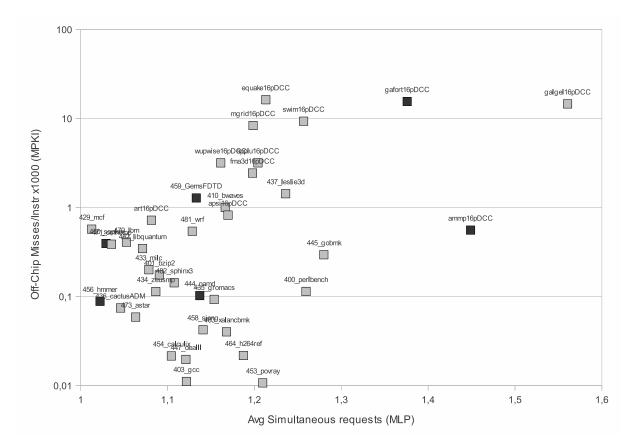

| 3.13 | Spec OMP2001 and CPU2006 characterization without prefetch.                   | 56        |

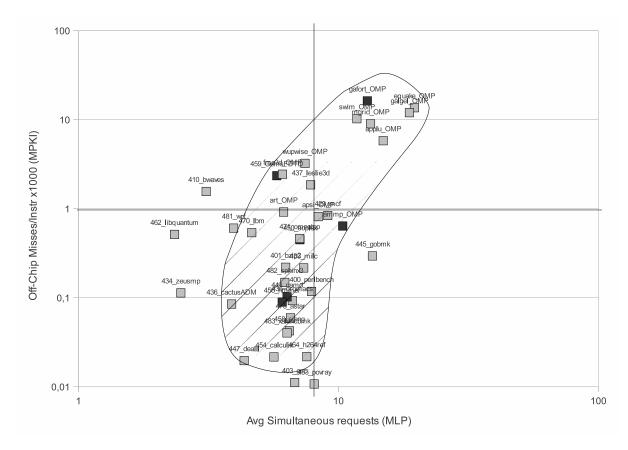

| 3.14 | Spec OMP2001 and CPU2006 classification with prefetch.                        | 57        |

| 4 4  | CO Marramy Structure                                                          | <b>C1</b> |

| 4.1  |                                                                               | 61        |

| 4.2  |                                                                               | 62        |

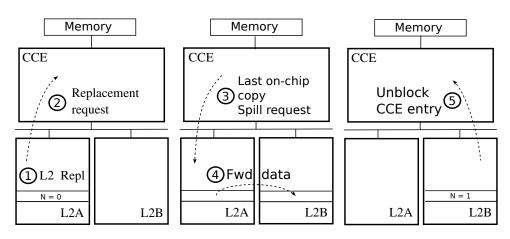

| 4.3  |                                                                               | 63        |

| 4.4  |                                                                               | 64        |

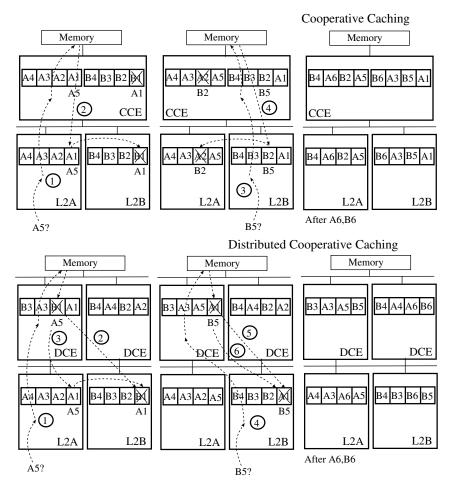

| 4.5  | Working Example.                                                              | 65<br>62  |

| 4.6  | Spilled blocks being reused by the evicting node.                             | 69<br>70  |

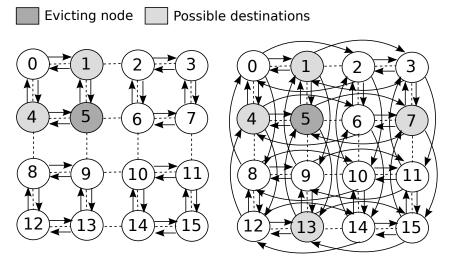

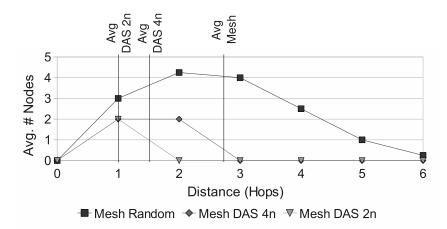

| 4.7  | Distance-Aware Spilling node assignment in a mesh network.                    | 70        |

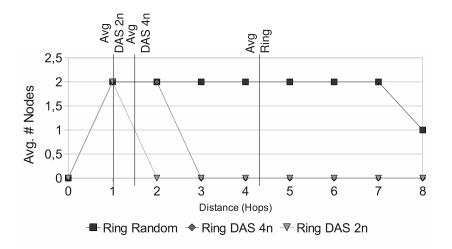

| 4.8  | Average distance to destination nodes in a mesh network.                      | 71        |

| 4.9  | Distance-Aware Spilling node assignment in a ring network.                    | 71        |

|      | Average distance to destination nodes in a ring network.                      | 72        |

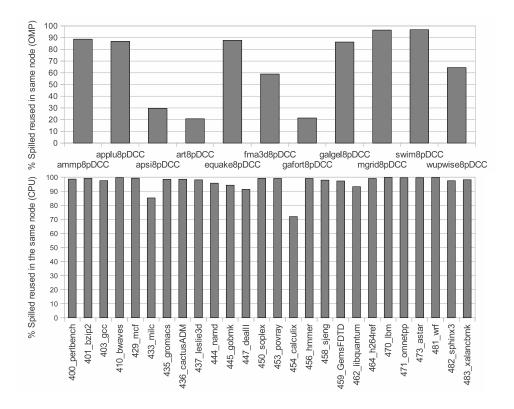

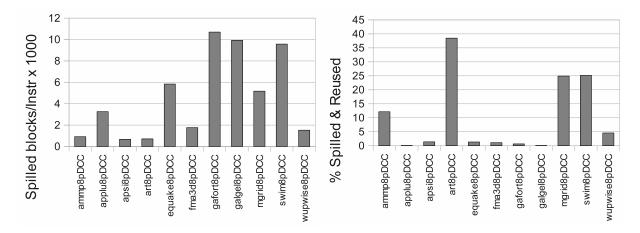

|      | Spilling characterization of SpecOMP2001 benchmarks.                          | 72        |

|      | Spilling characterization of SpecCPU2006 benchmarks.                          | 73        |

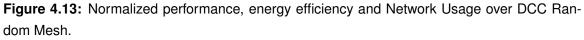

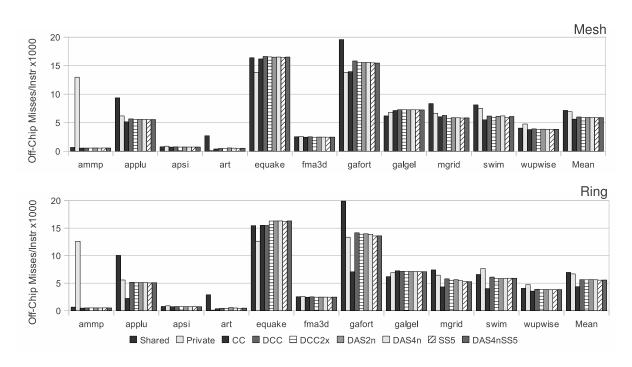

| 4.13 | Normalized performance, energy efficiency and Network Usage over DCC          |           |

|      | Random Mesh.                                                                  | 75        |

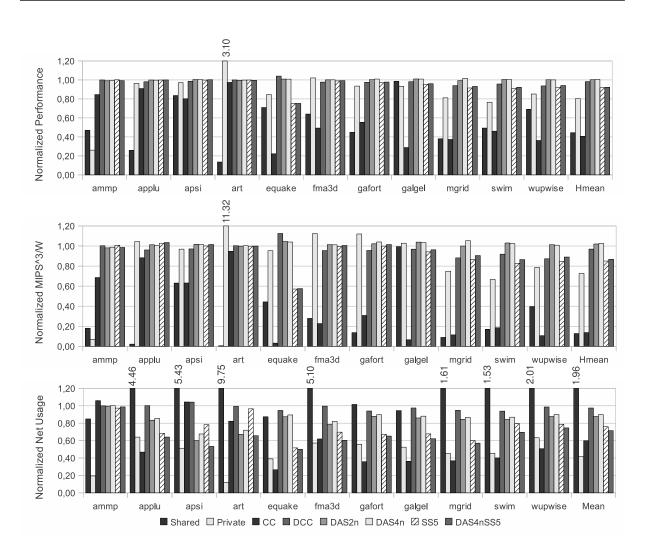

| 4.14 | Normalized performance, energy efficiency and Network Usage over DCC          |           |

|      | Random Ring.                                                                  | 77        |

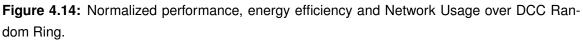

|      | Off-Chip Misses per thousand instructions.                                    | 78        |

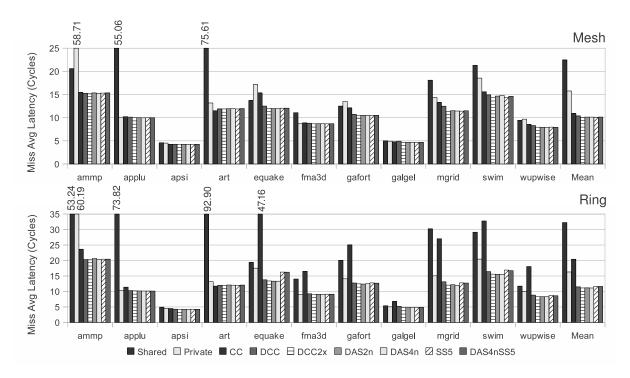

|      | Average L1 Miss latency.                                                      | 78        |

|      | DCC16CE and DCC4CE organization                                               | 79        |

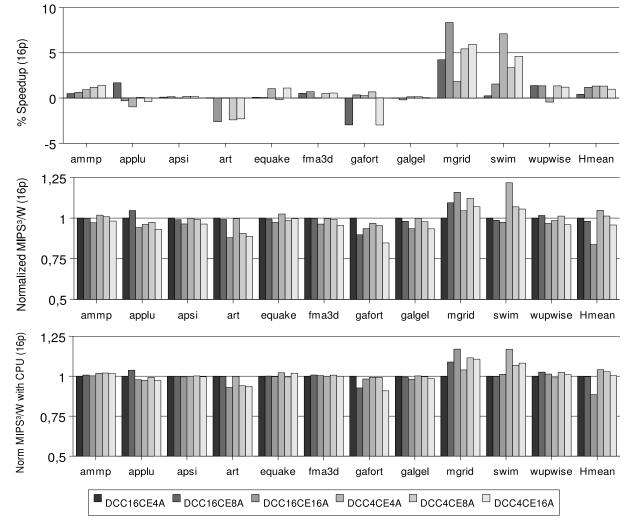

|      | DCC Optimal Configuration Study.                                              | 80        |

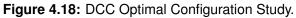

| 4.19 | DCE replacements per request.                                                 | 81        |

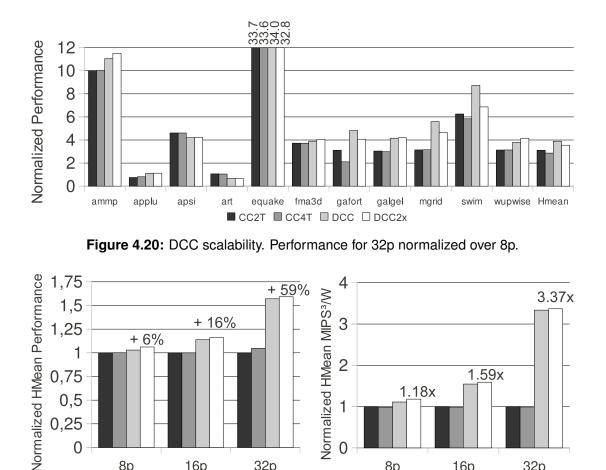

| 4.20 | DCC scalability. Performance for 32p normalized over 8p.                      | 82        |

|      | DCC scalability. Performance normalized over CC2T                             | 82        |

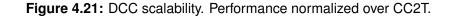

| 4.22 | Normalized performance, energy efficiency and Network Usage over DCC          |           |

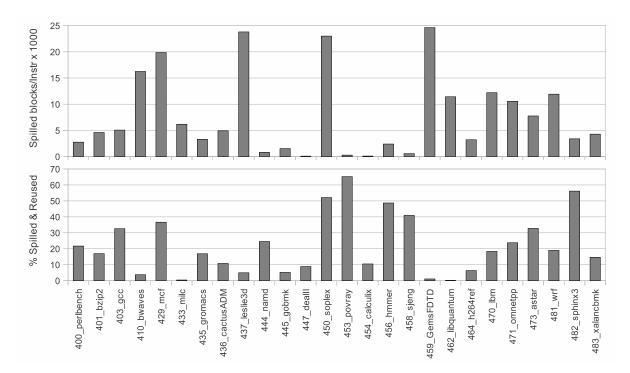

|      | Random Mesh.                                                                  | 84        |

| 4.23 | Normalized performance, energy efficiency and network usage over DCC          |           |

|      | Random Ring                                                                   | 85        |

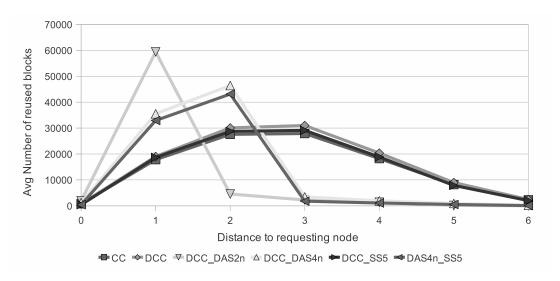

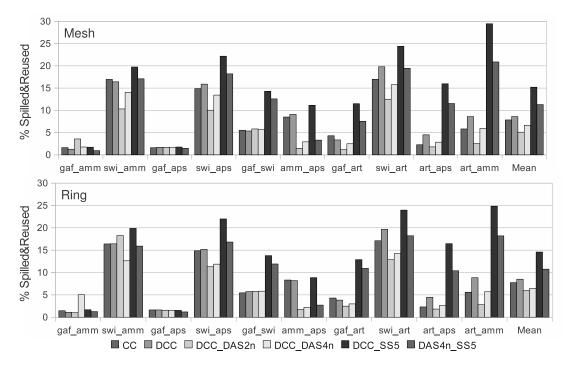

| 4.24 | Average distance of reused blocks                                             | 86        |

| 4.25 | Percentage of spilled blocks being reused                                     | 86        |

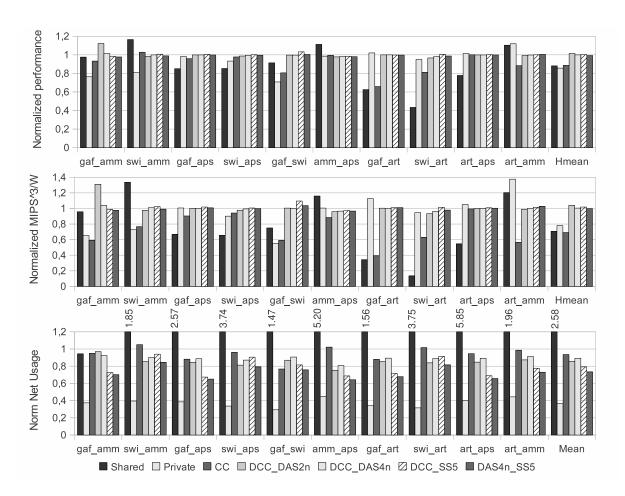

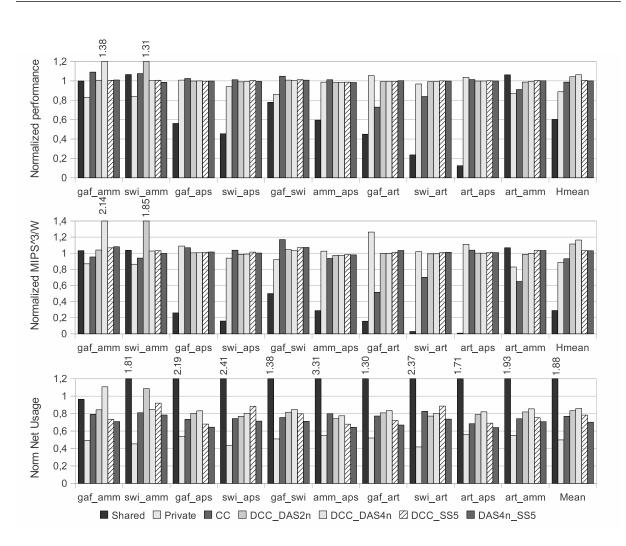

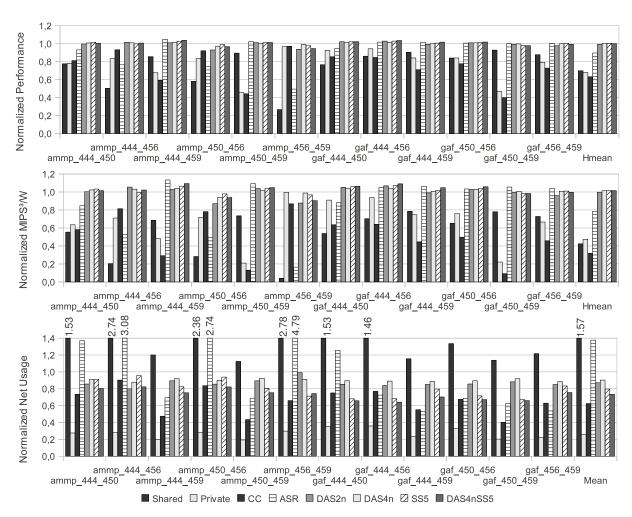

| 4.26 | Normalized performance, energy efficiency and Network Usage over DCC          |           |

|      | Random Mesh.                                                                  | 88        |

### LIST OF FIGURES

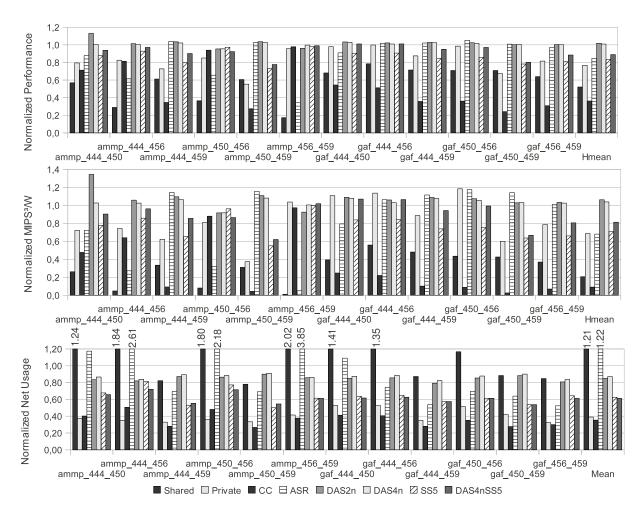

| 4.27 1 | Normalized performance, energy efficiency and network usage over DCC       |     |

|--------|----------------------------------------------------------------------------|-----|

| F      | Random Ring                                                                | 89  |

| 5.1    | Adaptive Shared/Private NUCA Repartitioning Unit                           | 93  |

|        | ElasticCC Node Structure.                                                  | 95  |

|        | ElasticCC Repartitioning Unit.                                             | 96  |

|        | Cache Repartitioning Algorithm.                                            | 97  |

|        | Spilled Block Allocator.                                                   | 98  |

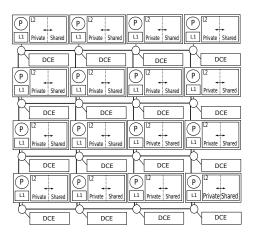

|        | ElasticCC Memory Structure.                                                | 100 |

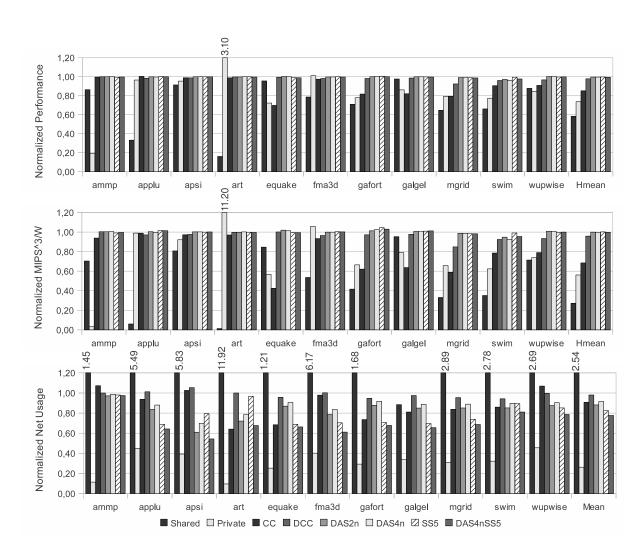

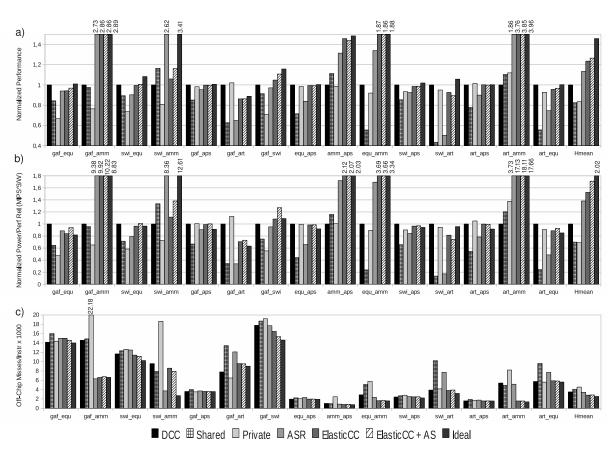

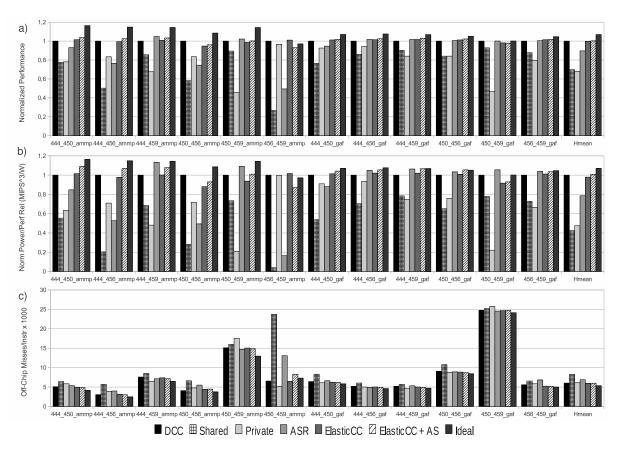

|        | Normalized performance, Normalized energy efficiency and Off-Chip misses   |     |

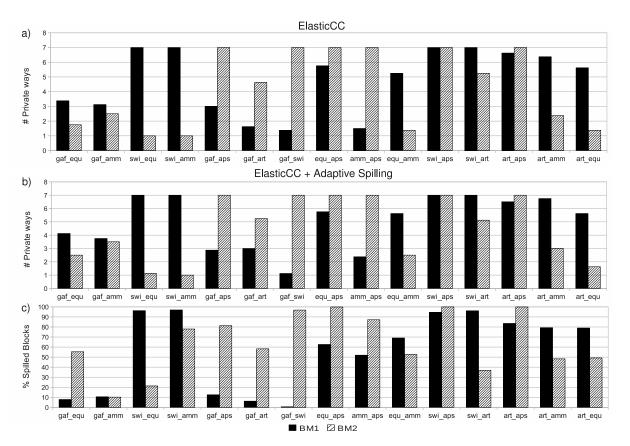

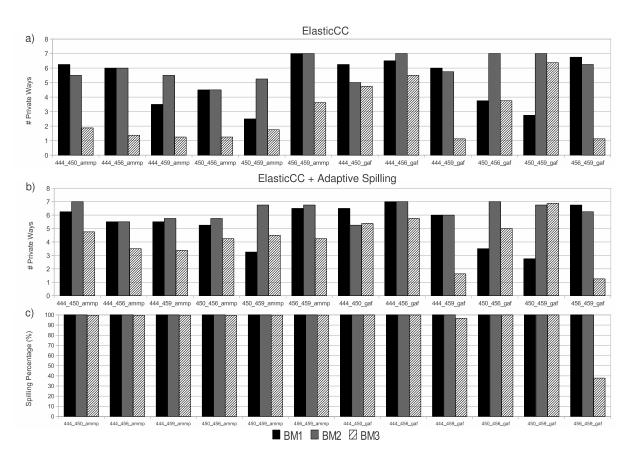

|        | per Instr                                                                  | 102 |

| 5.8    | Average number of private ways per benchmark in ElasticCC and ElasticCC    |     |

|        | + AS and percentage of spilled blocks per benchmark in ElasticCC + AS      |     |

| C      | compared to ElasticCC.                                                     | 104 |

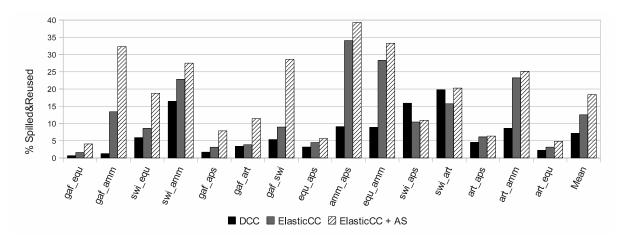

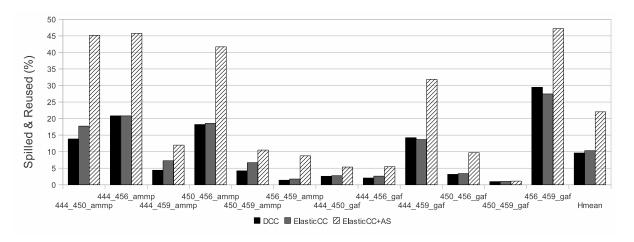

| 5.9 F  | Percentage of spilled blocks that are reused in Benchmark Set 1            | 105 |

| 5.10   | Normalized performance, Normalized energy efficiency and Off-Chip misses   |     |

| k      | per Instr                                                                  | 106 |

| 5.11 / | Average number of private ways per benchmark in ElasticCC and ElasticCC    |     |

| -      | + AS and percentage of spilled blocks per benchmark in ElasticCC + AS      |     |

| C      | compared to ElasticCC                                                      | 107 |

| 5.12 F | Percentage of spilled blocks that are reused in Benchmark Set 2            | 108 |

| 5.13 ( | Cache behavior for thread 1 of Equake.                                     | 109 |

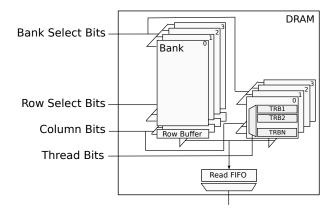

| 6.1 [  | DRAM with TRBs structure                                                   | 113 |

| 6.2 F  | Priority calculation for FR-FCS, PAR-BS and TRB-SP.                        | 114 |

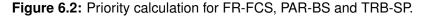

| 6.3    | Thread priority calculation hardware.                                      | 114 |

| 6.4    | Scheduling example.                                                        | 115 |

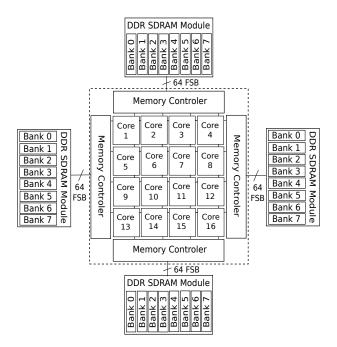

| 6.5    | Simulated CMP Structure.                                                   | 116 |

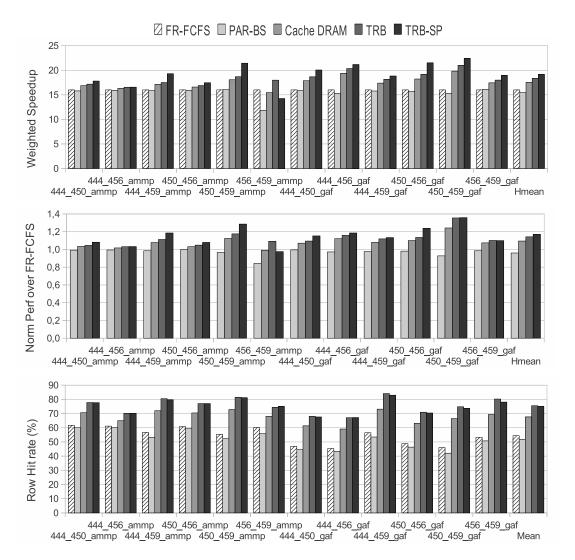

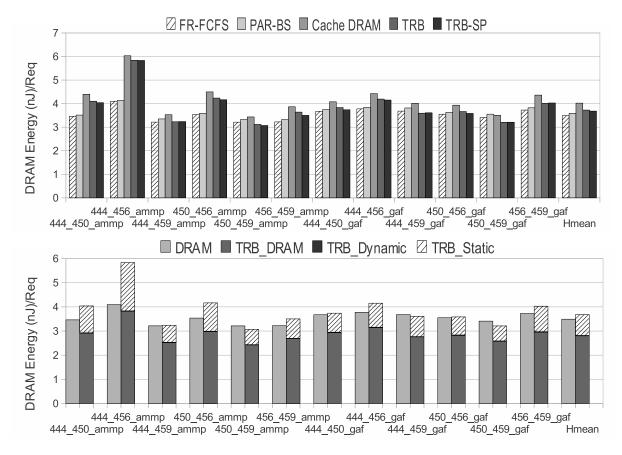

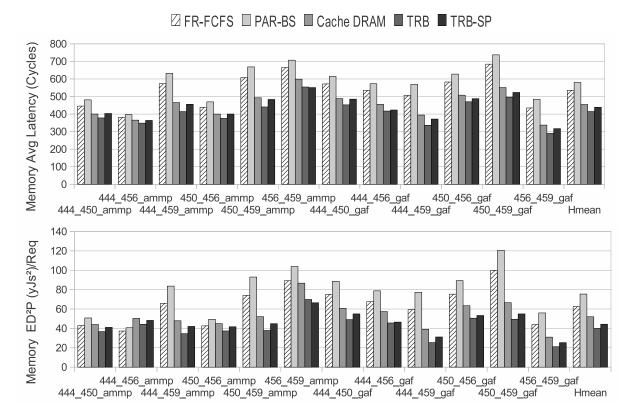

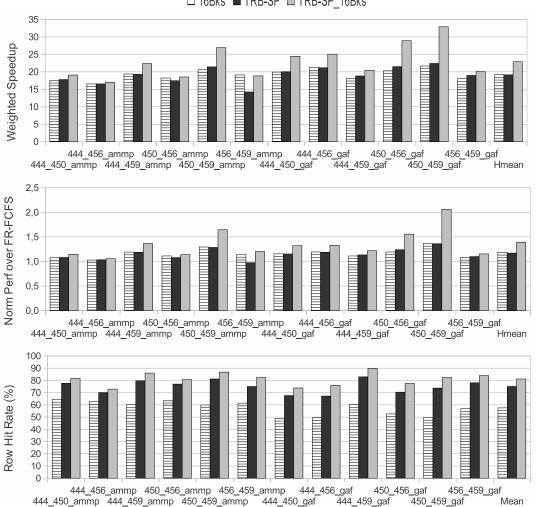

| 6.6 \  | Weighted Speedup, normalized throughput and row hit rate                   | 118 |

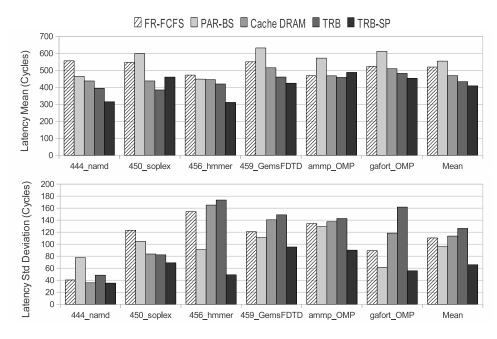

| 6.7    | Average BM latency and standard deviation                                  | 119 |

| 6.8    | TRB-SP memory power decomposition.                                         | 120 |

| 6.9 I  | Power, Avg latency and Energy-efficiency.                                  | 121 |

| 6.10 \ | Weighted Speedup, normalized throughput and Row Hit rate with extra banks. | 122 |

#### LIST OF FIGURES

# **List of Tables**

| 2.1  | MP-CMP memory organization similarities | 11 |

|------|-----------------------------------------|----|

| 2.2  | Taxonomy of CMP Cache Organizations     | 13 |

| 2.3  | Schedulers Taxonomy                     | 23 |

| 3.1  | Configuration Parameters                | 36 |

| 3.2  | Memory Configuration Parameters         | 36 |

| 3.3  | Configuration Parameters                | 37 |

| 3.4  | Memory Timing Parameters [91]           | 37 |

| 3.5  | Power related configuration parameters  | 40 |

| 3.6  | Buffer transistor sizes                 | 42 |

| 3.7  | Router transistor sizes                 | 44 |

| 3.8  | SPEC OMP2001 evaluated starting point   | 47 |

| 3.9  | SPEC OMP2001 evaluated starting point   | 48 |

| 3.10 | Benchmark Classification                | 51 |

| 5.1  | Application Types Behavior              | 99 |

# **Chapter 1**

# Introduction

Computer microarchitecture has evolved from its beginning with an improvement rate never seen before in other domains. Moore's law [95], which states that the number of transistors that can be placed inexpensively on an integrated circuit doubles every two years, has been kept true thanks to fabrication process improvements and this has allowed computer architects to introduce many optimizations in the computer architecture.

All these improvements have allowed an exponential increase in processor performance. Memory access, however, has not experienced the same improvement rate. Figure 1.1 shows a comparison between the improvements in the processor and the memory system. It can be seen that the gap between both parts has been increasing, forcing new optimizations in the memory hierarchy to alleviate this problem.

One of the solutions to this problem appeared in the early 60's with the introduction of caches [13]. The addition of extra on-chip storage allowed to take advantage of the data locality and showed to be very effective in reducing the number of off-chip accesses. A good measure of this effectiveness is that all current commercial processors make use of this technique. However, the amount of chip transistors is limited and, therefore, the amount of on-chip storage that can be added. This implies that usually not all the application data fits in this storage space and that, as a consequence, cache organizations and policies have a great impact on the system performance.

Another solution to this problem is the usage of Out-of-Order scheduling of instructions [126] which was implemented in the IBM 360/91 in 1966. These type of processors allow to execute instructions as soon as the required data is available and to advance stalled requests. This organization hides some of the memory latency and reduces the impact of the memory gap.

#### **1. INTRODUCTION**

Figure 1.1: Gap between memory and CPU performance [39].

The improvements brought by these solutions along with many others have reduced the impact of increasingly high memory latencies but the problem has remained. Furthermore, the extended usage of chip multiprocessors in the recent years has brought new challenges by adding multiple applications competing for the memory resources. In such environments, cache organization has increased its importance in the overall performance [49].

Therefore, in this thesis we have focused on the design of efficient memory hierarchies for next generation processors, which are a critical part in order to improve processor performance and try to keep sustained performance improvements in the forthcoming years.

## 1.1 Memory Hierarchy Challenges

There are several challenges brought by the fabrication technologies and the introduction of chip multiprocessors that have driven the research of this thesis. These challenges are the increasing number of processors, the limited off-chip bandwidth and power budget of processors and the arbitration between competing applications in the memory hierarchy.

#### 1.1.1 Increasing number of processors

The increased available on-chip real state and the limited power budget of current processors has forced the apparition of chip multiprocessors, which, rather than providing the maximum performance from a single core, try to improve the overall performance through parallel execution. Chip multiprocessors started packing a small number of cores but in the recent years several processors have appeared packing up to 80 cores on a single chip [52, 127]. This trend implies that shared structures should be distributed in order to avoid bottlenecks in centralized structures and allow a good scalability in next generation chip multiprocessors.

#### 1.1.2 Increased off-chip miss cost

The cost of off-chip misses has increased in importance due to several reasons that are expected to be maintained in the future [7]. First, memory clock speeds have increased at a slower pace than processor speeds, increasing the miss latency significantly. And second, the usage of chip multiprocessors has introduced the simultaneous execution of more applications in the chip while the pin count has increased very slightly. This implies that the same memory channels must be shared among all threads, increasing the pressure on the memory system.

All these limitations have increased the importance of an efficient use of the off-chip bandwidth. Therefore, new solutions must minimize the number of off-chip misses due to its high cost and in addition optimize the usage of the memory bus to extract the maximum throughput.

#### 1.1.3 Limited power budget

Another important factor in new microarchitectural designs is energy efficiency. Power consumption minimization is a very important issue in current computer architectures. Low energy consumption reduces the energy budget of companies, increases the battery lifetime of portable devices and allows lower operating temperatures that yield a higher reliability and simpler cooling mechanisms.

In the memory hierarchy improvements can come in several ways, by reducing the activity of the system (number of misses, messages, accesses to data structures), introducing simpler mechanisms that consume less energy or avoiding structures that do not increase the performance enough to justify the corresponding increase in energy consumption. In any case, novel improvements in computer architecture must focus not only on performance; energy density and energy consumption must be also taken into account.

#### **1. INTRODUCTION**

#### 1.1.4 Multiprogrammed Environments

Finally, the latest aspect that must be taken into account is the heterogeneous environment of multicore and multithreaded architectures. The simultaneous execution of different applications with different requirements makes necessary to provide an arbitration between them. Not all applications have the same data and instruction locality and, therefore, they require different amount of resources. In addition, some critical applications may require a minimal performance to operate which implies that the arbiter must deal with inter-thread interference and avoid it if possible. All these factors are a challenge in the design of a responsive memory hierarchy, able to provide the best response to all applications. The implementation of an application aware system, however, also has a great potential of improving the overall system performance.

## 1.2 Contributions

In this thesis we have focused in optimizing the memory hierarchy for next generation multiprocessors taking into account the challenges presented previously. Proposed optimizations range from the cache level to the memory level.

### 1.2.1 Distributed Coherence Mechanism

Coherence enforcement, as we are going to show, is especially important in multiprogrammed or multithreaded environments. Most of the existing solutions, however, rely in traditional private and shared cache configurations and in most cases make use of centralized structures which limit the scalability of the memory hierarchy. In this thesis we propose a distributed structure, the Distributed Cooperative Caching (DCC) [42], which has the advantages of both private and shared caches and has a better scalability and energy efficiency than existing state of the art configurations. Furthermore, we propose additional improvements to DCC in order to improve the energy-efficiency and network usage. We propose the Distance-Aware and Selective Spilling [44], which increase the spilling efficiency and reduce network usage.

### 1.2.2 Dynamic and Distributed Cache Allocation

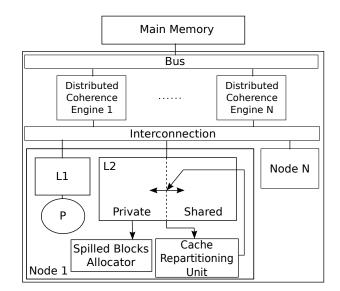

In addition of providing a distributed management of cache resources, an efficient allocation of these resources is mandatory if we want to optimize cache allocation and minimize the

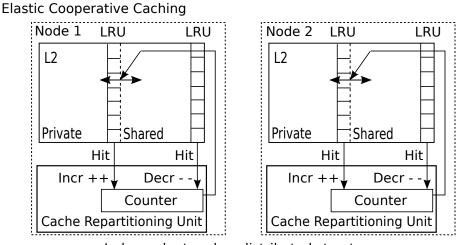

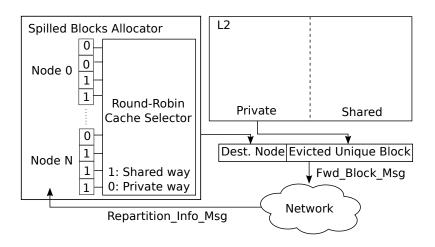

number of off-chip misses. Therefore, in this thesis we propose the Elastic Cooperative Caching (ECC) [43], a distributed cache repartitioning mechanism. ECC is able to detect the memory requirements of each application and reallocate cache resources accordingly during program execution. Most of dynamic repartitioning mechanisms rely on centralized structures. ECC, on the other hand, is able to adapt dynamically using only local information and distributed repartitioning units which make it more suitable for chip multiprocessors with a high number of cores.

All the cache organizations above, in addition to their publication in top conferences like ISCA, PACT or EuroPar, also have led to the publication of a book chapter [16] and an article in the IEEE Transactions of Parallel and Distributed Systems [45].

#### 1.2.3 DRAM organization for multiprogrammed environments

Finally, in this thesis we have focused on optimizing DRAM memories and memory controllers for multiprogrammed environments. Traditional memory bank schedulers have been designed for uniprocessor systems. The advent of chip multiprocessors, however, has led to the apparition of new access patterns and forced a trade-off between memory throughput and fairness. In this thesis we present Thread Row Buffers (TRBs), a modification of the DRAM memory structure which allows to increase the row hit rate significantly under a multiprogrammed environment and avoids the throughput-fairness trade-off. TRBs make possible to design a new generation of bank schedulers focused on an efficient arbitration between threads without hurting memory throughput.

### **1. INTRODUCTION**

# **Chapter 2**

# **Background and Motivation**

### 2.1 Introduction

The design of new processors always has been driven by the need of more computing performance. Performance improvements have arrived through the evolution of the fabrication technology, microarchitectural improvements and increase in the parallelism. Parallelism has been exploited at the instruction level, thread level and application level; being the last one the first to be used.

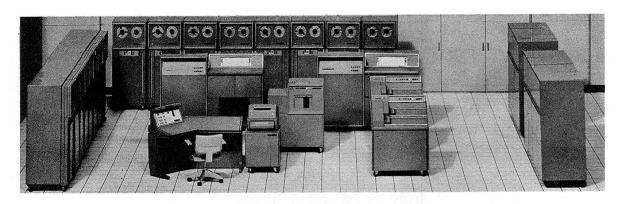

Multiprocessors have existed for many years, the first of them appearing in the early 60's. Burroughs Corporation was the first company to introduce a multiprocessor system<sup>1</sup> with the B5000 introduced in 1961 [24] that operated a second processor in a master-slave configuration. First multiprocessors were asymmetric since the operating system ran in the main processor and the second one executed specific processes, having access to main memory but not to peripherals.

Other vendors also released their multiprocessor like IBM with the model 65MP of System/360 [101] in 1968 or the PDP-10 [11] which added multiprocessing capabilities to its TOPS-10 monitor software in 1972. The PDP-10 was already a Symmetric Multiprocessor (SMP) were all processors had the same importance and capabilities and the operating system managed the shared resources.

Most of these systems, however, used a centralized memory, which posed a limitation in the scalability of the systems. Therefore, in 1973 Bell et al. [12] proposed the usage of independent computer modules with their own memory storage. The implementation of

<sup>&</sup>lt;sup>1</sup>Some people argues that the BINAC developed by the Eckert-Mauchly Computer Corporation in 1949 was the first one although it was designed to improve the reliability and not to perform different tasks in parallel. [26]

#### 2. BACKGROUND AND MOTIVATION

#### **Finally hatched**

# **BURROUGHS ANNOUNCES THE B5000**

T WAS A LONG TIME COMING – but the Burroughs Corporation B5000, that firm's first entry in the solid state computer field, promises to be an interesting addition to the industry.

Featuring an add time of three microseconds and a six microsecond memory cycle, a maximum system may include up to eight memory modules, each containing 4,096 49 bit words. An interesting feature of the machine lies in the fact that two central processors may be employed simultaneously for what Burroughs calls "true parallel processing."

B5000 will rent from \$13,500 to \$50,000 a month. The sale price range is \$540,000 to \$2,000,000. A more detailed article on the B5000 will appear in an early issue of DATAMATION.

**Figure 2.1:** Article in the Datamation magazine presenting the first multiprocessor on March 1961

multiprocessors with independent memories brought the apparition of new challenges due to the interaction of the different processes in the memory space. This generated two ways of managing the memory space; through message passing or through a shared memory space.

Message passing multiprocessors have independent memory spaces and all communications between processor nodes are explicitly defined by the programming language. Therefore, applications must know in all cases where is the data and ask for it, if necessary, to other nodes. This type of organization is intended for applications with low interaction and optimizes the network usage.

On the other hand, shared memory multiprocessors share the address space among all the nodes, therefore, allowing the programmer to access to all the memory space in a transparent way. This type of organization simplifies significantly the programming and is specially suited for applications with high interaction. The shared memory space, however, generates new requirements to manage the data in a safe way.

In shared memory multiprocessors there are two main types of data, private and shared.

Private data is used by only one processor and, therefore, should be allocated as close as possible to this processor. On the other hand, shared data is used by several processors and should be either stored in a common storage space or replicated in several locations. The existence of shared data requires the implementation of one of the main characteristics of shared memory hierarchies, memory coherence.

A coherent memory system can be defined in a simplistic way as a memory system that enforces that any read of a data item is done to the more updated version of this item. Hennessy and Patterson [39] give a more detailed definition and state that a memory system is coherent if:

- A read by a processor P to a location X that follows a write by P to X, with no writes of X by another processor occurring between the write and the read by P, always returns the value written by P.

- A read by a processor to location X that follows a write by another processor to X returns the written value if the read and the write are sufficiently separated in time and no other writes to X occur between the two accesses.

- Writes to the same location are serialized; that is, two writes to the same location by any two processors are seen in the same order by all processors.

In the first multiprocessors, the memory storage was shared and centralized and, therefore, the implementation of coherence was trivial. The usage of a centralized structure does not require to migrate or replicate data and all writes are already serialized in the request queue. Newer shared memory multiprocessors, however, implement independent memory storage which makes coherence enforcement more complex.

## 2.2 Modern multiprocessors, from NUMA to NUCA

Shared memory multiprocessors with multiple memories are known as Non-Uniform Memory Access (NUMA). Many of these organizations implement migration and replication of data in order to keep the data as close as possible to the user and reduce the access latency and network traffic. These types of systems require the implementation of coherence protocols that store the information of the sharers and the valid copies of the data.

There are three main ways of implementing the coherence protocols, with directories, with a snoop based system and explicitly by software. In implementations with directory [3]

#### 2. BACKGROUND AND MOTIVATION

the state of the data is stored in a directory that centralizes all requests and enforces coherence.

Snoop based systems [4, 35], on the other hand, store the information with all the data copies. We have divided this configuration in three types, bus based, fixed mapping and token based. Snoop based systems were traditionally bus based because a bus can be easily monitored by all sharers to update the state when the data is modified. Some implementations, however, allow the implementation of snoop protocols in any kind of network [119]. A variation for NUCA caches is to have a fixed mapping of cache blocks and try to find the block doing a search among the nodes were the data can be. A fixed order is usually defined, accessing first to the local node and having a home node for every block. Some solutions also rely on software hints to use different mappings [38]. Another variation are Token based systems [87, 89] which try to separate performance from correctness and get the benefits of both techniques. This idea tries to optimize the protocol for common cases and allow an unordered interconnect but rely on a correctness substrate to resolve races.

Finally, software coherence is the easiest one to implement by hardware because it basically consists in not providing coherence. Some processors [52] implement this technique because coherence protocols are very expensive in terms of hardware and explicitly managing cache operations can improve performance. The bad part of this type of systems is that programming complexity is much higher and, therefore, not suited for all kind of applications, especially if performance is not critical.

The selection of one memory organization and protocol or another highly depends on the physical constraints, desired performance and energy-efficiency and the type of applications that are going to be executed in the multiprocessor. In general a memory organization can be classified by the following parameters:

- Resource Placement: Memories/caches are centralized or distributed and highly banked or not.

- Coherence Enforcement: Directory-based, snoop-based or software-based.

- **Migration & Replication:** Ability to migrate or replicate data close to the requesting nodes in order to reduce the access latency and network traffic.

- **Performance Isolation:** Ability of the system to execute independent applications without interfering one with each other.

- Adaptivity: Ability of the system to adapt the available memory resources to optimize a certain performance metric depending on the different application requirements.

| Common                 | Multiprocessors  | Chip Multiprocessors     |  |  |  |

|------------------------|------------------|--------------------------|--|--|--|

| Features               | Memory (MP)      | Cache (CMP)              |  |  |  |

| Shared Centralized.    | UMA [19]         | Shared cache (UCA)       |  |  |  |

| High capacity,         |                  |                          |  |  |  |

| uniformly long latency |                  |                          |  |  |  |

| Shared Distributed.    | CC-NUMA          | Shared banked            |  |  |  |

| High capacity,         | [2, 68, 73, 74]  | cache (S-NUCA) [60]      |  |  |  |

| non-uniform latencies  |                  |                          |  |  |  |

| Private Distributed.   | COMA [36, 110]   | Private caches           |  |  |  |

| Lowered capacity,      |                  |                          |  |  |  |

| low latency            |                  |                          |  |  |  |

| Partition between      | RC-NUMA [140]    | Adaptive private/shared  |  |  |  |

| private/shared space   |                  | NUCA [30, 55]            |  |  |  |

| Victim caching         | VC-NUMA [93]     | Victim replication [138] |  |  |  |

| Hints for              | R-NUMA [32]      | R-NUCA [38]              |  |  |  |

| relocation             |                  | CMP-NuRapid [22]         |  |  |  |

| Adaptivity through     | AS-COMA [67]     | CC [17]                  |  |  |  |

| biased replacement     |                  | MLP-Repl [103]           |  |  |  |

| Adaptivity through     | OS support [129] | ASR [9]                  |  |  |  |

| selective replication  | MigRep [113]     |                          |  |  |  |

| Performance isolation  | Performance      | Fair Caching [62]        |  |  |  |

| enforcement            | Isolation [130]  | CQoS [54]                |  |  |  |

Table 2.1: MP-CMP memory organization similarities

The steady increase in the die real state has made possible the creation of multiprocessors on-chip, also known as chip multiprocessors (CMPs). CMPs started to appear as research projects like the TRIPS [109] or the Piranha [33] in 2000 and in 2001 IBM presented the first non-embedded commercial CMP with two cores, the Power4 [125]. From then the number of cores has been increasing, especially for high-end server market processors with the apparition of chips like the Niagara [65] with 8 cores and 32 threads in 2005 or the Niagara 3 with 16 cores and 128 threads in 2010.

Extensive work has been done to design a suitable memory hierarchy for these microarchitectures and many ideas from traditional multiprocessors have been adapted and reused. Table 2.1 shows the similarities of proposed memory organizations for traditional multiprocessors and chip multiprocessors.

#### 2. BACKGROUND AND MOTIVATION

Most of the existing processors use cache coherence protocols that enforce a relaxed consistency. This is that protocols allow reads and writes to complete out of order and any synchronization operation in a multithreaded application is left to the programmer. On the other hand, extensive work has appeared to create a transactional memory [41, 83, 84, 136] to facilitate parallel programming and provide atomicity, consistency and isolation to some code regions called transactions. In this thesis we use cache coherence protocols that enforce a relaxed consistency because of its simplicity and wide adoption in commercial processors. However, more strict consistency models could be added to the presented techniques.

### 2.3 Cache organizations in the multicore era

In chip multiprocessors, latencies between the different levels of the memory hierarchy have changed significantly compared to traditional multiprocessors, forcing a redistribution and reassignment of resources. In these architectures off-chip bandwidth is much more limited because it must be shared among all the on-chip cores, forcing an optimization of the on-chip cache allocation to minimize off-chip misses. In addition, access latencies between caches inside the chip are much lower than in traditional multiprocessors, allowing cheap communication between them and cache-to-cache transfers. These differences have motivated the apparition of multiple new organizations in the last decade.

Table 2.2 shows a classification of the most relevant cache configurations that have appeared. The different techniques are classified according to the type of cache being used and the coherence protocol. This classification has been done based on the last-level cache (LLC) configuration, in most cases centralized cache structures also have private L1 caches per core. Also, centralized and distributed snoop/token structures usually implement a bit vector of L1 sharers in the cache entries which can be considered a directory. However the search mechanism in the LLC is very different from the directory configuration and, therefore, are classified in different categories.

Another important characteristic of cache organizations is the ability to reassign cache resources in order to optimize cache allocation and reduce off-chip misses. Several studies have evaluated the optimal Partitioning of Cache Memory [48, 76, 118] and, if done correctly, it can have a great impact in the overall performance. We have divided the most recent work in two categories, static and dynamic. In static resource partition mechanisms all threads have the same priority and the amount of cache assigned to each thread is changed through the coherence protocol and replacement mechanisms. Dynamic resource

| Structure         | Coherence   | Ме     | mory Organization Type             | Migration     | Replication     | Isolation | Repartition | SW Support |     |     |     |                                |   |  |  |  |  |

|-------------------|-------------|--------|------------------------------------|---------------|-----------------|-----------|-------------|------------|-----|-----|-----|--------------------------------|---|--|--|--|--|

|                   |             | Ada    | aptive Caches [121]                |               |                 |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   | gs          | ML     | P-Aware Cache Replacement [103]    |               |                 |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   | e Tags      | Du     | al data Cache [34]                 |               |                 |           |             |            |     |     |     |                                |   |  |  |  |  |

| e                 | Cache       | V-w    | vay Cache [105]                    |               |                 |           | Х           |            |     |     |     |                                |   |  |  |  |  |

| ach               | Ca          | He     | terogeneous Way-Size Cache [1]     |               |                 |           | Х           |            |     |     |     |                                |   |  |  |  |  |

| С<br>Р            | e or        | Ind    | irect Index Cache [37]             |               |                 |           | Х           | X          |     |     |     |                                |   |  |  |  |  |

| lize              | Queue       |        | -Managed Cache [106]               |               |                 | X         | Х           | X          |     |     |     |                                |   |  |  |  |  |

| ntra              | ğ           |        | r Caching [62]                     |               |                 | X         | Х           |            |     |     |     |                                |   |  |  |  |  |

| Centralized Cache | Ве          |        | oS [54]                            |               |                 | X         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   | ied         |        | ity-Based Cache Partitioning [104] |               |                 | X         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   | Unified Req |        | aptive Set Pinning [115]           |               |                 | X         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   |             | -      | namic Partitioning [122]           |               |                 | X         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   |             | Ada    | aptive Shared/Private NUCA [30]    |               |                 | X         | X           |            |     |     |     |                                |   |  |  |  |  |

|                   | Snoop       | Bus    | Adaptive L2 snarfing [114]         | X             | X               |           | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   |             |        | NuRapid [22]                       | X             | V               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             |        | CMP-NuRapid [22]                   | X             | X               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             | pinç   | S-NUCA [50, 60]                    | x             |                 |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             | Snoop  | Snoop                              | doo           | doo             | doo       | doo         | doo        | doo | doo | nap | D-NUCA [50, 60]<br>M-NUCA [59] | X |  |  |  |  |

| he                |             |        |                                    | Fixed mapping | CMP-Hybrid [10] | X         |             |            |     |     |     |                                |   |  |  |  |  |

| Cache             |             |        |                                    | ТX            | R-NUCA [38]     |           | x           |            |     | x   |     |                                |   |  |  |  |  |

| σ                 |             |        | The Auction [80]                   |               | X               |           |             |            |     |     |     |                                |   |  |  |  |  |

| ibut              |             | Token  | Adaptive Selective Replication [9] |               | X               |           |             |            |     |     |     |                                |   |  |  |  |  |

| Distribute        |             | P<br>۲ | ESP-NUCA [55]                      | x             | X               | x         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   |             | Ada    | aptive Migratory Sharing [117]     | Х             | X               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   | Directory   |        | aptive Protocol [25]               | x             | x               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             |        | lecular Caches [128]               |               | x               | x         | Х           |            |     |     |     |                                |   |  |  |  |  |

|                   | lirec       |        | geNUCA [20]                        | x             |                 |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             | Vic    | tim Replication [138]              |               | x               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             |        | operative Caching [17]             | х             | x               |           |             |            |     |     |     |                                |   |  |  |  |  |

|                   |             | Co     | operative Cache Partitioning [18]  | Х             | X               | x         | Х           |            |     |     |     |                                |   |  |  |  |  |

Table 2.2: Taxonomy of CMP Cache Organizations

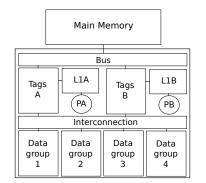

Figure 2.2: CMP-NuRapid Memory Structure.

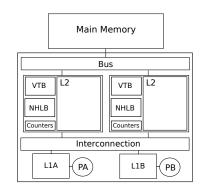

**Figure 2.3:** Adaptive Selective Replication Memory Structure.

partitioning mechanisms, on the other hand, take an active role and enforce the creation of cache partitions which are adapted to the different application requirements.

#### 2.3.1 Static partitioning

Most of the traditional cache organizations are classified in this category since the allocation of caches to threads is fixed. This does not mean that these organizations are not able to use dynamic policies to optimize the memory performance. Most techniques use dynamic migration or replication to reduce access latencies or the number of off-chip misses.

CMP-NuRapid [22] from Chisti et al. is one of the static partitioning schemes. This work proposes a duplication of tags in each node like in Figure 2.2. In this scheme, tags are copied to the local node tag set the first time the block is accessed, and the data replicated in a closer cache if the block is accessed again. This way, all subsequent accesses will have a smaller latency. It has the advantage that several blocks of the same set can be in the closer cache if they are used often with no risk of being replaced since tags and data are separated. This proposal has the power and performance limitation of requiring most of the times a transfer of the least used block to a slower group when we want to add a new one to the fast and is not scalable because blocks are found via snoop requests.

Beckmann et al. proposed the Adaptive Selective Replication mechanism [9] which adapts the level of replication dynamically. This system uses a distributed shared memory with every address mapped to only one L2. As it can be seen in Figure 2.3 the system also has extra hardware to measure if the level of replication is adequate. This hardware is a group of Next Level Hit Buffers (NHLB), a group of Victim Tag Buffers (VTB) and some counters. With this hardware a percentage of the blocks evicted from the L1 is replicated in the local L2. This percentage is known as the level of replication and is adjusted dynamically.

#### 2.3 Cache organizations in the multicore era

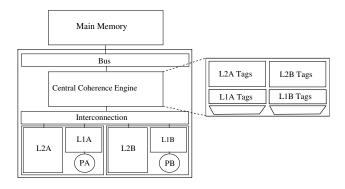

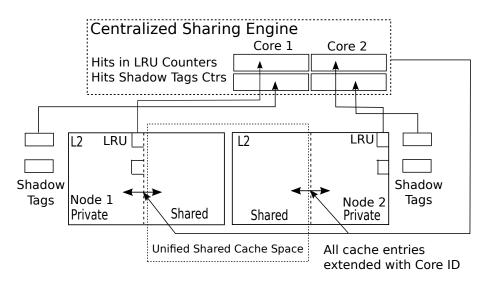

Figure 2.4: CC Memory Structure.

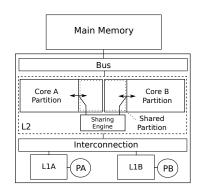

Cooperative Caching [17], on the other hand, uses a directory based protocol and private caches. This technique proposes to replicate all cache tags in a centralized directory, as shown in Figure 2.4, to allow sharing between distributed private caches. In addition, it proposes a mechanism to forward blocks with only one on-chip copy to other caches when evicted to reduce the number of off-chip misses and share the available cache space.

Finally Kim et al. [50, 60] propose a shared pool of small cache banks that can have different degrees of sharing. Dynamic mapping (D-NUCA) allows data to be stored in multiple banks but requires a tag check of all the possible destinations. Results show that statically mapping (S-NUCA) banks has similar performance and much less complexity. Different additional techniques [78, 79, 80] have been proposed to optimize replacement policies in this type of organization.

Organizations with static partitioning either have inter-thread interferences (e.g. Cacheintensive threads may degrade performance of other applications by replacing their blocks) or are not able to give all the cache space to a single thread if the others are not using the cache. This is logical if we consider that the cache space is either completely shared or statically mapped to threads, and can lead to a non-optimal usage of resources in unbalanced workloads.

#### 2.3.2 Dynamic partitioning

Dynamic resource partition mechanisms, on the other hand, dynamically modify the amount of memory that is assigned to every node. In addition to the benefits of previous proposals, they eliminate inter-thread cache conflicts and allow the implementation of fair systems or even to provide a Quality-of-Service. Thread interference is mitigated by allocating inde-

#### 2. BACKGROUND AND MOTIVATION

Figure 2.6: R-NUCA Memory Structure.

Figure 2.7: Adaptive Set Pinning Memory Structure.

pendent partitions of resources. These resources can be divided in banks, sets or ways and require an arbitration mechanism that can be software or hardware based.

Software-based dynamic configurations delegate resource allocation to the OS. Most of these organizations divide resources in independent sections to be able to provide QoS [18, 38, 54, 100]. Virtual Private Caches [100] divide resources in ways and implement a hardware arbiter to dynamically distribute the unallocated space in accordance to a fairness policy. In the Cooperative Cache Partitioning [18] resources are not only partitioned spatially, but also in time. They apply Multiple Time-sharing Partitions to expand the cache capacity of some threads at a given time and increase throughput. Iyer [54] studies different mechanisms to provide QoS in the memory hierarchy. However, it is focused on the distribution of a unified shared last-level cache. Liu et al. present the Shared Processor-Based Split L2 [81], a cache configuration that also allows software-based distribution of cache resources. The purpose of this configuration is not to provide QoS but to be able to select private or shared caches depending on the application. This organization is limited by a snoop based protocol to access cache data that requires broadcast messages to all cache banks.

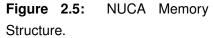

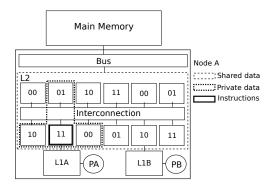

Finally, R-NUCA proposes a variable block mapping depending on the kind of data; allocating private data close to the requesting node and replicating shared read-only blocks. Figure 2.6 shows the structure and the data locations for Node A. Classification is done at a page-level granularity at the time of the TLB miss by the OS.

Hardware-based dynamic organizations [30, 50, 104, 115], on the other hand, are able to implement the repartitioning policy in hardware, reducing the programming complexity. They are based on performance counters to measure the benefit of increasing the cache size for each thread.

**Figure 2.8:** Utility-Based Cache Partitioning Memory Structure.

**Figure 2.9:** Adaptive Shared-Private NUCA Memory Structure.

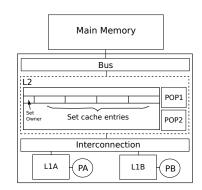

Srikantaiah et al. [115] presented the Adaptive Set Pinning, a technique to reduce interprocessor misses by assigning a replacement ownership to every set. This ownership is varied dynamically to optimize the cache usage. In addition, it uses extra small private caches (POPs) to allocate blocks of threads that do not have the ownership of the corresponding set. Figure 2.7 shows the proposed structure.

The Dynamic Spill-Receive (DSR) [102], on the other hand, uses private L2 caches to allocate evicted blocks from other caches if a performance improvement is expected. The ability to reallocate or accept evicted blocks is decided through set dueling using miss information of all caches. Therefore, for a given cache, miss information of all caches must be provided for the tested sets to decide its behavior. This makes this technique interesting for a small number of nodes but unfeasible for a large number of them due to the communication overhead that this would entail.

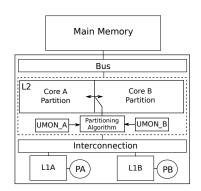

The Utility-Based Cache Partitioning [104] uses a big unified 16-way cache. In this cache, ways are assigned to nodes according to the benefits that can produce to each thread. Figure 2.8 shows the structure of this technique, which uses a centralized cache partitioned with the column caching technique [21]. In addition, the system uses Utility Monitors (UMON) which track the utility of each way for each core and decide the optimal partition of the cache. Dybdahl et al. [30] proposed a similar technique, depicted in Figure 2.9, but with a different selection criteria for the sharing mechanism. Both proposals do not try to reduce latency by allocating blocks in the closer nodes and are not scalable due to the centralized nature of the last level cache.

Another hybrid proposal is the Victim Replication [138] protocol. This configuration has a traditional distributed shared memory but adds a new replacement mechanism to reduce the miss latency. By default, blocks have a fixed L2 cache for being stored but in L1 replacements the block is replicated in the local cache if there is a spare place. The main limitation

#### 2. BACKGROUND AND MOTIVATION

of this configuration is that under heavy load conditions behaves as a normal shared cache configuration. Finally, Qureshi [102] proposed a dynamic technique that spills blocks to nodes in order to reduce the overall cache misses. This technique, however is based on a snoop protocol and is only useful for a small number of processors.

### 2.4 Memory Controllers

During the last decade memories have greatly evolved in terms of capacity and integration but still remain one of the main limiting factors of current processor performance. The steady increase in processor performance in the last decades has not been followed at the same pace by memory systems and, therefore, has created what is known as the memory gap.

This problem has been exacerbated with the introduction of chip multiprocessors, which require much larger amounts of data and have different access patterns. The simultaneous execution of multiple applications in a single core also introduces inter-thread interference and a competition to use shared resources like the memory bus. Such changes suggest that the memory hierarchy must be adapted to deal with the new requirements.

In the overall memory performance, memory schedulers have a great influence due to its capacity to prioritize different type of requests according to a given goal. Traditionally for uniprocessors throughput has been the main concern when designing these schedulers. Due to the large size of memory arrays, memories use row buffers which store a whole page to allow faster reads and writes. This buffer needs to be updated every time a different row is read or written, consuming time and energy. Therefore, it is critical that memory systems make as much use as possible of row locality to both increase performance and reduce energy consumption. The First-Ready First-Come-First-Serve (FR-FCFS) policy [108, 133, 142] is the most used organization for uniprocessors due to its simplicity and high row hit rate.

In addition, the usage of a shared resource like DRAM memory by different threads makes it necessary for the system to provide some kind of fairness or performance isolation control. Several solutions [97, 98, 99] have appeared that enforce that all threads receive a similar amount of service.

Other solutions have seen that prioritizing certain threads or regions of data can be beneficial to the overall system throughput [63, 64, 141]. Therefore, they have presented techniques not centered in memory throughput but in providing critical data in a reduced latency and in some cases combined with a fairness control.

In these microarchitectures, prefetchers continue to play an important role by increasing the memory level parallelism. The usage of prefetchers, however, can also degrade memory performance and penalize demand requests. Therefore, several organizations have been proposed [31, 70, 71, 77] in order to take into account the different request priorities and optimize the interaction of prefetchers and memory controllers.

And finally, energy efficiency has also risen as an important concern in the memory system which already can account for 30% of total system power [8]. Therefore, several new organizations have appeared [69, 137] to tackle this problem through a better usage of the DRAM power modes or through a simplification of the memory structures.

In this thesis, we present a survey of the most recent schedulers proposed for chip multiprocessors and its taxonomy. We show that many different approaches exist in the design of the memory controller and that depending on the optimization goal different solutions may be desirable.

#### 2.4.1 Memory Organization

Memory performance is highly tied to its structure and any optimization must always consider the trade-offs brought by it. Therefore, it is important to know how a DRAM memory is implemented. In this section we present a brief explanation of the main characteristics of DRAM memories, for a more detailed explanation we refer to the work of Wang et al. [131].

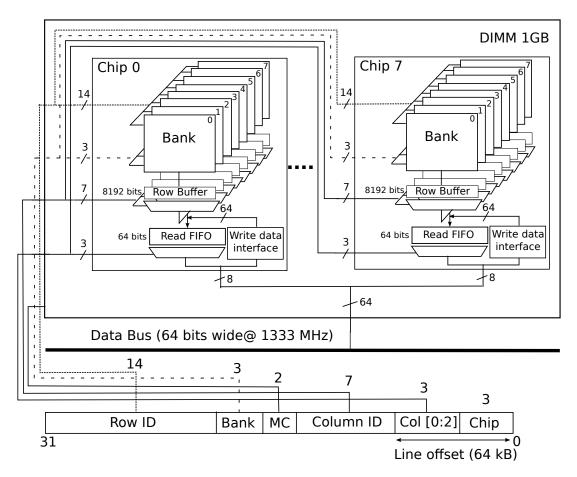

Figure 2.10 shows the organization of a typical DRAM memory. These memories have several chips (typically 8 + 1 to provide ECC), each responsible for providing a part of the block simultaneously. Inside the chip, memory is organized in banks, each holding a part of the address space. Since memory parts are very big, and to reduce access latency, data is accessed inside the memory in rows (also called pages). In order to access data every bank has a row buffer and every time that an address is accessed the corresponding row is loaded to the row buffer. Subsequent accesses to addresses in the same row require a much smaller access time since the row is already in the row buffer. This organization generates different situations that can arise when accessing memory:

**Row Hit**: In this case the row is already in the row buffer so we can read it directly. Access latency will be the Column Access Strobe latency ( $T_{CL}$ ), the time between column access and data return by the DRAM.

**Row Closed**: There is no data in the row buffer. Access latency is the one required to load (*activate command*) the row and then read. Access latency will be the Row to Column

Figure 2.10: Memory Organization and Mapping.

command Delay ( $T_{RCD}$ ), the delay between the row access command and the data ready at the row buffer, plus the read latency;  $T_{RCD} + T_{CL}$ .

**Row Conflict**: In this case, we have a different row in the row buffer and, therefore, we need to writeback this row (*precharge command*) and load the one we want to access before reading. Access latency will be the Row Precharge time ( $T_{RP}$ ) plus the activate and read latency;  $T_{RP} + T_{RCD} + T_{CL}$ .

Since no data from one bank can be transferred during its row activation or row precharge, multiple banks are used. Therefore, when a row is activated in one bank a block can be read in another one and there is always data available to be transferred.

Address mapping to physical memory also has great influence in the overall performance. In a general configuration suited for all kind of applications it would be desirable to distribute memory accesses among all memory banks and also maximize the hit rate. Figure 2.10 shows the address mapping used in this thesis. In this mapping Column ID is mapped to the least significant bits to keep consecutive addresses in the same row and

Figure 2.11: Memory Controller Structure.

maximize the hit rate. The next bits after the row are mapped to DIMMs and banks in order to spread requests among memory controllers. Finally, more significant bits are devoted to Row ID to reduce the row miss rate. This mapping is intended for open-page configurations (row is not precharged after being accessed). For closed-page configurations (row is always precharged after being accessed) adjacent lines are usually mapped to different banks to take advantage of the available bandwidth and because spatial locality is expected to be small between consecutive accesses.

### 2.4.2 Memory Controller structure

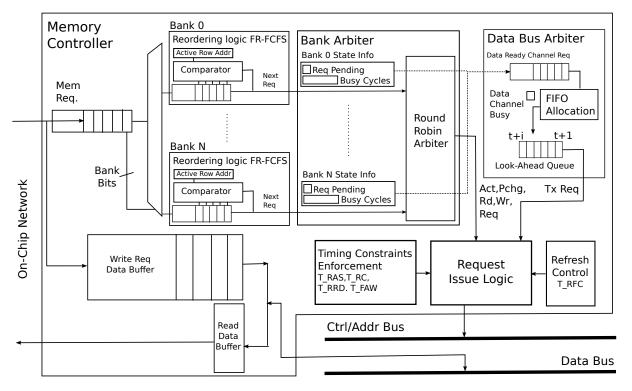

Tightly connected to the memories are the memory controllers. Memory controllers arbitrate between requests to different banks, arbitrate the data bus usage and enforce the memory timing constraints.

Figure 2.11 shows the structure of a memory controller. Requests are separated in different queues depending on the bank where the address is mapped. In these queues accesses are reordered following the desired scheduler policy. Several types of schedulers exist depending on the desired behavior of the memory system and which are going to be analyzed and classified in the following section of the chapter.

The second part of the memory controller is the bank arbiter. This part usually implements a simple round-robin arbitration policy. However, only idle banks can issue requests; therefore, it is necessary to keep track of bank states to know if they are performing a row activation or precharge or if a previous request is waiting to use the data bus.

Once the desired row is activated, requests are enqueued in the data bus queue. The data bus arbiter is a critical part of the memory controller since the limited bandwidth usually is the bottleneck in current processors. Due to the delay after read requests and data availability a look-ahead queue is required to reserve the bus at the time the data is in the Read FIFO. This arbiter also must take into account the 1 cycle delay incurred when requests change from read to write or vice-versa.

Another important function of the memory controller is the enforcement of timing constraints. Due to energy and thermal limitations memories are constrained by some parameters like  $T_{RAS}$ ,  $T_{RC}$ ,  $T_{RRD}$  and  $T_{FAW}$ . It is also necessary to refresh the data to ensure no information is lost and this must be done every  $T_{RFC}$  cycles for a given region of memory. Therefore, one important part of the memory controller must include cycle and event counters that enforce these constraints regardless of the number of requests.

Finally, the request issue logic must prioritize the request that is going to use the ctrl/addr bus, priority is given first to memory constraints, then the data bus arbiter, and finally the bank arbiter.

# 2.5 DRAM Bank Schedulers for multicore processors

In the previous section we have seen the main parts composing a typical memory controller. Most of the scheduling done in the memory controller is fixed and based on physical constraints (like the power related timing parameters) or must be First-Come-First-Serve like the bus scheduling due to complexity and starvation issues. Bank scheduling however is much more flexible since it allows to implement different reordering policies depending on the desired behavior of the memory controller and this has allowed the apparition of multiple schedulers oriented to different goals.

We have classified existing memory bank schedulers in two categories; memory oriented and system oriented. Memory oriented schedulers only consider memory metrics while system oriented take into consideration the whole system. Then we have divided these categories depending on the optimization goal. Table 2.3 shows this classification.

It is important to note that the schedulers can be optimized for two different types of throughput: memory throughput and system throughput. Memory throughput is the number

| Optimization |            | Configurations                                             |  |

|--------------|------------|------------------------------------------------------------|--|

|              | Memory     | First-Ready First-Come-First-Serve (FR-FCFS) [108, 142]    |  |

|              | Throughput | Adaptive History-Based memory scheduler [51]               |  |

|              |            | Intel's 870 system controller [14]                         |  |

| Memory       |            | Self-Optimizing memory controller [53]                     |  |

| Oriented     |            | Virtual Write Queue [120]                                  |  |

|              | Fairness   | Fair Queuing [99]                                          |  |

|              |            | Stall-Time Fair scheduling (STFM) [97]                     |  |

|              |            | Parallelism-Aware Batch Scheduling (PAR-BS) [98]           |  |

|              | System     | Fine-grain Priority scheduling [141]                       |  |

|              | Throughput | ATLAS [63]                                                 |  |

|              |            | Thread Cluster Memory (TCM) [64]                           |  |

| System       | Prefetch   | Hierarchical Prefetcher Aggressiveness Control (HPAC) [31] |  |

| Oriented     | -Aware     | Low priority prefetch [77]                                 |  |

|              |            | Prefetch-Aware DRAM Controller (PADC) [70]                 |  |

|              |            | BLP-Preserving Multicore Request Issue [71]                |  |

|              | Power/     | Power aware page allocation [69]                           |  |

|              | Area-Aware | Complexity Effective scheduling [137]                      |  |

Table 2.3: Schedulers Taxonomy

of memory requests that can be serviced in a given amount of time while system throughput is the number of instructions executed in that time. While it may seem that the higher memory throughput can provide the highest system throughput, it is not always the case as we are going to see. Several schedulers [63, 64] try to improve system throughput by prioritizing the least-attained service, assuming that thread service requirements follow a Pareto distribution.

# 2.5.1 Memory Throughput Oriented Schedulers

There has been extensive work in optimizing memory controllers for chip multiprocessors. This work has been greatly centered in the optimization of bank and channel arbitration. Request arbitration in banks first was mainly focused on memory throughput.

The First-Ready First-Come-First-Serve (FR-FCFS) policy [108, 142] is an optimal solution from the memory throughput point of view and it is widely used. This technique prioritizes accesses to active rows, minimizing the amount of row activations. Some mechanism

to avoid starvation must be included in order to ensure that under heavy load conditions all requests are serviced. Since only memory throughput is considered this technique can present fairness and isolation problems.

Many techniques have appeared lately that take into consideration the interaction between threads. One of them is the Adaptive History-Based memory scheduler [51] which reorders requests making use of the command history and the set of available commands to minimize the request delay. This technique extends the FR-FCFS policy to also consider change of rank and port delays. In addition, it proposes a mechanism to enforce that the number of reads and writes matches the application behavior in order to avoid filling the reorder queues. This technique, however, does not consider the delay of switching from a read to a write operation in the memory channel which can add a significant overhead if not taken into account.

Several techniques have considered the R/W switch delay and the fact that write requests are typically not latency critical which allows grouping and stalling requests. This write request stalling is known as write caching and is implemented in commercial controllers like Intel's 870 [14]. Write grouping allows to reduce the number of bus turnaround delays and use it more efficiently. Other techniques like Eager writeback [72], although not being memory schedulers, also consider these trade-offs and perform writebacks before the block is evicted. This technique does not necessarily group requests but allows to perform writebacks when the bus is less congested.

The Self-Optimizing memory controller [53] uses reinforcement learning techniques to estimate the long term performance impact of each action and reorder requests to maximize long-term performance. The goal of this system is also to maximize the memory throughput and this is done through the calculation of a value (Q-value) for each request which is used to select the next request to issue. The Q-value is calculated based on the number of read and write requests in the queue, the number of reads in the queue due to load misses and their arrival order, and if the reads and writes produce a row hit. The hardware solution proposed is able to compare only 12 requests from the queue which they consider is enough to achieve a good performance.